fpga时序相关概念与理解

一、基本概念理解

对于数字系统而言,建立时间(setup time)和保持时间(hold time)是数字电路时序的基础。数字电路系统的稳定性,基本取决于时序是否满足建立时间和保持时间。

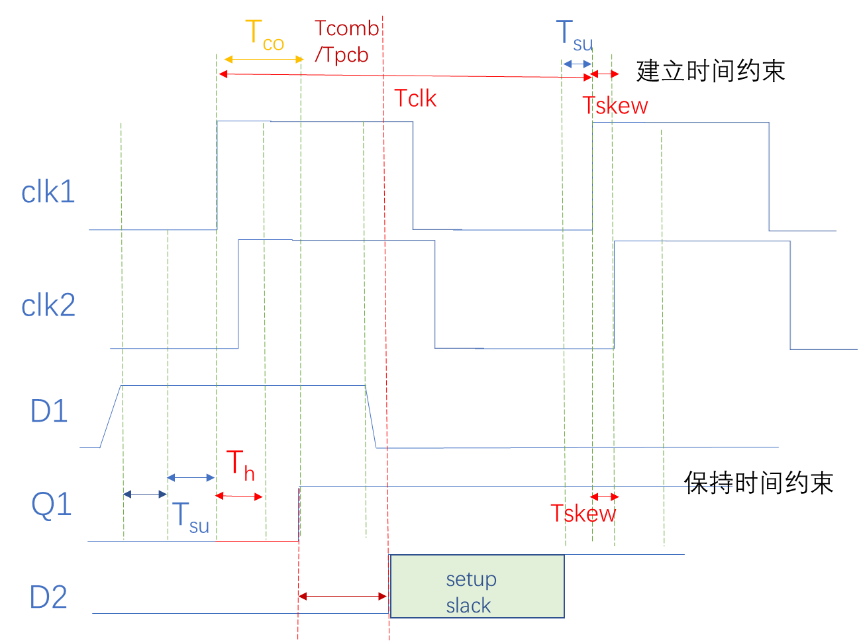

建立时间Tsu:触发器的时钟信号触发沿到来以前,数据要维持稳定不变的时间。如果D进入Tsu后仍然变化(如图1),就不满足建立时间,可能出现亚稳态。

保持时间Th:触发器的时钟信号触发沿到来以后,数据要维持稳定不变的时间。如果D进入Th后仍然变化(如图1),就不满足保持时间,可能出现亚稳态。

输出时间Tco:触发器的时钟信号触发沿 到 数据从D稳定输出到Q所需时间。

建立时间裕量setup slack:D数据变化已稳定到Tsu之前。

保持时间裕量hold slack:Th之后到D变化之前。

同步信号:和时钟信号有关,实际上输入信号和时钟信号进行了与运算或与非运算,输入信号和时钟信号的运算结果为有效状态时,器件的状态才会改变。

异步信号:信号和时钟信号无关,输入信号变为有效状态时,器件的状态就会立即改变;

恢复时间(Recovery Time):指异步控制信号在“下个时钟沿”来临之前变无效的最小时间长度。如果保证不了这个最小恢复时间,也就是说这个异步控制信号的解除与“下个时钟沿”离得太近,没有给寄存器留有足够时间来恢复至正常状态,就不能保证“下个时钟沿”能正常作用,也就是说这个“时钟沿”可能会失效。

去除时间(Removal Time):是指异步控制信号在“有效时钟沿”之后变无效的最小时间长度。 这个时间的意义是,如果保证不了这个去除时间,也就是说这个异步控制信号的解除与“有效时钟沿”离得太近,那么就不能保证这个“有效时钟沿”能正常作用,也就是说这个“有效时钟沿”可能会失效。

FAN-OUT:某信号扇出值,即驱动几个寄存器。

FPGA组成:

①可编程输入/输出单元:可配置不同阻抗特性,电流大小等。

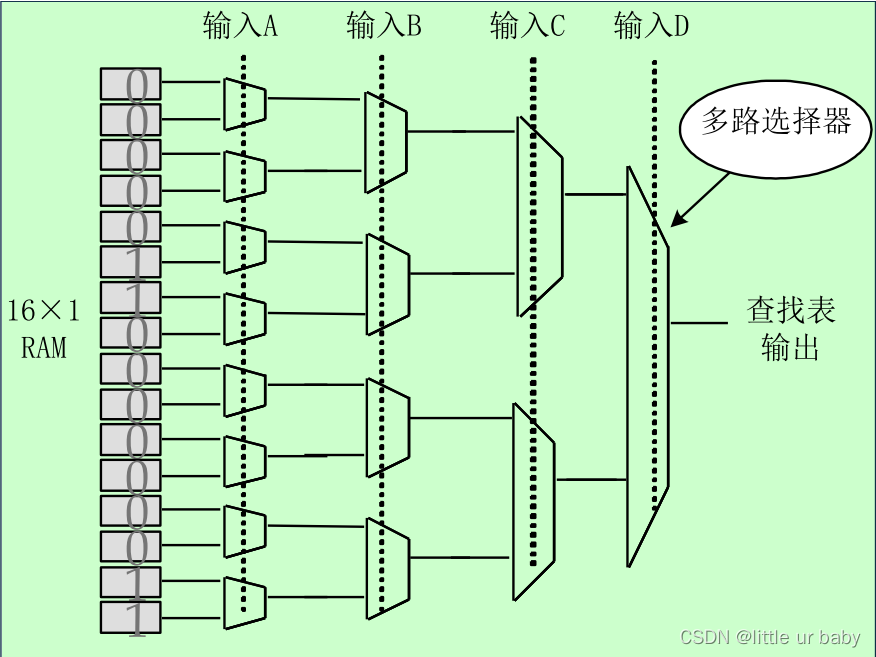

②基本可编程逻辑单元:由查找表(LUT用于组合逻辑)与寄存器(Register用于时序逻辑)。

③嵌入式块RAM:FPGA内嵌的RAM,可配置为单端口/双端口RAM,FIFO等。(FPGA还可外挂ram芯片等)。

④布线资源:全局专用布线资源(全局时钟/全局复位)、长线资源(长度、驱动能力仅次于全局资源,可用于高速信号)、短线资源(用于基本的逻辑单元连线)。

⑤底层嵌入功能单元:不固定。

⑥内嵌专用硬核:

FPGA同源时钟:源寄存器和目的寄存器应用同源时钟驱动,同源指源头是同一个时钟,相位差相同(比如由同个PLL输出的俩时钟)。

阻塞:触发器由时钟触发,在时钟触发沿到来之前,输出值不会因为输入值改变,输入值被阻塞,即电路具有维持阻塞作用。(由此理解阻塞赋值与非阻塞赋值,非阻塞即组合逻辑)使用时序逻辑替代组合逻辑可以提高时序性能。

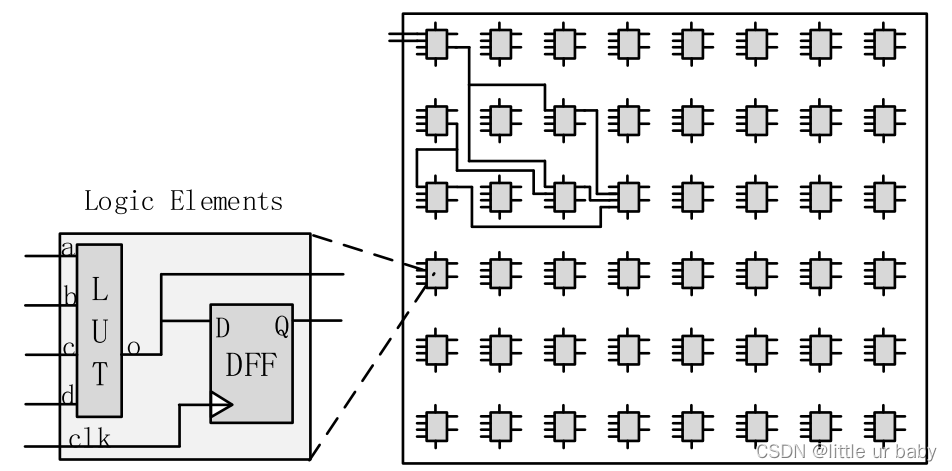

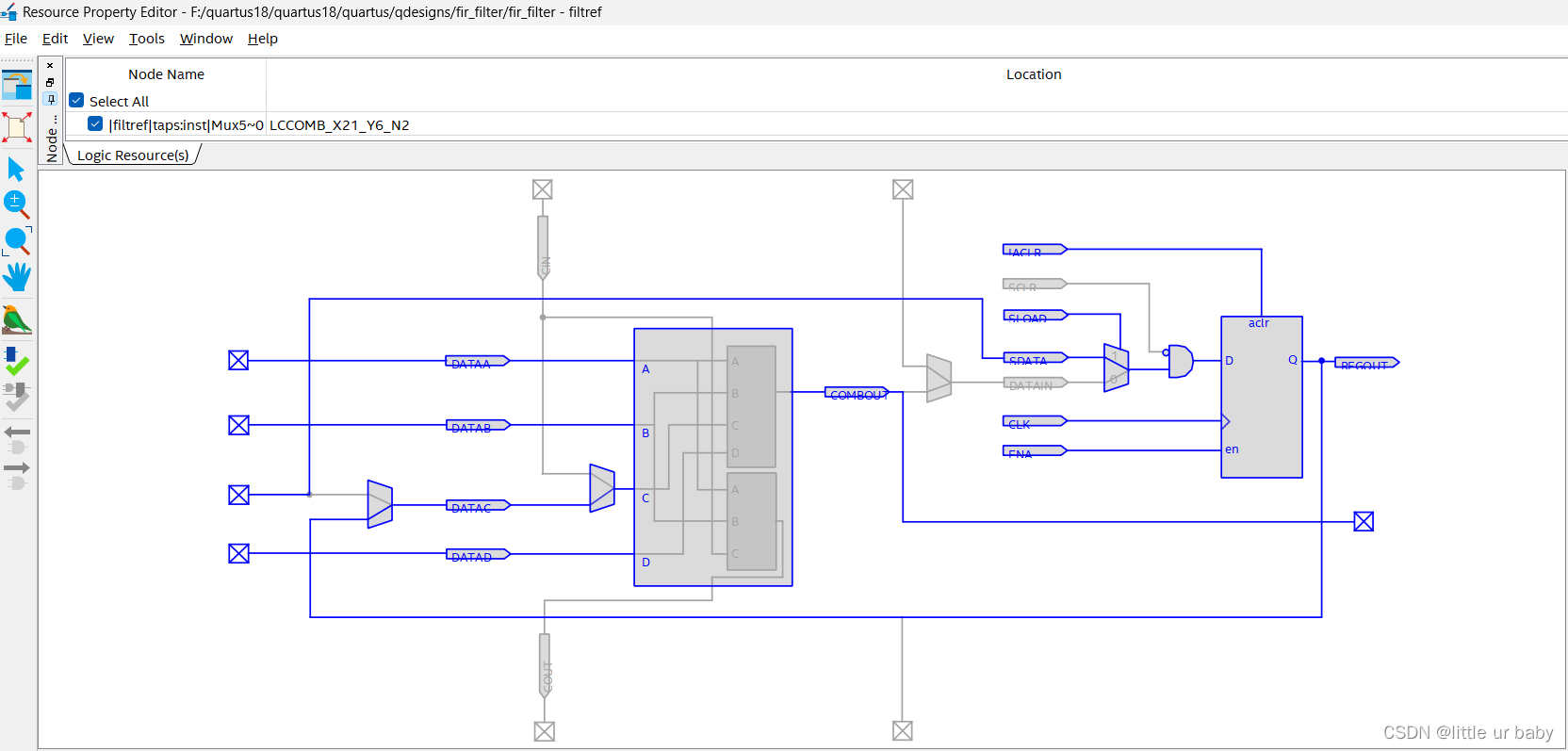

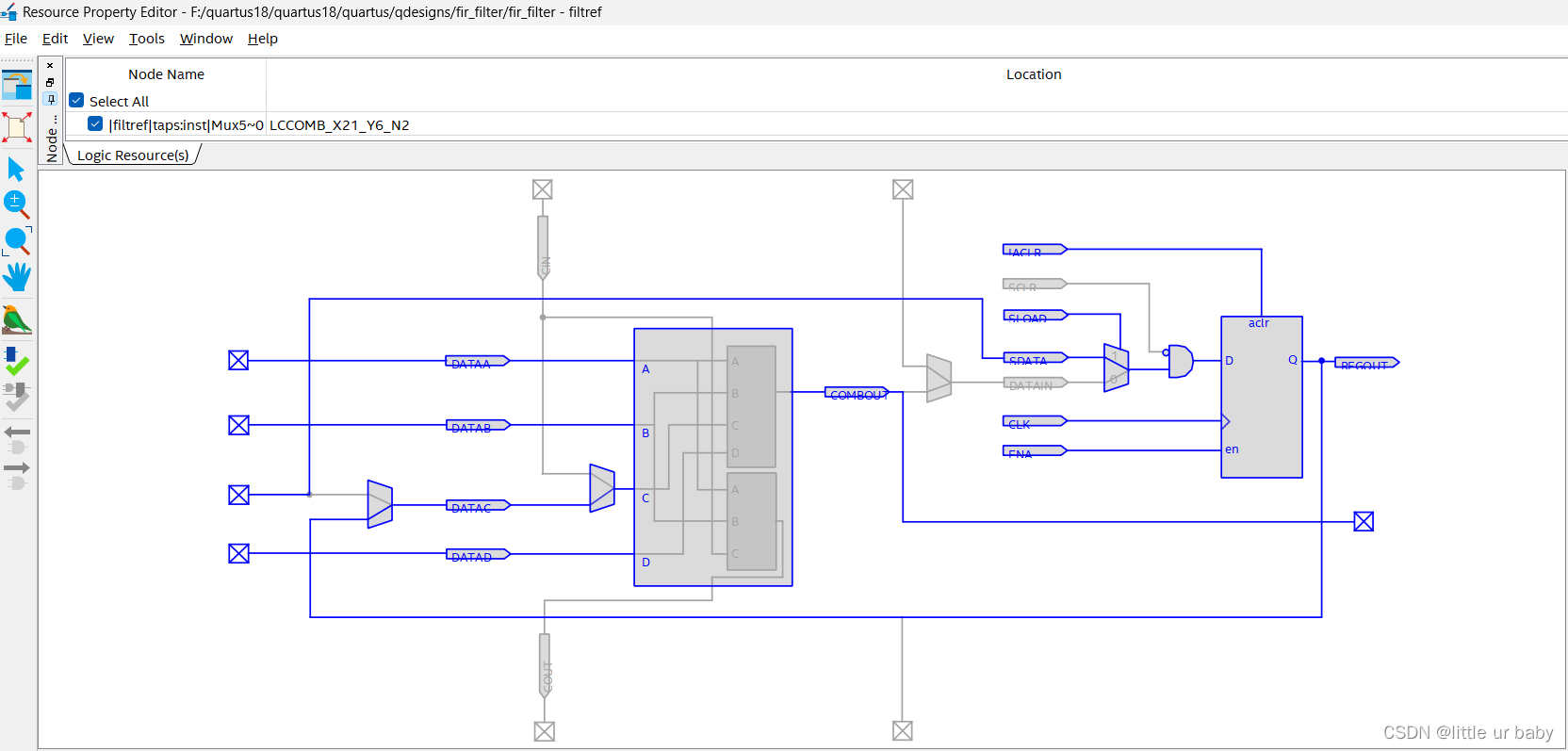

FPGA实现可编程:通过查找表LUT(由与或非等逻辑组成的特定逻辑表达式(真值表))实现任意组合逻辑;通过D触发器与时钟实现时序逻辑。FPGA架构如下图。

一个LUT里面可以实现各种组合逻辑,与、或、非门等,LUT 里面实际有16个1bit 的基于 SRAM 结构的存储器,能够对应 a、b、c、d 四个输入的逻辑组合的所有可能, Quartus 通过向这16bit的存储器里写入不同的初始值,就能使abcd 四个输入在不同的状态下输出不同的逻辑结果,从而实现使用一个LUT实现各种组合逻辑的功能。

最高运行时钟频率Fmax:在保证设计时序收敛的情况下,将时钟沿提前Tslack(最小建立时序余量)时间后得到的新时钟的周期,即最小时钟周期,对应最高运行时钟频率。即一个系统最高能跑多少兆而不出错(时序报告看)。

Slow 1200mV 85C Model:芯片内核供电电压 1200mV,工作温度85度情况下的慢速传输模型。

Slow 1200mV 0C Model:芯片内核供电电压 1200mV,工作温度0度情况下的慢速传输模型。

Fast 1200mV 0C Model:芯片内核供电电压 1200mV,工作温度0度情况下的快速传输模型。

时序分析的对象是网表模型。网表就是 Quartus 软件经过编译,布局布线后得到的实际适配某一个特定型号芯片的电路信息,该电路信息就是对应下载到芯 片中后实际在芯片中呈现的电路。

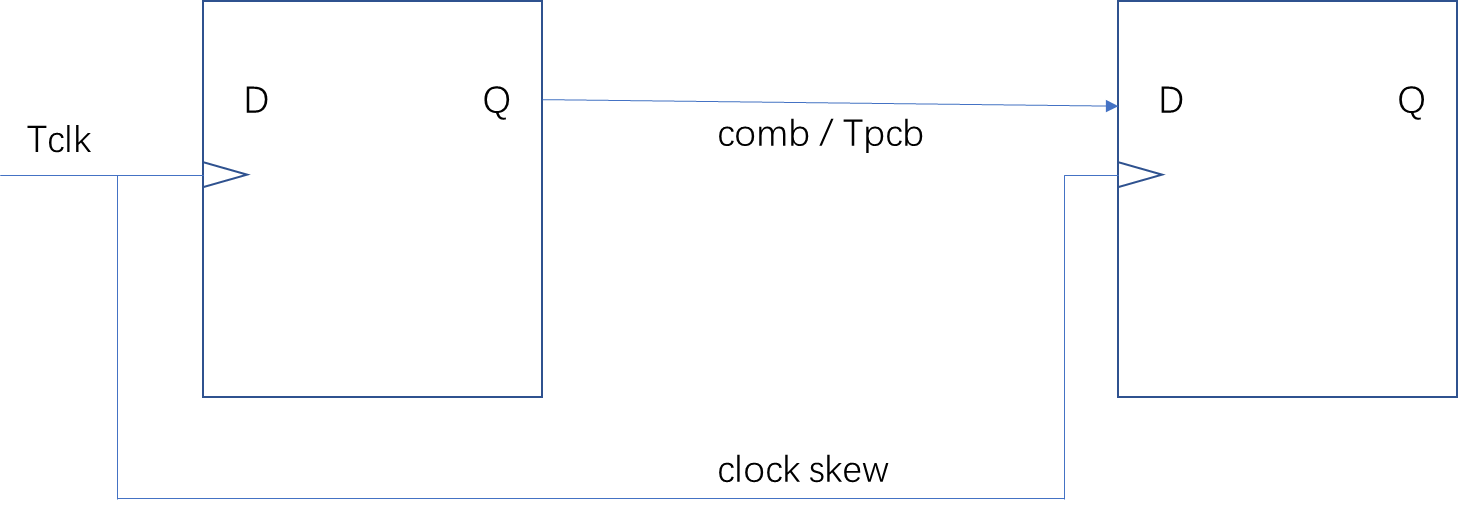

二、FPGA内部约束条件公式推导

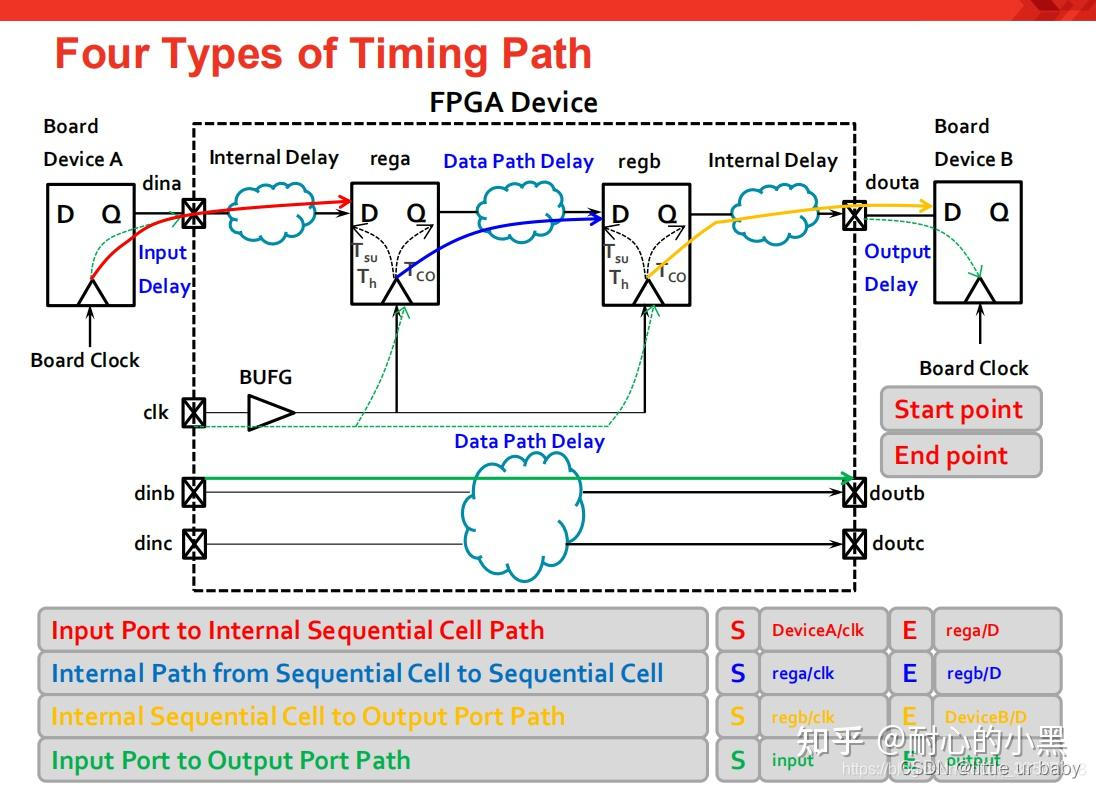

触发器-触发器 / 外部器件-FPGA 的数据传输,示意图:

Comb为组合逻辑时延,pcb为pcb板走线时延

1.建立时间约束条件:

(即满足建立时间数据是稳定的)

Tco + Tcomb+ Tsu <= Tclk + Tskew(时钟偏移)

即:Tco + Tcomb <= Tclk + Tskew(时钟偏移)- Tsu

由此可知满足建立时间约束条件的Tclk最小值为:

Tclk(min) = Tco + Tcomb + Tsu - Tskew(时钟偏移)

则最高时钟频率为: F(max) = 1 / Tclk(min)

2.保持时间约束条件:

(即满足保持时间数据是稳定的)

Tco + Tcomb >= Th + Tskew(时钟偏移)

3.建立时间约束与保持时间约束联立:

Th + Tskew(时钟偏移)<= Tco + Tcomb <= Tclk + Tskew(时钟偏移)- Tsu

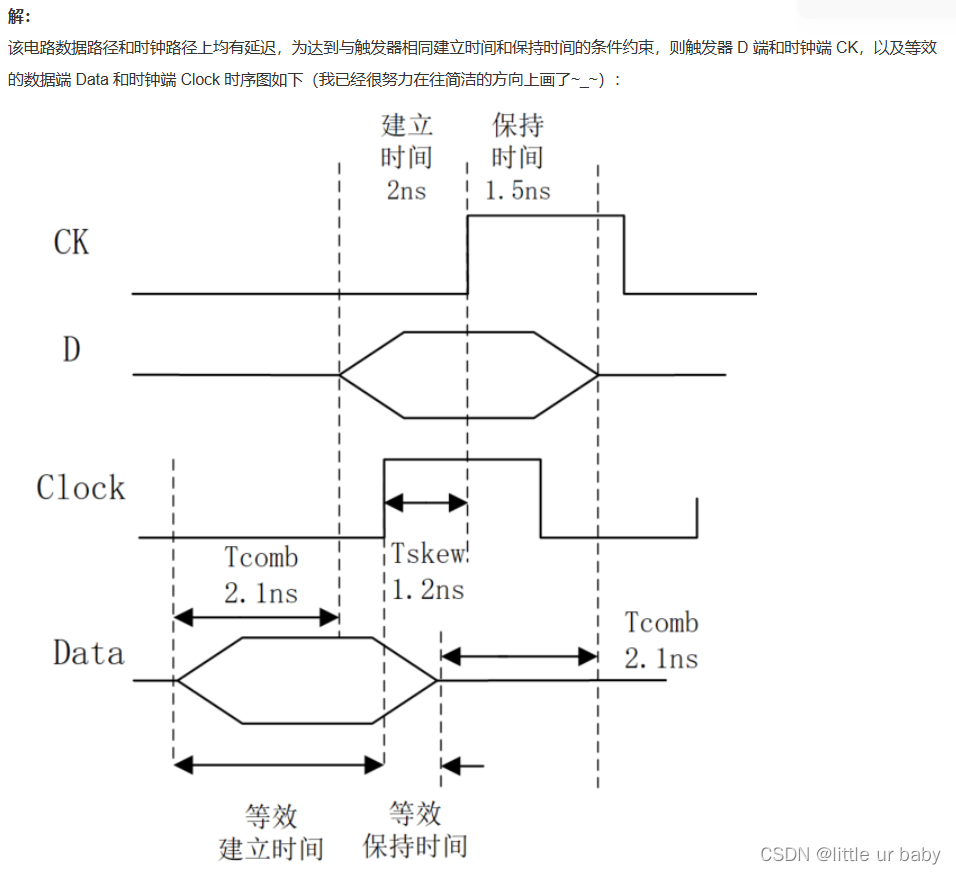

具体电路具体分析,反正就根据给出的时序图和参数,按照建立时间与保持时间的定义来解,保证没有亚稳态。即前一级输出到寄存器的时间 不能进入当前级的建立时间;当前级的保持时间不能超过当前级输出到下一级的时间。

三、题目

总结:求解电路的Tsu和Th,从电路的内部寄存器出发,假设裕量为0,从内层往外层推导。

四、IO延时约束

IO约束确保外部器件输入到FPGA时满足FPGA输入寄存器的建立时间和保持时间;确保FPGA输出到外部器件时满足外部器件的建立时间和保持时间。

1.输入最大最小延时

输入延时:外部器件发出数据到FPGA输入端口的时间。(定义)

表达式:Tin = Tco + Tpcb – Tskew (这里Tskew为什么是-,可以从上面的建立时间约束公式理解)

其中,Tco 为外部器件发出数据的时间,Tpcb为PCB板级走线的延时时间,Tskew为两个器件的时钟边沿延时时间。

根据表达式和器件物理特性可以确定:

最大输入延时:Tin(max) = Tco(max) + Tpcb(max) – Tskew(min)

最小输入延时:Tin(min) = Tco(min) + Tpcb(min) – Tskew(max)

故需估算Tco、Tpcb、Tskew。

从而对FPGA的IO口进行最大最小延时约束,优化从输入端口到第一级寄存器的路径延迟,保证系统时钟可靠采集到从外部来的信号。

2.输出最大最小延时

输出延时:FPGA输出数据后到达外部器件的延时时间。(定义)

最大输出时延:Tout max = Tpcb(max) + Tsu – Tskew(min)

其中,Tpcb为PCB板级走线的延时时间,Tskew为两个器件的时钟边沿延时时间,Tsu为外部器件的建立时间。

最小输出时延:Tout min = Tpcb(min) - Th – Tskew(max)

其中,Tpcb为PCB板级走线的延时时间,Tskew为两个器件的时钟边沿延时时间,Tsu为外部器件的保持时间。

约束最大输出延时是为了约束IO口输出,防止输出过慢,使外部器件的数据建立时间裕量为负;约束最小输出延时,是为了约束IO口输出,使IO口输出一个最小延时值,防止输出过快,破坏了外部器件上一个时钟周期的数据保持时间,导致保持时间裕量为负。

即通知编译器FPGA的Ftco最大最小值,根据这个值去综合。

对于一些参数:

PLL产生时钟信号到源寄存器的时钟延时,即使是走全局时钟网路这一延时虽小但是必然存在。 值不知道,但是TimeQuest Timing Analyzer软件可以知道,EDA软件可以一定程度控制其值大小

Tco,值不知道,但这是一个固有的物理参数,其值TTA,EDA软件也知道

数据从寄存器Q端口产生后,到达IO口,在FPGA内部传输所花费的时间。值不知道,但是TTA软件可以知道,EDA软件可以一定程度控制其值大小

在PCB走线传输花费的时间。(可以计算的,5555mil/ns,看器件)

输出时钟到达FPGA引脚的延时,值不知道,但是TTA软件可以知道,EDA软件可以一定程度控制其值大小

输出时钟到达外部器件的走线延时,(可以计算的,5555mil/ns,看器件)

五、时序约束

作用:

1.提高设计的工作频率;告知EDA软件我们的时序标准。指示布局布线器在诸多路径中选择正确的方式,减少时延,保证编译结果能够尽可能稳定运行在你指定的时钟频率下。

2.作为静态时序分析工具的判断标准,提供正确的时序分析报告。

Clock transfer:跨时钟域传输

在高速系统中,时序约束包括:

1.内部时钟约束

2.IO时序约束

3.时序例外约束

才能实现时序收敛

需要特别指出的一点是:由于时序分析是针对时钟驱动的电路进行的,所以分析的对象一定是“寄存器-寄存器”对。在分析涉及到I/O 的时序关系对时,看似缺少一个寄存器分析对象,构不成“寄存器-寄存器” 对,其实是穿过FPGA 的I/O 引脚,在FPGA 外部虚拟了一个寄存器作为分析对象。

对于源寄存器和目的寄存器中有一个不在 FPGA 内部的情况下,单纯约束 FPGA的时钟是无法让 EDA 软件对这样的路径进行分析。

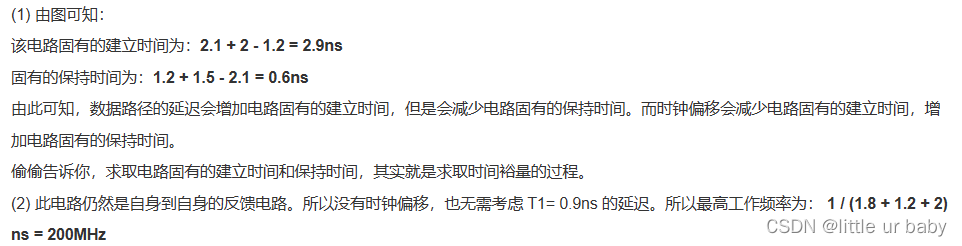

做时钟约束主要就是告诉EDA软件输入的时钟信号的频率。

IO约束就是通过告知 EDA 软件一些IO传输路径中的已知时间参数,来让 EDA 软件编译并控制 FPGA 内部的各个路径传输延迟,使得总的路径能够满足建立时间余量为正的目的。

1.内部时钟约束

在代码里,时钟信号你写input CLK_50M,你知道这是50Mhz的时钟,但EDA软件如quartus它不知道,只知道这是个时钟端口,它会根据时钟信号进行时序分析后,生成电路网表,不同的时钟信号会生成不同的优化电路网表。如果不进行时钟约束,EDA软件会自动分配一个时钟信号,编译后可以查看Clocks选项看该信号,频率不一定是我们想要的,所以需要进行时钟约束,告诉EDA软件这个时钟信号的频率,指导其布局布线。

时钟约束步骤:使用timing analyzer,依照timiequest timing analyzer文件进行即可。

2.IO时序约束

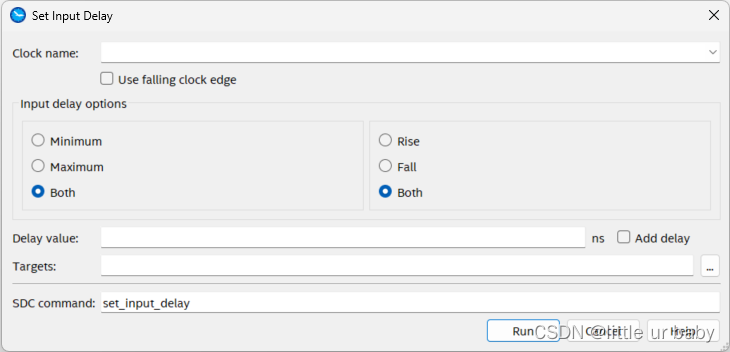

IO口约束针对最大最小输入时延和最大最小输出时延,可以在constraint-set input delay 以及 set output delay 中设置。

IO时序分析分为系统同步和源同步两种。

系统同步:基于同一时钟源进行系统同步,器件间的传输延时无法确定,不能进行高速数据的传输。

源同步:源同步输出的信号有时钟和数据信号,输出时钟由FPGA产生,有多种输出方式,如:锁相环;ALTDDIO IP核;状态机;驱动数据的时钟。

2.时序例外约束

2.1伪路径例外:伪路径表示该路径实际存在,但该路径的电路功能无须考虑时序约束。通过定义伪路径,通知vivado等FPGA开发软件无需对这些路径进行时序优化布线。这样FPGA开发软件就会自动跳过这部分路径的优化,可以减少综合布线的优化时间。使用伪路径命令可以有效地减少时序分析的复杂度,同时提高系统性能和可靠性。

六、提高Fmax

影响Fmax的是寄存器到寄存器传输路径中延迟最大(对应的建立时间余量最小)的那一条path,保证目的寄存器能够正确接收数据,所能够运行的时钟信号的最大频率。

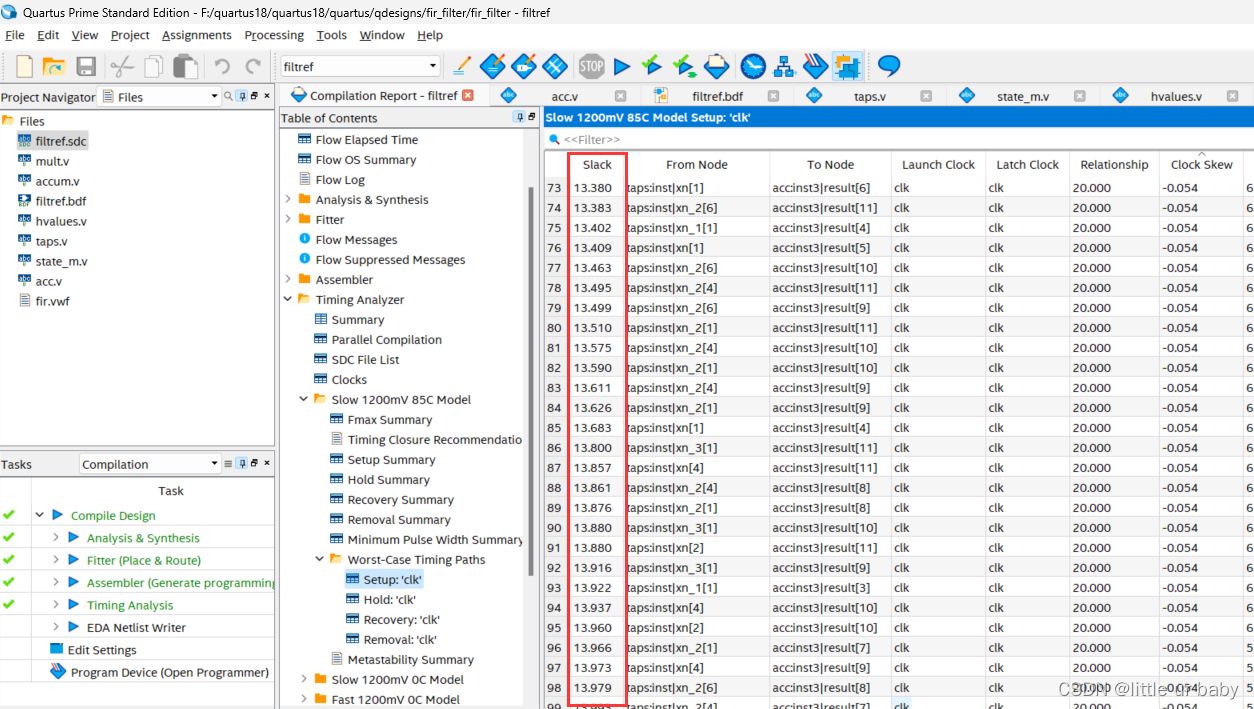

1.找最坏路径:在综合报告中,Timequest timing analyzer -> slow 1200mv 85c mode->worst-case timing paths,点击Setup:,就能在slack这一列看到建立时间余量的排序。这个余量以你约束的launch clock时钟作为参考。可以根据这个余量来提升你的工作时钟频率从而提高系统性能。正的表示在参考时钟频率下还有建立时间余量,负的表示无余量,系统Fmax达不到你要的频率。

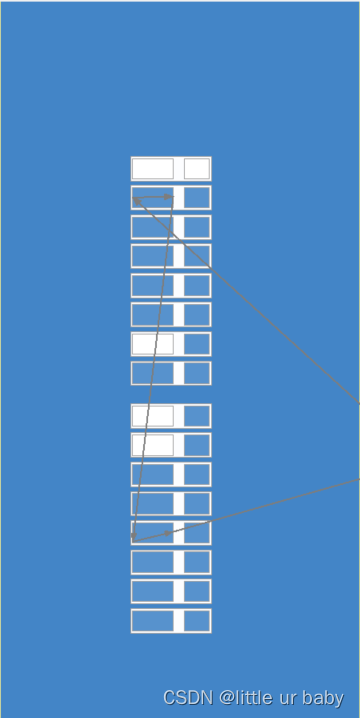

2.点击最坏路径的To node 的一个信号,右键找到locate->locate in design file。找到该信号的设计逻辑起点与终点,分析设计中是否引入了多层组合逻辑,针对优化。

3.优化的方法可以为:插入寄存器大法。在多层组合逻辑中间插入触发器(即时序逻辑),将原本较长的组合逻辑链路路径切割为了两段较短的组合逻辑路径,便可减小传输延迟。这会带来一个时钟周期的延迟。

4.优化后重新编译,可能性能只提升一点点,因为也许之前的关键路径解决了,但是马上又会有新的路径成为关键路径,需要再对新的关键路径进行分析,直到最后满足设计需求或者再也无法优化。

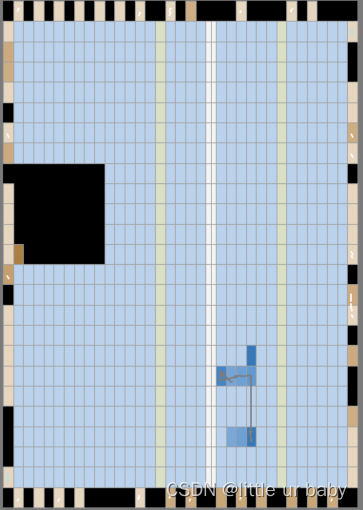

七、芯片版图

由多个逻辑阵列块组成(Logic Array Block,LAB),浅色为未使用资源,深色为已使用资源,黑色区域为一些固定功能的资源或没有资源,用户不可对其进行任意配置。

(1)逻辑阵列块(Logic Array Block,LAB):每个LAB由16个LE(Logic Element)组成。

(2)逻辑单元(Logic Element,LE):每个LE由一个寄存器和一个查找表组成。

内部结构:

由查找表、寄存器、进位链、数据选择器组成。查找表大部分采用SRAM工艺,即存储真值表,实现组合逻辑;寄存器可配置成触发器、锁存器、同步/异步复位等模式;进位链方便加法器实现。

锁相环:PLL 的时钟输入可以是PLL 所在的 Bank 的时钟输入管脚或者其他 PLL 的输出,FPGA 内部产生的信号不能驱动PLL。

时序分析时可以通过在data path页面右击选择locate到chip planner,从而在芯片版图上看路径连线等情况。

相关文章:

fpga时序相关概念与理解

一、基本概念理解 对于数字系统而言,建立时间(setup time)和保持时间(hold time)是数字电路时序的基础。数字电路系统的稳定性,基本取决于时序是否满足建立时间和保持时间。 建立时间Tsu:触发器…...

)

安卓常见设计模式12------观察者模式(Kotlin版、Livedata、Flow)

1. W1 是什么,什么是观察者模式? 观察者模式(Observer Pattern)是一种行为型设计模式,用于实现组件间的松耦合通信。主要对象有观察者接口(Observer)和可观察对象(Observable&…...

USB偏好设置-Android13

USB偏好设置 1、USB偏好设置界面和入口2、USB功能设置2.1 USB功能对应模式2.2 点击设置2.3 广播监听刷新 3、日志开关3.1 Evet日志3.2 代码中日志开关3.3 关键日志 4、异常 1、USB偏好设置界面和入口 设置》已连接的设备》USB packages/apps/Settings/src/com/android/setting…...

安装 libssl1.1)

Ubuntu 22.04 (WSL) 安装 libssl1.1

废话不多说!!! 步骤一: echo "deb http://security.ubuntu.com/ubuntu focal-security main" | sudo tee /etc/apt/sources.list.d/focal-security.list 步骤二: sudo apt-get update 步骤三:…...

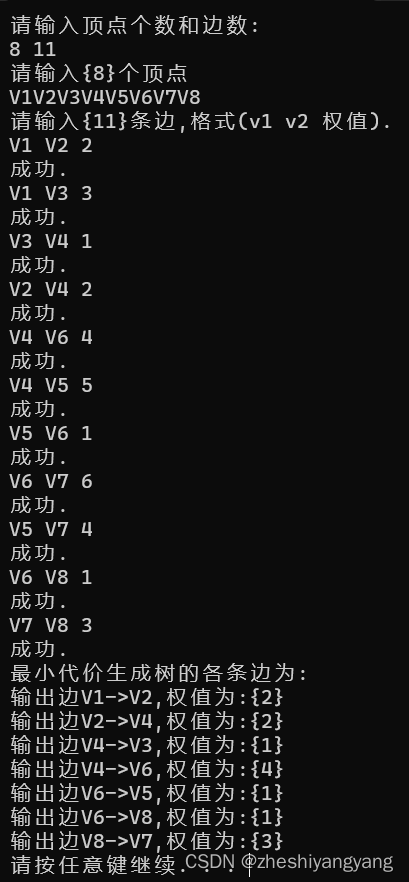

数据结构-图的课后习题(2)

题目要求: 对于下面的这个无向网,给出: 1.“深度优先搜索序列”(从V1开始) 2.“广度优先序列”(从V1开始) 3.“用Prim算法求最小生成树” 代码实现: 1.深度优先搜索:…...

[Machine Learning] 多任务学习

文章目录 基于参数的MTL模型 (Parameter-based MTL Models)基于特征的MTL模型 (Feature-based MTL Models)基于特征的MTL模型 I:基于特征的MTL模型 II: 基于特征和参数的MTL模型 (Feature- and Parameter-based MTL Models) 多任务学习 (Multi-task Lear…...

【C语言从入门到放弃 6】递归,强制类型转换,可变参数和错误处理详解

C语言是一种功能强大的编程语言,具有许多高级特性,包括强制类型转换,递归,可变参数和错误处理。在本文中,我们将深入了解这些特性,并提供简单的示例来帮助理解。 递归 递归是一种函数调用自身的技术&…...

使用LLama和ChatGPT为多聊天后端构建微服务

微服务架构便于创建边界明确定义的灵活独立服务。这种可扩展的方法使开发人员能够在不影响整个应用程序的情况下单独维护和完善服务。然而,若要充分发挥微服务架构的潜力、特别是针对基于人工智能的聊天应用程序,需要与最新的大语言模型(LLM&…...

CSS3 用户界面、图片、按钮

一、CSS3用户界面: 在CSS3中,增加了一些新的用户界面特性来调整元素尺寸、框尺寸和外边框。CSS3用户界面属性:resize、box-sizing、outline-offset。 1、resize: resize属性指定一个元素是否应该由用户去调整大小。 <style…...

说说对Redux中间件的理解?常用的中间件有哪些?实现原理?

一、是什么 中间件(Middleware)是介于应用系统和系统软件之间的一类软件,它使用系统软件所提供的基础服务(功能),衔接网络上应用系统的各个部分或不同的应用,能够达到资源共享、功能共享的目的…...

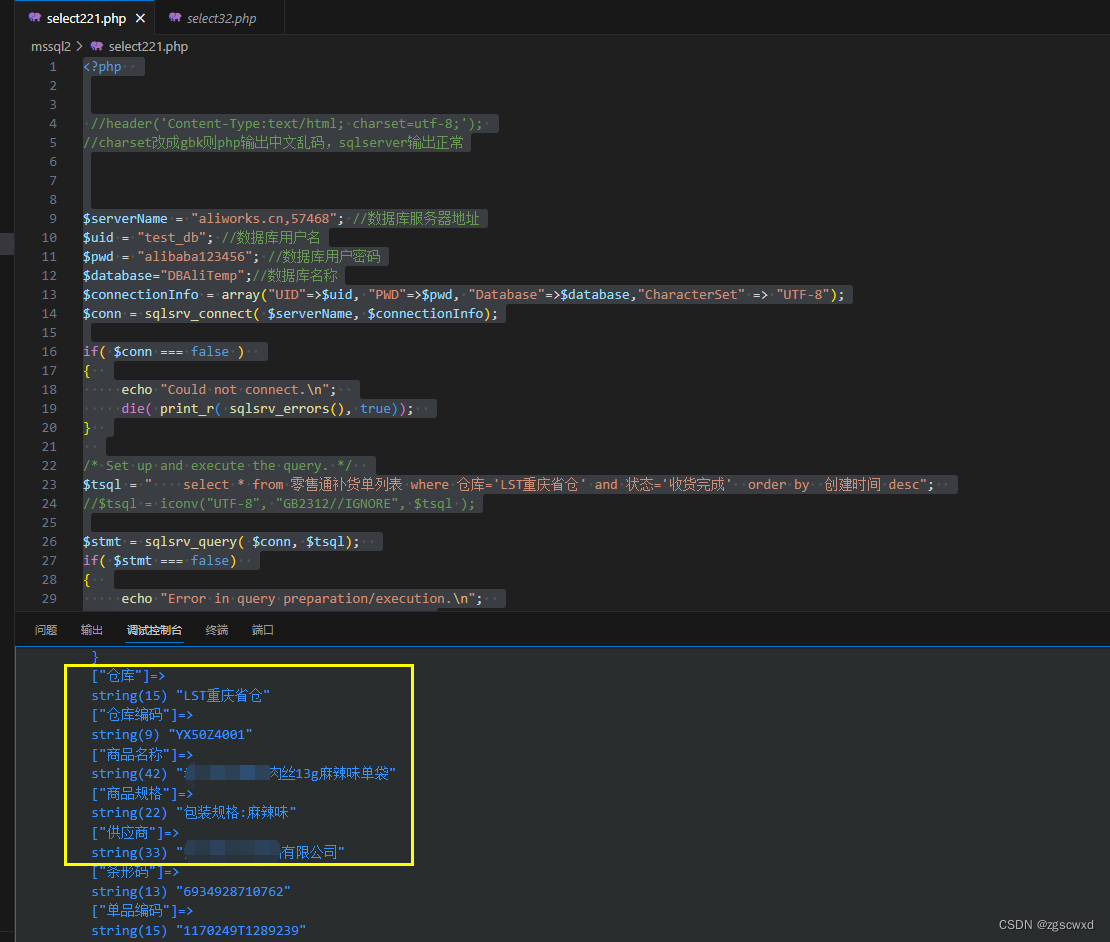

【已验证】php配置连接sql server中文乱码(解决方法)更改utf-8格式

解决数据库中的中文数据在页面显示乱码的问题 在连接的$connectionInfo中设置"CharacterSet" > "UTF-8",指定编码方式即可 $connectionInfo array("UID">$uid, "PWD">$pwd, "Database">$database…...

《未来之路:技术探索与梦想的追逐》

创作纪念日 日期:2023年07月05日文章标题:《从零开始-与大语言模型对话学技术-gradio篇(1)》成为创作者第128天 在这个平凡的一天,我撰写了自己的第一篇技术博客,题为《从零开始-与大语言模型对话学技术-…...

vue3 自动导入composition-apiI和组件

1.api的自动导入 常规写法: <script setup>import { ref, reactive, onMounted, computed ,watch } from vue;import { useRouter } from "vue-router";const router useRouter();const person reactive ({name:张三,age…...

LeetCode15-三数之和

本文最精华的就是下面的视频讲解! 🔗:参考的视频讲解 class Solution {public List<List<Integer>> threeSum(int[] nums) {List<List<Integer>> ans new ArrayList<>();Arrays.sort(nums);int nnums.length;int i0,j0,k0,sum0;for(…...

)

安全物理环境(设备和技术注解)

网络安全等级保护相关标准参考《GB/T 22239-2019 网络安全等级保护基本要求》和《GB/T 28448-2019 网络安全等级保护测评要求》 密码应用安全性相关标准参考《GB/T 39786-2021 信息系统密码应用基本要求》和《GM/T 0115-2021 信息系统密码应用测评要求》 1物理位置选择 1.1机房…...

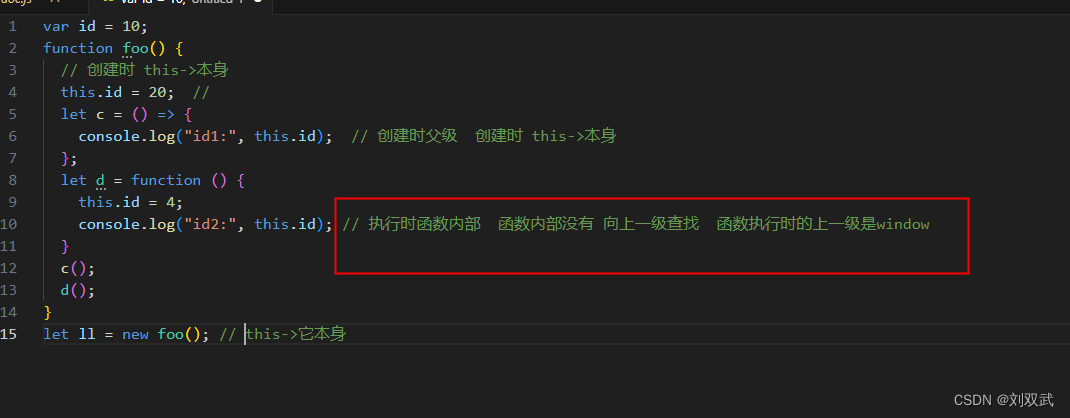

箭头函数 跟匿名函数this的指向问题

var id 10; function foo() {// 创建时 this->windowthis.id 20; // 等价于 window.id 20let c () > {console.log("id1:", this.id); // 创建时父级 创建时 this->window};let d function () {console.log("id2:", this.id); // 执行时本…...

Java Stream:List分组成Map或LinkedHashMap

在Java中,使用Stream API可以轻松地对集合进行操作,包括将List转换为Map或LinkedHashMap。本篇博客将演示如何利用Java Stream实现这两种转换,同时假设List中的元素是User对象。 1. 数据准备 List<User> list new ArrayList<>(…...

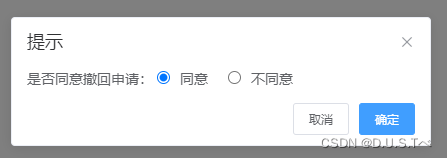

vue2+elementui使用MessageBox 弹框$msgbox自定义VNode内容:实现radio

虽说实现下面的效果,用el-dialog很轻松就能搞定。但是这种简单的交互,我更喜欢使用MessageBox。 话不多说,直接上代码~ <el-button type"primary" size"mini" click"handleApply()" >处理申请</el-b…...

OC 实现手指滑动拖动View

RPReplay_Final1699613924 实现手指滑动拖动View 支持手势移动的控件 支持 Masonry frame 布局 使用富文本 也支持自动高度 核心代码 - (void)handlePanGesture:(UIPanGestureRecognizer *)p {CGPoint panPoint [p locationInView:self.view];CGPoint currentViewPoint _dr…...

多级缓存之实现多级缓存

多级缓存的实现离不开Nginx编程,而Nginx编程又离不开OpenResty。 1. OpenResty快速入门 我们希望达到的多级缓存架构如图: 其中: windows上的nginx用来做反向代理服务,将前端的查询商品的ajax请求代理到OpenResty集群 OpenRest…...

终极指南:如何用ViGEmBus虚拟手柄驱动彻底解决Windows游戏兼容性问题

终极指南:如何用ViGEmBus虚拟手柄驱动彻底解决Windows游戏兼容性问题 【免费下载链接】ViGEmBus Windows kernel-mode driver emulating well-known USB game controllers. 项目地址: https://gitcode.com/gh_mirrors/vi/ViGEmBus 你是否曾经遇到过这样的尴尬…...

PHP PDF生成方案:FPDF如何解决Web应用中的文档输出难题

PHP PDF生成方案:FPDF如何解决Web应用中的文档输出难题 【免费下载链接】FPDF FPDF is a PHP class which allows to generate PDF files with pure PHP. F from FPDF stands for Free: you may use it for any kind of usage and modify it to suit your needs. …...

)

Ubuntu 18.04 + ROS Melodic 下,ORB-SLAM3 1.0 与 0.3 版本安装避坑全记录(附USB摄像头实战)

Ubuntu 18.04 ROS Melodic 下 ORB-SLAM3 双版本安装实战指南 在机器人视觉领域,ORB-SLAM3 作为当前最先进的视觉 SLAM 系统之一,其安装配置过程却常常让开发者头疼不已。本文将针对 Ubuntu 18.04 ROS Melodic 环境,详细解析 ORB-SLAM3 1.0 …...

告别调参玄学:用Das and Dennis‘s Method在NSGA-II中均匀生成Pareto前沿参考点

告别调参玄学:用Das and Denniss Method在NSGA-II中均匀生成Pareto前沿参考点 多目标优化问题中,如何让算法高效收敛到均匀分布的Pareto前沿解集,一直是研究者和工程师面临的挑战。NSGA-II作为经典的多目标进化算法,其性能很大程度…...

别再让LED捣乱!STM32/GD32上LCD驱动编写的引脚保护避坑指南

嵌入式开发实战:多设备GPIO冲突的深度防御策略 在资源受限的MCU开发中,GPIO引脚复用引发的设备冲突堪称"经典翻车现场"。我曾亲眼见证一个智能家居项目因为LED指示灯干扰温湿度传感器数据,导致空调在38℃高温天疯狂制热——而这一切…...

)

直播卡顿、首开慢、延时高?别慌!一份超全的排查手册(附FFmpeg/WebRTC实战参数)

直播质量优化全链路实战:从现象定位到参数调优 直播过程中突然出现的卡顿、首开延迟或音画不同步,往往让技术团队如临大敌。不同于点播的事后处理,直播问题的排查需要工程师在分钟级内完成根因定位与修复。本文将构建一套从现象分析到参数调优…...

小白程序员必看!收藏这份AI大模型学习进阶指南,轻松入行!

本文针对AI大趋势下,大学生如何快速进入AI领域的问题,提出解决方案。文章从专业背景出发,将学生分为技术背景和非技术背景两类,并分别给出适合的AI岗位选择,如算法工程师、AI产品经理等。随后,针对技术岗和…...

)

告别手动保存:用PySpider + jQuery打造自动化图片收集器(附前端展示代码)

告别手动保存:用PySpider jQuery打造自动化图片收集器(附前端展示代码) 每次在网上看到喜欢的图片都要右键另存为?面对海量图片资源却无从下手?今天我们就来解决这个痛点。本文将带你用PySpider这个轻量级爬虫框架&am…...

ITK-SNAP医学图像分割:从入门到精通的完整指南

ITK-SNAP医学图像分割:从入门到精通的完整指南 【免费下载链接】itksnap ITK-SNAP medical image segmentation tool 项目地址: https://gitcode.com/gh_mirrors/it/itksnap ITK-SNAP是一款功能强大的开源医学图像分割工具,专为医生、研究人员和医…...

DoL汉化美化整合包构建指南:5分钟掌握自动化打包技巧

DoL汉化美化整合包构建指南:5分钟掌握自动化打包技巧 【免费下载链接】DOL-CHS-MODS Degrees of Lewdity 整合 项目地址: https://gitcode.com/gh_mirrors/do/DOL-CHS-MODS DoL-Lyra 构建系统是一个专为 Degrees of Lewdity 游戏打造的自动化打包工具&#x…...