聊聊近些年 CPU 在微架构、IO 速率上的演进过程

大家好,我是飞哥!

在上一篇《深入了解 CPU 的型号、代际架构与微架构》 中我们介绍了我手头的一颗 Intel(R) Core(TM) i5 的型号规则,以及它的物理硬件的 Die 图结构。以及它对应的 Skylake 核的微架构实现。

不少同学开始问我其它型号的 CPU 和它比有什么区别呢。考虑到了市场上各种新老 CPU 型号太多了,咱们没办法一一介绍。所以我想了一个办法,咱们把这些年 CPU 进化的几个关键点讲一讲。这样将来大家再看其它的 CPU 的时候,也能做到懂得历史,也能展望未来了。最重要的微内核 sunny cove的 介绍在文章的最后。

一、制程工艺的变化

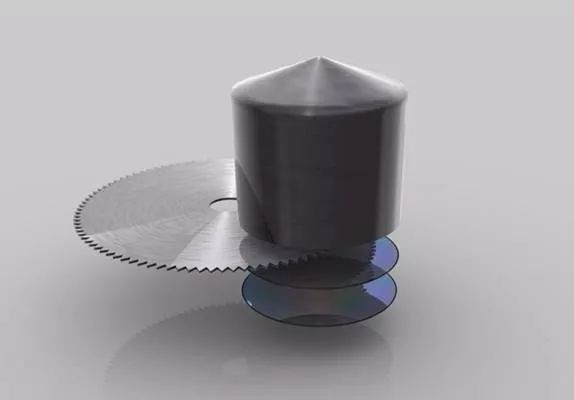

CPU 的生产过程大概是需要经过如下几步:第一步是晶圆的生产。具体过程是将包含有大量硅的石英沙放到一个巨大的石英熔炉中加热融化,然后向熔炉中加入一个小的晶种以便于硅晶体围着这颗晶种生长。直到生成一个单晶硅硅锭。这个硅锭是一个圆柱体,直径大概在 200 mm 或 300 mm。然后对硅锭进行切割,将圆柱体的硅锭切割成圆形的晶圆。

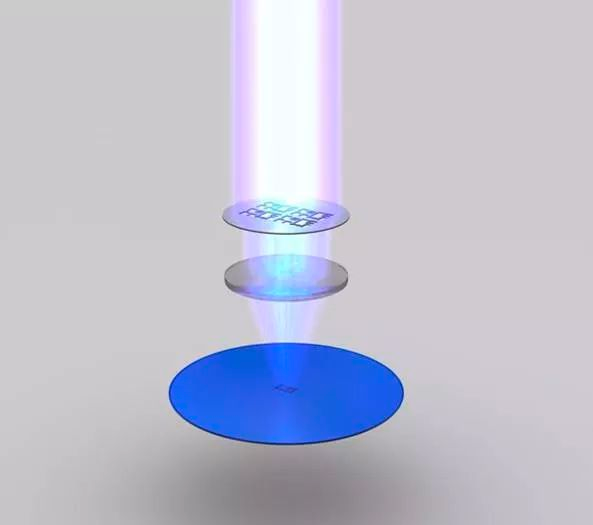

第二步是 CPU 硬件电路的制作。晶圆表面会被涂上一层光阻物质,这种光阻物质后面被紫外线照到的地方会融化。接着使用固定波长的紫外线通过印着 CPU 复杂电路结构图样的模版照射晶圆。用光来对晶圆进行蚀刻。然后再通过沉积的方式加一层硅,涂光阻物质,再次影印,蚀刻重复多遍形成一个多层结构。而且每层中间都要填充金属导体。最终在一个非常小的面积上形成一个比一座城市还要复杂的 3D 结构。

第三步是进行封装和测试。晶圆上的电路被封装起来,然后进行测试合格后就会推向市场销售。

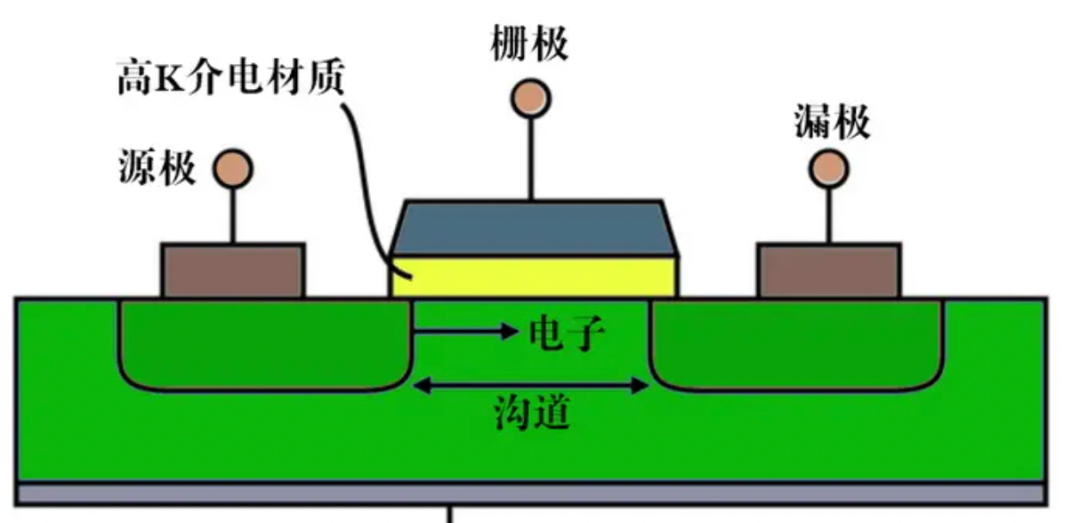

在上面的制作步骤中,最重要的是第二步。在这个过程中追求的是不断底在单位面积的芯片上布局更多的晶体管。每个晶体管的结构大概如下。

晶体管的尺寸越小,单位面积上的电路就越丰富,生产出来的 CPU 的性能就越好。另外还有就是晶体管越小的话,单个晶体管的能耗也会越低,整颗 CPU 也会越省电。

衡量晶体管尺寸大小的标准是晶体管中源极和栅极之间(沟道长度)的距离。在 Intel 历年的 CPU 中,在 2013 年的 Haswell 采用的是 22 nm 的工艺。到了 2014 年的 Broadwell 开始采用 14 nm 工艺。到了 2019 年的 Ice Lake 开始引入 10 nm 工艺。到了 2022 年的 Raptor Lake,已经开始采用 7 nm 工艺了。

一般来说,制程工艺越短,生产出来的 CPU 也就越先进。

二、集成度的变化

CPU 虽然是最精密的设备,但是它也是无法自己完成工作的。需要和计算机中的内存、显卡、硬盘、网卡、USB设备、鼠标键盘等组件配合才行。所以,CPU 需要通过硬件线路来和这些设备相连。

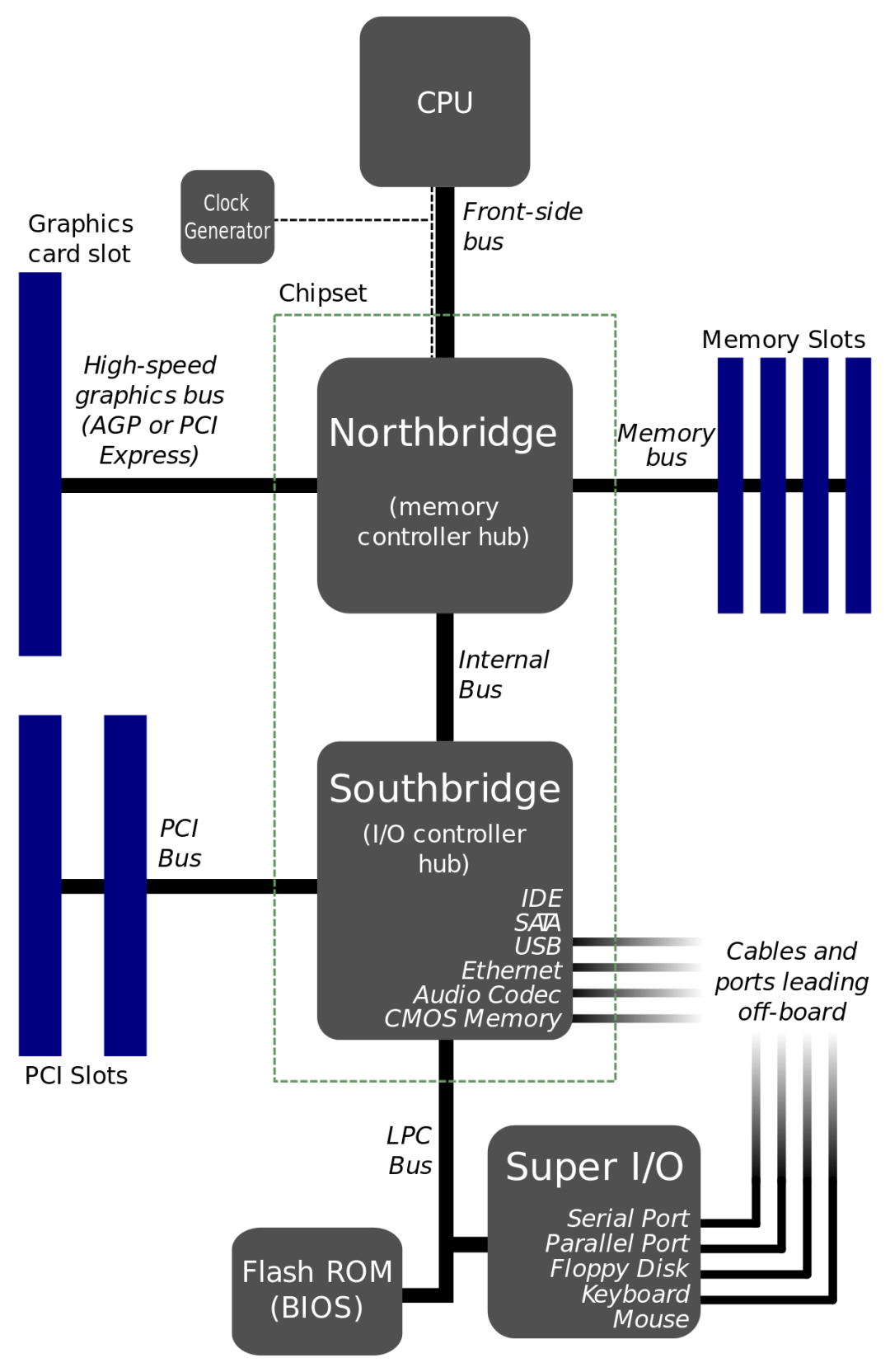

在这些设备中,所有硬件的工作频率都比 CPU 要慢。只不过有的设备虽然速度比不上 CPU,但是还是比较快的。另外一些设备比如硬盘、键盘鼠标相比更慢一些。在老式 Intel CPU 中。

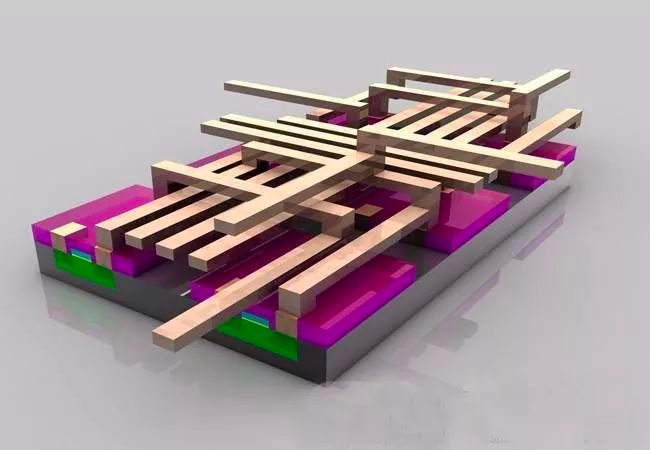

在大约 2000 年前后的老式电脑体系结构中,CPU 在主板上设计了南桥和北桥两个硬件。北桥负责与CPU通信,并且连接高速设备内存和显卡,并且与南桥通信;南桥负责与低速设备硬盘、网卡、键盘鼠标、USB设备通信,并且与北桥通信。

其中北桥芯片是存储控制器(Memory Controller Hub, MCH)。功能包括了 PCIe(Peripheral Component Interconnect Express,是一种高速串行计算机扩展总线标准)总线功能用来连接显卡。也包括了内存控制器,用来连接内存。

后来由于 CPU 对内存和显卡的数据带宽需求越来越大。Intel 从 2011 年正式发布的 SandyBridge 开始,CPU 整合内存控制器和 PCIe 控制器,相当于是把原来北桥的功能集成在 CPU 内部了,北桥从那时开始就消失了(参考https://en.wikichip.org/wiki/intel/microarchitectures/sandy_bridge_(client))。

随着时间的推移,CPU 硬件整合度越来越高。在手机芯片中,已经由于只剩下一个芯片了,也没有“芯片组”的说法了,只剩下孤零零的PCH (Platform Controller Hub)。未来随着集成度的进一步提高,未来在台式机中南桥也可能会消失。在手机中由于体积的特殊性,已经实现了最高的集成度。通过系统级芯片(System on Chip,SOC)已经把 CPU、GPU、内存、导航定位模块、多媒体模块等全部集成到了一起。

三、内存控制器的变化

每代 CPU 的一大变化就是内存控制器的提升,一般来说,越新的 CPU 所支持的内存代际越来越新、支持的内存频率越来越高。

先看 2011 年第 3 代的 Ivy Bridge。该代际下的的 CPU 支持的还是 DDR3 代的内存。Celeron、Pentium 等系列的 CPU 支持的内存频率大部分都是 DDR3-1333。只有 Core i3 和 Core i5 系列的内存频率支持到了 DDR3-1600。

到了 2014 年第 5 代 Broadwell 开始,Intel 开始在多数的 Core 系列开始大规模地支持 DDR4-2400 内存。2015 年的第 6 代 Skylake,其代际下高端的 Core i9 支持到了 DDR4-2666。到了 2016 年的 Kaby Lake,普通的 Core i5 和 Core i7 也都支持了 DDR4-2666。2019 年的 Ice Lake 的 Core 系列支持了 DDR4 3200。

到了 2021 年的 Alder Lake S 开始,开始支持 DDR5 的新内存。而且还是同时支持 DDR4-3200 和 DDR5-4800。

上面说的是台式机的内存规格。对于笔记本电脑来说,还有对应的低电压规格的内存条代际。低电压标准的内存相对比较省电,但性能会差10%左右。在具体的内存标准上,包括 DDRxL 和 LPDDRx 两个系列标准。其中其中 L 是低电压 Low Voltage 的简写,LP 是 Low Power 的简写。

拿第 4 代内存来举例, DDR4 的工作电压虽然相比 DDR3 的 1.5 v 下降到了 1.2 v,更加省电。但是相比用在笔记本中的话,功耗仍然是比较高的。而 DDR4L 可以同时除了兼容 DDR4 的 1.2 v 电压模式外,还支持 1.05 v 的低电压模式。LPDDR4 的工作电压是 1.1 v,DDR4L 和 LPDDR4 所以更适用于用在笔记本电脑等移动设备上。

CPU支持的内存除了以上指标外,还有另外一个就是通道数。直观理解,就是 CPU 上可以支持几条内存插槽。家用 PC 电脑一般都 2 个或 4 个内存插槽。在英文中对应的叫 channel 数。越多内存插槽的电脑支持的最大内存数量也就越大,整体带宽也就更高。

四、PCIe 插槽变化

前面我们提到 PCIe 总线。它是一种用于连接高速组件的高速串行计算机扩展总线标准,它取代了历史上出现的 AGP、PCI 和 PCI- X 总线标准,并经过了多次调整改进。

最早在 2003 年的时候,PCIe 1.0标准首次发布。后来因为带宽需求增长越来越快,已经陆续出现了 PCIe 1.0、PCIe 2.0、PCIe 3.0、PCIe 4.0 和 PCIe 5.0 等 5 代标准,PCIe 6.0也将在不久后发布。传输速率每过一代就会增加很多。

| 版本 | 发布时间 | 单通道传输速率 | 16通道传输速率 |

|---|---|---|---|

| PCIe 1.0 | 2003 | 2.5 GT/s (250 MB/s) | 40 GT/s (4 GB/s) |

| PCIe 2.0 | 2007 | 5 GT/s (500 MB/s) | 80 GT/s (8 GB/s) |

| PCIe 3.0 | 2010 | 8 GT/s (984.6 MB/s) | 128 GT/s (15.75 GB/s) |

| PCIe 4.0 | 2017 | 16 GT/s (1968 MB/s) | 256 GT/s (31.51 GB/s) |

| PCIe 5.0 | 2019 | 32 GT/s (3938 MB/s) | 512 GT/s (63.02 GB/s) |

Intel 的 CPU 发展过程中,在 2015 年的 Skylake 中支持了 PCIe 3.0 标准。在 2020 年的 Tiger Lake 的 CPU 中,开始支持了 PCIe 4.0 标准。在 2021 年的 Alder Lake S 中,提供了 16 通道的 PCIe 5.0 用于连接显卡,同时还支持 4 通道的 PCIe 4.0 通道用于连接固态硬盘。

五、微架构(核)的变化

在每代的 CPU 中,单个物理核的设计结构也是非常不同的。所以隔代的 CPU 性能差异也不尽相同。

在 2013 年和 2014 年,Haswell、Haswell Refresh、Broadwell 等代际采用的核的微架构设计都是一样的,都采用的是 Haswell 微架构。

在 2015 年的 SkyLake、KabyLake、Coffee Lake 等代际中,采用的都是 Skylake 微架构。

到了 2019 年发布的 Ice Lake 代际中,开始引入了 Sunny Cove 微架构。该架构下的单核性能大约比上一代提升了有 18% - 20%(参考 https://en.wikichip.org/wiki/intel/microarchitectures/sunny_cove)

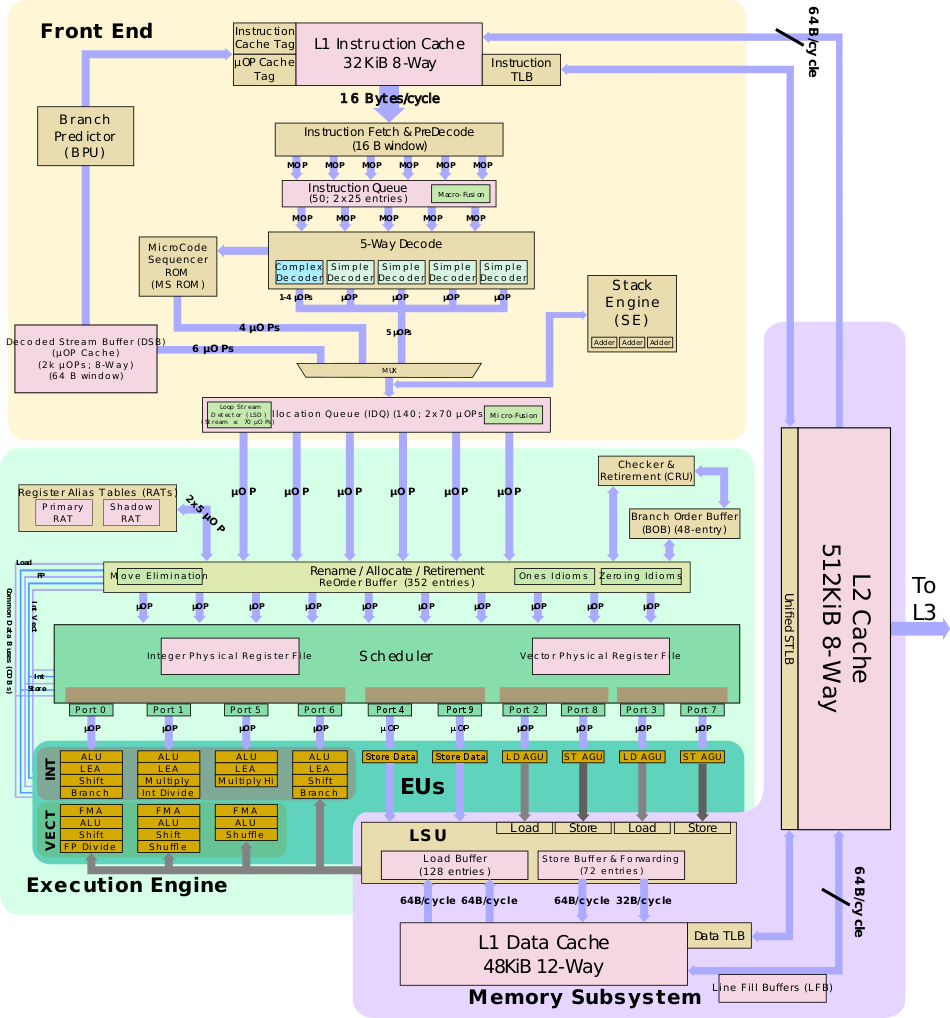

每一种不同的 CPU 微架构,在核的内部实现细节上都会有一些不同。就拿 Ice Lake 中使用的 Sunny Cove 微架构来举例,它相比上一代的 Skylake,具体的改进有如下。

对于负责指令解析的前端部分

µOP cache提升到了 2.3 k(上一代是 1536)

改进的分支预测

iTLB 缓存翻倍

对于负责指令执行的后端部分

顺序重排缓存器(ReOrder Buffer,ROB)提升到了 352 条目(上一代是224条目)

调度器(Scheduler)提升到支持 10 路超标量(上一代是 8 路超标量),每个时钟周期最多可以支持 10 个微操作

对于执行引擎部分

存储操作端口提升到了 2 个(上一代是 1 个)

地址生成端口提升到了 2 个(上一代是 1 个)

对于缓存子系统

L1 缓存提升到了 48 KiB(上一代是 32 KiB)

L2 缓存提升到了 512 Kib(上一代是 256 KiB)

STLB(Shared TLB)缓存提升了到了 2048 条目(上一代是 1536 条目),DTLB也有较大改进

另外 Sunny Cove 还引入了一些新的指令,比如 AVX-512 向量指令。所有这些核设计细节中的提升,铸就了 Sunny Cove 比上一代更强的单核性能。

到了 2020 年之后的 Tiger Lake 中,开始采用 Willow Cove 新微架构中 L2 又进一步提升到了 1.25 MB,L3 提升到了 12 MB。(参考https://en.wikichip.org/wiki/intel/microarchitectures/willow_cove)

后面到了 2021 年的 Alder Lake S 时为了平衡性能和功耗, 又开启了一个新的 CPU 设计趋势。就是借鉴手机 CPU 设计,引入了大核小核的设计区分。

在 CPU 的设计中,在性能核功耗上一直无法兼顾。内置更多的晶体管虽然可以提升性能,但会让发热功耗问题更严重。虽然制程不断提升到了 22nm、14nm、10nm、7nm、...,但是由于芯片功能的增加和性能的提升,功耗上取得的效果一直不能令人满意。

在传统的 CPU 中,不管是什么样的任务,都采用一样的核来调度和使用。但其实很多场景中,并不需要这些性能和能耗都较高的核。在新的设计趋势中,“大核”叫做“Performance Cores”,小核”叫“Efficiency cores”。

当运行各种低负载应用时,可以使用“Efficiency cores”来满足用户需求的同时来节约电量,这种核的性能一般,但优势在于省电。当真正需要有更多性能的时候,才会启动更高性能的“Performance Cores”。

总结

由于市场上各种新老 CPU 型号太多了,咱们没办法一一去了解。我们只要掌握 CPU 发展中的几个关键点的进步,就能够做到对所有 CPU 有个基本的了解了。

其中最重要的进步点是 CPU 制程工艺的变化。衡量 CPU 制程工艺的尺寸的标准是晶体管中源极和栅极之间(沟道长度)的距离。在这些年中,制程一直在进步。从 65 nm、45nm、22nm、...、10nm、7nm一直在进步。但总体上来说,已经快到物理的极限,制程的进步速度在变缓。

另外一个就是集成度的变化。早年的 CPU 中,硬件架构上设计的比较细。在新的 CPU 中,由于对带宽的要求变得越来越高。所以 CPU 硬件开发者们倾向于把更多的模块都集成到 CPU 硬件中。比如历史上的北桥,绝大部分功能都被 CPU 硬件实现了。在手机芯片中,一个 SoC 更是集成了 CPU、RAM、导航定位模块、多媒体模块等众多功能模块。

还有就是 IO 支持上的提升。对于内存控制器部分来说,支持的内存代际越来越高,从 DDR3、DDR4,一直到了今天的 DDR5。另外就是内存的频率,即使是同一代际的内存,频率支持的也是越来越高。还有就是连接显卡和固态硬盘的 PCIe 总线,也是从 1.0 逐步支持到了 5.0。

还有更重要的变化是单核微架构的设计。在新的单核架构中,CPU 中的各种缓存如 TLB、L1、L2变的越来越大,支持的超变量路数也再变多。还有就是一个新的发展趋势,CPU 厂商们引入了一些更省电的“Efficiency cores”,俗称小核。用来在系统计算任务不重的时候,使用小核来调度,节约更多的能耗。

CPU硬件一直在进步,在过去的很多年中,服务器端计算性能的提升都是靠硬件来提升的。但我觉得近些年来,这个提升趋势有变缓的迹象。因此未来更好地理解硬件内部原理,好好设计和调优服务的软件部分,让硬件性能最大程度地发挥,这件事情会变得越来越重要。

PS:应部分读者需要我规划了视频体系。具体内容包括硬件原理、内存管理、进程管理、文件系统、网络管理、容器底层原理、Golang 语言运行时、性能观测和性能优化共计九大部分。详情参见开发内功修炼视频课程上线

相关文章:

聊聊近些年 CPU 在微架构、IO 速率上的演进过程

大家好,我是飞哥! 在上一篇《深入了解 CPU 的型号、代际架构与微架构》 中我们介绍了我手头的一颗 Intel(R) Core(TM) i5 的型号规则,以及它的物理硬件的 Die 图结构。以及它对应的 Skylake 核的微架构实现。 不少同学开始问我其它型号的 CPU…...

PS学习笔记——移动工具

文章目录 介绍文档内移动文档间移动 介绍 移动工具:用于移动图层中的对象,并且同一图层中的所有对象都将一起移动 选中移动工具后,选项栏中会出现“显示变换控件”,勾选后即可看见图层中的对象周围出现边框,可以进行缩…...

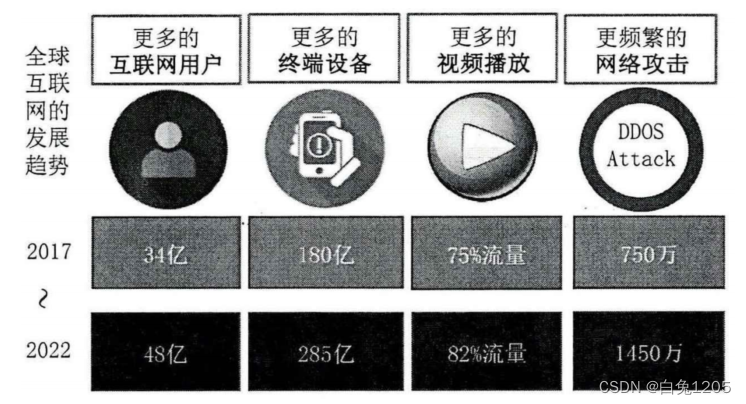

信息中心网络提出的背景、研究现状及研究内容

信息中心网络什么时候提出的?未来发展前景?有什么著名实验室在做? 1、提出背景: 互联网产生于上世纪60年代: (1)网络设备数量呈指数性增长 截至2022年底全球范围内预计将有超过280亿台终端设…...

【计算机视觉】24-Object Detection

文章目录 24-Object Detection1. Introduction2. Methods2.1 Sliding Window2.2 R-CNN: Region-Based CNN2.3 Fast R-CNN2.4 Faster R-CNN: Learnable Region Proposals2.5 Results of objects detection 3. SummaryReference 24-Object Detection 1. Introduction Task Defin…...

【mac 解决eclipse意外退出】

打开eclipse时提示报错信息应用程序"Eclipse.app"无法打开(这里忘了截图就不上图了)。 点击 “好” 的按钮后会弹出发送报告的弹窗 终端输入:sudo codesign --force --deep --sign - /Applications/Eclipse.app/ 就可以解决了...

mysql innodb buffer pool缓冲池命中率和命中了哪些表?—— 筑梦之路

环境说明 mysql 5.7及以上 公式 # InnoDB缓冲区缓存的命中率计算公式100 * (1 - (innodb_buffer_pool_reads/innodb_buffer_pool_read_requests ))注意: 对于具有大型缓冲池的系统,既要关注该比率,也要关注OS页面读写速率的变化可以更好地跟踪差异。s…...

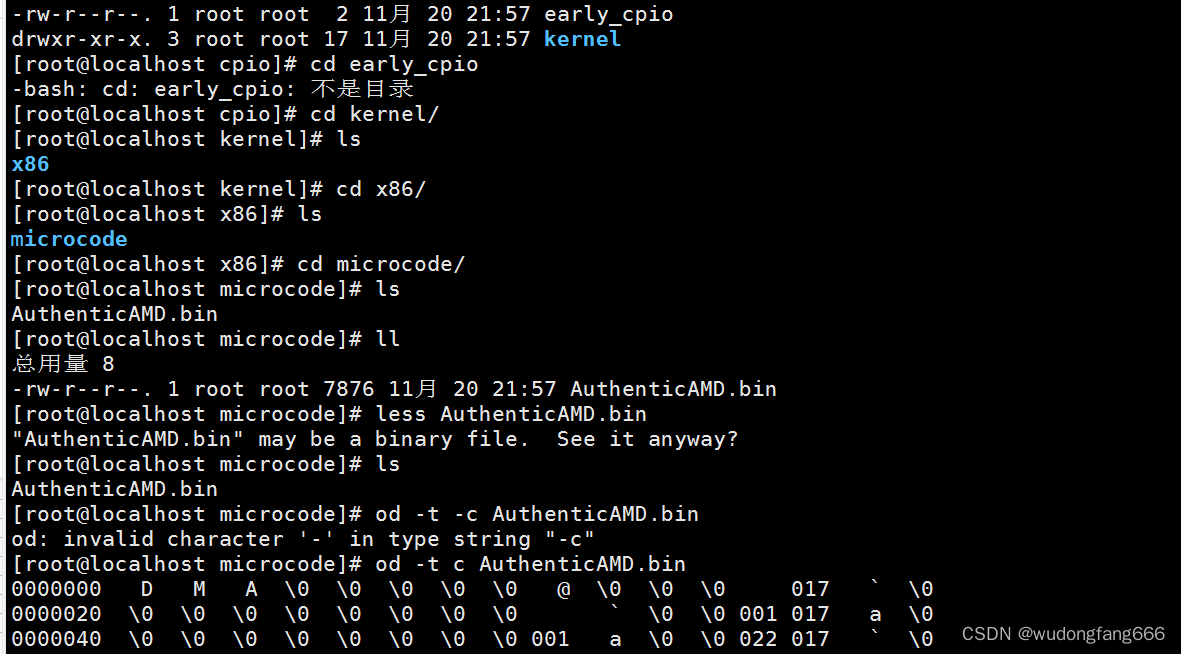

牛掰的dd命令,cpi0配合find备份(不会主动备份),od查看

dd if设备1或文件 of设备2或文件 blocknsize countn 还原就是把设备1,2调过来 这里想到dump的还原是命令restore,想起来就写一下,省的总忘记 可以针对整块磁盘进行复制,对于新创建的分区,也不用格式化,可以直接…...

pip list 和 conda list的区别

PS : 网上说conda activate了之后就可以随意pip了 可以conda和pip混用 但是安全起见还是尽量用pip 这样就算activate了,进入base虚拟环境了 conda与pip的区别 来源 Conda和pip通常被认为几乎完全相同。虽然这两个工具的某些功能重叠,但它们设计用于不…...

多目标应用:基于多目标灰狼优化算法MOGWO求解微电网多目标优化调度(MATLAB代码)

一、微网系统运行优化模型 微电网优化模型介绍: 微电网多目标优化调度模型简介_IT猿手的博客-CSDN博客 二、多目标灰狼优化算法MOGWO 多目标灰狼优化算法MOGWO简介: 三、多目标灰狼优化算法MOGWO求解微电网多目标优化调度 (1)…...

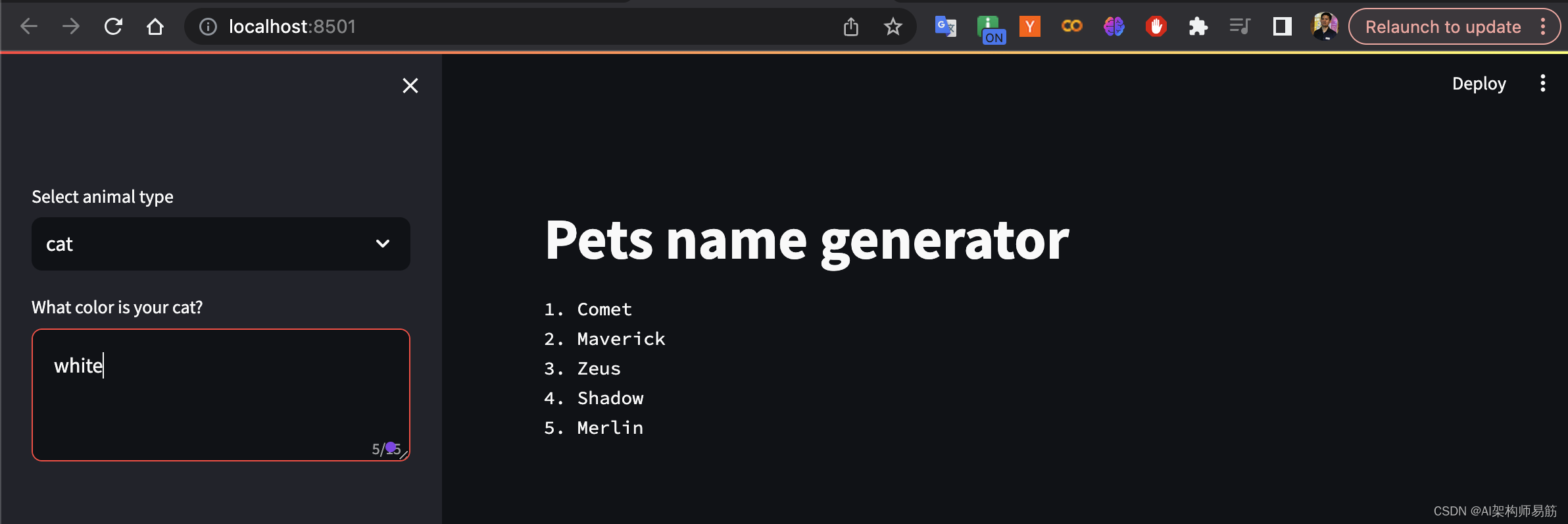

LangChain 2模块化prompt template并用streamlit生成网站 实现给动物取名字

上一节实现了 LangChain 实现给动物取名字, 实际上每次给不同的动物取名字,还得修改源代码,这周就用模块化template来实现。 1. 添加promptTemplate from langchain.llms import OpenAI # 导入Langchain库中的OpenAI模块 from langchain.p…...

linux nas

挂载到本地 mkdir -p /mnt/mountnasdir mount -t nfs 192.168.62:/cnas_id10086_vol10010_dev/ /mnt/mountnasdir...

控制您的音乐、视频等媒体内容

跨多个 Chrome 标签页播放音乐或声音 在计算机上打开 Chrome 。在标签页中播放音乐、视频或其他任何有声内容。您可以停留在该标签页上,也可以转到别处。要控制声音,请在右上角点击“媒体控件”图标 。您可暂停播放、转到下一首歌曲/下一个视频…...

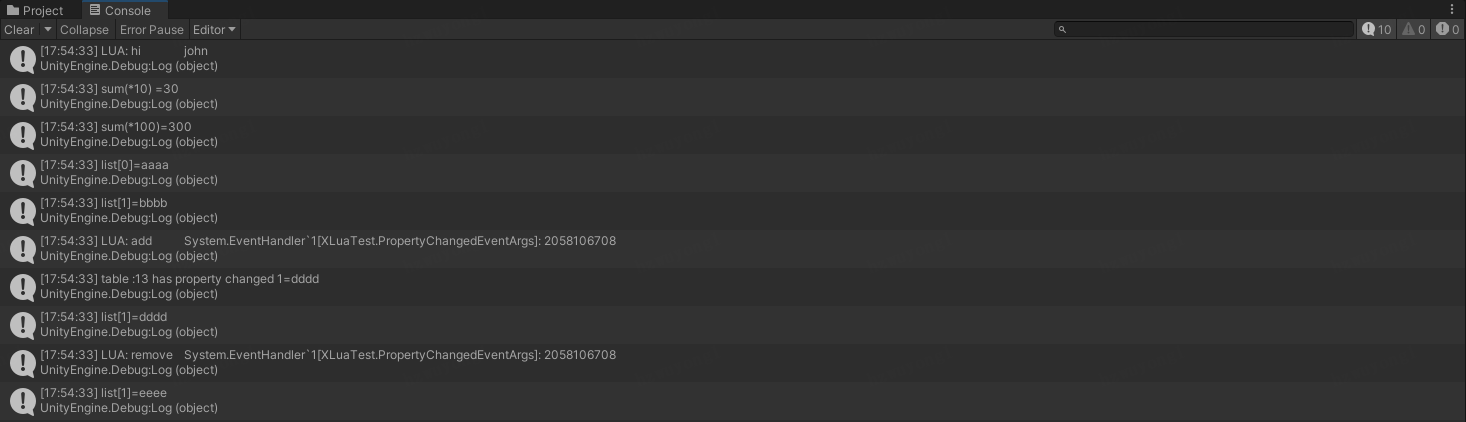

xlua源码分析(三)C#访问lua的映射

xlua源码分析(三)C#访问lua的映射 上一节我们主要分析了lua call C#的无wrap实现。同时我们在第一节里提到过,C#使用LuaTable类持有lua层的table,以及使用Action委托持有lua层的function。而在xlua的官方文档中,推荐使…...

2023 极术通讯-汽车“新四化”路上,需要一片安全山海

导读:极术社区推出极术通讯,引入行业媒体和技术社区、咨询机构优质内容,定期分享产业技术趋势与市场应用热点。 芯方向 【Armv9】-动态TrustZone技术的介绍 动态 TrustZone 是提供多租户安全媒体 pipeline 的绝佳工具。完全不受操作系统、虚…...

Spring Boot接口设计规范

接口参数处理及统一结果响应 1、接口参数处理 1、普通参数接收 这种参数接收方式是比较常见的,由于是GET请求方式,所以在传参时直接在路径后拼接参数和参数值即可。 例如:localhost:8080/api/product/list?key1value1&key2value2 /…...

美创科技与南京大数据安全技术有限公司达成战略合作

近日,美创科技与南京大数据安全技术有限公司正式签署战略合作协议,优势力量共享、共拓共创共赢。 美创科技CEO柳遵梁、副总裁罗亮亮、副总裁王利强,南京大数据安全技术有限公司总经理潘杰、市场总监刘莉莎、销售总监王皓月、技术总监薛松等出…...

2.4路由日志管理

2.4路由/日志管理 一、静态路由和动态路由 路由器在转发数据时,需要现在路由表中查找相应的路由,有三种途径 (1)直连路由:路由器自动添加和自己直连的路由 (2)静态路由:管理员手动…...

归并排序详解:递归实现+非递归实现(图文详解+代码)

文章目录 归并排序1.递归实现2.非递归实现3.海量数据的排序问题 归并排序 时间复杂度:O ( N * logzN ) 每一层都是N,有log2N层空间复杂度:O(N),每个区间都会申请内存,最后申请的数组大小和array大小相同稳定…...

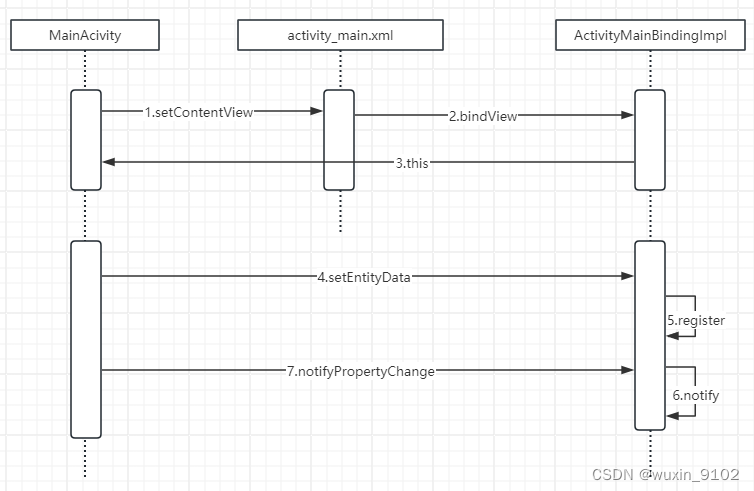

DataBinding原理

1、MainActivity首先使用DataBindingUtil.setContentView设置布局文件activity_main.xml。 2、随后,经过一系列函数调用,ActivityMainBindingImpl对象最终会实例化,并与activity_main.xml进行绑定。 3、实例化后的ActivityMainBindingImpl对象…...

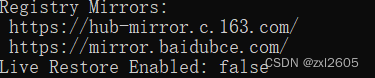

docker更换国内源

docker更换国内源 1、编辑Docker配置文件 在终端中执行以下命令,编辑Docker配置文件: vi /etc/docker/daemon.json2、添加更新源 在打开的配置文件中,添加以下内容: {"registry-mirrors": ["https://hub-mirror…...

使用Alpine配置WSL ssh门户

1. 哑铃图是什么? 哑铃图(Dumbbell Plot),有时也称为DNA图或杠铃图,是一种用于比较两个相关数据点的可视化图表。 它源于人们对更有效数据比较方式的持续探索。 在传统的时间序列比较中,我们通常使用两条折…...

NoSleep防休眠工具:系统唤醒与持续运行的高效解决方案

NoSleep防休眠工具:系统唤醒与持续运行的高效解决方案 【免费下载链接】NoSleep Lightweight Windows utility to prevent screen locking 项目地址: https://gitcode.com/gh_mirrors/nos/NoSleep 在数字化工作环境中,电脑意外休眠往往导致工作中…...

飞机上吸烟还叫嚣“憋得难受”?

坐飞机最怕遇到什么?不是延误,也不是颠簸,而是那种不拿一飞机人性命当回事的“巨婴”旅客。就在昨天(3月29日),四川航空一架从成都飞往尼泊尔加德满都的航班上,就出了这么一档子事儿。一位“老烟…...

AI辅助开发:利用快马构建openclaw强化学习抓取训练环境

最近在研究机械爪的抓取策略优化,发现手动调参效率太低,于是尝试用AI辅助开发来构建一个强化学习训练环境。这个项目主要围绕openclaw机械爪的启动和控制策略展开,通过快马平台的AI能力快速搭建实验环境,效果出乎意料地好。 环境搭…...

线段树优化建图

1. 概念 1.1.本质 本质就是用两颗线段树优化建图(节省空间) 1.2.作用 看标题可以知道 这东西其实就是一个辅助(优化)我们建图的东西 可以辅助(优化)我们干些什么: 点向区间连边区间向点连…...

新手必看:详解cursor注册手机号填写步骤与前端实现

新手必看:详解cursor注册手机号填写步骤与前端实现 最近在帮几个编程新手朋友解决cursor注册时遇到的手机号填写问题,发现很多细节容易被忽略。于是我用InsCode(快马)平台快速搭建了一个演示项目,把整个过程拆解成可视化的步骤,顺…...

肿瘤免疫微环境解析:8大免疫浸润工具实战指南

1. 肿瘤免疫微环境分析的核心价值 当你拿到一份肿瘤样本的转录组数据时,最令人兴奋的莫过于揭开它的免疫面纱——那些隐藏在肿瘤组织中的免疫细胞究竟在做什么?这就是免疫浸润分析的价值所在。想象一下,肿瘤组织就像一座复杂的城市࿰…...

基于python开发的送货上门系统

目录同行可拿货,招校园代理 ,本人源头供货商功能模块划分技术实现要点扩展功能建议部署与维护项目技术支持源码获取详细视频演示 :文章底部获取博主联系方式!同行可合作同行可拿货,招校园代理 ,本人源头供货商 功能模块划分 用户管理模块 用户注册与登录…...

Linux 调度器中的限流机制:throttled 标志的触发与解除

一、简介在实时系统和云计算环境中,资源隔离与公平分配是 Linux 内核调度的核心挑战。当多个任务共享 CPU 资源时,某些恶意或失控的任务可能耗尽全部 CPU 时间,导致关键任务饥饿(Starvation)。为此,Linux 内…...

Delayed Job测试策略完整指南:如何在开发和测试环境中高效测试异步任务

Delayed Job测试策略完整指南:如何在开发和测试环境中高效测试异步任务 【免费下载链接】delayed_job 项目地址: https://gitcode.com/gh_mirrors/de/delayed_job Delayed Job是Ruby on Rails生态系统中最受欢迎的异步任务处理库之一,它让开发者…...