Design Guidelines for 100 Gbps

文章目录

- Stratix V GT Transceiver Channels

- CFP2 Host Connector Assembly and Pinout

- Stratix V GT to CFP2 Interface Layout Design

- Board Stack Up Dimensions

- Example Design Channel Performance

- Simulation Results for Stratix V GT to CFP2 Connector Layout Design

Design Guidelines for 100 Gbps - CFP2 Interface

This document shows an example layout design that implements a 4 x 25/28 Gbps CFP2 module interface that meets the insertion and return loss mask requirements proposed in the working clause draft version 8.0 for CEI-28G-VSR.

The common electrical interface CEI-28G-VSR implementation architecture (IA) for short reach channels is intended for next generation 100 Gbps chip - to - optical module applications. CFP2 is a pluggable optical module that uses CEI-28G-VSR as its electrical interface (as defined by the CFP Multi-Source Agreement (MSA) member companies). CFP2 also defines the mechanical form factor for a 100 Gbps optical transceiver module targeted for Ethernet and OTN (Optical Transport Network) applications.

CFP2 provides an industry standard to develop next generation 100 G interfaces with lower power and greater port density compared to previous generation CFP optical modules.

Note: For more information, refer to the CEI-28G-VSR working clause specification. Document number OIF2010.404.08.

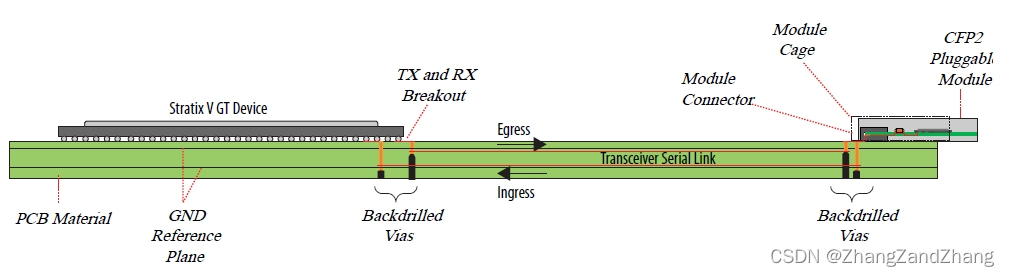

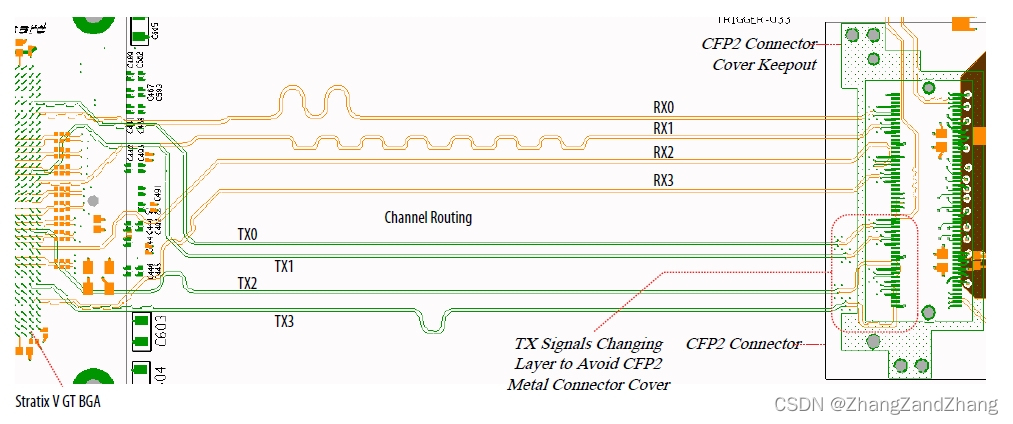

Figure 1: Stratix V GT Device to a CFP2 Pluggable Module Interface on a PCB

The channel layout on the PCB is optimized in order to meet the strict insertion and return loss masks defined by CEI-28G-VSR.

Refer to the following documents for more information on optimizing your board designs for high speed serial links.

Related Information

• AN529: Via Optimization Techniques for High-Speed Channel Designs

• AN530: Optimizing Impedance Discontinuity Caused by Surface Mount Pads for High-Speed Channel Designs

Stratix V GT Transceiver Channels

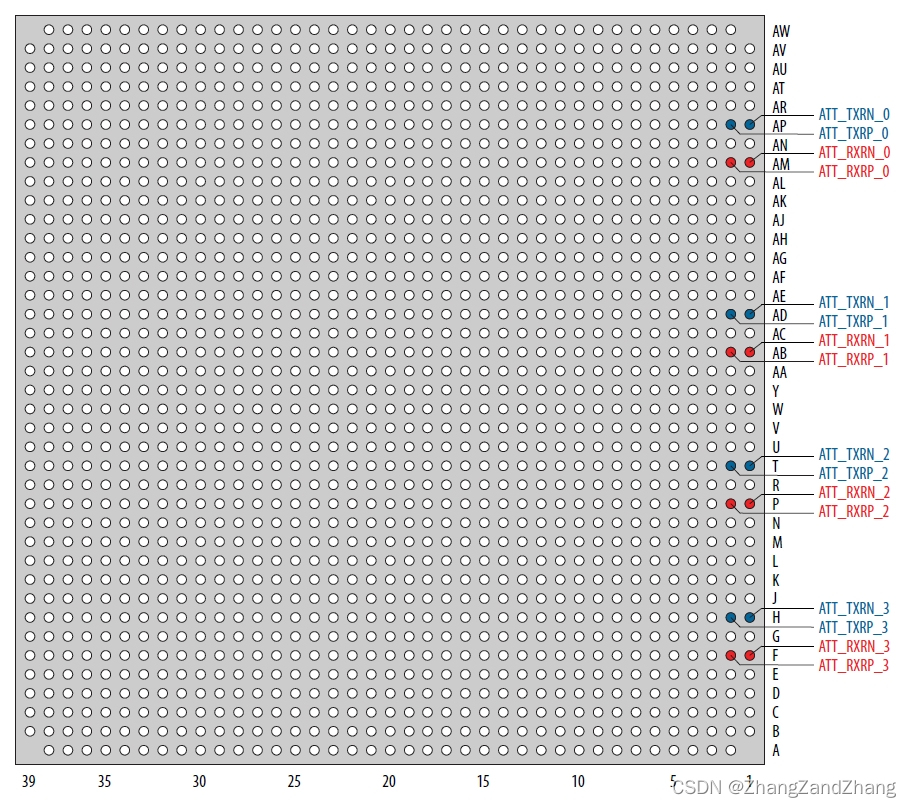

Stratix® V GT FPGAs offer four transceiver channels (ATT_TXR[3:0]_P/N and ATT_RXR[3:0]_P/N) that can operate up to 28 Gbps for interfacing with CFP2 or other optical modules.

Figure 2: Top View of 28 Gbps Transmitter and Receiver Channel Locations in Stratix V GT FPGAs

CFP2 Host Connector Assembly and Pinout

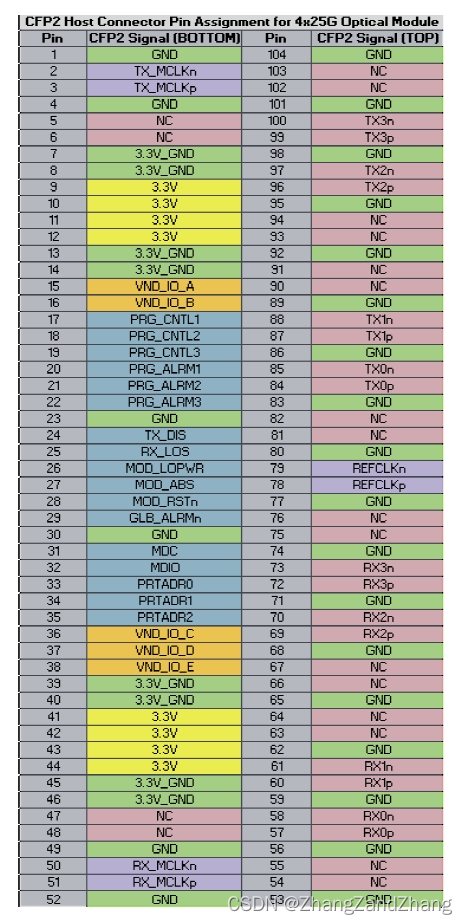

The CFP2 specification defines the mechanical connector requirements for the 104-pin CFP2 connector. The host connector assembly is composed of a female host connector, and a metal connector cover and cage for retention and electromagnetic shielding of the inserted CFP2 optical module.

Figure 3: CFP2 Host Connector Assembly for a 4x25G/28G Module Interface as Defined by the CFP2 Mechanical Specification

Note: This figure is courtesy of Yamaichi Electronics.

Figure 4: CFP2 Host Connector Pinout for 4x25G/28G Module Interface as Defined by the CFP2 Mechanical Specification

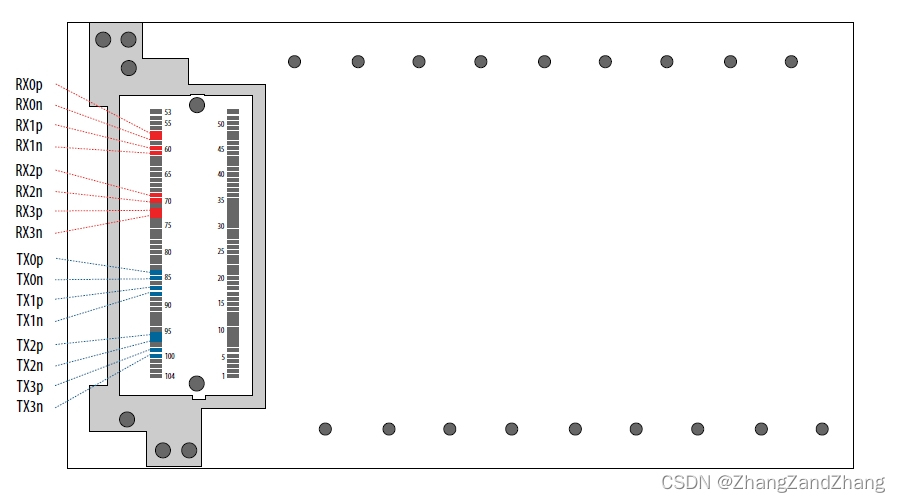

Figure 5: CFP2 Host Connector Layout Footprint

The high-speed transceiver pins are identified in the following figure to show their position within the connector. Blue pins are the TX transceiver channels and red pins are the RX transceiver channels.

Stratix V GT to CFP2 Interface Layout Design

The TX and RX channels are connected directly to the CFP2 connector with approximately 5.5 inches of differential trace routing on the top and bottom layer of the board. DC blocking capacitors are included in the optical module for both the TX and RX traces. Nominal trace impedance is controlled at approximately 100Ω differential and the board material used is Panasonic Megtron-6.

Figure 6: Stratix V GT to CFP2 Interface Layout Design Example

The figure shows an example layout design where the green traces are the TX channels routed on the top layer while the orange traces are the RX channels routed on the bottom layer.

In this example, vias are used for the RX channel breakout at the BGA, and for both the TX and RX channels at the CFP2 connector. To avoid the top layer keep out requirement of the CFP2 metal connector cover assembly, the TX channel routing is switched briefly to the bottom layer and then back to the top layer at the CFP2 connector as illustrated by the circled area in the above figure. Top to bottom routing is used to avoid via stubs.

The BGA pads, signal vias, and CFP2 trace to pad interfaces are large discontinuity sources in the channel. Ansys HFSS (High Frequency Structural Simulator) 3-D field solver simulation is used to optimize the BGA breakout and CFP2 interface design. The trace impedance is kept within ±10% of the nominal 100Ω

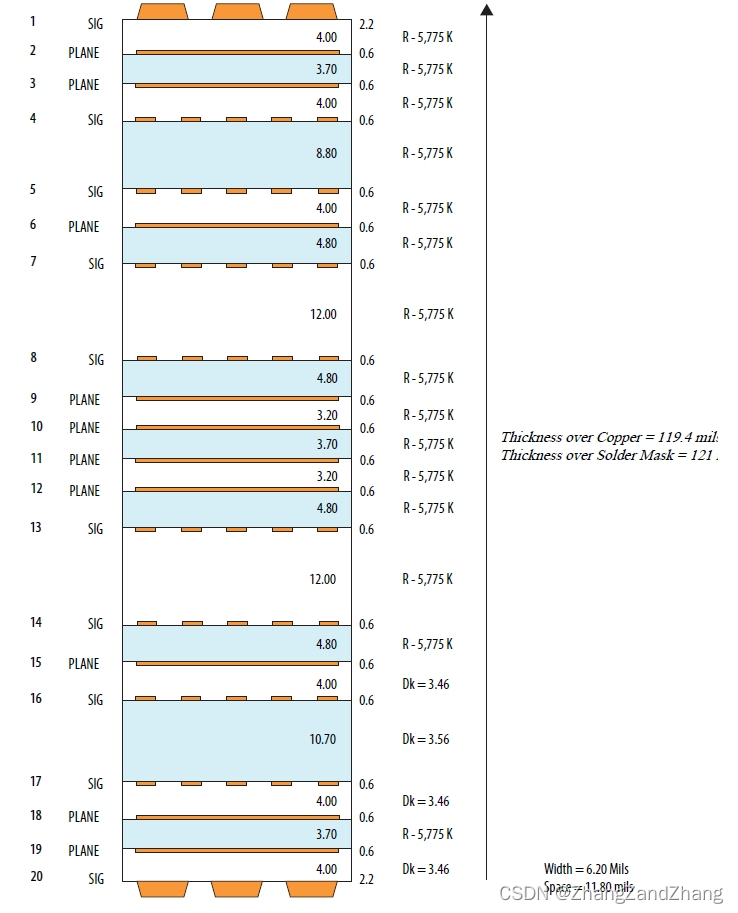

Board Stack Up Dimensions

The detailed trace design and board stack up dimensions are shown in the figure below.

Figure 7: Differential Trace Construction and Stack Up Details

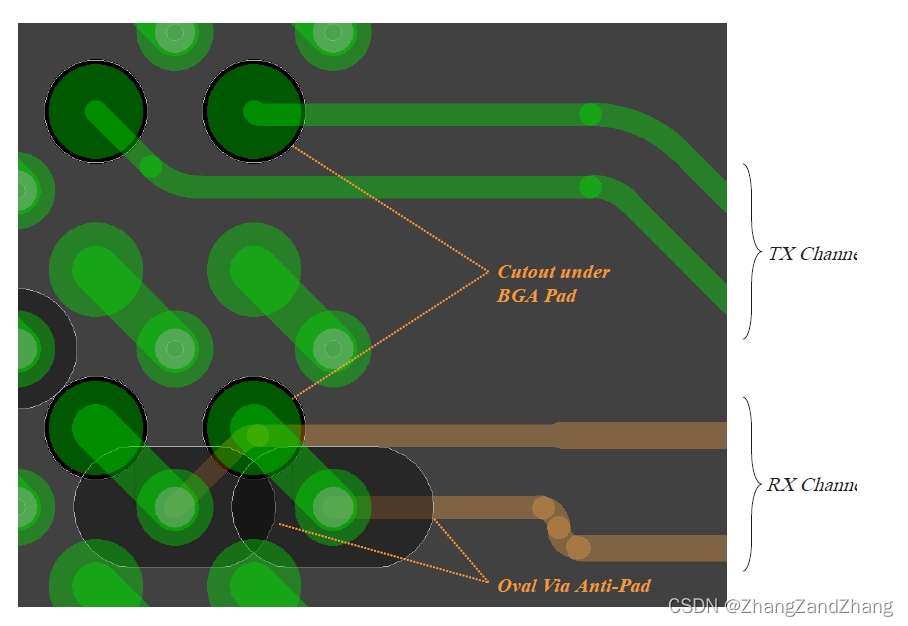

BGA Breakout Optimization

BGA breakout optimization targets both the BGA pads and dog bone vias. A cutout is provided in the reference plane under the BGA pad and large oval via anti-pads are used for better BGA pad and via impedance matching.

Figure 8: BGA Via Breakout Layout Optimization

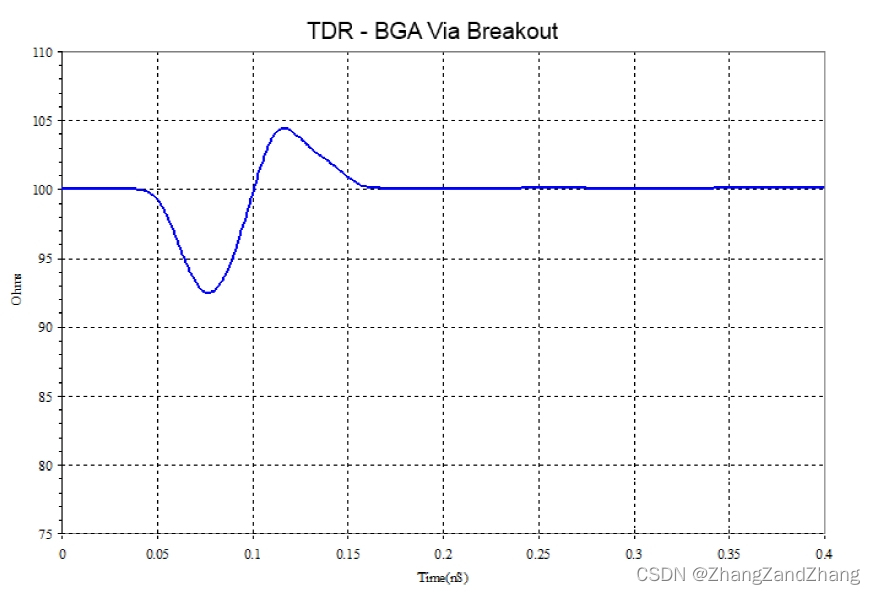

Figure 9: TDR of BGA Via Breakout

HFSS simulation results show that the TDR deviation of the BGA escape is maintained within ±10% of the nominal 100Ω channel target impedance.

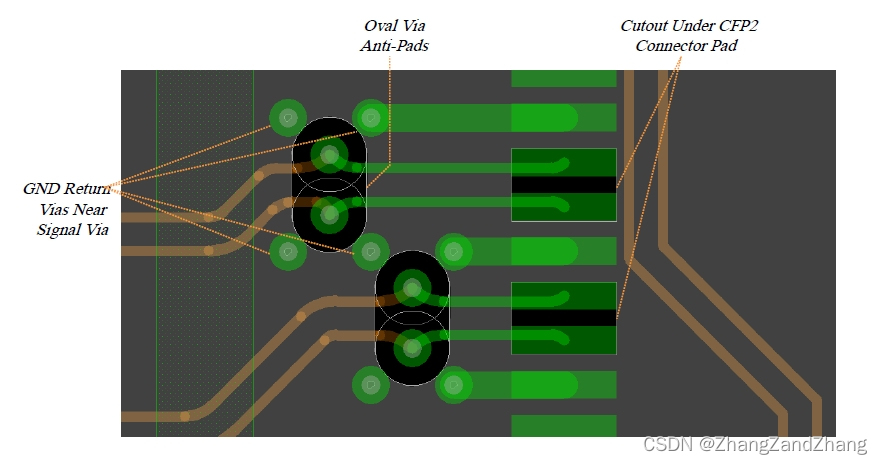

CFP2 Interface Optimization

The CFP2 host connector layout optimization reduces the impact of discontinuity at the differential pair to the CFP2 connector interface. A reference plane cutout is provided beneath the connector pads and larger oval anti-pads are used for the signal vias. Four nearby ground return vias are provided to help reduce the connector interface discontinuity.

Figure 10: CFP2 Connector Interface Layout Optimization

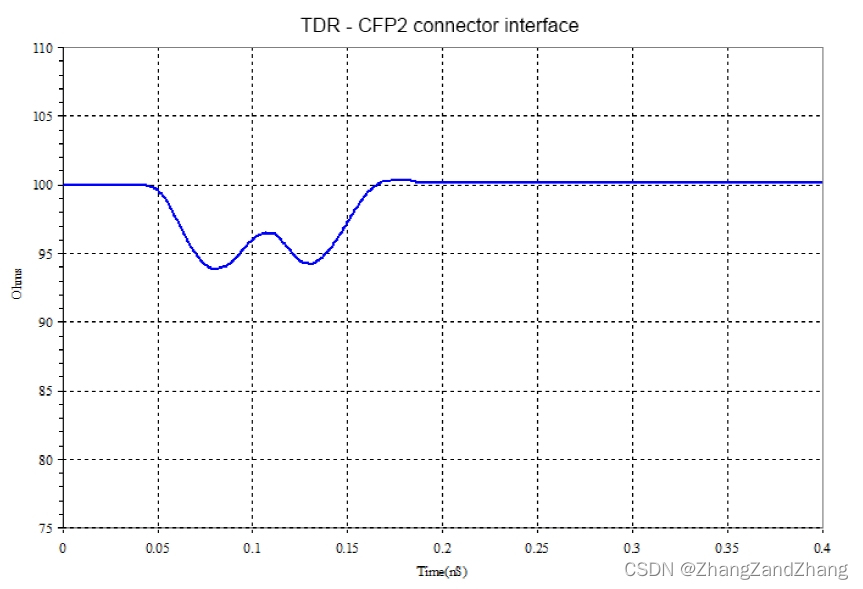

Figure 11: HFSS Simulated TDR of the CFP2 Connector interface

The following figure shows the HFSS simulated TDR results. With the layout optimizations, the TDR deviation due to the discontinuity caused by the via and connector pad is kept within ±10% of the nominal 100Ω target impedance.

Example Design Channel Performance

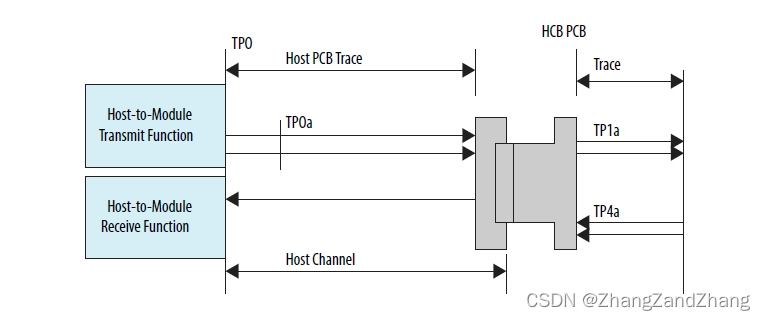

The CEI-28G-VSR working clause defines several mask requirements for the channel, including insertion loss, return loss, and differential-to-common mode conversion. Because it is difficult to verify electrical parameters of a full channel in a system, the working clause also defines a Host Compliance Board (HCB) with test points for verifying the host-to-module channel performance at various test points.

Figure 12: Host Compliance Board Measurement Points

For example, TP1a and TP4a define the measurement points and the associated mask requirements for the host-to-module electrical signal performance for insertion loss, return loss, and differential-to-common mode conversion. For more information about these definitions, refer to the CEI-28G-VSR working clause specification (document number OIF2010.404.08).

Simulation Results for Stratix V GT to CFP2 Connector Layout Design

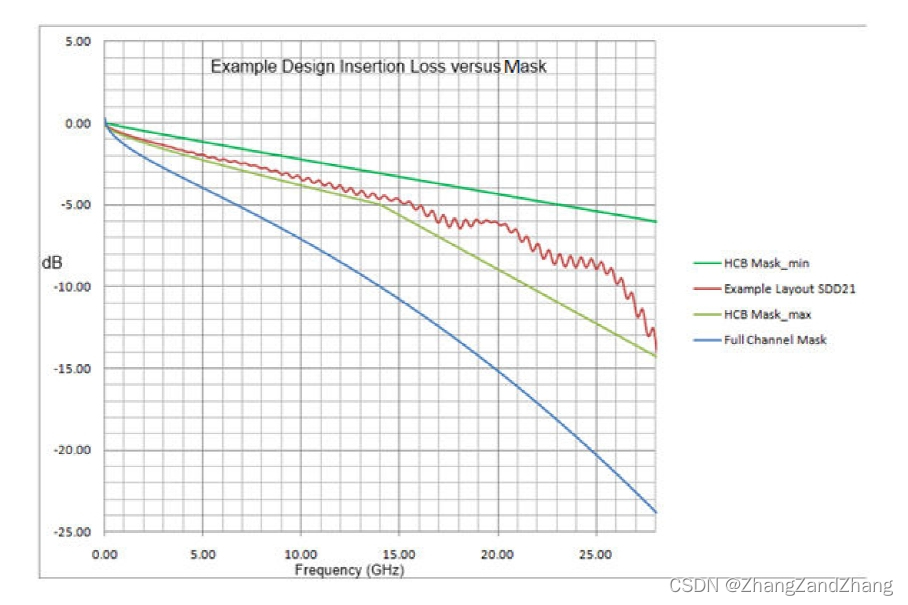

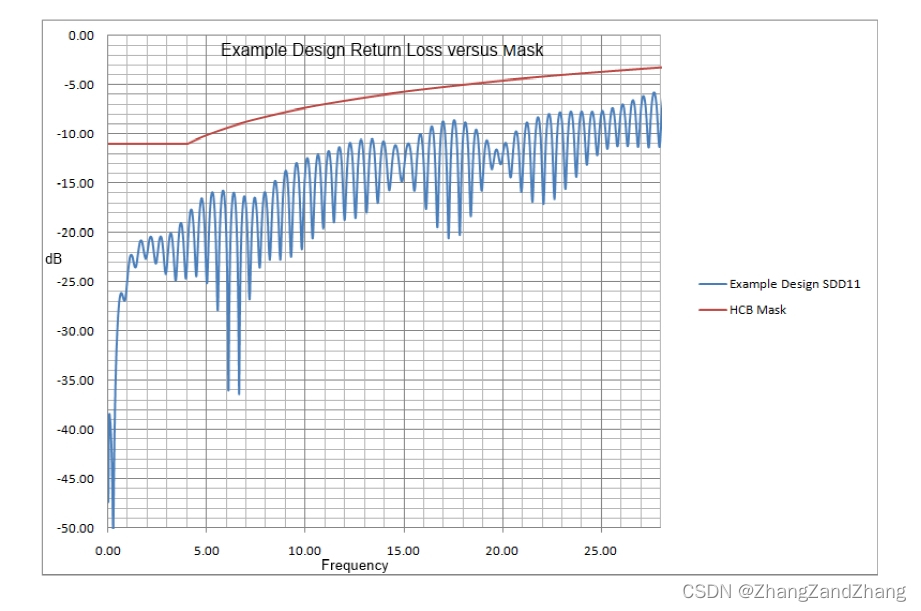

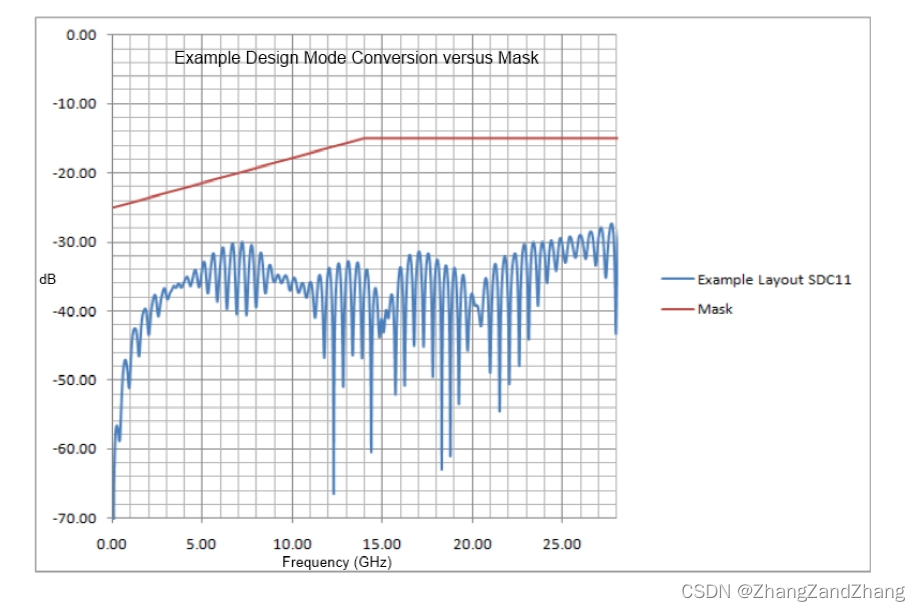

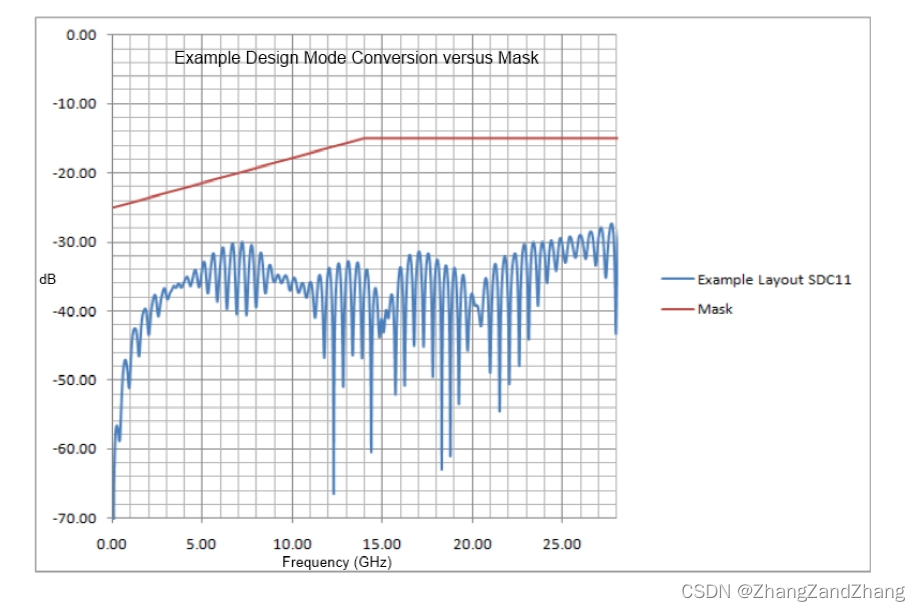

Ansys HFSS (High Frequency Structural Simulator) simulation results for the insertion loss (SDD21), return loss (SDD11) and differential-to-common mode conversion (SDC11) of the channel with the CFP2 connector included are shown in the following figures. The simulation models the HCB for validating the channel layout against the CEI-28G-VSR defined masks.

Figure 13: Insertion Loss versus CEI-28G-VSR Mask Requirements

The SDD21 resides within the HCB minimum and maximum insertion loss masks as defined by the CEI-28G-VSR specification. This insertion loss meets the complete VSR channel (host board + connector + optical module) mask requirement with ample margin to accommodate the additional loss of an inserted CFP2 optical module. Note that the complete channel with the optical module is not simulated.

Similarly, the figures below show that the return loss and differential-to-common mode conversion both meet their respective masks as defined by the CEI-28G-VSR requirement.

Figure 14: Return Loss versus CEI-28G-VSR Mask Requirements

Figure 15: Mode Conversion versus CEI-28G-VSR Mask Requirements

相关文章:

Design Guidelines for 100 Gbps

文章目录 Stratix V GT Transceiver ChannelsCFP2 Host Connector Assembly and PinoutStratix V GT to CFP2 Interface Layout DesignBoard Stack Up DimensionsExample Design Channel PerformanceSimulation Results for Stratix V GT to CFP2 Connector Layout Design Desi…...

苹果企业账号申请思考

苹果企业账号 好多年的企业账号想启用,但是没有找到入口,直接联系了一下苹果的技术支持。通过邮件联系,之后他们回电,吧啦吧啦问了一大堆关于企业账号的事情,他们对这个还挺关注的,主要是集中在是否是有必…...

【C/C++】素数专题

素数专题 1.判断素数模板2.求范围内的素数(101-200)3.判断素数与分解 1.判断素数模板 #include<stdio.h> #include<math.h>int prism(int n){if(n1) return 0;for(int i2;i<sqrt(n);i){if(n%i0) return 0;}return 1; }int main() {int n…...

Apple Vision Pro 开发机申请

申请地址: (免费租用形式) Developer Kit - visionOS - Apple Developer 上海Apple Lab 互动申请: View - Meet with Apple Experts - Apple Developer (需要完善的产品才能去测试哦) 它是如何工作的 我们将借给你一个Apple Vision Pro开发…...

NFS服务器搭建 配置nfs共享目录

一定要用二级目录,否则NFS坏了主机都启动不起来 一级目录是强制挂载,二级目录是动态挂载 nfs共享远程目录具体步骤: 服务器端配置: 1.安装NFS服务器软件 sudo apt-get install nfs-kernel-server # 安装 NFS服务器端 2.添加…...

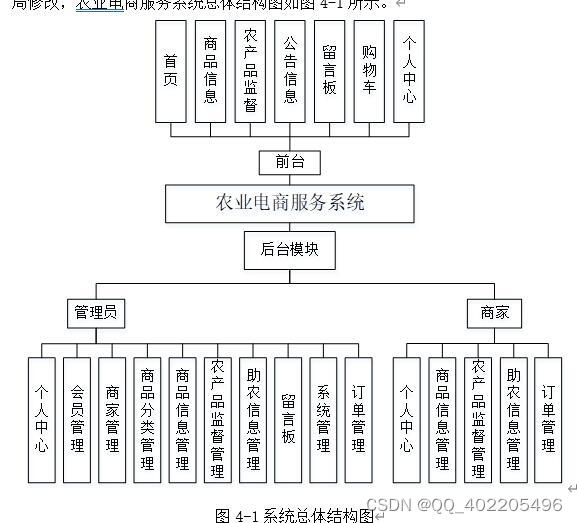

springboot+bootstrap+java农业电商服务商城系统_30249

本农业电商服务系统是为了提高用户查阅信息的效率和管理人员管理信息的工作效率,可以快速存储大量数据,还有信息检索功能,这大大的满足了管理员、会员和商家这三者的需求。操作简单易懂,合理分析各个模块的功能,尽可能…...

【shell】脚本实现将开发机user1账户下的abc文件夹复制到user2~4账户下

1 主要内容 可以使用Shell脚本来实现将开发机(Linux)上user1账户下的abc文件夹复制到user2、user3和user4账户下。 #!/bin/bash# 数组赋值,目标用户列表 # target_users(user2 user3 user4) # 定义数组 target_users()# 生成user数字的数组…...

steamui.dll找不到指定模块,要怎么修复steamui.dll文件

当我们使用Steam进行游戏时,有时可能会面对一些令人无奈的技术问题。一种常见的问题是“找不到指定模块steamui.dll”,这可能是由于缺少文件、文件损坏或软件冲突等原因导致。但别担心,这篇文章将提供几种解决此问题的方法,并针对…...

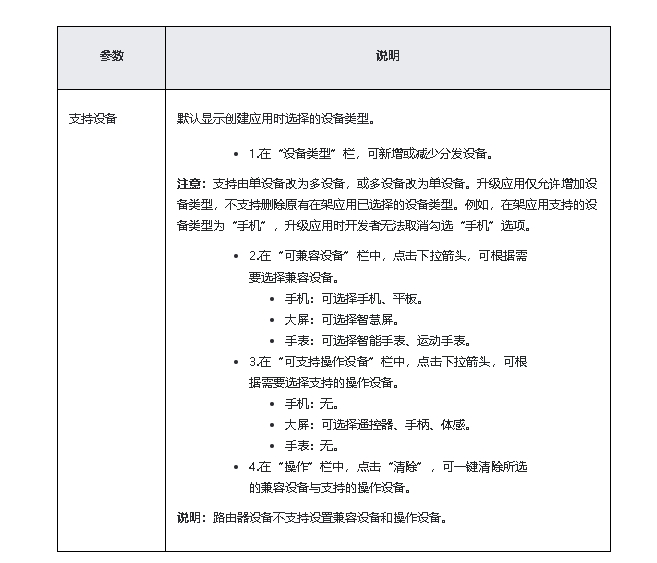

鸿蒙原生应用/元服务开发-AGC分发如何上架HarmonyOS应用

一、上架整体流程 二、上架HarmonyOS应用 获取到HarmonyOS应用软件包后,开发者可将应用提交至AGC申请上架。上架成功后,用户即可在华为应用市场搜索获取开发者的HarmonyOS应用。 配置应用信息 1.登录AppGallery Connect,选择“我的应用”。…...

基于单片机仓库温湿度监测报警系统仿真设计

**单片机设计介绍,基于单片机仓库温湿度监测报警系统仿真设计 文章目录 一 概要二、功能设计设计思路 三、 软件设计原理图 五、 程序六、 文章目录 一 概要 基于单片机的仓库温湿度监测报警系统可以被设计成能够实时监测仓库内的温度和湿度,并根据预设…...

中文rlhf数据集50w条数据解析

中文rlhf数据集50w条数据解析 解析代码数据名代码解析 解析代码 import jieba from tqdm import tqdm import re import pandas as pd import numpy as npdef find_non_english_text(text):pattern re.compile(r[^a-zA-Z])return pattern.sub(, text)def find_chinese_text(t…...

:UnicodeDecodeError: ‘gbk‘ codec can‘t decode byte xxx)

解决解析PDF编码报错(以pdfminer为例):UnicodeDecodeError: ‘gbk‘ codec can‘t decode byte xxx

解决方法 博主使用的是pdfminer解析PDF文档,这个解决方法是通用的,只需要使PDFParser传入的文件为二进制文件即可,示例程序: from pdfminer.pdfparser import PDFParserpdf_parser PDFParser(open("pdf文件.pdf", &q…...

)

chatGPT2:如何构建一个可以回答有关您网站问题的 AI 嵌入(embeddings)

感觉这个目前没有什么用,因为客户可以直接问通用chatGPT,实时了解你网站内的信息,除非你的网站chatGPT无法访问。 不过自动预订、买票等用嵌入还是挺有用的。 什么是嵌入? OpenAI的嵌入(embeddings)是一种…...

Vue3-新特性defineOptions和defineModel

defineOptions 问题:用了<script setup>后,就无法添加与其平级的属性了,比如定义组件的name或其他自定义的属性。 为了解决这一问题,引入了defineProps与defineEmits这两个宏,但这只解决了props与emits这两个属…...

【计算机基础】通过插件plantuml,实现在VScode里面绘制状态机

📢:如果你也对机器人、人工智能感兴趣,看来我们志同道合✨ 📢:不妨浏览一下我的博客主页【https://blog.csdn.net/weixin_51244852】 📢:文章若有幸对你有帮助,可点赞 👍…...

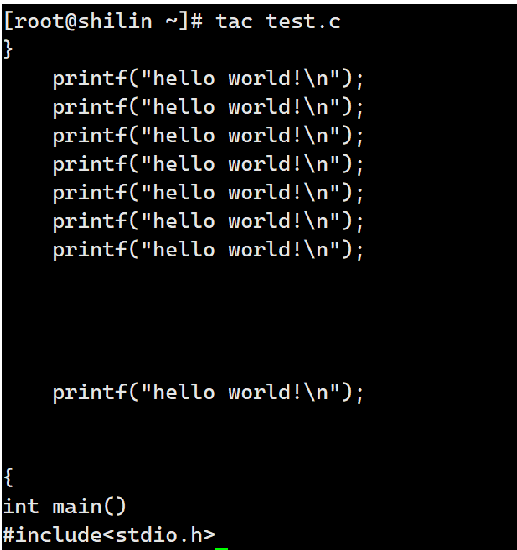

Linux常用基础命令及重要目录,配置文件功能介绍

目录 一,Linux常用必备基础命令 1,网络类命令 2,文件目录类命令 3,操作类命令 4,关机重启命令 5,帮助命令 6,查看显示类命令 7,命令常用快捷键 二,Linux重要目录…...

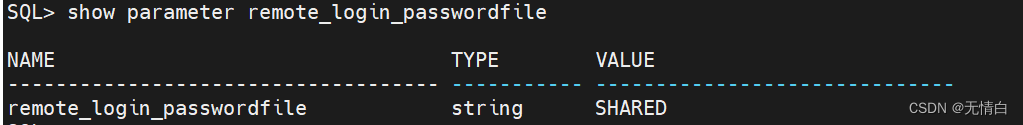

Oracle登录认证方式详解

文章目录 一、简介二、OS认证三、口令认证四、remote_login_passwordfile 详解 一、简介 在数据库管理中,登录认证是确保数据库安全性的重要环节。Oracle数据库提供 了两种认证方式,一种是“操作系统认证”,一种是“口令文件认证,…...

ate测试原理及ate测试系统(软件)知识科普 -纳米软件

ATE(Automatic Test Equipment)测试也叫自动化测试,通过计算机控制测试仪器对被测对象进行测试。以计算机编程代替人工测试,基于测试程序控制仪器并对待测品进行输入和输出信号检测分析,从而判断待测品的性能是否符合要求。 ATE测试需要根据测…...

Linux | 创建 | 删除 | 查看 | 基本命名详解

Linux | 创建 | 删除 | 查看 | 基本命名详解 文章目录 Linux | 创建 | 删除 | 查看 | 基本命名详解前言一、安装Linux1.1 方法一:云服务器方式1.2 方法二:虚拟机方式 二、ls2.2 ll 三、which3.1 ls -ld 四、pwd五、cd5.1 cd .\.5.2 ls -al5.3 重新认识命…...

搭配:基于OpenCV的边缘检测实战

引言 计算机中的目标检测与人类识别物体的方式相似。作为人类,我们可以分辨出狗的形象,因为狗的特征是独特的。尾巴、形状、鼻子、舌头等特征综合在一起,帮助我们把狗和牛区分开来。 同样,计算机能够通过检测与估计物体的结构和性…...

多站点多元时间序列预测基线方法开发与实践

1. 多站点多元空气污染时间序列预测的基线方法开发在真实世界的时间序列预测任务中,我们常常面临多重挑战:多输入变量、多步预测需求,以及跨多个物理站点的同步预测要求。EMC数据科学全球黑客马拉松提供的"空气质量预测"数据集正是…...

CL2307OL CL2315OL带输入保护功能的原边控制恒压/恒流 PWM 驱动器

概述 CL23XX是一款适用于低功率AC / DC充电器和适配器应用的高性能PWM电源开关控制器,它可在初级侧进行检测和调节,集高精度恒定电压(CV)和恒定电流(CC)控制于一体,省去了光电耦合器和431比较器…...

SpringBoot+Vue出租车服务管理系统源码+论文

代码可以查看文章末尾⬇️联系方式获取,记得注明来意哦~🌹 分享万套开题报告任务书答辩PPT模板 作者完整代码目录供你选择: 《SpringBoot网站项目》1800套 《SSM网站项目》1500套 《小程序项目》1600套 《APP项目》1500套 《Python网站项目》…...

2026年餐饮外卖小程序选型:从成本、功能到避坑,5家平台全解析

2026年餐饮外卖小程序选型:从成本、功能到避坑,5家平台全解析 在移动互联网全面渗透餐饮行业的今天,小程序已成为餐饮商家不可或缺的线上经营阵地。从堂食到外卖,从到店自提到私域流量沉淀,一款功能完备、稳定可靠的外…...

Keras图像增强技术实战:提升计算机视觉模型性能

1. 项目概述:为什么需要图像增强?在计算机视觉任务中,数据永远是王道。但现实情况是,我们往往难以获取足够数量和多样性的标注图像数据。想象一下你要训练一个猫狗分类器,但手头只有100张正面拍摄的宠物照片——这样的…...

)

Conda创建环境卡在‘Solving environment: failed’?别慌,试试这3种镜像源配置方法(附.condarc文件详解)

Conda环境创建卡在Solving environment: failed的深度解决方案与镜像源配置指南 当你在使用Conda创建Python环境时遇到Solving environment: failed错误,这通常意味着Conda无法解析和满足你指定的依赖关系。这个问题在配置不当或网络连接不稳定的情况下尤为常见。本…...

告别无效修改!2026年最聪明的降AI率工具盘点,精准降低AI率

今天,我们就来盘点几款在2026年备受关注的降AI率工具。它们不单是简单的改写,而是更能从思维逻辑、语言习惯和内容特质入手,帮助你将AI生成内容转化为富有个人特色的自然内容,让你告别无效修改。第一款:智媒ai降ai率工…...

别再搞混了!C++里printf和setprecision控制小数位,到底有啥区别?

别再搞混了!C里printf和setprecision控制小数位,到底有啥区别? 在财务系统开发中,一个工程师因为混淆了printf和setprecision的精度控制逻辑,导致公司报表出现数百万的误差。这个真实案例揭示了C数值格式化中一个关键但…...

深度学习训练中学习率设置与优化策略详解

1. 学习率在深度学习中的核心作用 第一次接触神经网络训练时,我犯过所有新手都会犯的错误——把学习率设成0.1然后眼睁睁看着损失值爆炸。这个看似简单的超参数实际上是模型训练中最关键的调控旋钮,它决定了每次参数更新的步长幅度。就像用显微镜调焦时&…...

)

别再手动挖洞了!用Acunetix 13.0自动化扫描你的Pikachu靶场(附详细配置与报告解读)

从零构建自动化Web安全测试体系:Acunetix与Pikachu靶场深度实践 当你在本地搭建好Pikachu靶场,看着那些精心设计的漏洞页面时,是否曾陷入这样的困境:手动点击每个输入框测试XSS、反复修改URL参数尝试SQL注入、用Burp Suite截获请求…...