北邮22级信通院数电:Verilog-FPGA(11)第十一周实验(2)设计一个24秒倒计时器

北邮22信通一枚~

跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章

持续关注作者 迎接数电实验学习~

获取更多文章,请访问专栏:

北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客

目录

一.代码部分

1.1 counter_24.v

1.2 divide.v

1.3 debounce.v

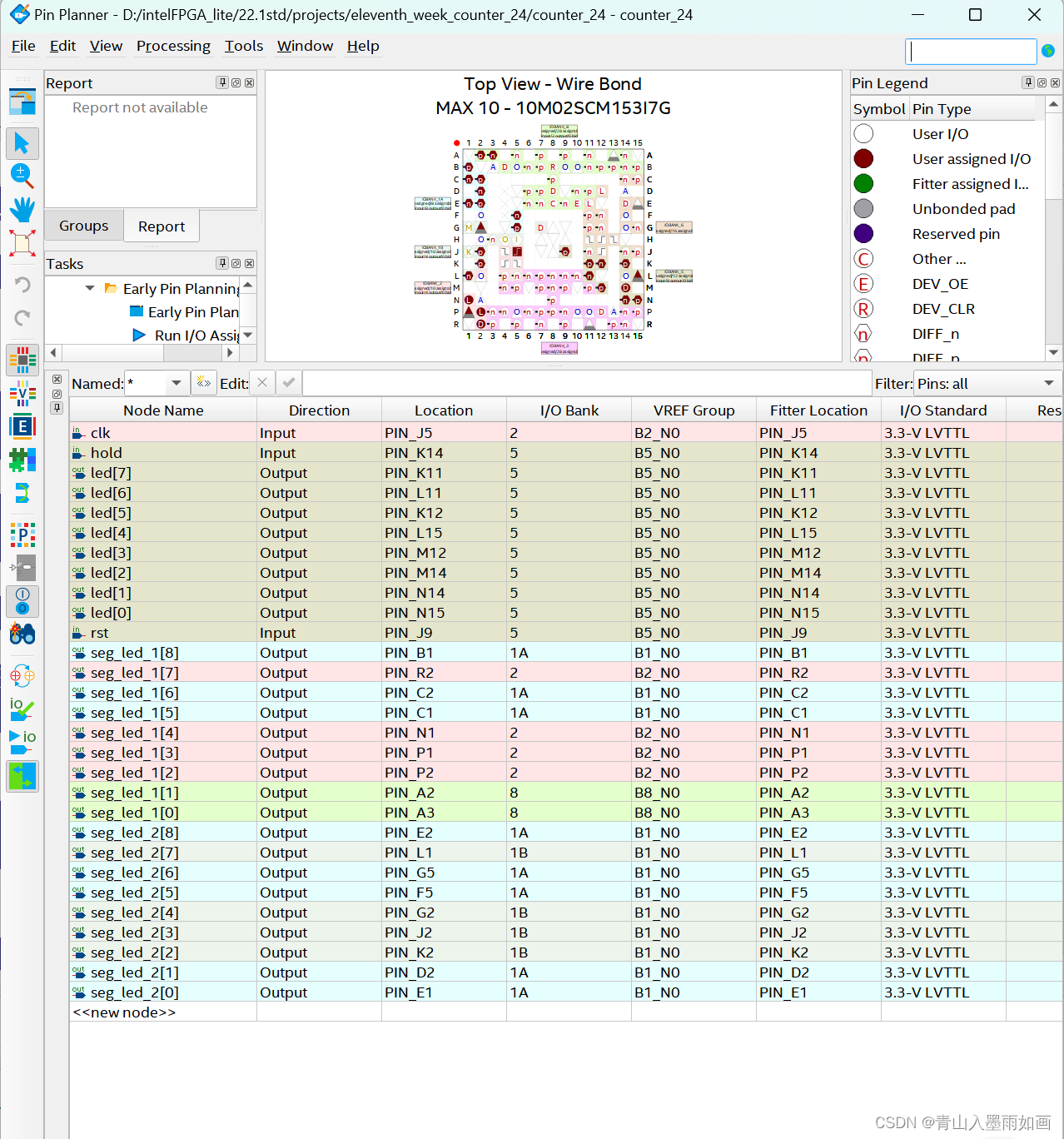

二.管脚分配

三.实验效果

一.代码部分

1.1 counter_24.v

module counter_24

(input clk,rst,hold,output [8:0] seg_led_1,output [8:0] seg_led_2,output reg [7:0] led

);wire clk_lh;wire hold_pulse;reg hold_flag;reg back_to_zero_flag;reg [6:0] seg [16:0];reg [3:0] cnt_ge;reg [3:0] cnt_shi;initialbegin seg[0] = 7'h3f;seg[1] = 7'h06;seg[2] = 7'h5b;seg[3] = 7'h4f;seg[4] = 7'h66;seg[5] = 7'h6d;seg[6] = 7'h7d;seg[7] = 7'h07;seg[8] = 7'h7f;seg[9] = 7'h6f;seg[10] = 7'hf7;seg[11] = 7'h7c;seg[12] = 7'h39;seg[13] = 7'h5e;seg[14] = 7'h79;seg[15] = 7'h71;enddebounce debounce_1(.clk(clk),.rst(rst),.key(hold),.key_pulse(hold_pulse));divide # (.WIDTH(32),.N(12000000)) divide_1(.clk(clk),.rst_n(rst),.clkout(clk_lh));always @ (posedge hold_pulse)if(!rst==1)hold_flag <= 0;else hold_flag <= ~hold_flag;always @ (*)if(!rst==1)back_to_zero_flag <= 0;else if( cnt_shi==0 && cnt_ge==0)back_to_zero_flag <= 1;else back_to_zero_flag <= 0;always @ (posedge clk_lh or negedge rst)begin if(!rst==1)begin cnt_ge <= 4'd4;cnt_shi <=4'd2;endelse if(hold_flag==1)begin cnt_ge <= cnt_ge;cnt_shi <= cnt_shi;endelse if(cnt_shi==0 && cnt_ge==0)begin cnt_shi <= cnt_shi;cnt_ge <=cnt_ge;endelse if(cnt_ge==0)begin cnt_ge <=4'd9;cnt_shi <= cnt_shi-1;endelse begin cnt_ge <= cnt_ge-1; endend//计时完成点亮ledalways @ (back_to_zero_flag)begin if(back_to_zero_flag == 1)led = 8'b0;elseled = 8'b1111_1111;endassign seg_led_1[8:0] = {2'b00,seg[cnt_ge]};assign seg_led_2[8:0] = {2'b00,seg[cnt_shi]};endmodule1.2 divide.v

module divide ( clk,rst_n,clkout);input clk,rst_n; //输入信号,其中clk连接到FPGA的C1脚,频率为12MHzoutput clkout; //输出信号,可以连接到LED观察分频的时钟//parameter是verilog里常数语句parameter WIDTH = 3; //计数器的位数,计数的最大值为 2**WIDTH-1parameter N = 5; //分频系数,请确保 N < 2**WIDTH-1,否则计数会溢出reg [WIDTH-1:0] cnt_p,cnt_n; //cnt_p为上升沿触发时的计数器,cnt_n为下降沿触发时的计数器reg clk_p,clk_n; //clk_p为上升沿触发时分频时钟,clk_n为下降沿触发时分频时钟//上升沿触发时计数器的控制always @ (posedge clk or negedge rst_n ) //posedge和negedge是verilog表示信号上升沿和下降沿//当clk上升沿来临或者rst_n变低的时候执行一次always里的语句beginif(!rst_n)cnt_p<=0;else if (cnt_p==(N-1))cnt_p<=0;else cnt_p<=cnt_p+1; //计数器一直计数,当计数到N-1的时候清零,这是一个模N的计数器end//上升沿触发的分频时钟输出,如果N为奇数得到的时钟占空比不是50%;如果N为偶数得到的时钟占空比为50%always @ (posedge clk or negedge rst_n)beginif(!rst_n)clk_p<=0;else if (cnt_p<(N>>1)) //N>>1表示右移一位,相当于除以2去掉余数clk_p<=0;else clk_p<=1; //得到的分频时钟正周期比负周期多一个clk时钟end//下降沿触发时计数器的控制 always @ (negedge clk or negedge rst_n)beginif(!rst_n)cnt_n<=0;else if (cnt_n==(N-1))cnt_n<=0;else cnt_n<=cnt_n+1;end//下降沿触发的分频时钟输出,和clk_p相差半个时钟always @ (negedge clk)beginif(!rst_n)clk_n<=0;else if (cnt_n<(N>>1)) clk_n<=0;else clk_n<=1; //得到的分频时钟正周期比负周期多一个clk时钟endassign clkout = (N==1)?clk:(N[0])?(clk_p&clk_n):clk_p; //条件判断表达式//当N=1时,直接输出clk//当N为偶数也就是N的最低位为0,N(0)=0,输出clk_p//当N为奇数也就是N最低位为1,N(0)=1,输出clk_p&clk_n。正周期多所以是相与

endmodule 1.3 debounce.v

module debounce (clk,rst,key,key_pulse);parameter N = 1; //要消除的按键的数量input clk;input rst;input [N-1:0] key; //输入的按键 output [N-1:0] key_pulse; //按键动作产生的脉冲 reg [N-1:0] key_rst_pre; //定义一个寄存器型变量存储上一个触发时的按键值reg [N-1:0] key_rst; //定义一个寄存器变量储存储当前时刻触发的按键值wire [N-1:0] key_edge; //检测到按键由高到低变化是产生一个高脉冲//利用非阻塞赋值特点,将两个时钟触发时按键状态存储在两个寄存器变量中always @(posedge clk or negedge rst)beginif (!rst) beginkey_rst <= {N{1'b1}}; //初始化时给key_rst赋值全为1,{}中表示N个1key_rst_pre <= {N{1'b1}};endelse beginkey_rst <= key; //第一个时钟上升沿触发之后key的值赋给key_rst,//同时key_rst的值赋给key_rst_prekey_rst_pre <= key_rst; //非阻塞赋值。//相当于经过两个时钟触发,//key_rst存储的是当前时刻key的值,//key_rst_pre存储的是前一个时钟的key的值end endassign key_edge = key_rst_pre & (~key_rst);//脉冲边沿检测。//当key检测到下降沿时,//key_edge产生一个时钟周期的高电平reg [17:0] cnt; //产生延时所用的计数器,系统时钟12MHz,//要延时20ms左右时间,至少需要18位计数器 //产生20ms延时,当检测到key_edge有效是计数器清零开始计数always @(posedge clk or negedge rst)beginif(!rst)cnt <= 18'h0;else if(key_edge)cnt <= 18'h0;elsecnt <= cnt + 1'h1;end reg [N-1:0] key_sec_pre; //延时后检测电平寄存器变量reg [N-1:0] key_sec; //延时后检测key,如果按键状态变低产生一个时钟的高脉冲。如果按键状态是高的话说明按键无效always @(posedge clk or negedge rst)beginif (!rst) key_sec <= {N{1'b1}}; else if (cnt==18'h3ffff)key_sec <= key; endalways @(posedge clk or negedge rst)beginif (!rst)key_sec_pre <= {N{1'b1}};else key_sec_pre <= key_sec; end assign key_pulse = key_sec_pre & (~key_sec); endmodule二.管脚分配

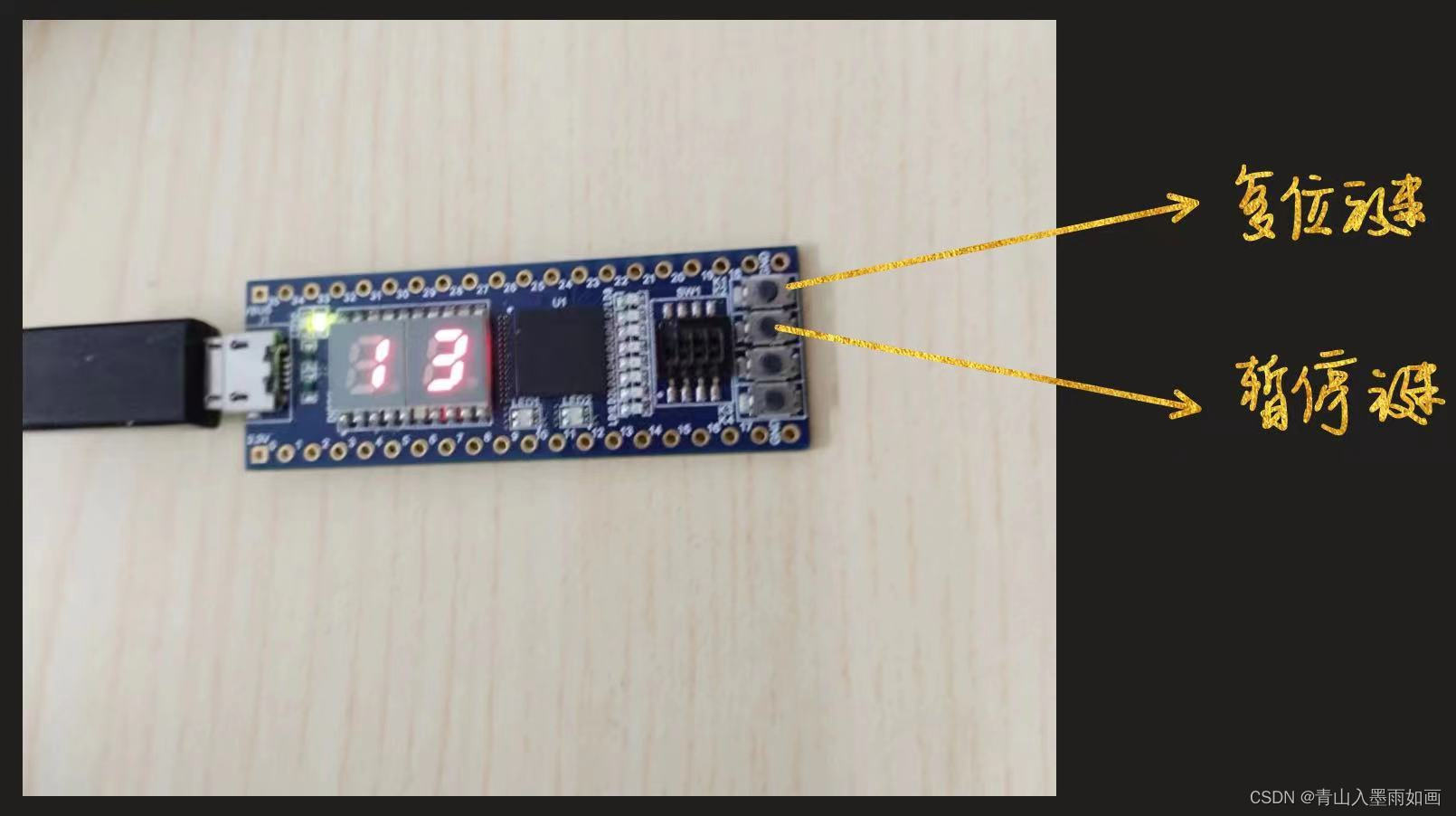

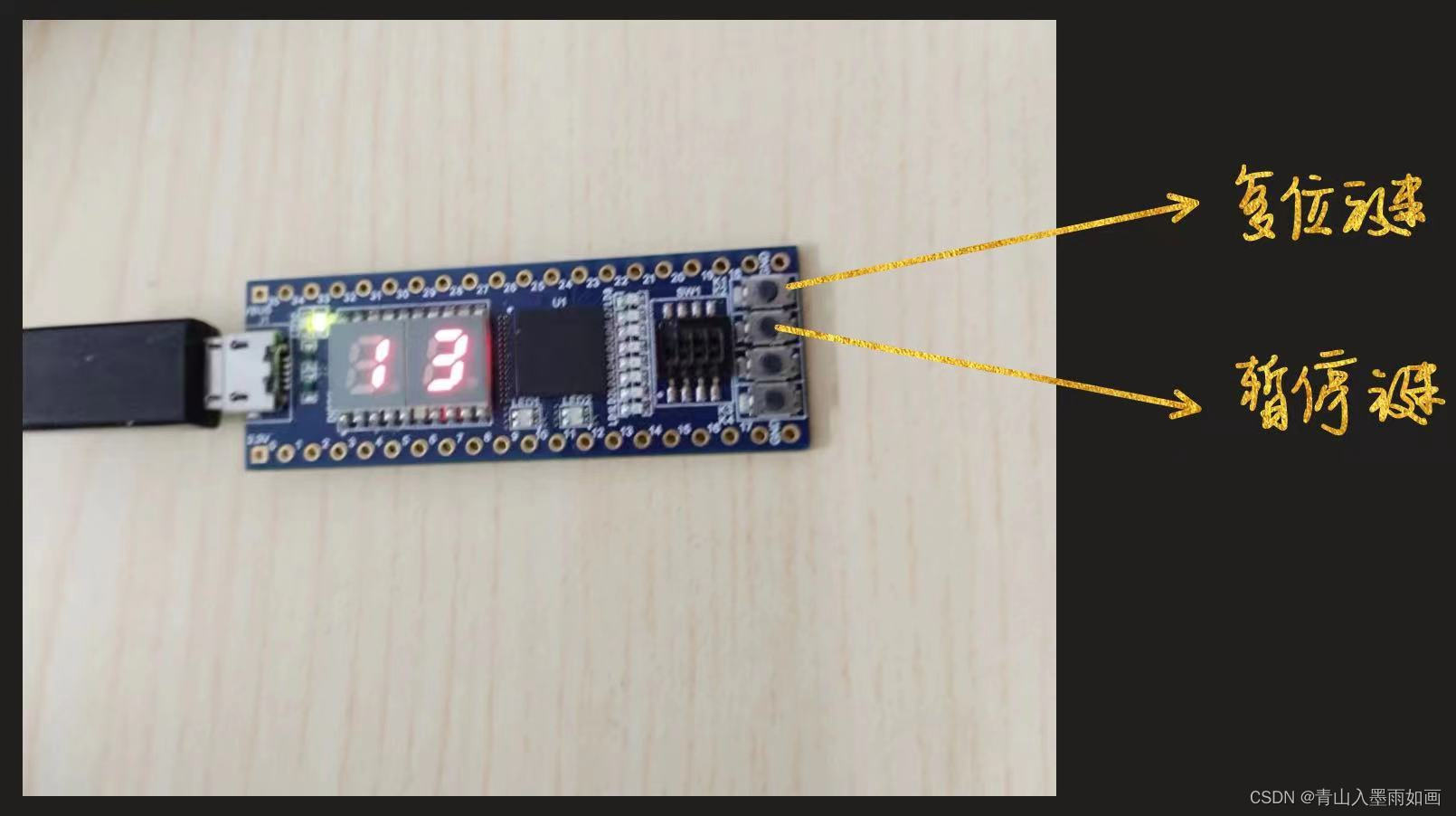

三.实验效果

数码管显示24秒倒计时,倒计时结束后所有LED灯亮起。

相关文章:

北邮22级信通院数电:Verilog-FPGA(11)第十一周实验(2)设计一个24秒倒计时器

北邮22信通一枚~ 跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章 持续关注作者 迎接数电实验学习~ 获取更多文章,请访问专栏: 北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客 目录 一.代码部分 1.1 counter_24.v 1.2 divid…...

什么是单元测试?

什么是单元测试 单元测试是软件开发中的一种测试方法,旨在验证各个软件组件或模块的功能正确性。在敏捷开发环境中,单元测试尤为重要,因为它有助于确保代码的质量和稳定性。下面是一些关于单元测试的关键点: 定义:单元…...

人口统计)

PTA-6-51(处理数组、字符串) 人口统计

题目: 本题运行时要求键盘输入10个人员的信息(每一个人信息包括:姓名,性别,年龄,民族),要求同学实现一个函数,统计民族是“汉族”的人数。 函数接口定义: pu…...

php中使用cdn

在 PHP 中使用 CDN 的一般流程如下: 1. 选择合适的 CDN 服务提供商:根据需求和预算选择合适的 CDN 服务提供商,例如阿里云CDN、腾讯云 CDN、Cloudflare 等。 2. 注册并配置 CDN 服务:在 CDN 服务提供商的网站上注册账号…...

docker部署MySQL5.7设置密码和远程访问的方法

运行MySQL docker run -p 3306:3306 --name mysql57 -v /root/mysql/log:/var/log/mysql -v /root/mysql/data:/var/lib/mysql -v /root/mysql/conf:/etc/mysql/conf.d -e MYSQL_ROOT_PASSWORDD7txumqc2b! -d mysql:5.7 --character-set-serverutf8mb4 --collation-serverutf8…...

Vue组件基础

Vue组件基础是DOMDOMjs前端组成下的页面布局区域划分,每个组件展示时都要在页面上有一定的大小。每个设定好的页面区域都可以定义Vue的组件,组件中包含了HTML模板、样式、Vue组件对象的定义。Vue的组件是包含页面设计在内的,是一种为页面某个…...

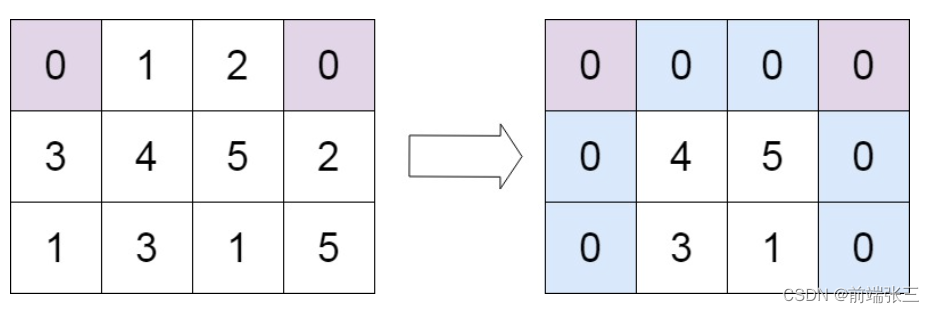

Javascript每天一道算法题(十八)——矩阵置零-中等

文章目录 1、问题2、示例3、解决方法(1)方法1——标记数组 1、问题 给定一个 y x x 的矩阵,如果一个元素为 0 ,则将其所在行和列的所有元素都设为 0 。请使用 原地 算法。 2、示例 示例 1: 输入:matrix [[…...

基于ROS开发的开源项目

基于ROS (Robot Operating System) 开发的开源项目很多,其中一些已经在机器人领域内非常知名。以下是一些比较著名的例子: Autoware: Autoware 是一个开源的自动驾驶车辆的软件栈,提供了从3D地图表示、环境感知(如障碍物、行人检测…...

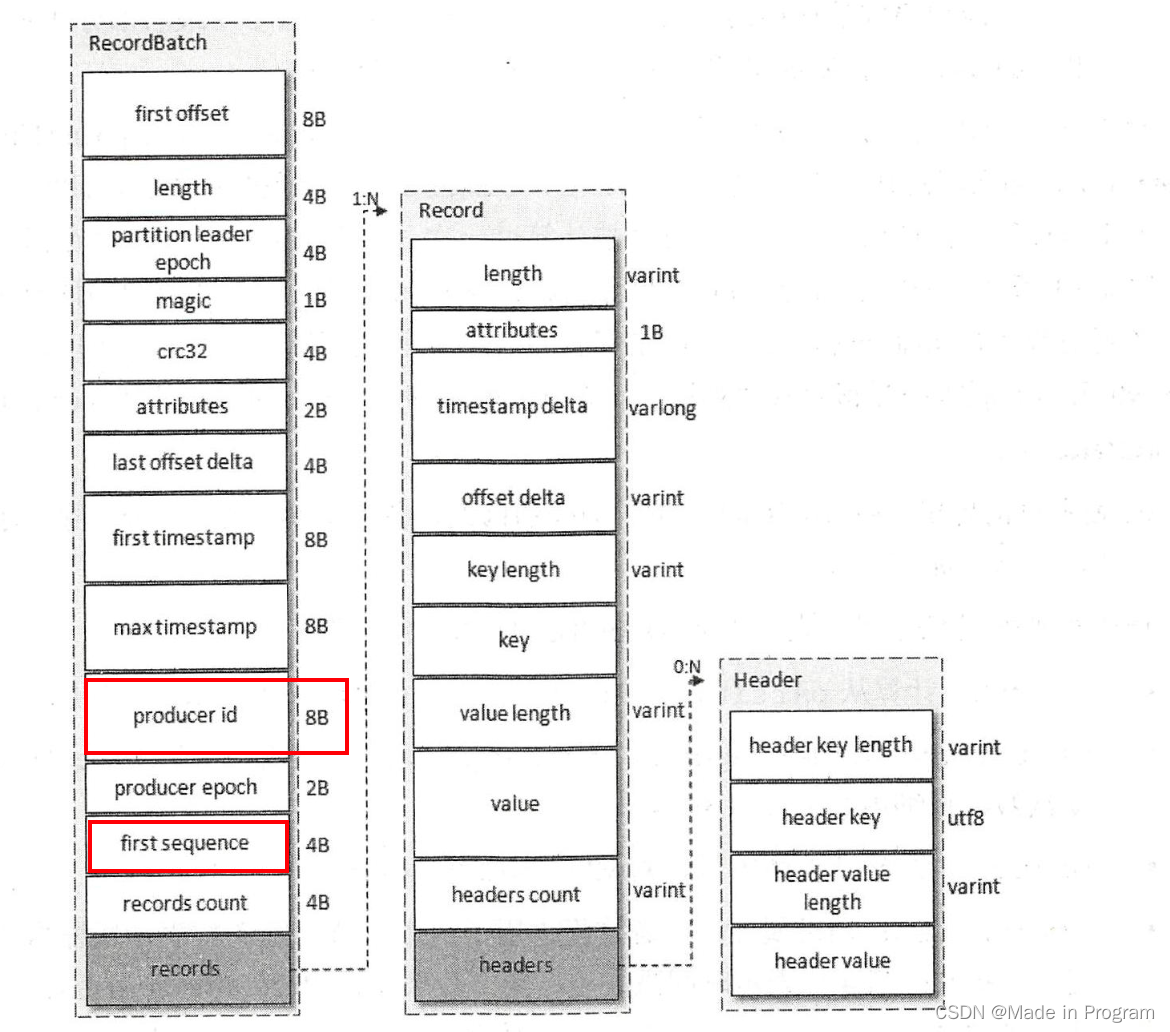

kafka精准一次、事务、幂等性

Kafka事务 消息中间件的消息保障的3个级别 At most once 至多一次。数据丢失。At last once 至少一次。数据冗余Exactly one 精准一次。好!!! 如何区分只要盯准提交位移、消费消息这两个动作的时机就可以了。 当:先消费消息、…...

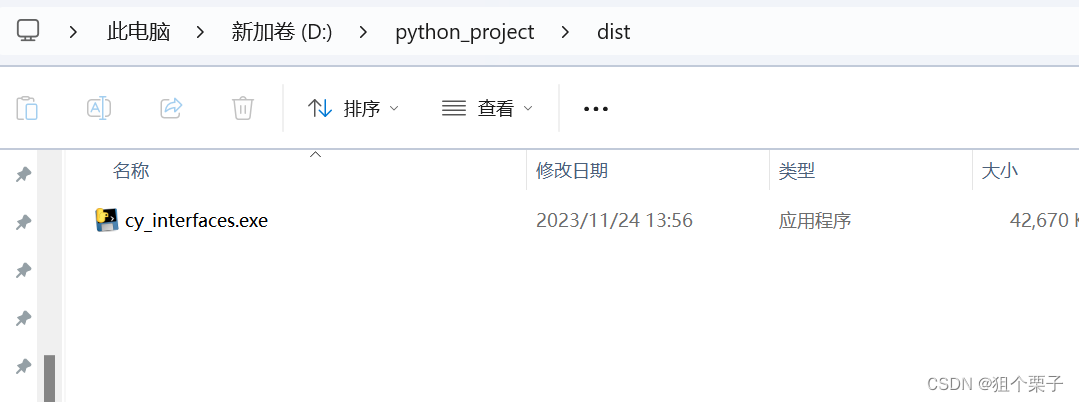

centos 7.9 下利用miniconda里的pyinstaller打包python程序为二进制文件操作方法

centos 7.9 下利用miniconda里的pyinstaller打包python程序为二进制文件操作方法 一.centos 7.9 操作系统安装 参考:https://blog.csdn.net/qq_46015509/article/details/134572030?utm_sourceminiapp_weixin 安装完成后用后台连接工具连上虚拟机 二.安装python3 …...

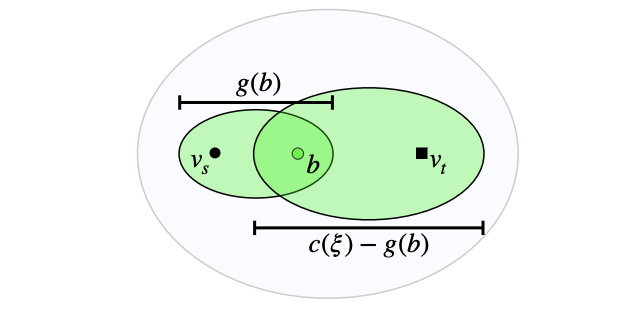

Motion Plan之基于采样的路径规划算法笔记

Motion Plan之搜索算法笔记 背景: 基于采样算法是一种在路径规划中广泛应用的有效方法。它通过在图中随机选择点来生成一个简化的搜索图,从而加速搜索过程。这种方法的主要优点包括减少内存使用,避免计算错误,具有动态障碍物对抗…...

idea里面常用插件

这里列出了一系列常用的 IntelliJ IDEA 插件,它们可以提高开发效率、简化操作,以及帮助进行代码分析和优化。以下是每个插件的简要介绍: GenerateAllSetter:生成对象的所有 set 方法和 get 方法,方便对象之间的转换。该…...

回归算法优化过程推导

假设存在一个数据集,包含工资、年龄及贷款额度三个维度的数据。我们需要根据这个数据集进行建模,从而在给定工资和年龄的情况下,实现对贷款额度的预测。其中,工资和年龄是模型构建时的两个特征,额度是模型输出的目标值…...

某高品质房产企业:借助NineData平台,统一数据库访问权限,保障业务安全

该企业是中国领先的优质房产品开发及生活综合服务供应商。在 2022 年取得了亮眼的业绩表现,销售额市场占有率跻身全国前五。业务涵盖房产开发、房产代建、城市更新、科技装修等多个领域。 2023 年,该企业和玖章算术(浙江)科技有限…...

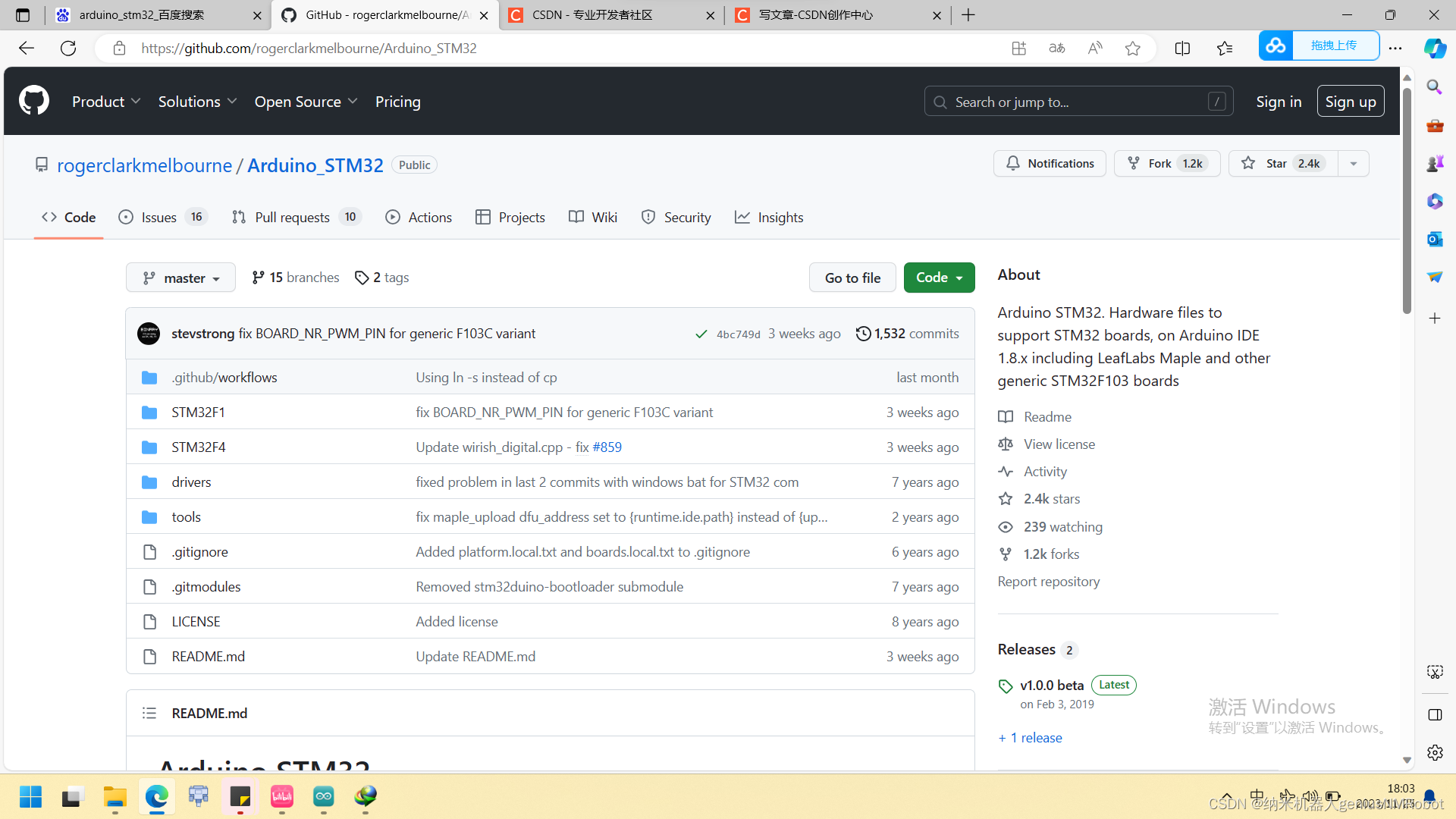

Arduio开发STM32所面临的风险

据说micro_ros用到了arduino,然后用arduino搞stm32需要用到这个Arduino STM32的东西,然后这里申明了:这些代码没有经过严格测试,如果是向心脏起搏器,自动驾驶这样要求严格的的情况下,这个东西不能保证100%不发生问题&a…...

精准人脉引流软件的开发流程与涉及到的技术

一、精准人脉引流软件的开发流程 1. 确定需求:首先,我们需要明确软件的需求,包括目标用户、功能需求、性能需求等。这些需求将直接影响到软件的开发方向和最终效果。 2. 系统设计:根据需求,进行系统设计,…...

Mysql数据库 20.DCL数据控制语言

因这类SQL语言开发人员操作较少,主要是数据库管理员(DBA)使用,所以前文没有提及,这篇文章进行补充说明 DCL数据控制语言 用来管理数据库用户,控制数据库的访问权限 1.管理用户 1.1 查询用户 select * f…...

使用CMake交叉编译Arm Linux程序

下载安装aarch64-linux-gnu-gcc arm交叉编译工具链 apt-get install aarch64-linux-gnu-gccapt-get install aarch64-linux-gnu-gcc创建编译目录构建makefle 注意,工具链文件的指定一定要紧跟cmake命令之后,不能放到 … 后面构建arm架构cmake mkdir arm…...

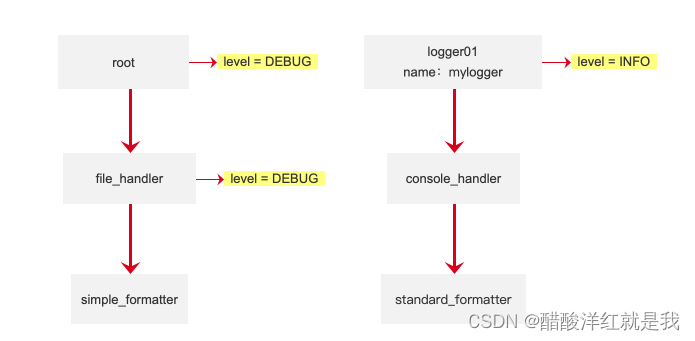

训练日志——logging

目录 基础使用日志的6个级别打印日志修改打印级别 高级应用logging的组成记录器Loggers处理器Handlers过滤器Filterformatter格式创建关联打印日志 配置文件参考 基础使用 日志的6个级别 打印日志 import logginglogging.debug(调试日志) logging.info(消息日志) logging.war…...

尺度为什么是sigma?

我们先看中值滤波和均值滤波。 以前,我认为是一样的,没有区分过。 他们说,均值滤波有使图像模糊的效果。 中值滤波有使图像去椒盐的效果。为什么不同呢?试了一下,果然不同,然后追踪了一下定义。 12345&…...

第一篇博客,自己大学后的目标

a.我是涛同学,来自重庆,学校是岭南师范大学,是一所普通本科,但我的目标却不普通。b.学习编程的目标是为了掌握编程技能,是为了以后更好的生活,是为了拿到大厂offerc.我打算先学好python和cd.我打算每周花5个…...

单片机P2口驱动LED的两种接法详解:“拉电流”与“灌电流”,你用对了吗?

单片机P2口驱动LED的两种接法详解:“拉电流”与“灌电流”,你用对了吗? 在单片机开发中,驱动LED是最基础却最容易忽视细节的环节。很多教程只教一种连接方法,但实际项目中,根据LED亮度需求、功耗限制和单片…...

Kerberos运维踩坑实录:从JDK版本到DNS解析,这10个报错我帮你趟平了

Kerberos运维深度排错指南:十大典型故障场景与根治方案 凌晨三点,告警铃声划破寂静——"Client cannot authenticate via:[TOKEN, KERBEROS]"的红色警报在监控屏上闪烁。作为大数据平台的核心认证网关,Kerberos的每次异常都可能引发…...

OpenClaw 微信通道搭建方法 三种部署模式详细讲解

一、方案背景与核心价值 在微信私域运营与自动化客服场景中,OpenClaw 可以打通微信客户端与后端服务的通信链路,降低接入门槛,支持本地、云端等多种环境部署,兼顾数据安全与连接稳定性。本文围绕部署细节与故障排查逻辑展开&…...

【Ubuntu24.04安装dirsearch】

Ubuntu24.04安装dirsearch常见问题无法直接使用pippipx的问题解决方法常见问题 无法直接使用pip 🔒 核心原因:Ubuntu 24.04 的 Python 保护机制 防止 pip 和 apt 互相覆盖文件,Ubuntu 24.04 及以上版本 引入了 PEP 668 规范,系统 Python 环…...

实战指南:3种高效配置ipget分布式文件下载方案深度解析

实战指南:3种高效配置ipget分布式文件下载方案深度解析 【免费下载链接】ipget Retrieve files over IPFS and save them locally. 项目地址: https://gitcode.com/gh_mirrors/ip/ipget ipget是一款专为IPFS网络设计的轻量级下载工具,能够直接从I…...

)

【力扣hot100】【Leetcode 15】三数之和|暴力枚举 双指针 算法笔记及打卡(14/100)

【力扣】【Leetcode 15】三数之和|暴力枚举 | 双指针 给你一个整数数组 nums ,判断是否存在三元组 [nums[i], nums[j], nums[k]] 满足 i ! j、i ! k 且 j ! k ,同时还满足 nums[i] nums[j] nums[k] 0 。请你返回所有和为 0 且不重复的三元…...

Spring Integration 2.2.1 和 2.1.5 是 Spring Integration 框架的历史版本

Spring Integration 2.2.1 和 2.1.5 是 Spring Integration 框架的历史版本,分别于 2013 年初发布(2.2.1 发布于 2013 年 2 月,2.1.5 发布于 2012 年 12 月),属于较早期的维护性补丁版本。它们主要包含: Bu…...

[特殊字符] MoviePy 报错:配置了 ImageMagick 环境变量却不好使?

.This error can be due to the fact that ImageMagick is not installed on your computer, or (for Windows users) that you didnt specify the path to the ImageMagick binary in file conf.py, or that the path you specified is incorrect在使用 Python 的 MoviePy 库制…...

:覆盖语言、视觉、决策、机器人、科学发现全场景)

AGI迁移学习能力评估体系(全球首套工业级5维量化框架):覆盖语言、视觉、决策、机器人、科学发现全场景

第一章:AGI的跨领域迁移学习能力 2026奇点智能技术大会(https://ml-summit.org) 跨领域迁移学习是通用人工智能(AGI)区别于狭义AI的核心能力之一——它要求模型在未经历显式训练的前提下,将从视觉识别中学到的抽象因果推理机制&a…...