CPU、MCU、MPU、DSP、FPGA各是什么?有什么区别?

1、CPU

中央处理器,简称 CPU(Central Processing Unit),中央处理器主要包括两个部分,即控制器、运算器,其中还包括高速缓冲存储器及实现它们之间联系的数据、控制的总线。

电子计算机三大核心部件就是CPU、内部存储器、输入/输出设备。中央处理器的功效主要为处理指令、执行操作、控制时间、处理数据.

CPU历史发展:

Intel于1971年发售了自己的第一款4位微处理器,设计与ROM 4001,RAM 4002和移位寄存器4003配合工作。其中4004自身负责运算,其它部分则是使CPU正常工作的重要组成。大部分4004被用于计算器和其它类似的设备,而不是用在计算机中。它的最大频率只有740KHz。

4004使得Intel成为了一家微处理器公司,为了适应潮流,Intel发布了新的8位处理器系列。8008,8080和8085分别于1972年,1974年和1975年发布。

8086:X86的起点(1978)

Intel的第一款16微处理器,相比于8080大有提升。不仅频率更高,而且16位总线和其它附加硬件允许8086同时执行两条8位指令。它也能执行更高效的16位任务,但此时大多数软件是8位软件,所以支持16位在多任务能力面前显得不那么重要。地址总线则扩展到了20位,使得8086可以存取1MB的内存,因而提高了性能。

80386:X86的32位开端(1986)

Intel的第一款32位X86处理器是80386,于1985年发布。其中最关键的特性就是采用了32位地址总线最大支持4GB内存,尽管这个数字比当时大多数人用的要大得多,但RAM的限制损害了早先X86处理器和它的竞品的性能。与现代CPU不同的是,在80386时代,更多的RAM能够直接转化为性能的提升。Intel同时采用了一些架构改进来提升相同RAM大小的性能表现。

最初的Pentium(奔腾)(1993)

最初的Pentium CPU在1993年发布,但没有沿用80X86的命名方式。Pentium采用了P5架构,这是Intel在X86 CPU首次采用超标量技术(注:这与我们现在常提到的超线程技术不同),尽管全面超越了80486,但最突出的进步是改进了FPU。

Westmere:核显的开端(2010)

Intel使用32nm工艺重做了Nehalem并命名为Westmere,它的底层架构没有太多变化,但是通过制程带来的进步,Intel可以在CPU中塞下更多的东西,Westere堆至10核心以及多达30MB的三级缓存。

Broadwell(2014)

Intel的下一代架构的核心代号为Broadwell,采用14nm制程,为移动端而设计,于2014年发布。首个Broadwell产品是Core M,双核超线程CPU,TDP仅有3-6W

但是在桌面市场,几乎难见Broadwell的身影,仅在2015年中期发布寥寥几款产品,但集成了Intel史上最强核显,包括48组EU单元,128MB L4 eDRAM缓存,解决了核显的带宽问题,在游戏性能的测试中,表现优于AMD最快的APU

Skylake(2015)

在Broadwell桌面端发布后不久,Intel发布了下一代产品Skylake架构,尽管这是Intel至今最强的CPU,不过平台的变化可以说比CPU本身更重要。

2、MCU

MCU(MicroControllerUnit)中文名称为微控制单元,又称单片微型计算机,是指随着大规模集成电路的出现及其发展,将计算机的CPU、RAM、ROM、定时数器和多种I/O接口集成在一片芯片上,形成芯片级的计算机,为不同的应用场合做不同组合控制。

MCU按其存储器类型可分为MASK(掩模)ROM、OTP(一次性可编程)ROM、FLASHROM等类型。MASKROM的MCU价格便宜,但程序在出厂时已经固化,适合程序固定不变的应用场合;

FALSHROM的MCU程序可以反复擦写,灵活性很强,但价格较高,适合对价格不敏感的应用场合或做开发用途;

OTPROM的MCU价格介于前两者之间,同时又拥有一次性可编程能力,适合既要求一定灵活性,又要求低成本的应用场合,尤其是功能不断翻新、需要迅速量产的电子产品。

3、MPU

微处理器单元(Micro Processor Unit, MPU),就是把很多 CPU 集成在一起并行处理数据的芯片。通俗来说,MCU 集成了 RAM,ROM 等设备;MPU 则不集成这些设备,是高度集成的通用结构的中央处理器矩阵,也可以认为是去除了集成外设的 MCU。

4、DSP

DSP(DigitalSignalProcessing),数字信号处理,简称DSP。DSP是用数值计算的方式对信号进行加工的理论和技术。另外DSP也是DigitalSignalProcessor的简称,即数字信号处理器,它是集成专用计算机的一种芯片,只有一枚硬币那么大。

5、FPGA

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA做得好的厂商:Altera((阿尔特拉)被Intel收购)、Xilinx(赛灵思)、Actel、Lattice(莱迪思)、Atmel、京微雅格、QuickLogic、Microsemi、Cypress、TI、上海复旦微、广东高云、同方国芯、西安智多晶、中国电子、成都华微、深圳国微、遨格芯等等。

CPU、MCU、MPU、DSP、FPGA的比较

CPU(Central Processing Unit,中央处理器)发展出来三个分枝,一个是DSP(Digital Signal Processing/Processor,数字信号处理),另外两个是MCU(Micro Control Unit,微控制器单元)和MPU(Micro Processor Unit,微处理器单元)。

MCU:大都在结构上是基于冯·诺伊曼结构的,这种结构清楚地定义了嵌入式系统所必需的四个基本部分:一个中央处理器核心,程序存储器(只读存储器或者闪存)、数据存储器(随机存储器)、一个或者更多的定时/计数器,还有用来与外围设备以及扩展资源进行通信的输入/输出端口——所有这些都被集成在单个集成电路芯片上。指令集上早期的MCU是采用CISC的,后面被RISC取代。在总线位数上,MCU覆盖了4位、8位、16位、32位,应用十分广泛。

DSP:结构上它采用哈佛结构,同样采用流水线技术。此外,DSP被用于宿主环境时可作为直接内存存取设备运作,还支持从模拟数字转换器(ADC)获得数据,最终输出的是由数字模拟转换器(DAC)转换为模拟信号的数据,支持一定的并行处理。

FPGA:FPGA采用了逻辑单元阵列LCA(LogicCellArray)这样一个新概念,内部包括可配置逻辑模块CLB(ConfigurableLogicBlock)、输出输入模块IOB(InputOutputBlock)和内部连线(Interconnect)三个部分。用户可对FPGA内部的逻辑模块和I/O模块重新配置,以实现用户的逻辑。它还具有静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改。FPGA有别于DSP、ARM、MCU的地方主要在于它的并行处理能力,它的强大并行性使复杂的运算得到极大的速度比提升。[4]

相关文章:

CPU、MCU、MPU、DSP、FPGA各是什么?有什么区别?

1、CPU 中央处理器,简称 CPU(Central Processing Unit),中央处理器主要包括两个部分,即控制器、运算器,其中还包括高速缓冲存储器及实现它们之间联系的数据、控制的总线。 电子计算机三大核心部件就是CPU…...

SpringBoot之logback 在Linux系统上启动的时候,设置日志按日期分割并设置指定时间自动清除日志

一、在src/main/resources/下创建logback-spring.xml文件 <?xml version"1.0" encoding"UTF-8"?> <configuration><!-- 日志存放路径 --><property name"log.path" value"/home/xmmc/logs" /><!-- 日志…...

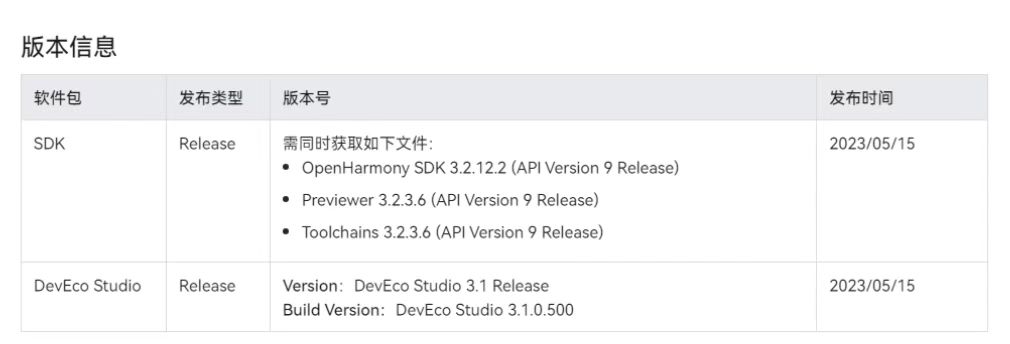

OpenHarmony北向-让更广泛的应用开发者更容易参与

一、标准系统的体验 按照官方文档指导,这样操作,OH标准系统开发板就可以运行开发者开发的OpenHarmony应用了。 二、实际情况 按照开发文档上的说明,肯定是装不上的。因为OH不同的发行版,不同发行板不同的设备,IDE&…...

数据结构之归并排序及排序总结

目录 归并排序 归并排序的时间复杂度 排序的稳定性 排序总结 归并排序 归并排序大家只需要掌握其递归方法即可,非递归方法由于在某些特殊场景下边界难控制,我们一般很少使用非递归实现归并排序。那么归并排序的递归方法我们究竟是怎样实现呢ÿ…...

仿windows12网盘,私有云盘部署教程,支持多种网盘

仿windows12网盘,私有云盘部署教程,支持多种网盘 资源宝分享:www.httple.net 视频教程:https://www.bilibili.com/video/BV1m64y1G7Bq/ 宝塔部署方式: 1.验证是否安装jdk,没有安装请看安装教程 推荐安装jdk8(注意您…...

深度学习 时间序列回归学习笔记

目录 常用的深度学习时间序列回归模型: ARIMA模型 ETS模型 效果评估...

【postgresql】ERROR: INSERT has more expressions than target columns

执行下面sql insert into apply_account_cancellation3 select * from pply_account_cancellation; 返回下面错误信息 insert into apply_account_cancellation3 select * from apply_account_cancellation > ERROR: INSERT has more expressions than target colu…...

Android Kotlin语言下的文件存储

目录 将数据存储到文件中 创建文件和保存数据 读取文件 SharedPreferences存储 存储数据到SharedPreferences中 Context类中的getSharedPreferences()方法 Activity类中的getPreferences()方法 从SharedPreferences中读取数据 SQLite数据库存储 创建数据库 调用数据…...

Verilog 入门(八)(验证)

文章目录 编写测试验证程序波形产生值序列重复模式 测试验证程序实例从文本文件中读取向量实例:时序检测器 测试验证程序用于测试和验证设计方法的正确性。Verilog 提供强有力的结构来说明测试验证程序。 编写测试验证程序 测试验证程序有三个主要目的:…...

)

vue3 vue-router 导航守卫 (五)

在Vue 3中,导航守卫仍然是一个重要的概念,用于在路由切换时执行一些特定的逻辑。Vue Router提供了多个导航守卫,包括全局守卫、路由独享守卫和组件内守卫。可以在路由切换时执行一些特定的逻辑,例如身份验证、权限控制、数据加载等…...

Git命令---查看远程仓库

介绍 使用git命令查看绑定的远程仓库。 命令 git remote -v...

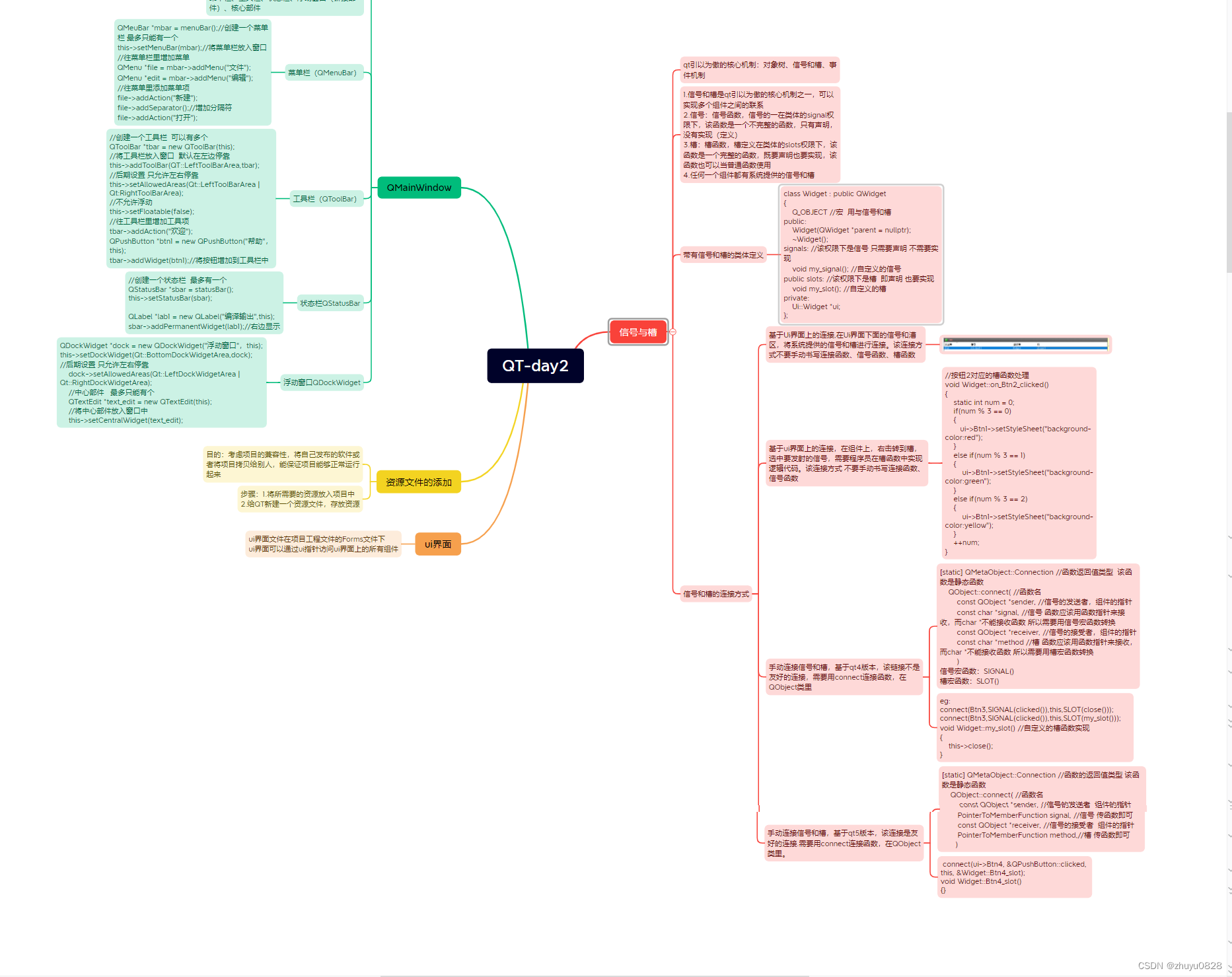

12.8作业

1. 使用手动连接,将登录框中的取消按钮使用qt4版本的连接到自定义的槽函数中,在自定义的槽函数中调用关闭函数 将登录按钮使用qt5版本的连接到自定义的槽函数中,在槽函数中判断ui界面上输入的账号是否为"admin",密码是…...

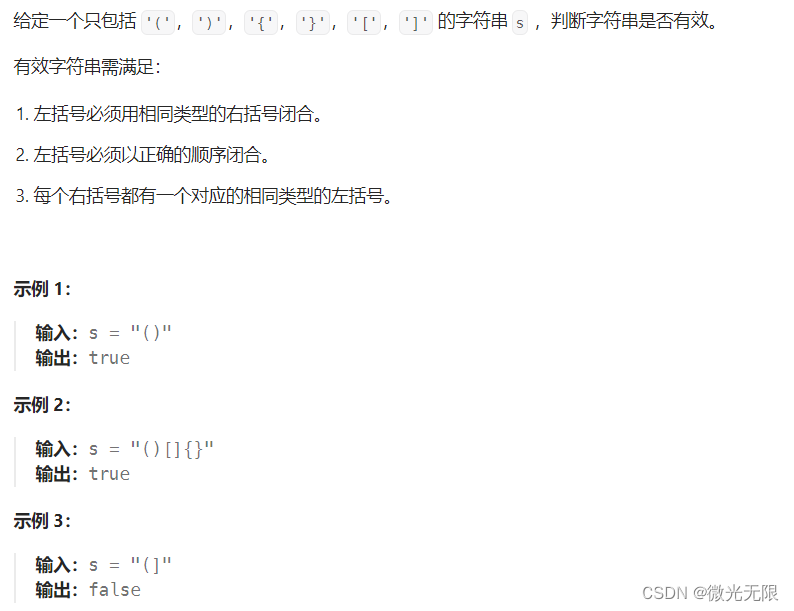

算法:有效的括号(入栈出栈)

时间复杂度 O(n) 空间复杂度 O(n∣Σ∣),其中 Σ 表示字符集,本题中字符串只包含 6 种括号 /*** param {string} s* return {boolean}*/ var isValid function(s) {const map {"(":")","{":"}","["…...

vxworks常用的指令归纳

目的:方便自己查阅 tftpboot 0x10000000 vxworks bootelf 0x10000000 ifconfig "gem0 dowm" ifconfig "gem0 inet 192.168.0.81" ifconfig "gem0 lladdr 01:02:03:04:05:06:07" ifconfig "gem0 up" ld 0,1,"…...

线性回归实战

3.1 使用正规方程进行求解 3.1.1 简单线性回归 公式 : y w x b y wx b ywxb 一元一次方程,在机器学习中一元表示一个特征,b表示截距,y表示目标值。 使用代码进行实现: 导入包 import numpy as np import matp…...

stm32 使用18B20 测试温度

用18b20 测试温度是非常常用的,不过18B20的调试不是这么容易的,有些内容网上很多的,不再重复说了,我先把波形说一下,再说程序部分: 整个都温度数据的顺序是: 1.700uS的低电平复位并测试18B20的…...

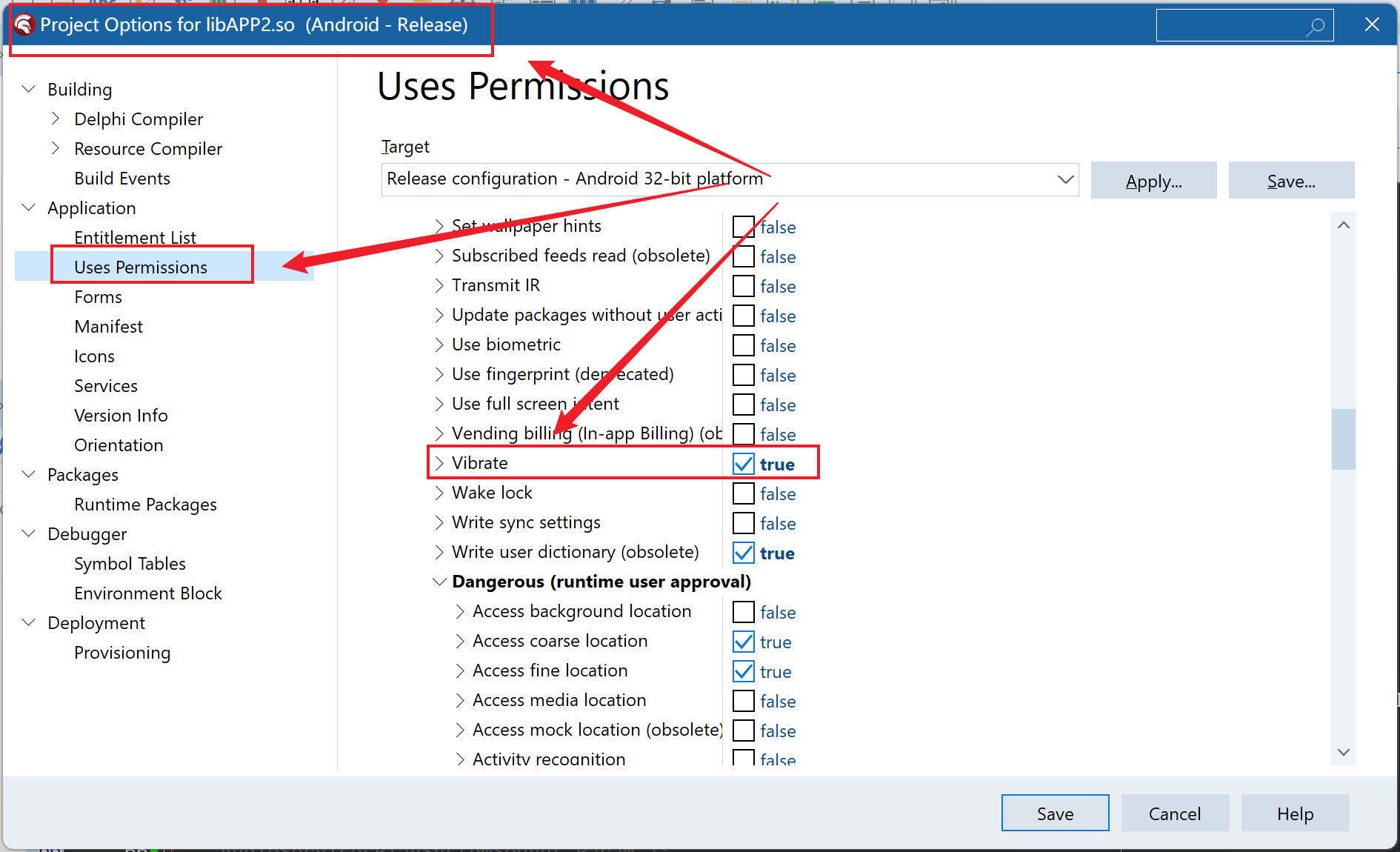

【Delphi】一个函数实现ios,android震动功能 Vibrate(包括3D Touch 中 Peek 震动等)

一、前言 我们在开发移动端APP的时候,有时可能需要APP能够提供震动功能,以便提醒操作者,特别是ios提供的3D Touch触感功能,操作者操作时会有触感震动,给操作者的感觉很友好。那么,在Delphi的移动端FMX开发中…...

国产Type-C PD芯片—接口快充取电芯片

常用USB PDTYPE-C受电端,即设备端协议IC芯片(PD Sink,也叫PD诱骗芯片),诱导取电芯片。 产品介绍 LDR6328: ◇ 采用 SOP-8 封装 ◇ 兼容 USB PD 3.0 规范,支持 USB PD 2.0 ◇ 兼容 QC 3.0 规范&#x…...

)

pytorch学习6-非线性变换(ReLU和sigmoid)

系列文章目录 pytorch学习1-数据加载以及Tensorboard可视化工具pytorch学习2-Transforms主要方法使用pytorch学习3-torchvisin和Dataloader的使用pytorch学习4-简易卷积实现pytorch学习5-最大池化层的使用pytorch学习6-非线性变换(ReLU和sigmoid)pytorc…...

详解Keras3.0 Models API: Whole model saving loading

1、save方法 Model.save(filepath, overwriteTrue, **kwargs) 将模型另存为.keras文件 参数说明 filepath: 保存模型的路径。必须以.keras结尾overwrite:布尔值,表示是否覆盖已存在的文件。默认为 True,即覆盖已存在的文件。save_format…...

LeagueAkari:如何用数据驱动你的英雄联盟竞技水平提升

LeagueAkari:如何用数据驱动你的英雄联盟竞技水平提升 【免费下载链接】League-Toolkit An all-in-one toolkit for LeagueClient. Gathering power 🚀. 项目地址: https://gitcode.com/gh_mirrors/le/League-Toolkit 在英雄联盟这款全球热门的竞…...

Qwen3-TTS开源模型教程:Gradio接口封装+API服务发布完整指南

Qwen3-TTS开源模型教程:Gradio接口封装API服务发布完整指南 1. 前言:为什么你需要一个专属的语音合成服务? 想象一下,你正在开发一个智能客服应用,需要为不同国家的用户提供多语言的语音回复;或者你是一个…...

新手入门:借助快马AI实现你的第一个超能力选择网页

作为一个刚接触编程的新手,我最近想尝试做一个有趣的网页项目。看到网上那些酷炫的交互效果,总觉得很神奇但又无从下手。直到发现了InsCode(快马)平台,它让我这个小白也能轻松实现"超能力选择器"这样的创意想法。 项目构思 我想做一…...

告别手动调参!用Simulink扫频法+PID Tuner,10分钟搞定升降压电路的PI控制器设计

10分钟自动化PI设计:Simulink扫频与PID Tuner在升降压电路中的实战技巧 电力电子工程师们对这样的场景一定不陌生:面对一个全新的升降压电路拓扑,为了获得稳定的输出电压,不得不花费数小时甚至数天时间反复调整PI控制器的参数。传…...

YOLO-v5实战:用预训练模型快速检测图片中的物体

YOLO-v5实战:用预训练模型快速检测图片中的物体 1. 引言:为什么选择YOLO-v5 在计算机视觉领域,物体检测是一项基础而重要的任务。YOLO(You Only Look Once)系列模型因其速度快、精度高的特点,成为工业界和…...

)

Claude Code本地安装与配置国产智谱模型 (保姆级教程)

目录 一、安装 二、验证安装完整性 三、绕过区域限制协议 1. 创建专属启动脚本 2. 配置系统环境变量 3. 通过脚本启动 四、配置国产智普模型 今天给大家带来一期非常实用的 AI 工具部署教程。作为开发者,善用 AI 工具能极大提升我们的日常编码和解决问题的效…...

Calypso vs PC-DMIS:三坐标两大软件脱机编程实战对比与选型指南

Calypso vs PC-DMIS:三坐标测量软件脱机编程深度对比与实战选型策略 在精密制造领域,三坐标测量机(CMM)的脱机编程能力直接决定了检测效率与资源利用率。作为行业两大标杆,蔡司Calypso与海克斯康PC-DMIS在用户界面设计、编程逻辑、仿真验证等…...

Qwen3.5-9B-AWQ-4bit参数调优实战:温度=0.7时中文回答质量与响应速度平衡点

Qwen3.5-9B-AWQ-4bit参数调优实战:温度0.7时中文回答质量与响应速度平衡点 1. 模型概述与参数调优背景 Qwen3.5-9B-AWQ-4bit是一个支持图像理解的多模态模型,能够结合上传图片与文字提示词输出中文分析结果。在实际应用中,我们发现温度参数…...

2026年Java面试最常被问的1000道题目及参考答案

Java学到什么程度可以面试工作? 要达到能够面试Java开发工作的水平,需要掌握以下几个方面的知识和技能: 1. 基础扎实:熟悉Java语法、面向对象编程概念、异常处理、I/O流等基础知识。这是所有Java开发者必备的基础,也…...

BabyOS:MCU裸机开发的轻量级框架解析

1. BabyOS:专为MCU裸机开发设计的轻量级框架 在嵌入式开发领域,重复造轮子一直是困扰工程师的痛点。每次新项目启动,我们总需要重新调试那些基础功能模块——从串口通信到Flash操作,从定时器管理到协议栈实现。BabyOS的出现&#…...