Verilog使用always块实现时序逻辑

这篇文章将讨论 verilog 中一个重要的结构---- always 块(always block)。

verilog 中可以实现的数字电路主要分为两类----组合逻辑电路和时序逻辑电路。与组合逻辑电路相反,时序电路电路使用时钟并一定需要触发器等存储元件。因此,输出信号与时钟同步,而不是立即发生变化。

在verilog中需要使用 always 块来编写时序逻辑电路,这一点至关重要。

1、Verilog 中的 Always 块(Always Block)

在编写 verilog 时,可以使用过程块(procedural blocks)来创建顺序执行的语句,过程块对于实现时序电路特别重要。相反,连续赋值语句在设计中并发(即并行)执行,这与底层电路的性质相匹配----底层电路由许多独立的逻辑门组成。

always 块是 verilog 中最常用的过程块之一,每当敏感列表中的一个信号改变状态时,always 块中的所有语句都会按顺序执行。

下面的 verilog 代码显示了 always 块的一般语法。

always @(<sensitivity_list>) begin//这里写要实现的代码

end使用这个结构时需要小心,因为有一些 verilog 独有的特性,特别是初学者经常很难理解信号在 always 块中更新的方式。

在使用 always 块时,可以并行或顺序(串行)更新信号的值。这取决于使用的是阻塞赋值(blocking assignment)还是非阻塞赋值(non-blocking assignment)。要想成为一名高效的 verilog 设计者,就必须很好地理解 always 块。

1.1、敏感列表(Sensitivity Lists)

在 always 块中编写的任何代码都会连续运行,这意味着代码块中的语句会按顺序执行,直到最后一行。一旦执行完序列中的最后一行,程序就会循环回到第一行,然后,always 块中的所有语句将再次按顺序执行。

然而,这种行为并不能描述这样一种电路----其中一个输入信号改变状态之前将保持稳定状态的真实电路。verilog使用 alway 块中的敏感列表来模拟这种行为,所以,always 块中的代码将仅在敏感列表中的信号之一更改状态后执行。

1.1.1、触发器(Flip Flop )示例

与所有触发器一样,D 触发器的输出仅在时钟上升沿时才改变状态,因此可以将时钟信号包含在敏感列表中,以便 always 块仅在时钟信号出现上升沿时执行。

下面的 verilog 代码展示了如何使用 always 块实现 D 触发器。

always @(posedge clock) beginq <= d;

end在此代码示例中使用了 posedge 来确定何时存在从 0 到 1 的转换(即时钟上升沿)。

当posedge的计算结果为真时,将执行 always 块中的单行代码,这行代码将输入D 的值分配给输出 Q。在 verilog 中使用 posedge 时,所有其他的状态变化都会被忽略,这正符合对 D 触发器的设计期望。

Verilog 也有一个具有相反功能的 negedge 。当使用negedge时,只要时钟从 1 变为 0(即时钟下降沿),always 块就会被执行。

设计者也可以不使用posedge/negedge,在这种情况下,只要敏感列表中的信号改变状态,代码就会执行。

1.1.2、敏感列表中的多个信号

在某些情况下,设计者希望在敏感列表中包含多个信号。一个常见的例子是要编写代码来实现一个具有异步复位的触发器,在这种情况下,设计师希望触发器在复位或时钟信号改变状态时才执行操作。

为此,可以在敏感度列表中列出两个信号,并用逗号分隔它们。下面的代码片段展示了如何实现这样一个触发器。

always @(posedge clock, posedge reset) beginif (reset) begin q <= 1'b0;endelse beginq <= d;end

end由于此示例使用了高电平有效复位,高电平有效复位意味着复位仅在等于 1 时有效,因此再次在灵敏度列表中使用了 posedge ,然后使用了 if 语句的结构来确定 always 块是由复位信号还是时钟边沿信号触发。

使用Verilog-1995 标准的代码时,必须使用 or 关键字或逗号来分隔敏感列表中的信号。

下面的代码片段展示了如何使用 Verilog-1995 标准来实现异步可复位触发器。

always @(posedge clock or posedge reset) beginif (reset) begin q <= 1'b0;endelse beginq <= d;end

end2、Verilog 中的阻塞赋值(Blocking Assignment)和非阻塞赋值(Non-Blocking Assignment)

到目前为止本文使用了两种不同类型的赋值运算符。这是因为 verilog 有两种不同类型的赋值——阻塞赋值和非阻塞赋值。使用非阻塞赋值编写代码时,使用 <= 符号,而阻塞赋值则使用 = 符号。

在verilog中使用连续赋值语句时时,只能使用阻塞赋值。但是,在过程块中可以使用这两种类型的赋值。

阻塞赋值通常会生成组合逻辑电路,而非阻塞赋值则通常会生成时序逻辑电路。

在 verilog 中使用阻塞赋值来对信号赋值时,信号会在代码行执行后立即更新它们的值,所以这种类型的赋值在 verilog 中通常被用来编写组合逻辑;相反,使用非阻塞赋值的信号在赋值后不会立即更新。

2.1、scheduled assignment

使用非阻塞赋值编写 verilog 代码时,代码仍然按顺序执行。但是,信号却不会以这种方式更新。为了说明为什么会这样,将以下面的扭环计数器电路(twisted ring counter)为例。

always @(posedge clock) beginq_dff1 <= ~q_dff2;q_dff2 <= q_dff1;

end首先来看看信号立即更新时的行为。假设当时钟边沿出现时两个触发器的输出都是 0,那么代码中的第二行会将 DFF1 的输出设置为 1,然后可以看到紧接其下方的代码行会将 DFF2 的输出设置为 1。但这显然不是该电路的预期行为。

为了克服这个问题,非阻塞赋值就会做scheduled assignment(预设赋值,这个术语我也不会翻译,大概意思是赋值的发生会“ 有计划性地安排在未来的某一个时间”)。因此,信号的更改不会在赋值后立即发生,而是在将来的某个时间发生。通常,信号会在仿真周期末尾更新它们的值----这是指仿真工具在给定时间步长内执行所有代码所花费的时间。

为了更好地演示scheduled assignment的工作方式,请再次考虑简单的双触发器电路(dual flip flop circuit)。

当检测到上升沿时,模拟器首先执行更新 DFF1 的语句,然后将计划对 DFF1 的输出进行更新。当模拟器运行第二行代码,这次使用 DFF1 触发器的原始值并安排 DFF2 的更新。

由于此设计中只有两个语句,因此仿真周期现已完成。此时,所有计划的更改都将被实现并更新两个触发器的值。

2.2、综合案例(Synthesis Example)

为了进一步展示 verilog 中阻塞赋值和非阻塞赋值之间的区别,接下来将再次模拟一个基本的双触发器扭环计数器电路。下面的代码片段展示了如何实现该电路。

always @(posedge clock) beginq_dff1 <= ~q_dff2;q_dff2 <= q_dff1;

end可以看下vivado所生成的电路图,如下所示。电路中有两个触发器,而非门是则使用 LUT1 实现的。

接着来看看如果在代码中使用阻塞赋值将会得到何种电路。下面的 verilog 代码展示如何尝试使用阻塞赋值来实现该电路(错误的示范)。

always @(posedge clock) beginq_dff1 = ~q_dff2;q_dff2 = q_dff1;

end这导致综合后的电路如下所示。

从这里可以看出,使用阻塞赋值导致电路中的第二个触发器被移除了。这样做的原因应该是相当明显的。由于 q_dff2 的值立即赋给与 q_dff1 相同的值,所以该信号路径中不应该有触发器。

这个例子实际上展示了 verilog 中阻塞赋值和非阻塞赋值之间最重要的一个区别----使用非阻塞赋值时,综合工具总是会在电路中放置一个触发器。这意味着设计者只能使用非阻塞赋值来实现时序逻辑电路。相反,设计者可以使用阻塞来创建时序电路或组合电路。

但是,设计者应该只使用阻塞赋值来实现 verilog 中的组合逻辑电路,这样做的主要原因是编写的代码将更容易理解和维护。

3、Always 块中的组合逻辑

到目前为止,本文只考虑了使用 always 块的时序电路建模。虽然这是最常见的用例,但设计者也可以使用这种方法对组合逻辑进行建模。

例如,下面的代码展示了如何使用 always 块来实现如下所示的 AND-OR 电路。

// verilog-2001标准

always @(a, b, c) beginlogic_out = (a & b) | c;

end// verilog-1995标准

always @(a or b or c) beginlogic_out = (a & b) | c;

end这段代码几乎与在连续赋值语句中实现的方法不同,主要区别就是被其封装在了一个 always 块中。此外还从语句中删除了assign关键字,因为在此情况下已经不再需要它了。

从这个例子中还可以看出,组合逻辑电路的敏感列表比时序逻辑电路更复杂。在实现组合逻辑电路时,实际上有两种方法可以用来编写敏感类别。

第一种方法是列出电路的每个输入,用 or 关键字或逗号分隔,这也是上面的示例代码中所使用的方法。

第二种方法是使用 * 字符来告诉综合工具自动决定将哪些信号包含在敏感列表当中。这种技术更可取,因为它更易于维护,但是,此方法是作为verilog-2001标准的一部分引入的,这意味着它不能与 verilog-1995标准的代码一起使用。

下面的代码片段展示了如何使用这两种方法。

// 穷举出所有信号的敏感列表

always @ (a, b, c)// 使用 * 实现的敏感列表

always @ (*)一般来讲,只在少数情况下使用 always 块对组合逻辑电路进行建模,因为它可以简化复杂组合逻辑的建模。

多路选择器(Multiplexors)

如果想要实现多路选择器,使用 always 块来实现这种组合逻辑可能是一个很有用的办法。在这种情况下,可以使用被称为 case 语句的结构来实现多路选择器。这是一种更简单、更直观的大型多路选择器的实现方法。

下面的代码片段展示了如何使用 case 语句来实现一个简单的4选1多路选择器。

always @(*)case (addr) begin0 : beginmux_out = a; //当addr = 0时,执行这条语句end 1 : beginmux_out = b; //当addr = 1时,执行这条语句end2 : beginmux_out = c; //当addr = 2时,执行这条语句end3 : beginmux_out = d; //当addr = 3时,执行这条语句endendcase

endcase 语句很容易理解,因为它通过一个变量来选择要执行哪条分支语句。在case语句中,设计者可以包含尽可能多的不同分支。此外,应该使用默认(default )分支来实现那些未被列出来的case条件值。

为了将其用作多路选择器,变量将被用作地址引脚,然后可以根据正在执行的分支将对应的值赋给多路选择器的输出。

📣您有任何问题,都可以在评论区和我交流📃!

📣本文由 孤独的单刀 原创,首发于CSDN平台🐵,博客主页:wuzhikai.blog.csdn.net

📣您的支持是我持续创作的最大动力!如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!

相关文章:

Verilog使用always块实现时序逻辑

这篇文章将讨论 verilog 中一个重要的结构---- always 块(always block)。verilog 中可以实现的数字电路主要分为两类----组合逻辑电路和时序逻辑电路。与组合逻辑电路相反,时序电路电路使用时钟并一定需要触发器等存储元件。因此,…...

面向对象设计模式:行为型模式之迭代器模式

一、迭代器模式,Iterator Pattern aka:Cursor Pattern 1.1 Intent 意图 Provide a way to access the elements of an aggregate object sequentially without exposing its underlying representation. 提供一种按顺序访问聚合对象的元素而不公开其基…...

如何快速在企业网盘中找到想要的文件

现在越来越多的企业采用企业网盘来存储文档和资料,而且现在市面上的企业网盘各种各样。在使用企业网盘过程中,很多用户会问到企业网盘中如何快速搜索文件的问题。但是无论是“标签”功能还是普通的“关键词搜索”功能,都是单层级的࿰…...

香橙派5使用NPU加速yolov5的实时视频推理(二)

三、将best.onnx转为RKNN格式 这一步就需要我们进入到Ubuntu20.04系统中了,我的Ubuntu系统中已经下载好了anaconda,使用anaconda的好处就是可以方便的安装一些库,而且还可以利用conda来配置虚拟环境,做到环境与环境之间相互独立。…...

)

算法练习-二分查找(一)

算法练习-二分查找 1 代码实现 1.1 非递归实现 public int bsearch(int[] a, int n, int value) {int low 0;int high n - 1;while (low < high) {int mid (low high) / 2;if (a[mid] value) {return mid;} else if (a[mid] < value) {low mid 1} else {high …...

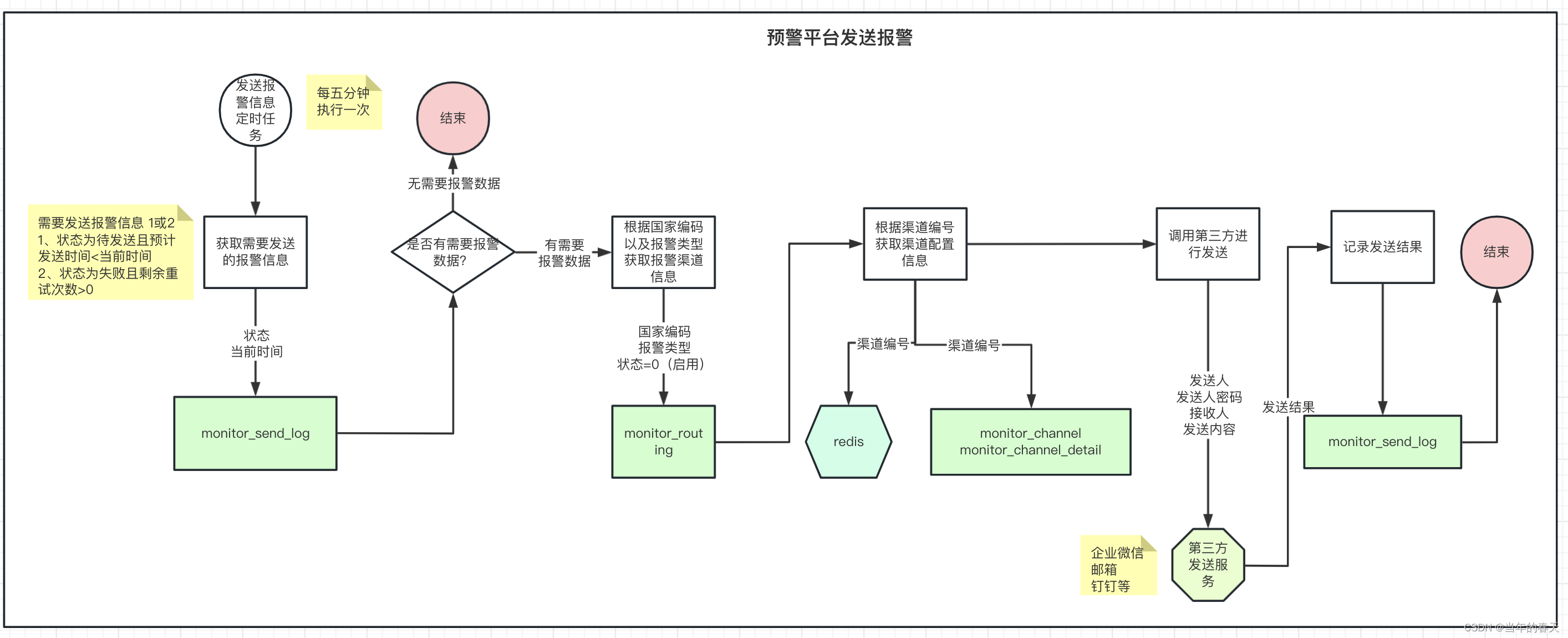

通用业务平台设计(五):预警平台建设

前言 在上家公司,随着业务的不断拓展(从支持单个国家单个主体演变成支持多个国家多个主体),对预警的诉求越来越紧迫;如何保障业务的稳定性那?预警可以帮我们提前甄别风险,从而让我们可以在风险来临前将其消灭ÿ…...

Windows openssl-1.1.1d vs2017编译

工具: 1. perl(https://strawberryperl.com/) 2. nasm(https://nasm.us/) 3. openssl源码(https://www.openssl.org/) 可以自己去下载 或者我的网盘提供下载: 链接:…...

【深蓝学院】手写VIO第2章--IMU传感器--笔记

0. 内容 1. 旋转运动学 角速度的推导: 左ω∧\omega^{\wedge}ω∧,而ω\omegaω是在z轴方向运动,θ′[0,0,1]T\theta^{\prime}[0,0,1]^Tθ′[0,0,1]T 两边取模后得到结论: 线速度大小半径 * 角速度大小 其中,对旋转矩…...

网络基础(二)之HTTP与HTTPS

应用层 再谈 "协议" 协议是一种 "约定". socket api的接口, 在读写数据时, 都是按 "字符串" 的方式来发送接收的. 如果我们要传输一些"结构化的数据" 怎么办呢? 为什么要转换呢? 如果我们将struct message里面的信息…...

Python每日一练(20230306)

目录 1. 翻转二叉树 ★★ 2. 最长公共前缀 ★★ 3. 2的幂 ★ 1. 翻转二叉树 翻转一棵二叉树。 示例 1: 输入: 4/ \2 7/ \ / \ 1 3 6 9 输出: 4/ \7 2/ \ / \ 9 6 3 1示例 2: 输入: 1…...

C/C++每日一练(20230305)

目录 1. 整数分解 ☆ 2. 二叉树的最小深度 ★★ 3. 找x ★★ 1. 整数分解 输入一个正整数,将其按7进制位分解为各乘式的累加和。 示例 1: 输入:49 输出:497^2示例 2: 输入:720 输出:720…...

SAS字典的应用

数据字典中常用信息检索DICTIONARY.COLUMNS、DICTIONARY.TABLES以及DICTIONARY.MEMBERS等字典表的内容。在编程实践中,如何以SAS字典表来提高效率。 1、DICTIONARY.COLUMNS 对于当前SAS任务的全部数据集,表格DICTIONARY.COLUMNS包含了诸如变量的名称、类…...

Mysql中的函数和触发器

函数函数是什么?多用于查询语句,实现了某种功能;用途与存储过程不同,但语法是类似的;函数语法create function 函数名([参数列表]) returns 数据类型 begin DECLARE 变量; sql 语句; return 值; end; 设置函…...

分布式架构之(Zookeeper原理)

Zookeeper是一个典型的分布式数据一致性的结局方案,分布式应用程序可以基于它实现注入数据发布、订阅、负载均衡、命名服务、分布式协调/通知、集群管理、Master选举、分布式锁和分布式队列等功能, Zookeeper可以保证如下分布式一致性特性: 顺…...

Java框架学习 | MyBatis

问题导向学习MyBatis 为什么要有MyBatis框架? 避免Java开发者直接使用 JDBC重复做数据库操作,同时更便捷地实现想要的数据库相关功能,让Java专注于开发业务。 MyBatis框架如何实现该目的? MyBatis是半自动化持久层ORM框架&#x…...

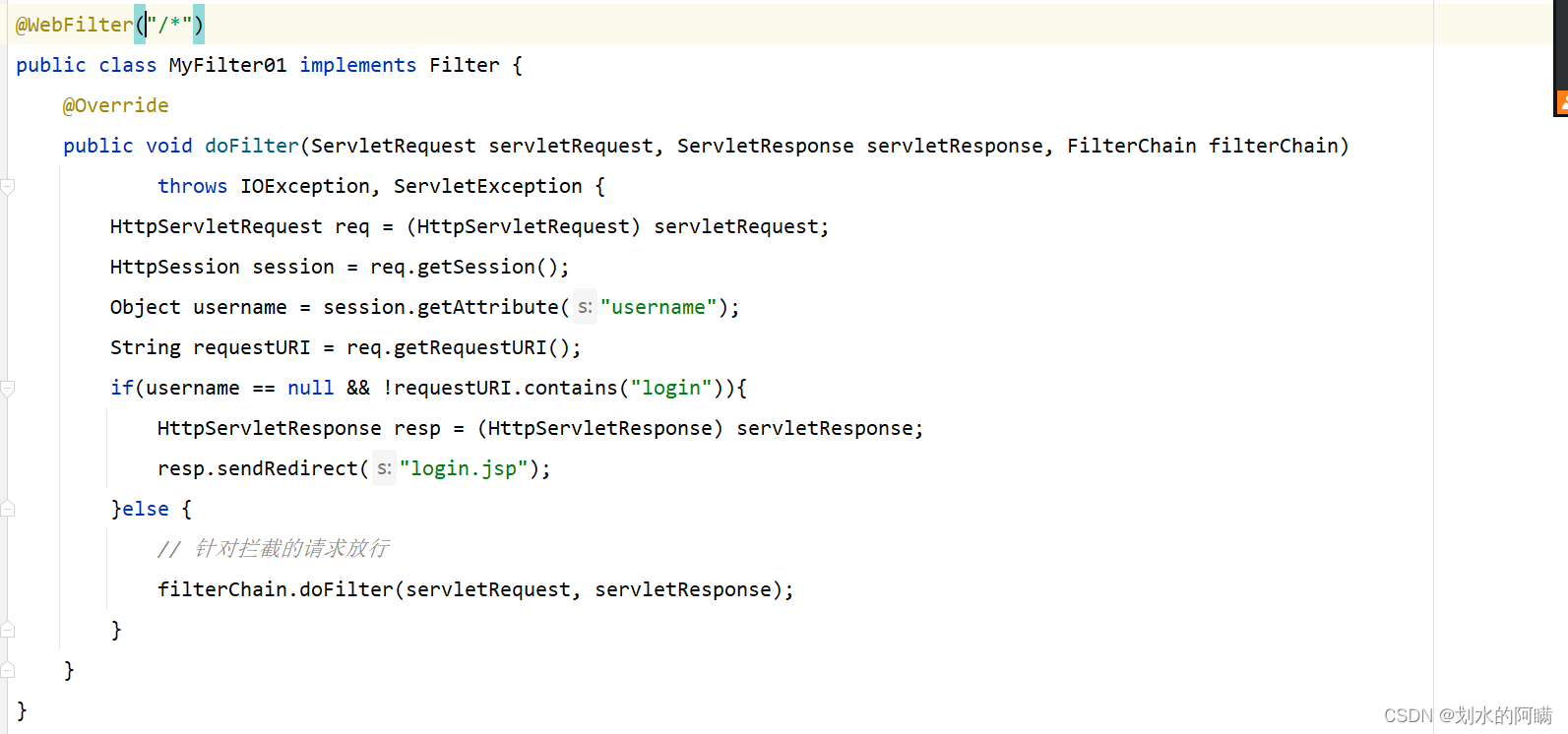

Cookie+Session详解

文章目录批量删除会话技术简介CookieCookie 查看Cookie 的删除Cookie 使用页面获取 cookie 信息cookie 特点Sessionsession 的使用Session 登录权限验证过滤器简介过滤器的使用WebFilter 注解过滤放行登录权限验证批量删除 servlet 类 dao 层 会话技术 简介 在计算机领域…...

CAPL脚本要注意区分elcount和strlen求数组长度的区别,不然要吃大亏

🍅 我是蚂蚁小兵,专注于车载诊断领域,尤其擅长于对CANoe工具的使用🍅 寻找组织 ,答疑解惑,摸鱼聊天,博客源码,点击加入👉【相亲相爱一家人】🍅 玩转CANoe&…...

CSS常用选择器

目录 1.CSS是什么 2.CSS的三种写法 2.1内部样式 2.2内联样式 2.3外部样式 3.CSS选择器 3.1标签选择器 3.2类选择器(更好的选择) 3.3ID选择器 3.4后代选择器 3.5子选择器 3.6并集选择器 3.7伪类选择器(复合选择器的特殊用法) 1.CSS是什么 CSS全称Cascding Style Sh…...

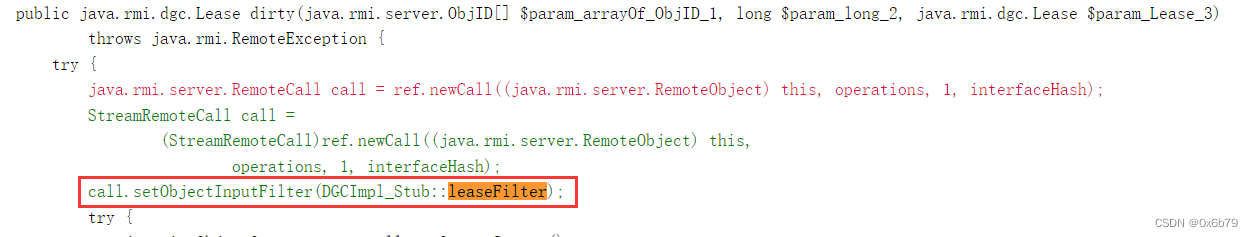

Registry与DGC的攻击利用

0x01 2022-02-03写的一篇文章。 0x02 Registry Registry指的是RMI的注册表,攻击的目标是注册表所在的机器,一般注册表和RMI Server在同一个机器上,特殊情况下也会在不同机器上。 在我们通过LocateRegistry#getRegistry获取到目标开启的注…...

赛道持续降温!又一家自动驾驶公司裁员,市值曾超50亿美元

从去年下半年开始,自动驾驶赛道的裁员、倒闭风潮盛行。 本周,美股卡车自动驾驶上市公司Embark Trucks(EMBK)宣布将裁员70%,同时大幅缩减业务。“痛苦可能还没有结束,”公司首席执行官Alex Rodrigues在给员…...

Adobe-GenP终极指南:5分钟破解Adobe创意套件限制的完整教程

Adobe-GenP终极指南:5分钟破解Adobe创意套件限制的完整教程 【免费下载链接】Adobe-GenP Adobe CC 2019/2020/2021/2022/2023 GenP Universal Patch 3.0 项目地址: https://gitcode.com/gh_mirrors/ad/Adobe-GenP 你是否曾因为Adobe Creative Cloud高昂的订阅…...

别再死记硬背了!用Python模拟超前进位加法器,直观理解其速度优势

用Python模拟超前进位加法器:从硬件原理到算法思维的跨越 在计算机科学和电子工程交叉领域,加法器是最基础却又最精妙的设计之一。传统教学中,我们往往通过抽象的电路图来理解超前进位加法器(CLA)的速度优势࿰…...

DownKyi完全指南:三步解锁B站8K视频下载的终极方案

DownKyi完全指南:三步解锁B站8K视频下载的终极方案 【免费下载链接】downkyi 哔哩下载姬downkyi,哔哩哔哩网站视频下载工具,支持批量下载,支持8K、HDR、杜比视界,提供工具箱(音视频提取、去水印等ÿ…...

UEFITool终极指南:轻松解析和编辑UEFI固件的开源利器

UEFITool终极指南:轻松解析和编辑UEFI固件的开源利器 【免费下载链接】UEFITool UEFI firmware image viewer and editor 项目地址: https://gitcode.com/gh_mirrors/ue/UEFITool 你是否曾好奇计算机启动时底层发生了什么?想要深入了解UEFI固件的…...

终极指南:如何在Mac上免费快速导出微信聊天记录

终极指南:如何在Mac上免费快速导出微信聊天记录 【免费下载链接】WeChatExporter 一个可以快速导出、查看你的微信聊天记录的工具 项目地址: https://gitcode.com/gh_mirrors/wec/WeChatExporter 你是否曾因误删重要微信聊天记录而焦虑?或需要查找…...

Copaw_dev:AI编程助手增强框架,提升代码生成与自动化开发效率

1. 项目概述:Copaw_dev 是什么,以及它为何值得关注如果你是一名开发者,尤其是对自动化、代码生成或者AI辅助编程感兴趣,那么“Copaw_dev”这个项目标题很可能已经引起了你的注意。乍一看,这个由“G-Divine”维护的项目…...

从开源AI导师项目GURU-Ai拆解:如何构建具备教学能力的智能体

1. 项目概述:一个“AI导师”的诞生与定位最近在GitHub上看到一个挺有意思的项目,叫“Guru322/GURU-Ai”。光看名字,你可能会觉得这又是一个平平无奇的AI工具仓库。但点进去细看,你会发现它的野心不小——它想做的不是又一个聊天机…...

企业级后端四层架构实战:从理论到代码的清晰落地

1. 项目概述:一个四层架构的实战蓝图最近在GitHub上看到一个挺有意思的项目,叫BTawaifi/four-layer-system。光看名字,你可能会觉得这又是一个老生常谈的“四层架构”理论教程,无非是Controller、Service、Repository那套东西。但…...

Grad-CAM实战:用热力图透视神经网络的决策焦点

1. Grad-CAM技术初探:为什么我们需要热力图? 当你训练了一个图像分类模型,准确率高达95%,但你真的了解它是如何做出判断的吗?我曾在项目中遇到过这样的尴尬:模型把一只坐在草地上的哈士奇误判为"狼&qu…...

Arm Iris组件参数化建模与调试实践

1. Arm Iris组件概述与核心价值Arm Iris组件是Fast Models仿真平台中的关键模块,它为芯片设计验证和软件开发提供了高度参数化的虚拟原型环境。作为一名长期从事Arm架构开发的工程师,我发现Iris组件的设计理念完美体现了"配置即硬件"的思想——…...