Xilinx 7系列FPGA配置(ug470)

Xilinx 7系列FPGA配置(ug470)

- 配置模式

- 串行配置模式

- 接口

- 从-连接方式

- 主-连接方式

- 串行菊花链(非同时配置)

- 串行配置(同时配置)

- 时序

- 主SPI配置模式

- SPIx1/x2 连接图

- SPIx1模式时序

- SPIx4 连接图

- SPI操作指令

- 操作flash空间大于128Mb

- SPI配置时序

- SPI最大速率计算

- 上电顺序要求

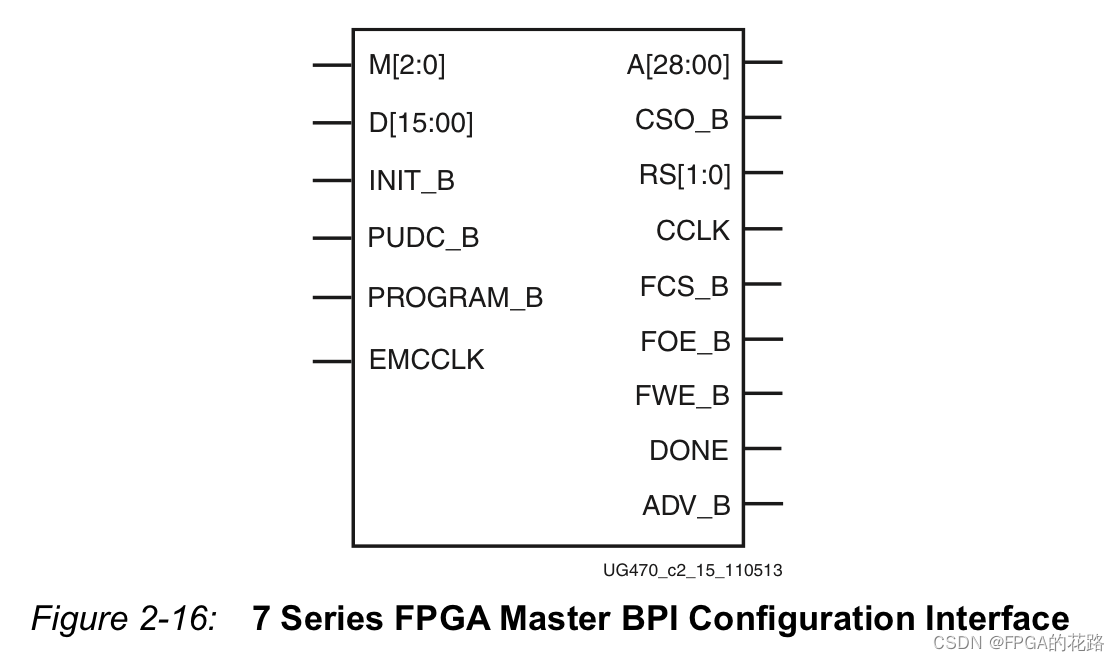

- 主BPI配置模式

- 接口

- 异步读取模式

- 连接图

- 时序

- 同步读取模式

- 连接图

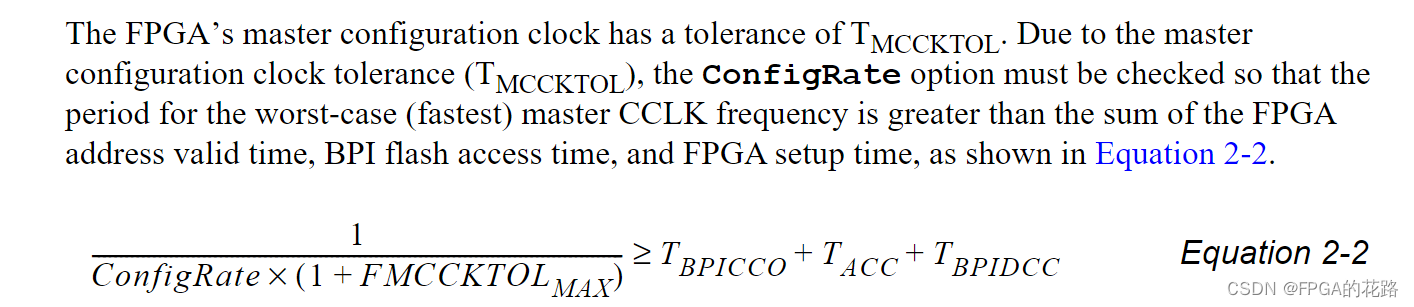

- 最大配置速率计算

- 上电顺序要求

- SelectMAP 配置模式

- 简介

- 接口

- Data Ordering

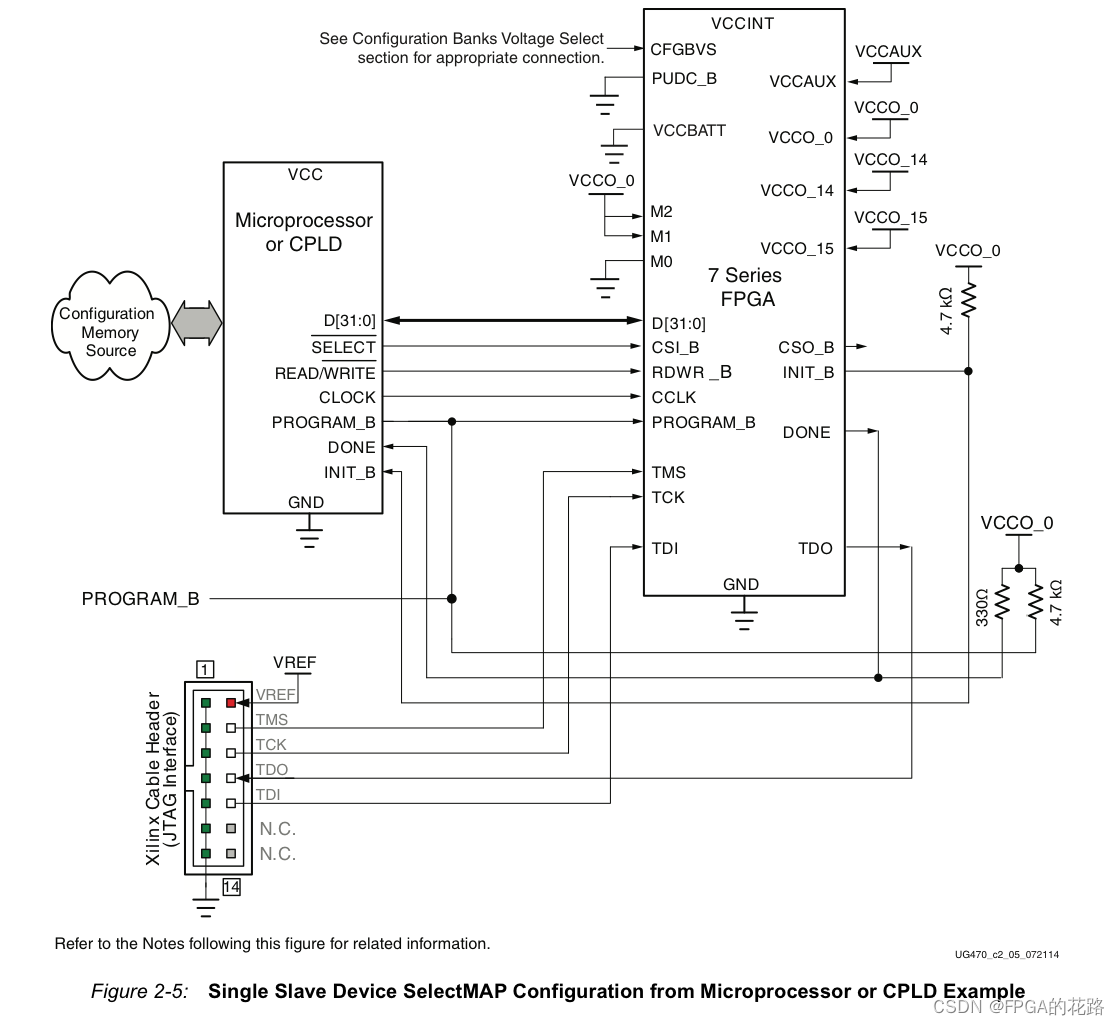

- 单器件配置模式

- 连接示例

- 数据加载

- 连续配置时序

- 非连续配置时序

- 终止操作

- 时序

- 状态字定义

- 状态字数据对齐

- 多器件SelectMAP独立配置

- 多器件SelectMAP同时配置

- 并行菊花链配置

- JTAG配置模式

- 配置引脚

- CVGBVS

- PROGRAM_B

- INIT_B

- PUDC_B

- VCCBATT

- RS0, RS1

- RDWR_B

- FCS_B

- FOE_B

- FWE_B

- Configuration Details

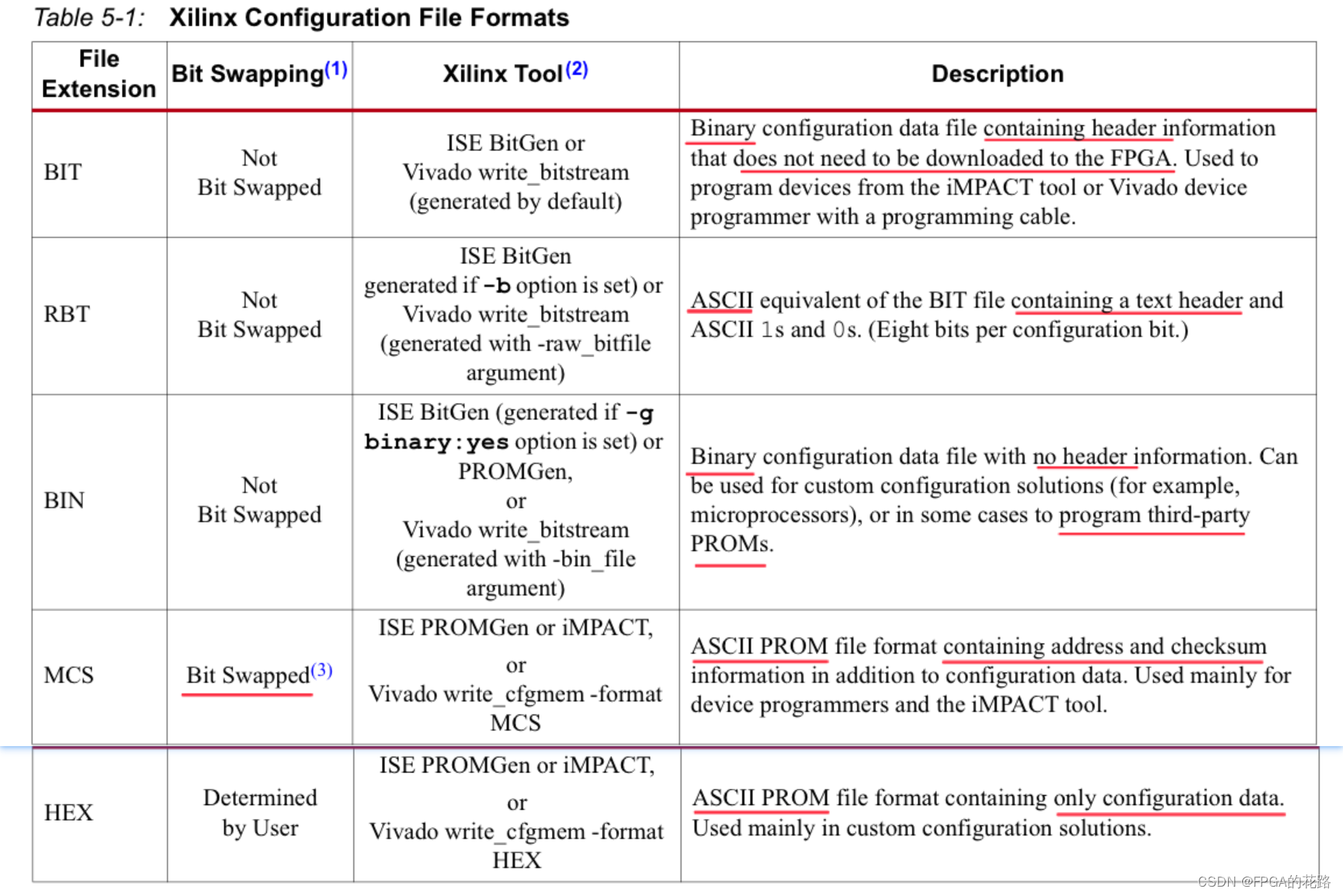

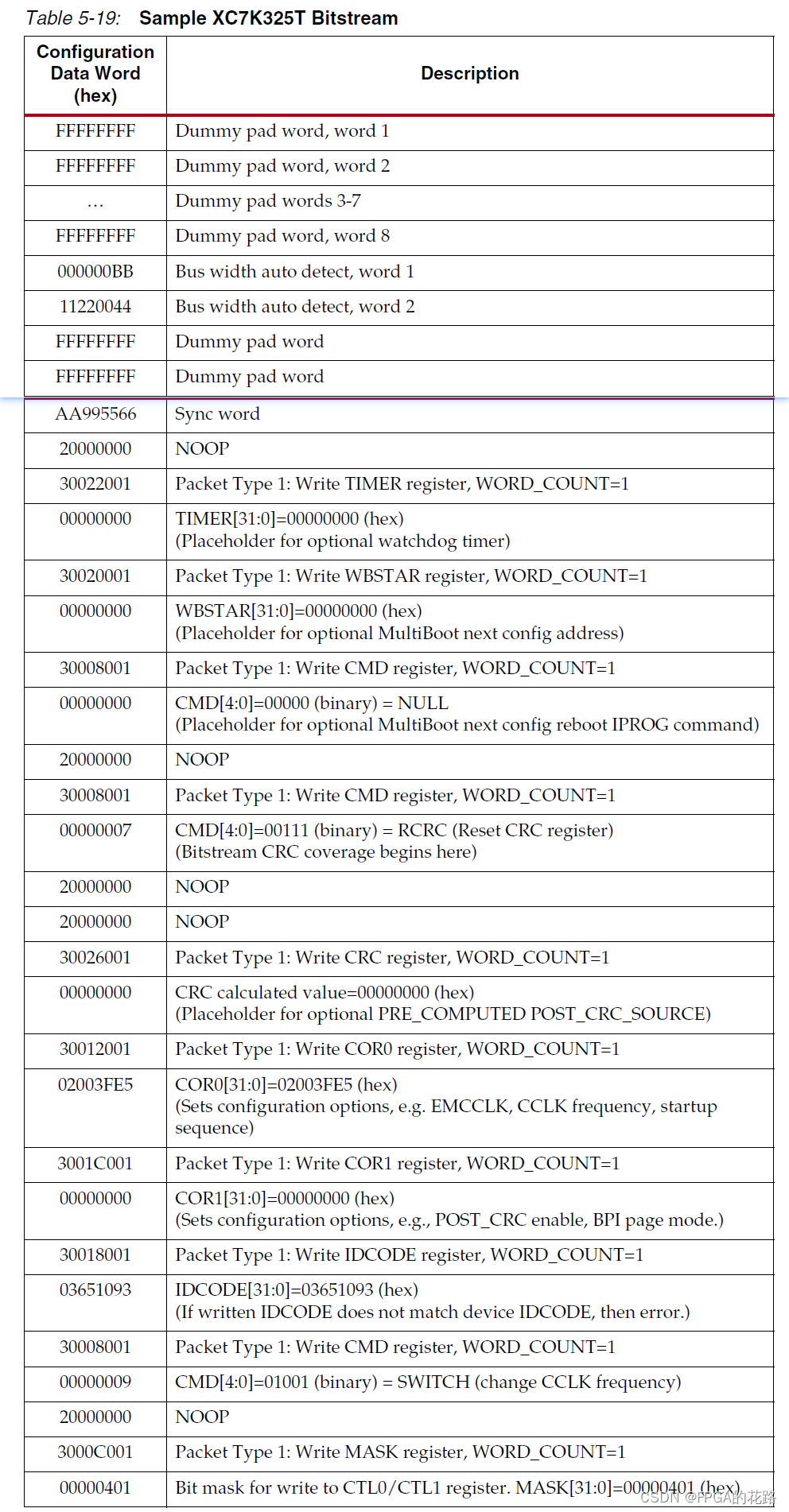

- 配置文件格式

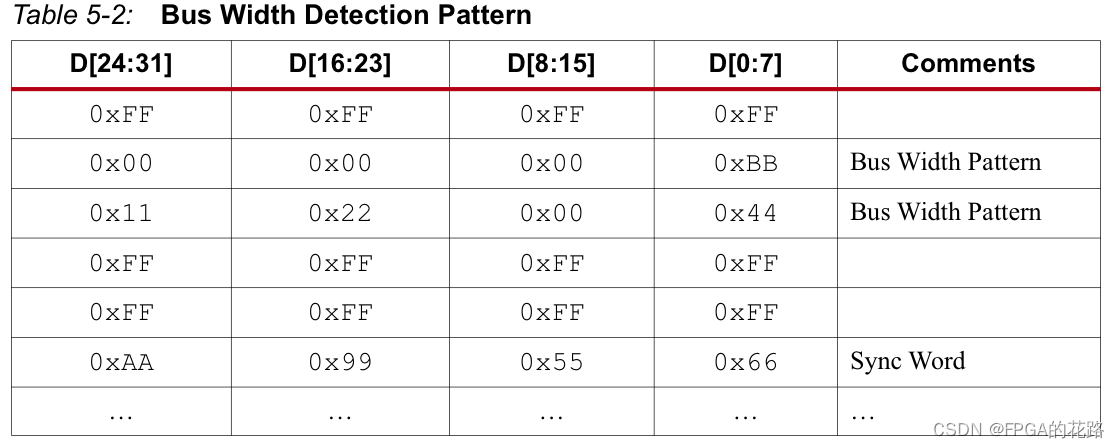

- 总线位宽自动检测

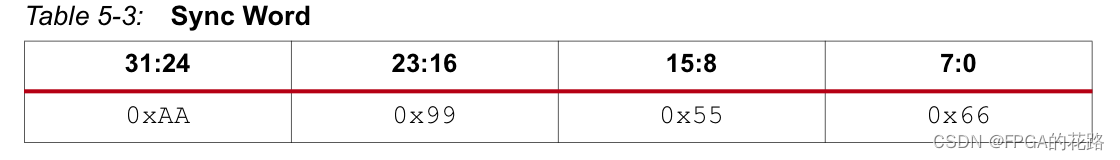

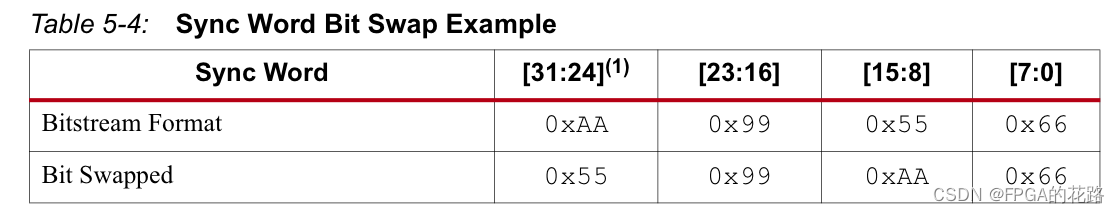

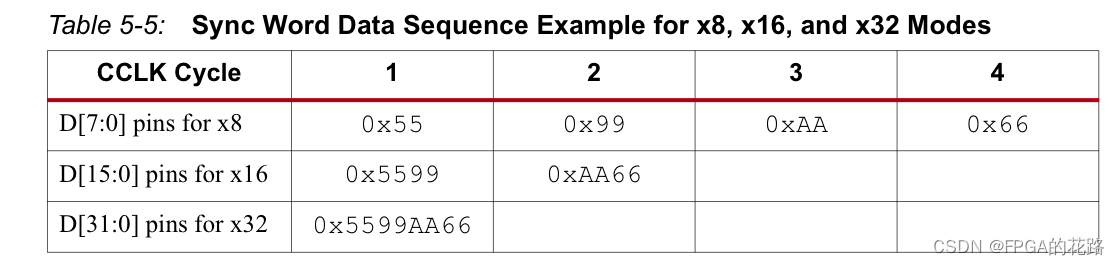

- 同步字

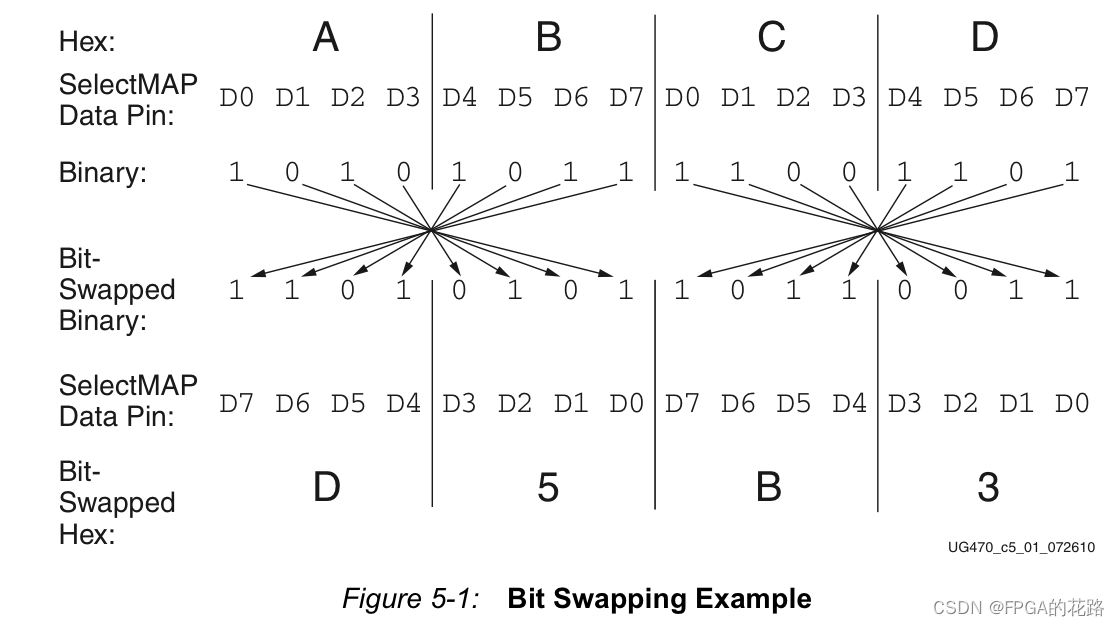

- 位交换和总线字序

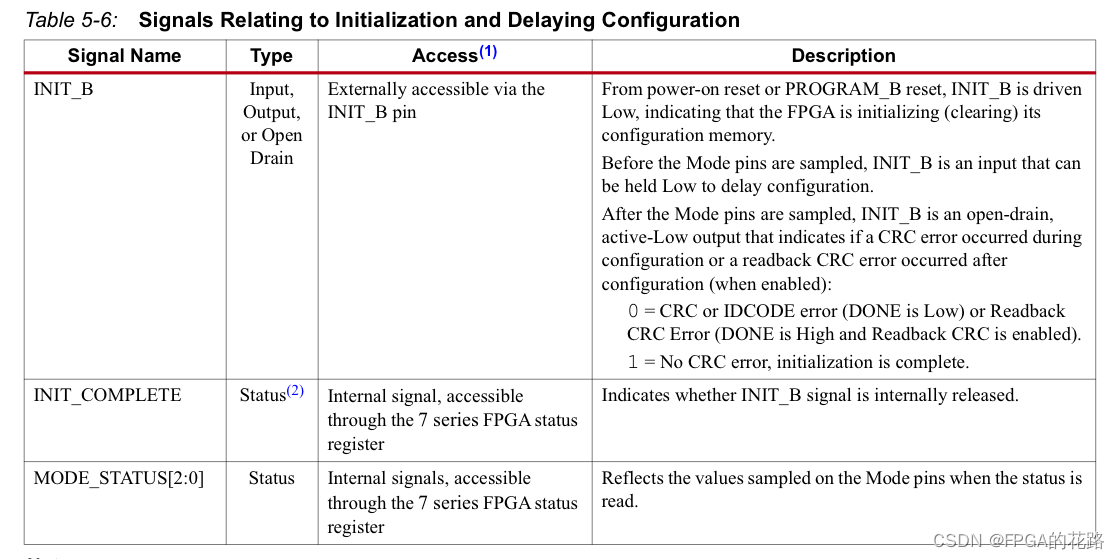

- 延迟配置

- 延迟相关信号

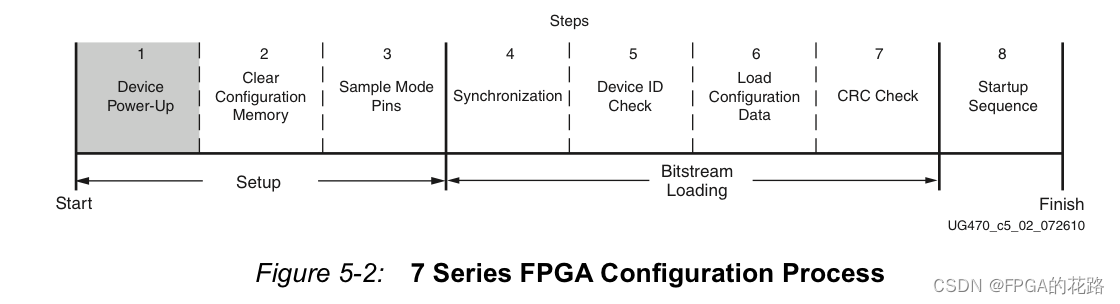

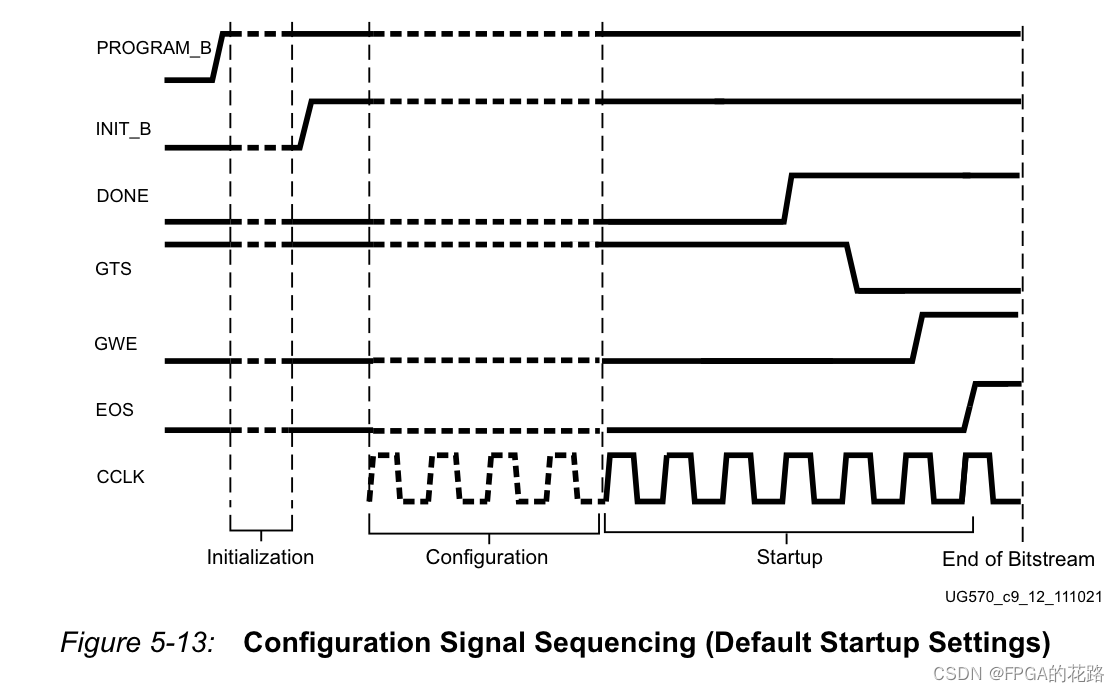

- 配置顺序

- Setup

- Device Power-Up (Step 1)

- Clear Configuration Memory (Step 2, Initialization)

- Sample Mode Pins (Step 3)

- Bitstream Loading

- Synchronization (Step 4)

- Check Device ID (Step 5)

- Load Configuration Data Frames (Step 6)

- Cyclic Redundancy Check (Step 7)

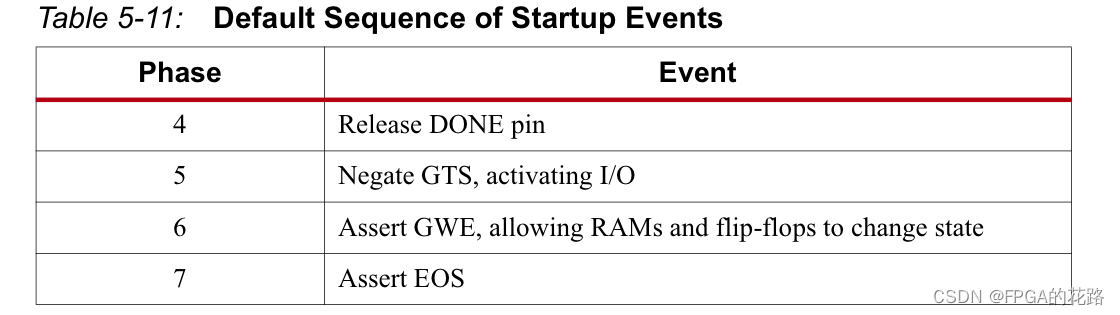

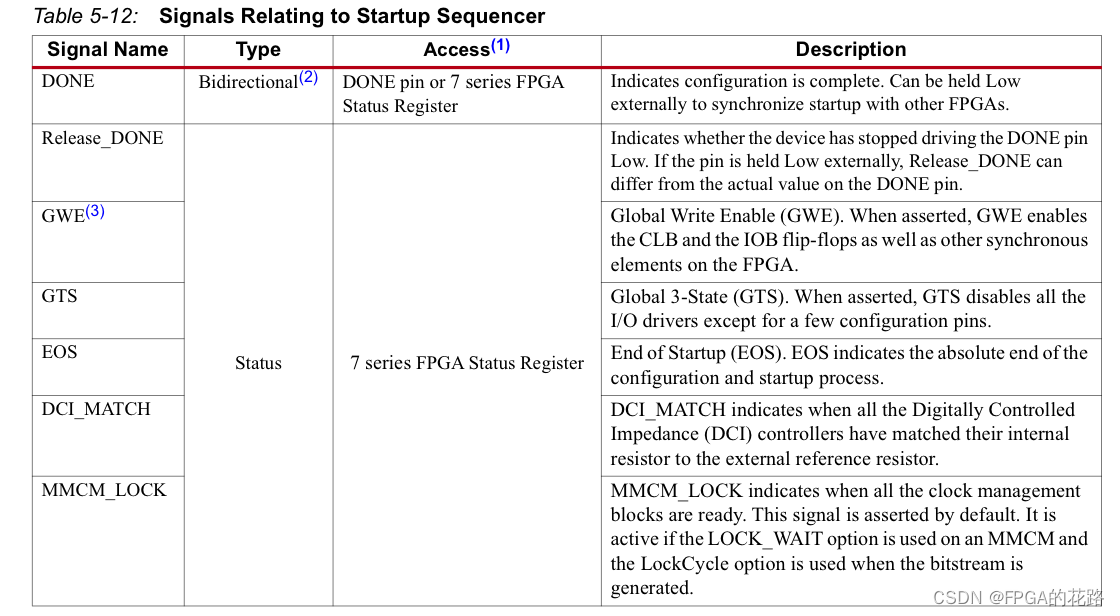

- Startup

- 配置过程I/O电平变化(EOS)

- STARTUPE2原语

- Bitstream Security

- Bitstream Composition

- 配置寄存器

- 重配置和多镜像

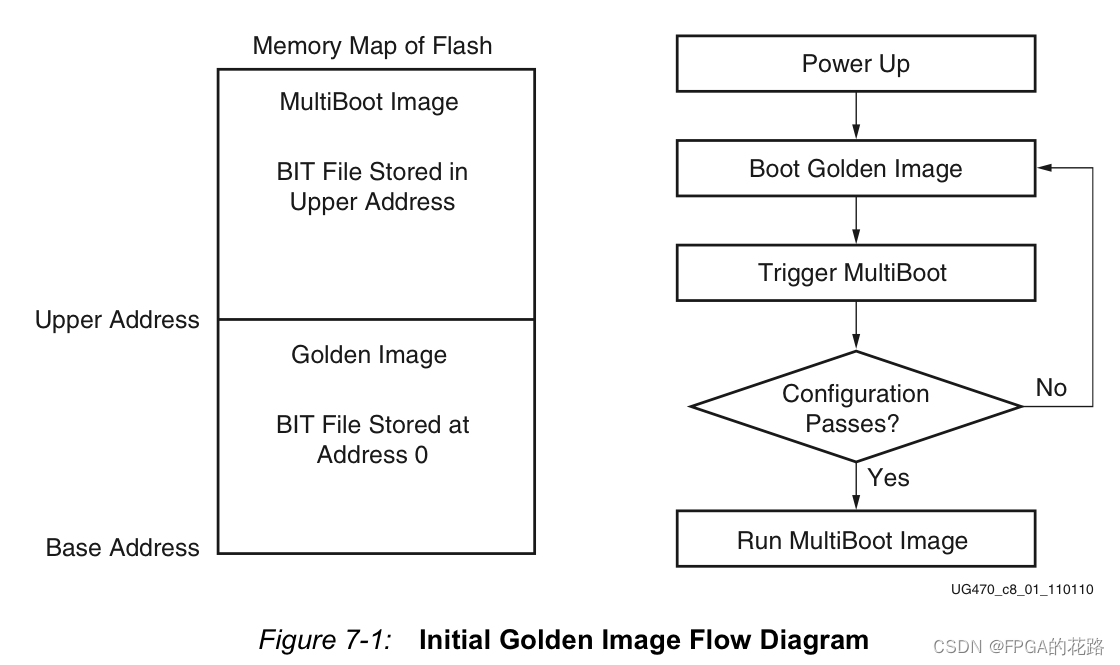

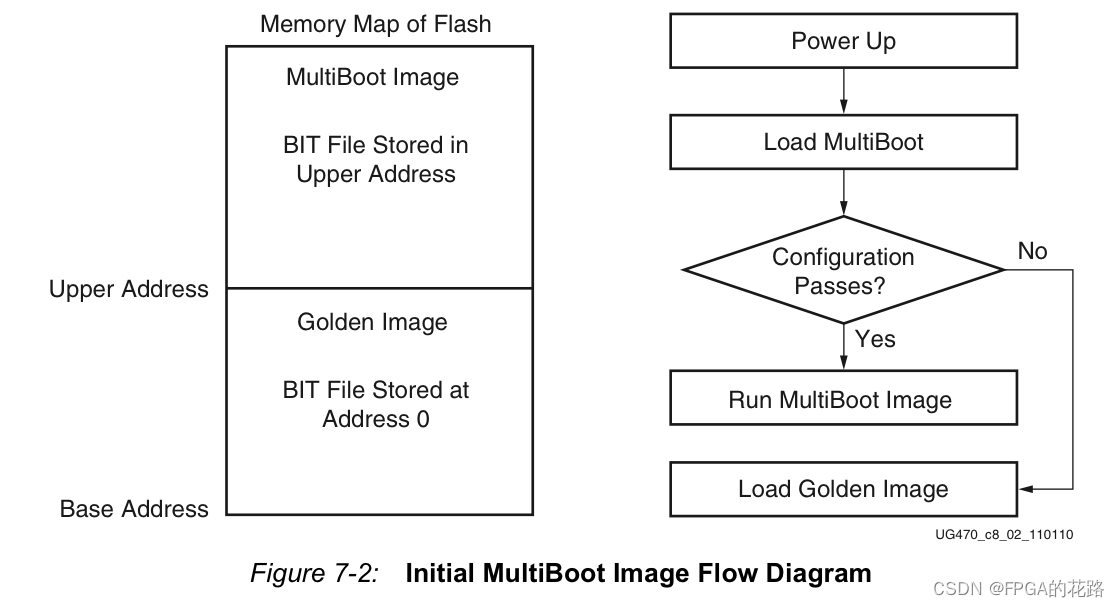

- Fallback MultiBoot

- 先加载golden再触发MultiBoot

- 直接加载MultiBoot

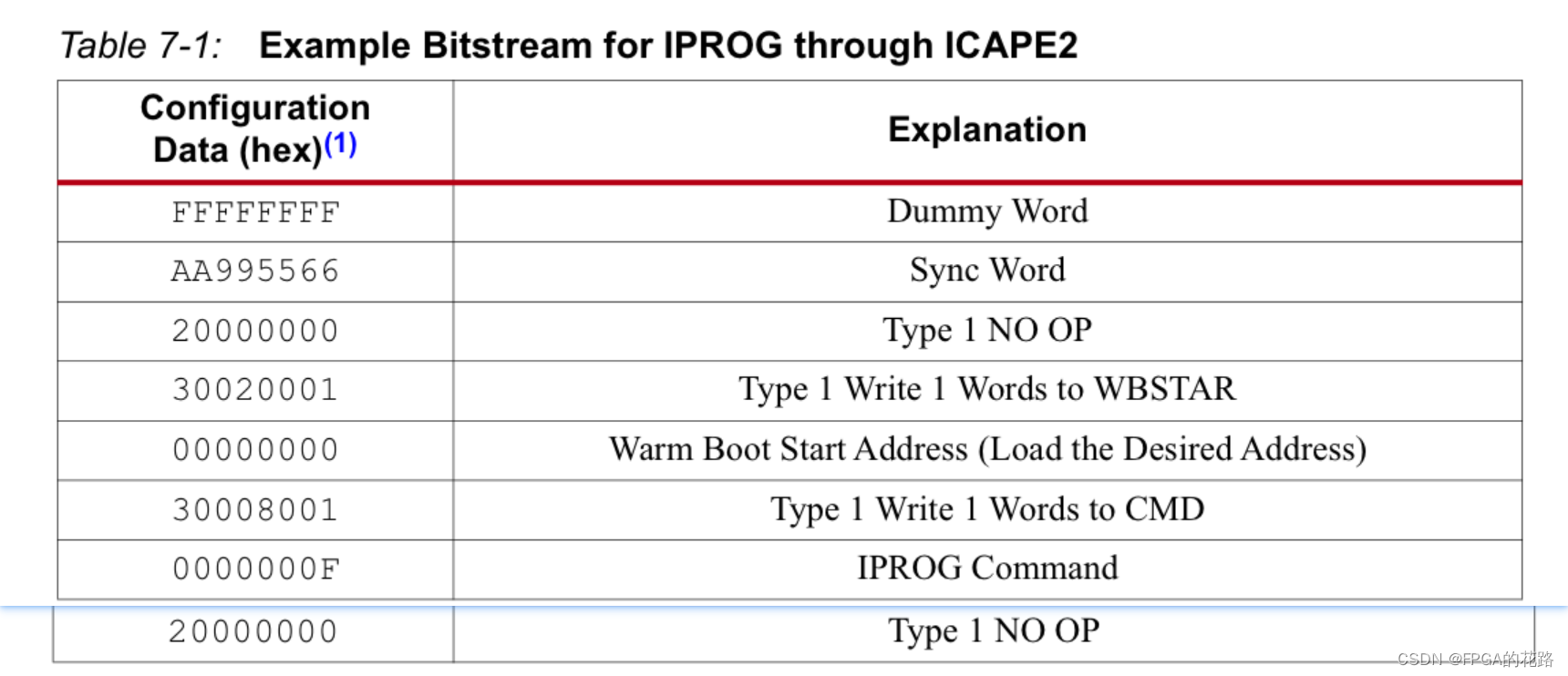

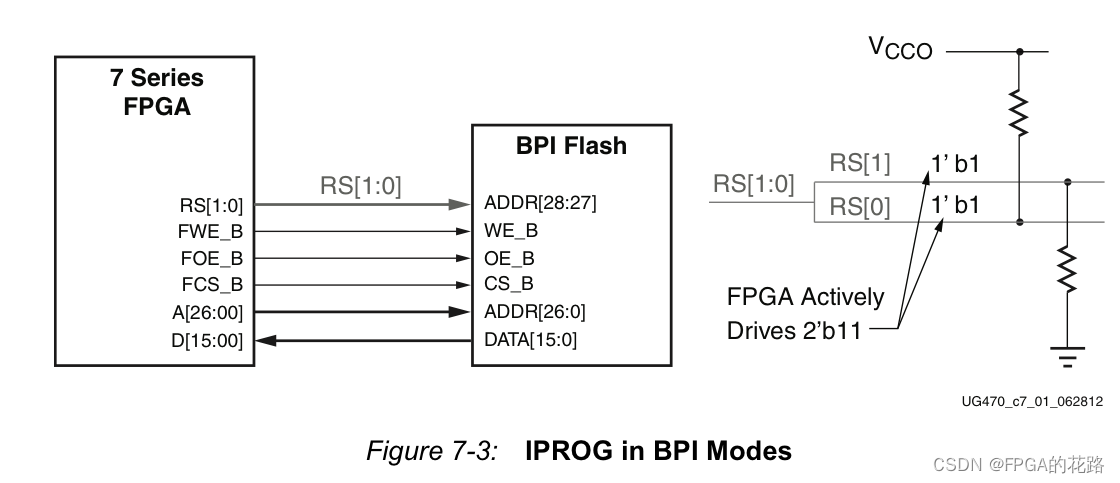

- IPROG

- IPROG Using ICAPE2

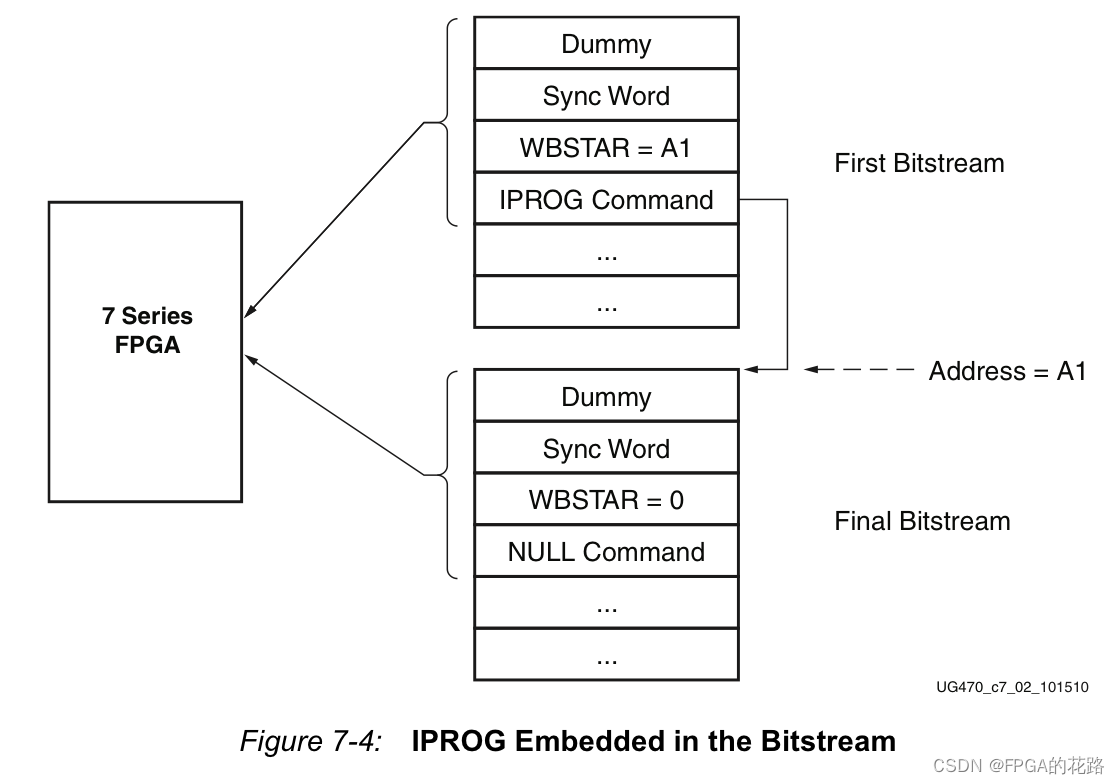

- IPROG Embedded in the Bitstream

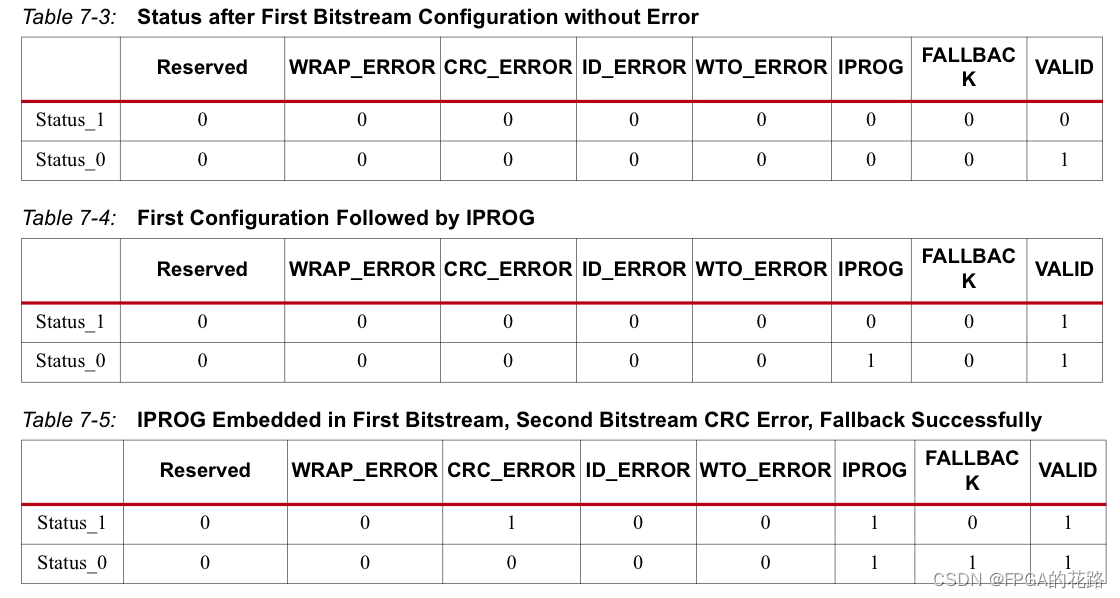

- Status Register for Fallback and IPROG Reconfiguration

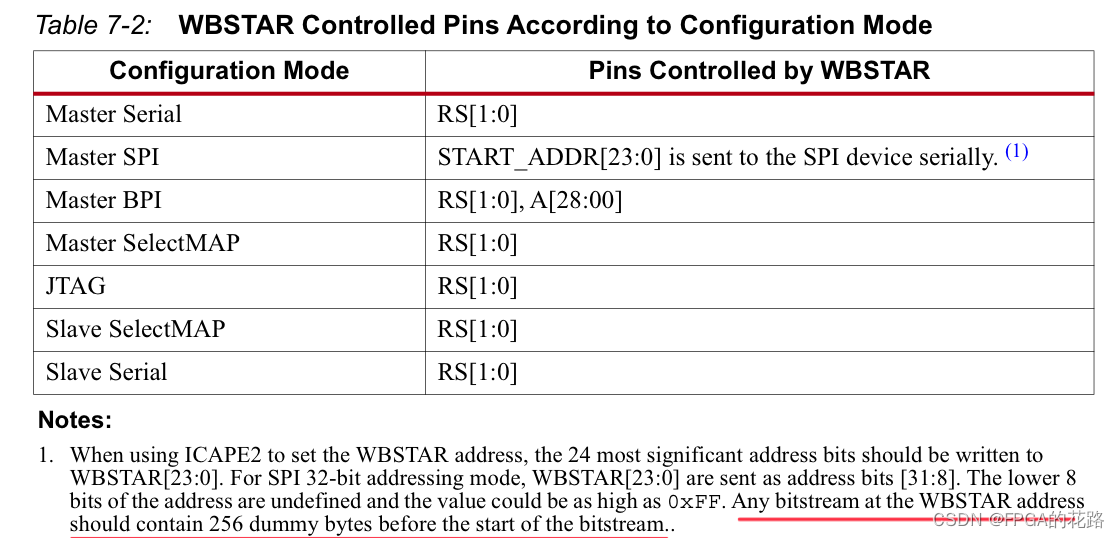

- WBSTAR Register

- Watchdog Timer

- Configuration Monitor Mode

- User Monitor Mode

- RS Pins

- JTAG高级用法

- 参考文献

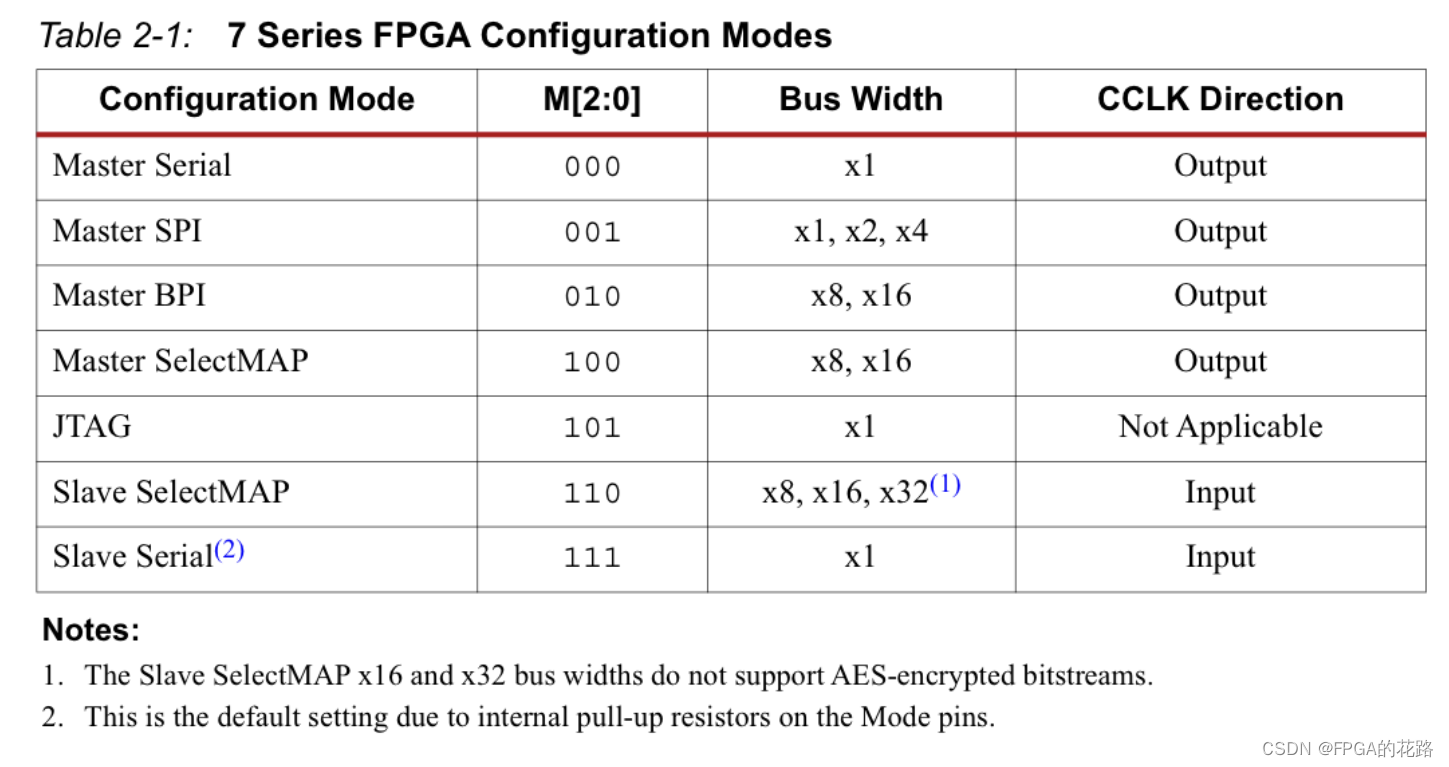

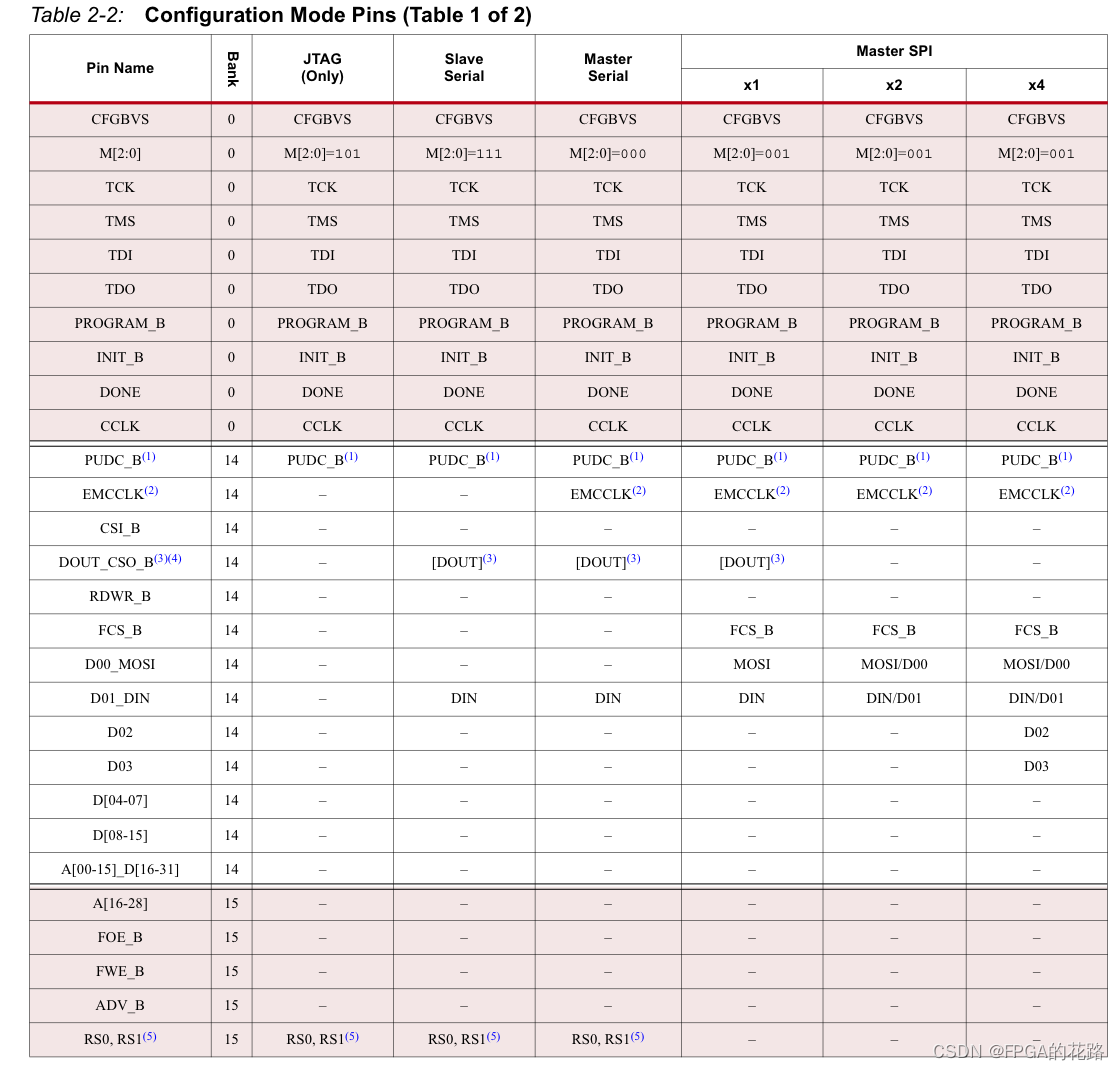

配置模式

如果 M[2:0] 为 ”101“,则该FPGA 只支持 JTAG 进行配置。处于其余配置模式下时,依旧可以使用 JTAG 模式进行调试,并且优先级最高。

串行配置模式

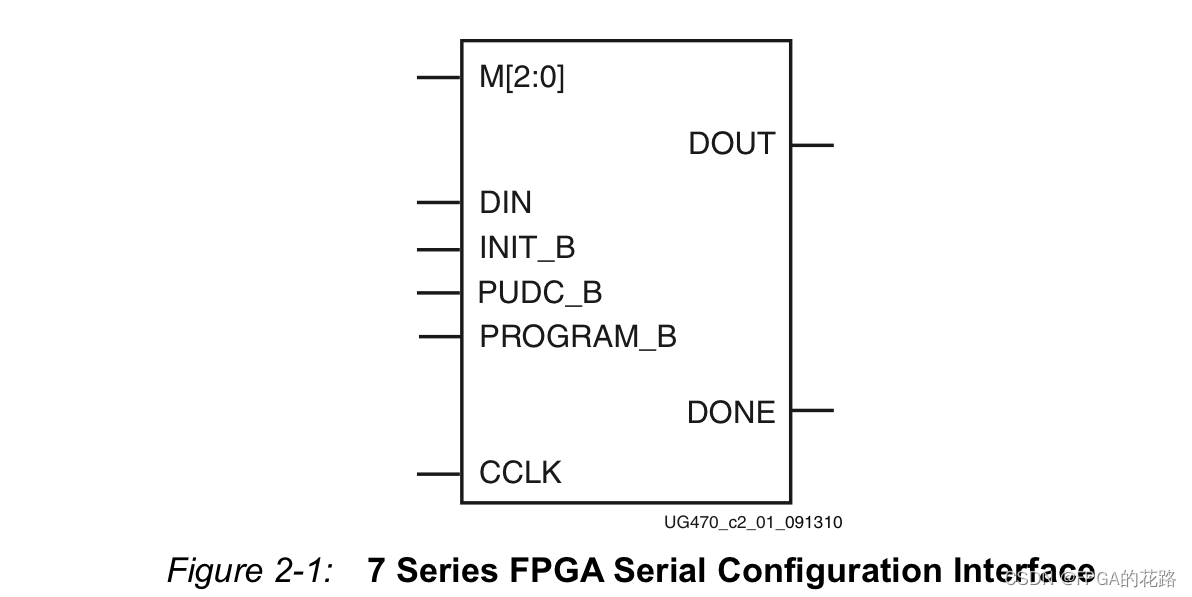

接口

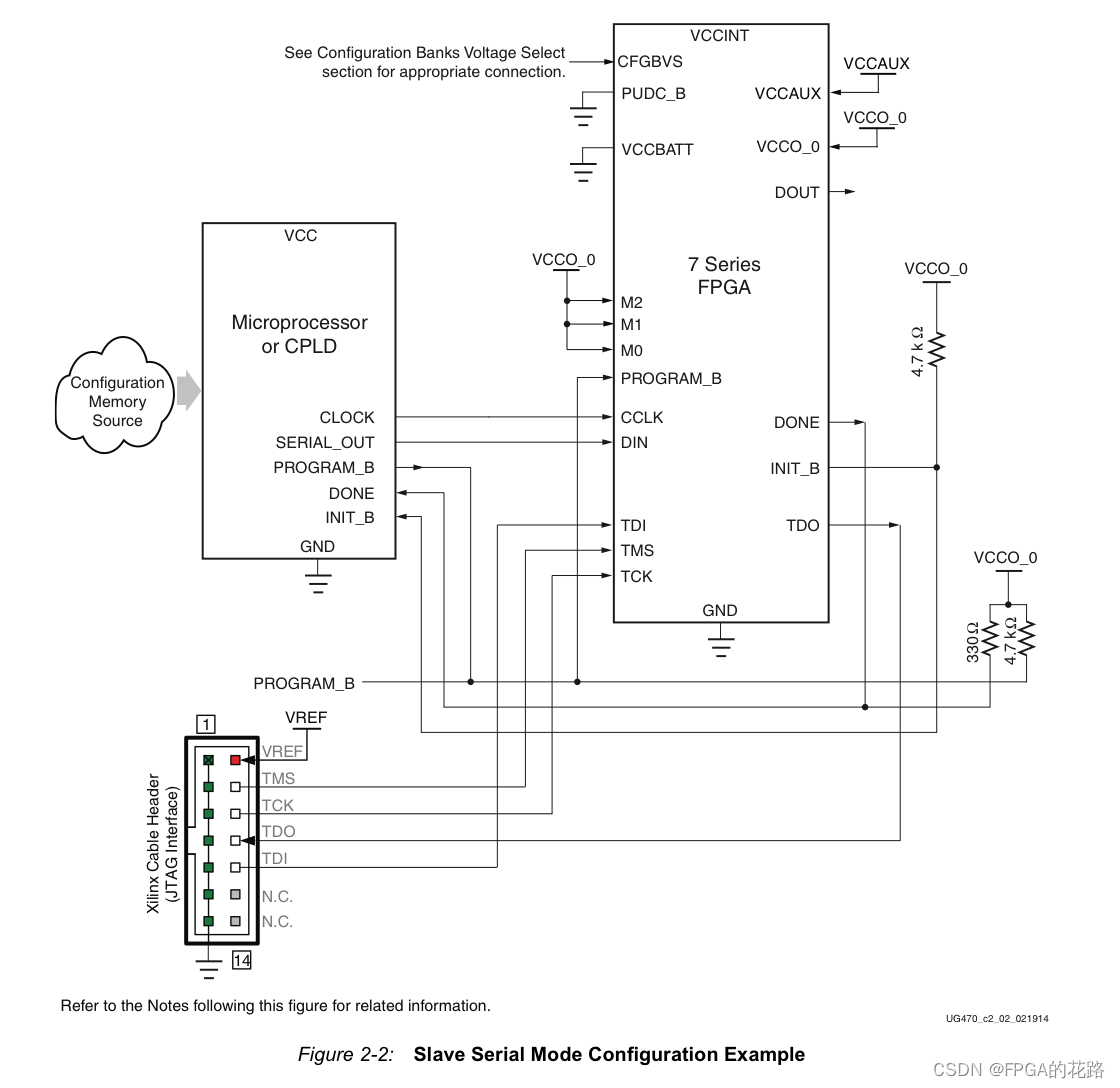

从-连接方式

主-连接方式

- 除了CCLK 连接不同,其他都和从串行模式一样

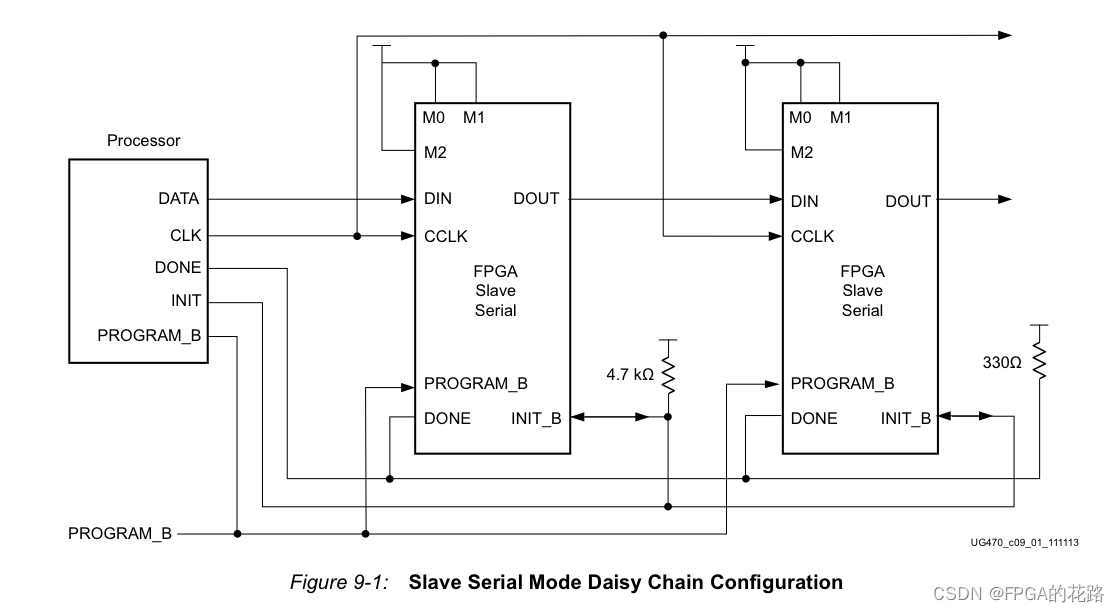

串行菊花链(非同时配置)

- 上升沿采样DIN数据,下降沿DOUT输出数据,形成上下流关系;

- SPI 在该连接方式下不支持重配置功能;

- 第一个器件最后完成配置;当链中最远端器件完成配置,则将DONE变为高阻态,这样下一个器件检测到DONE为高则开始配置;

- 7系列必须放在第一个;

- DOUT传输的总数据量有限制,所以要根据程序大小计算好可以连接的器件个数

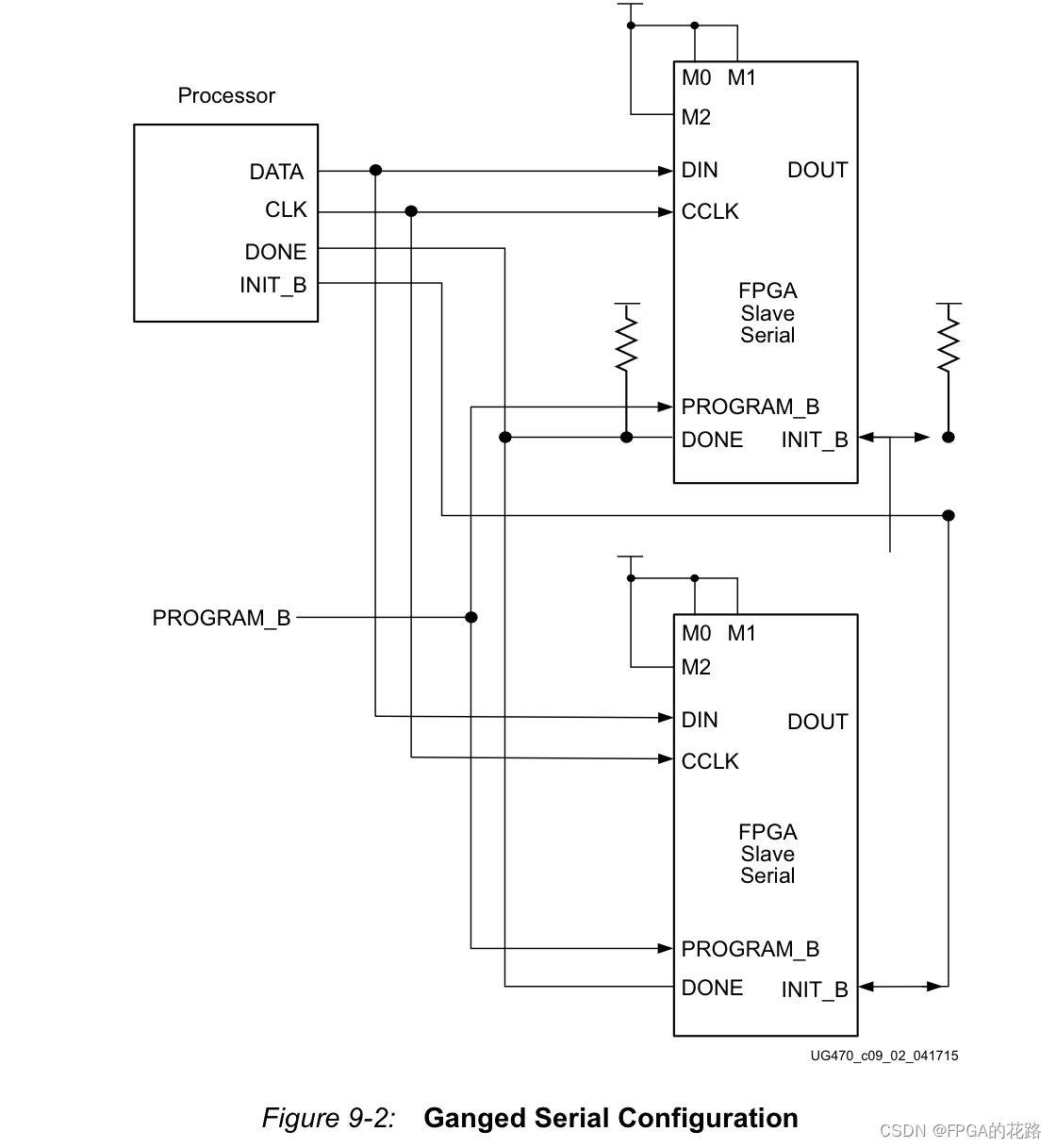

串行配置(同时配置)

- 所有器件要一样(IDCODE一样),配置程序也一样

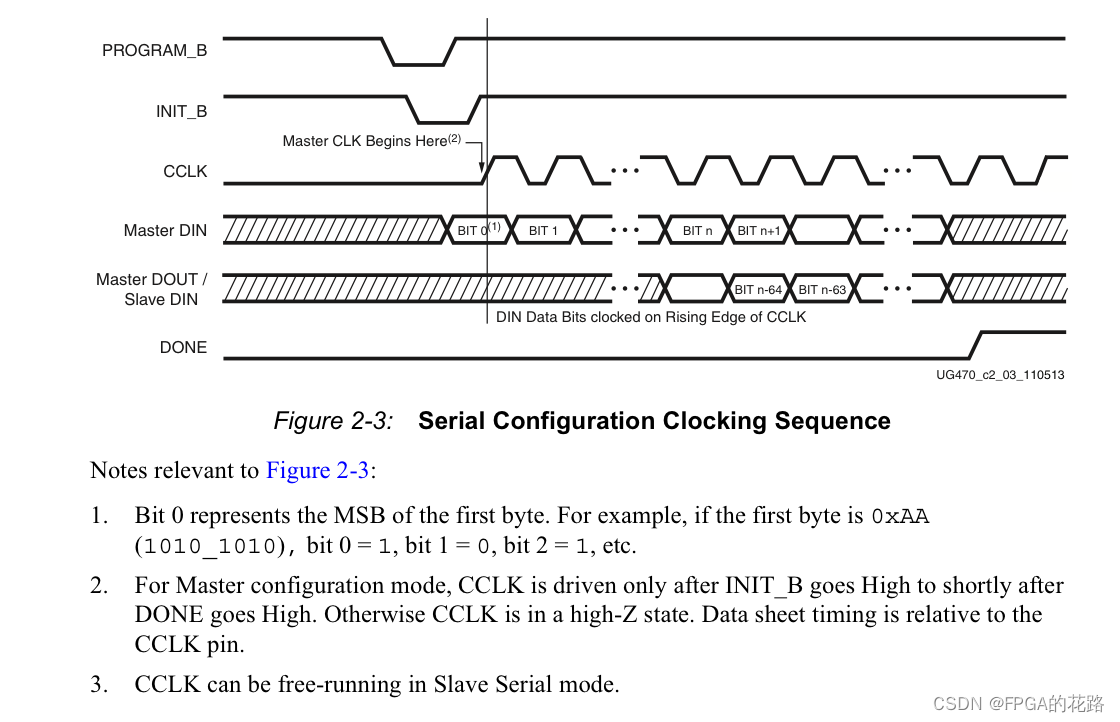

时序

主SPI配置模式

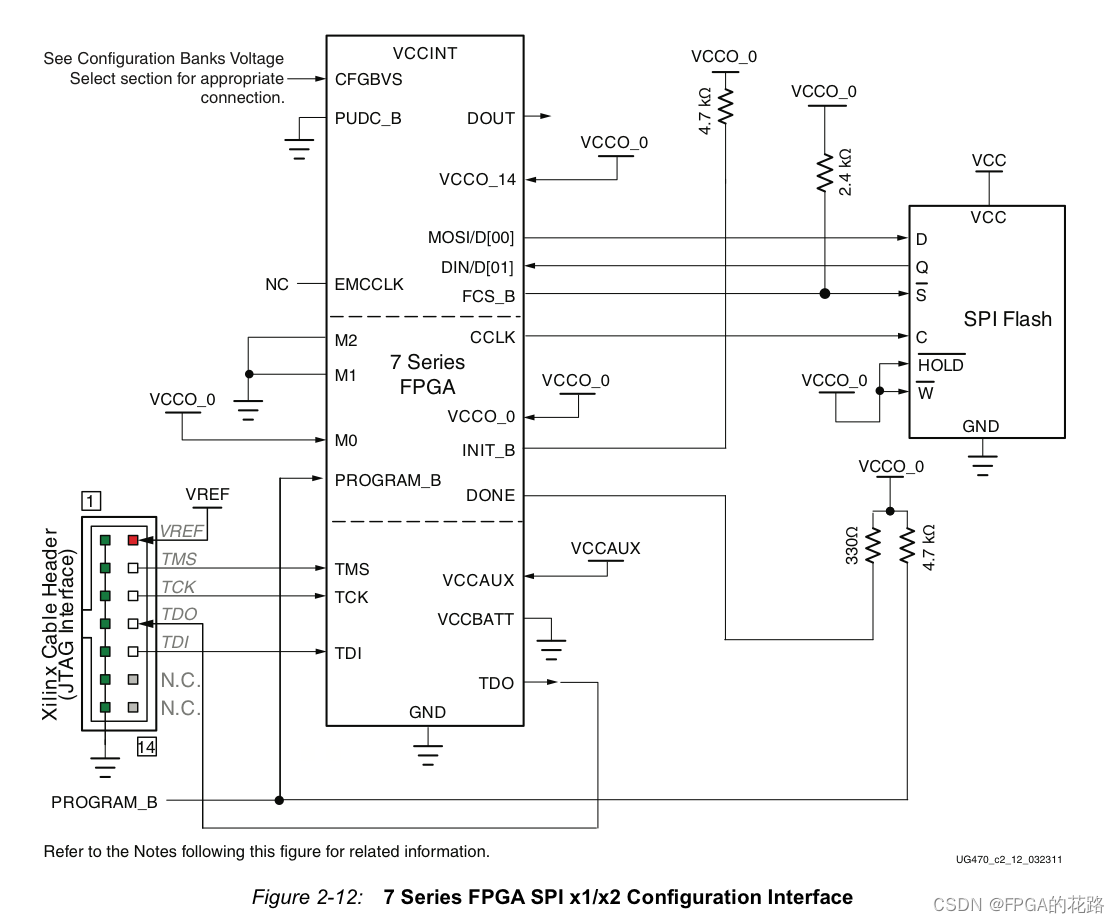

SPIx1/x2 连接图

- INIT_B 需要外部上拉电阻;

- 菊花链模式不支持SPIx2和x4,DOUT连接下个器件的DIN形成菊花链;

- FPGA VCCO_0 要适配 FLASH器件的VCC;

- 默认SPI器件在CCLK下降沿锁存数据,FPGA在上升沿采样数据(可以通过配置SPI_FALL_EDGE属性更改为下降沿采样);

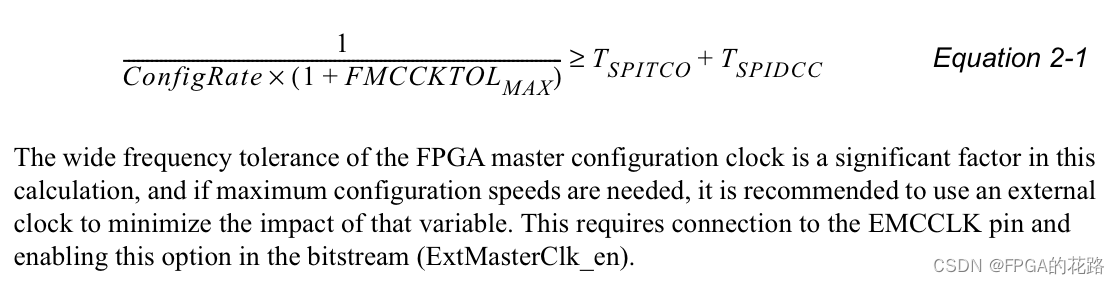

- 可通过ConfigRate属性调节CCLK频率;可通过ExtMasterCclk_en属性使能外部输入时钟EMCCLK作为CCLK源使用;

- VCCBATT用于AES密钥存储,需要时连接

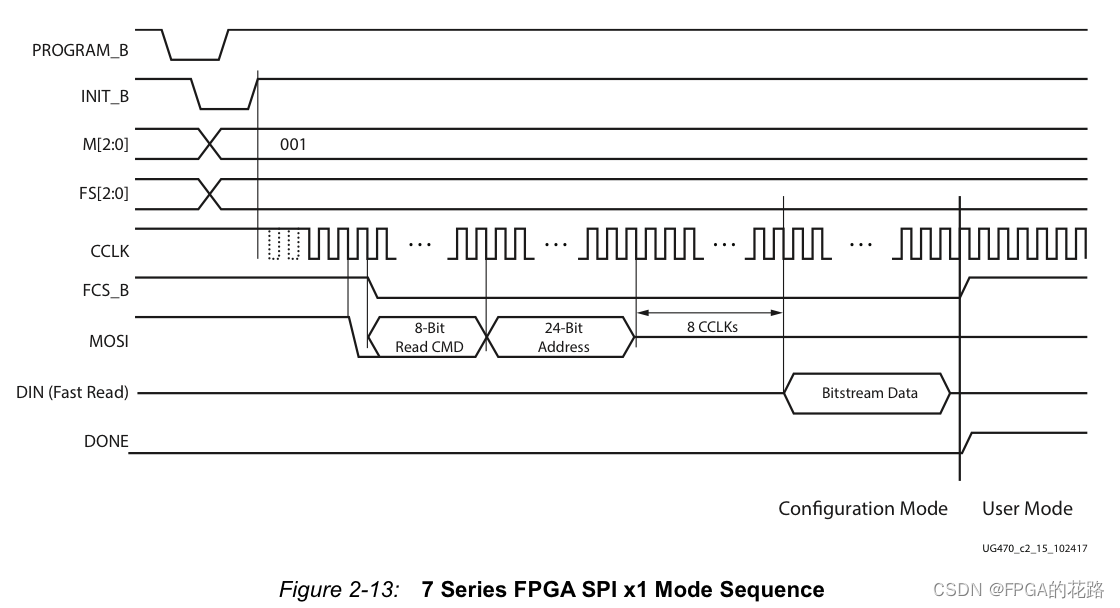

SPIx1模式时序

- CCLK初始始终为3MHz,配置ConfigRate只有在读写数据时生效,写地址和指令时不生效;

- SPI FLASH在配置后不使用,建议将FCS_B拉高;

- PUDC_B为低,在写完读指令和地址后,MOSI需要拉高或者为高阻态

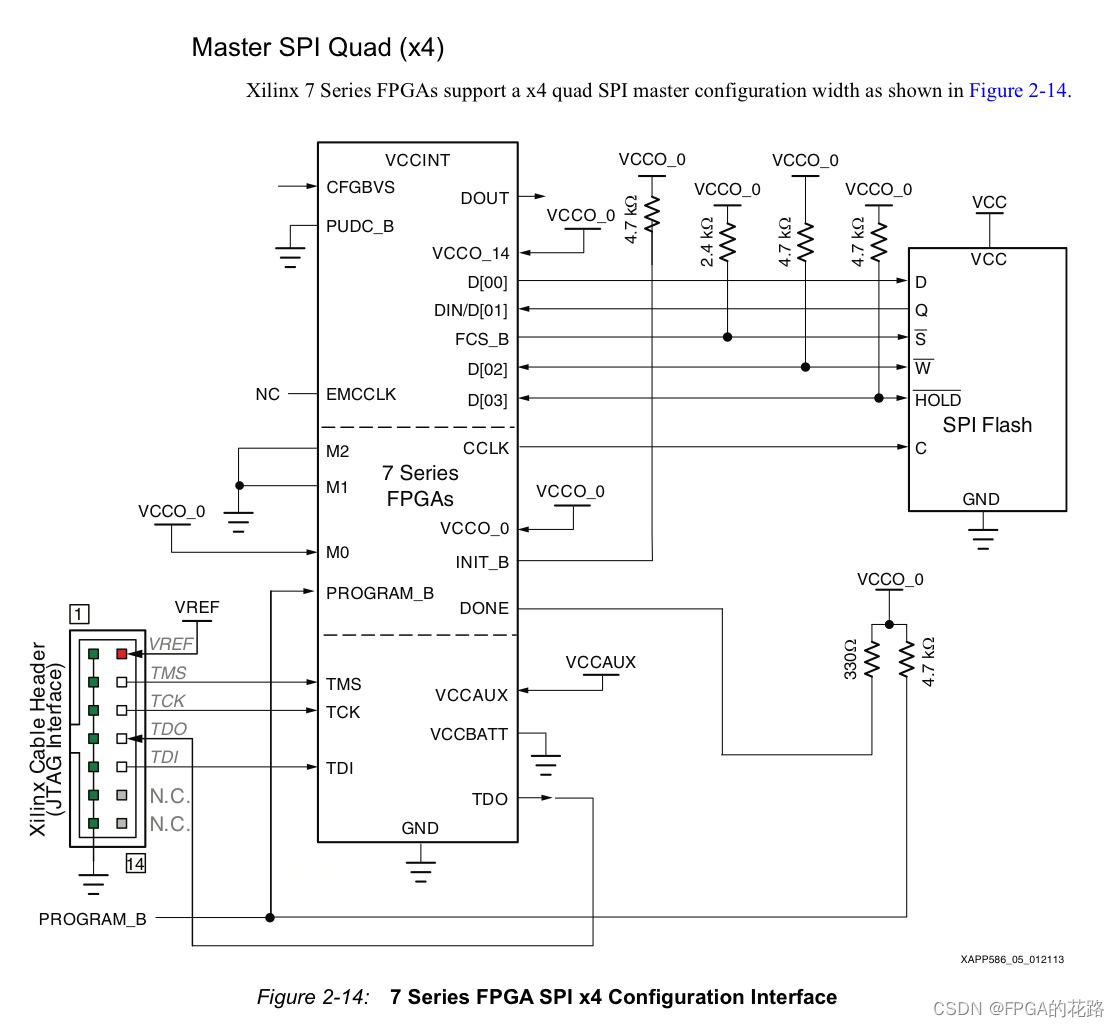

SPIx4 连接图

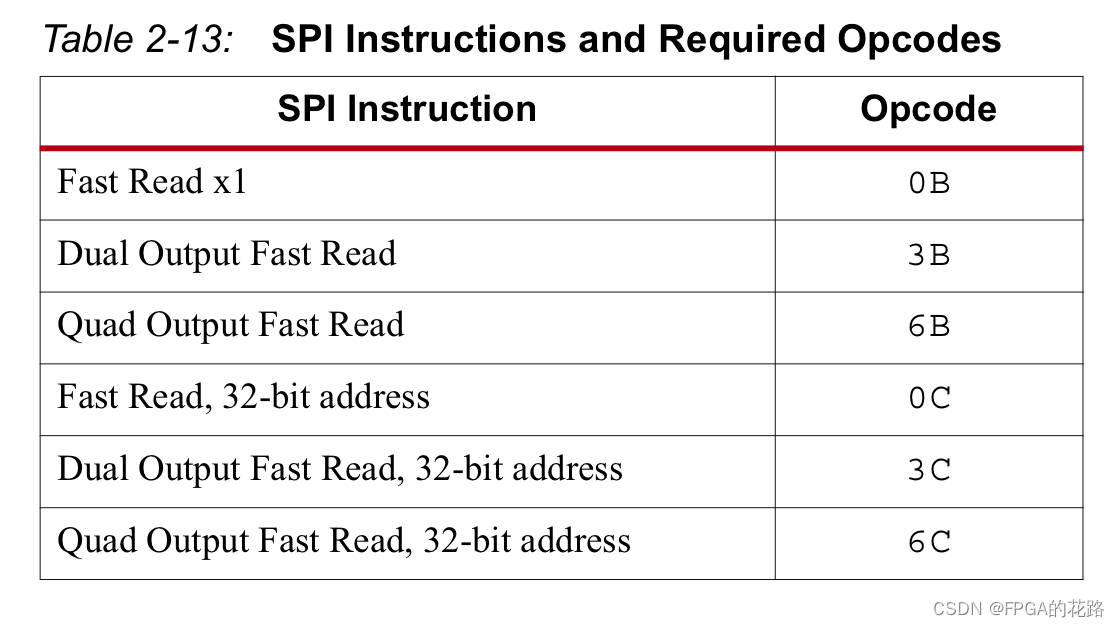

SPI操作指令

- 通过spi_buswidth属性改变读写位宽

操作flash空间大于128Mb

- 通过使能 spi_32bit_addr 属性支持32bit地址模式

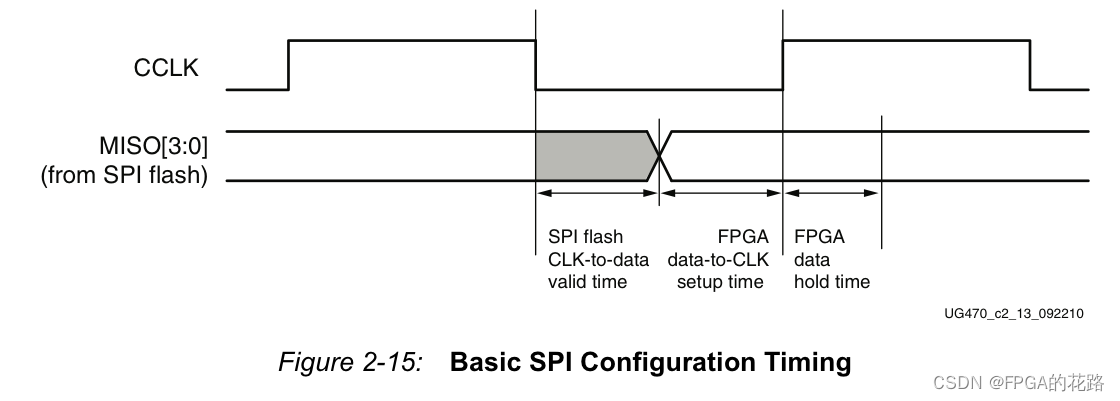

SPI配置时序

- 默认SPI器件在CCLK下降沿锁存数据,FPGA在上升沿采样数据;

- 可以通过配置SPI_FALL_EDGE属性更改为下降沿采样,但是一开始还是上升沿采样,只有到读取bit流中的更改为下降沿这个配置信息之后才会生效,这个在使能外部时钟源和更改速率之前生效

SPI最大速率计算

上电顺序要求

SPI flash必须在FPGA 拉低FCS_B和发送读指令之前具备接受指令状态

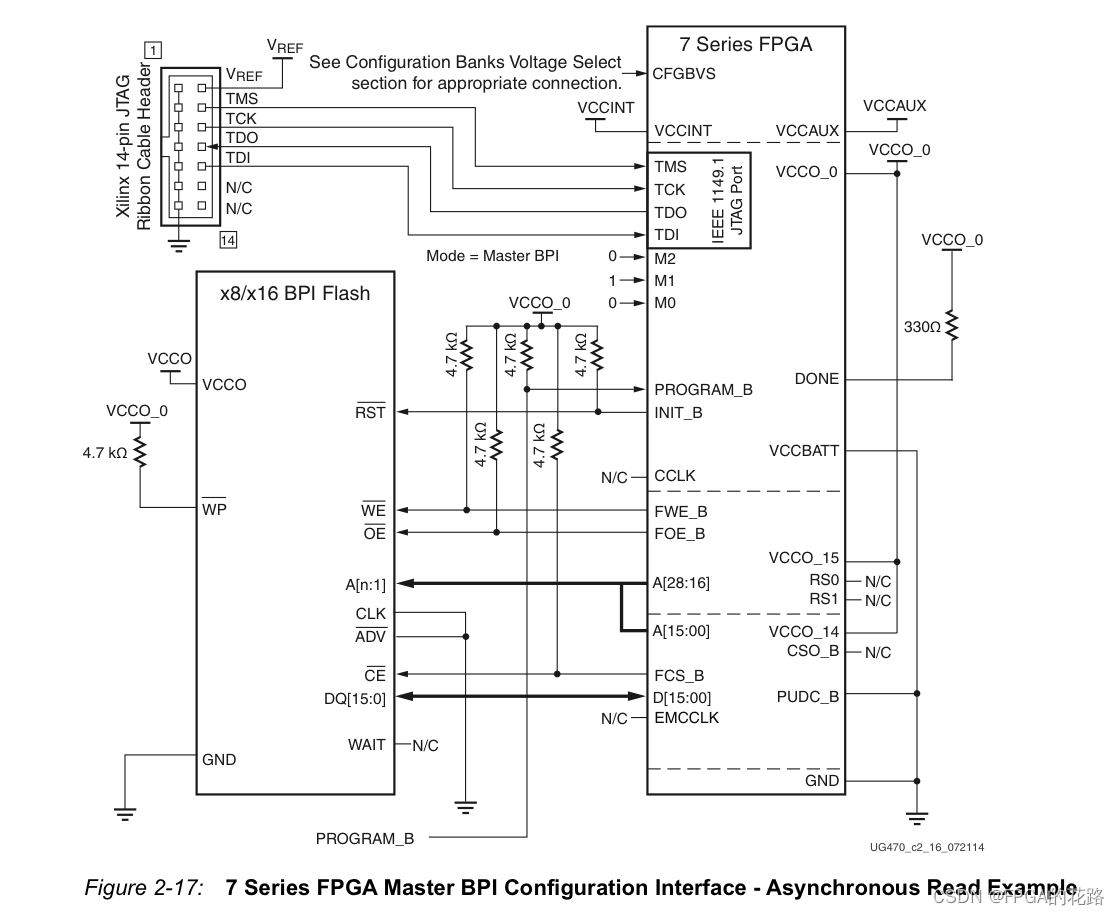

主BPI配置模式

- 某些引脚位于 bank15,Artix-7 中 7A50T 以及更小器件和 Spartan-7系列不支持 BPI 配置;

- BPI模式支持异步和同步读取两种方式,默认异步;

- 异步读取支持x8和x16两种位宽,均为自动识别

接口

异步读取模式

连接图

- BPI模式:M[2:0]= 101 ;

- CCLK必须作为输出悬空;

- RS[1:0]用于多镜像配置(MultiBoot)

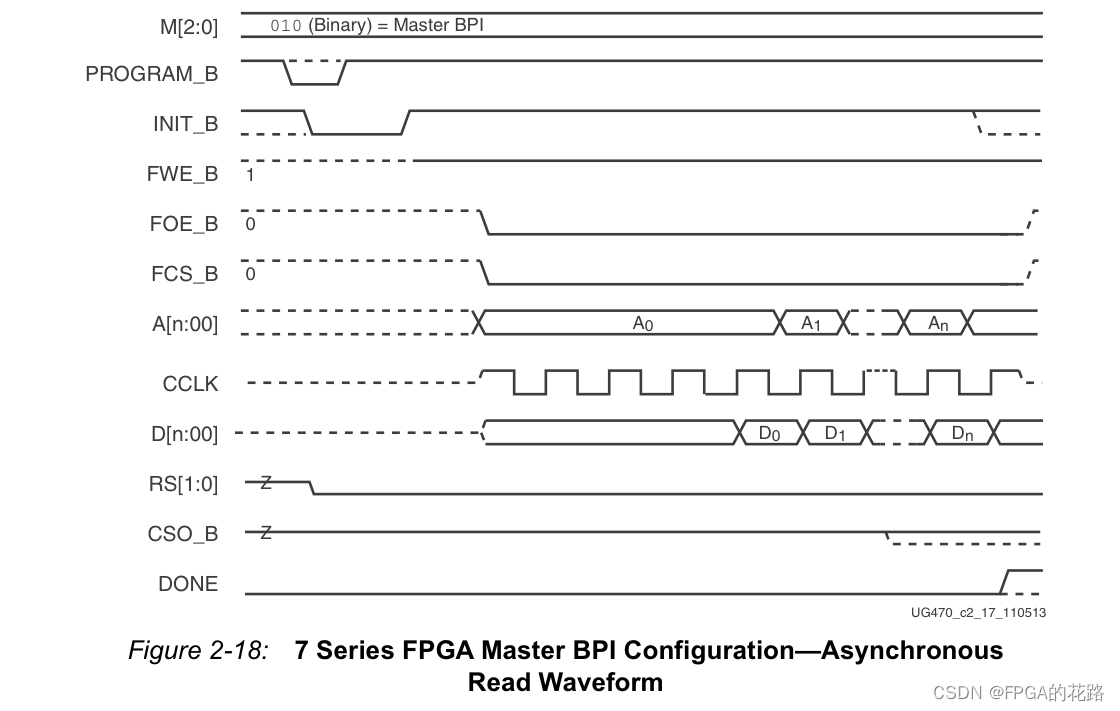

时序

- 开始配置:上电或者低脉冲PROGRAM_B信号;

- 上电配置:PROGRAM_B低电平时拉低INIT_B;

- 初始化完成:INIT_B变高,INIT_B上升沿采样M[2:0],识别配置模式;

- 识别为BPI模式:FWE_B拉高,FOE_B拉低,FCS_B拉低;

- 主模式时INIT_B上升沿一段延时后输出CCLK;

- FPGA输出初始地址并维持10个CCLK;

- FPGA在CCLK上升沿读取数据;

- CRC错误,INIT_B输出低,DONE保持低电平;

- 加载完成,DONE拉高;

- CCLK变为高阻态;

- 在GTS_cycle后多功能I/O引脚变为用户模式,默认为DONE变为高后一个周期

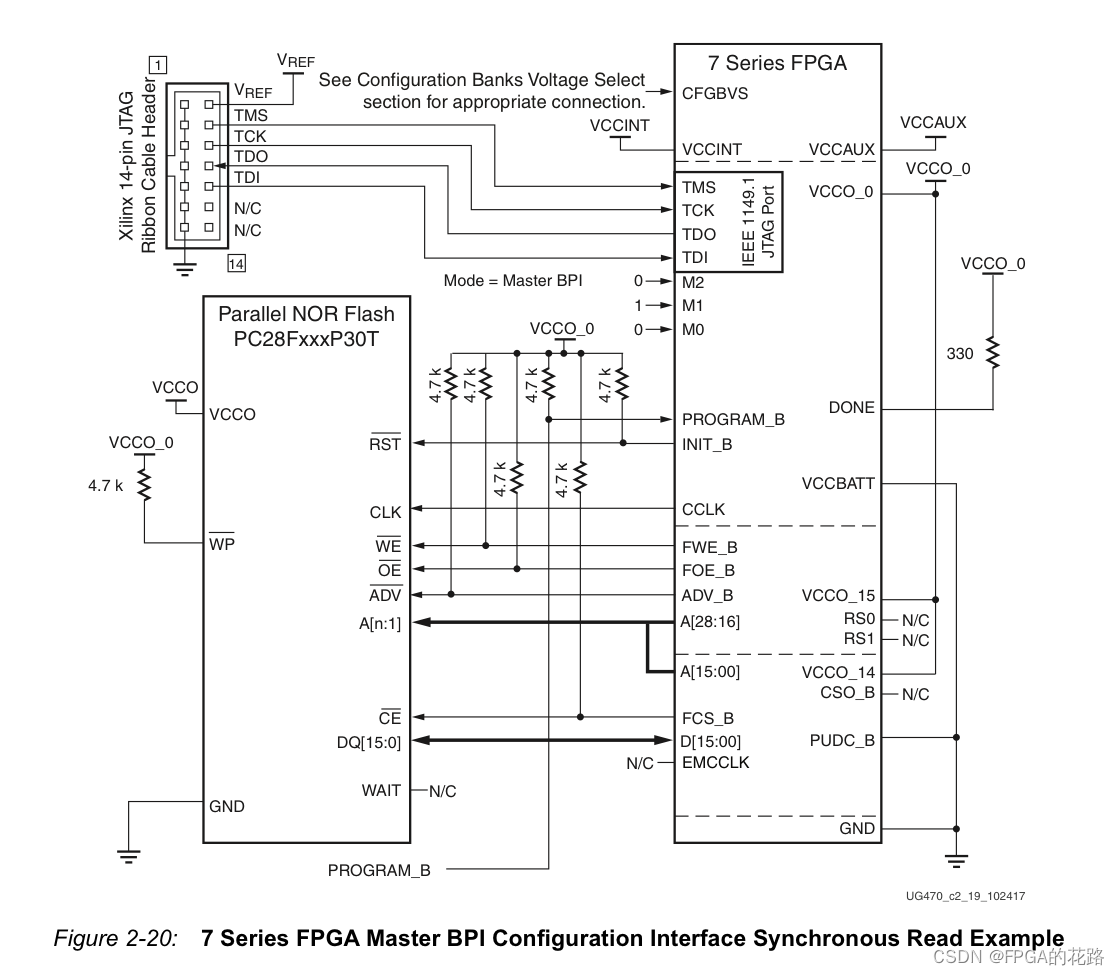

同步读取模式

连接图

- 同步读取模式是最快的配置模式;

- 一开始使用默认CCLK速率和异步读取模式,直到读取bitstream的header才转换为同步读模式;

- 同步模式需要通过设置BPI_sync_mode属性设置,有两种属性值:Type1(用于G18F信号flash);Type2(用于P30/P33信号flash);

- 同步读模式,FPGA CCLK输出连接BPI Flash,ADV_B连接FLASH ADV引脚;

- FPGA配置完成后 BPI flash保持同步读模式;

- 同步读模式只支持x16;

- bit顺序和SelectMap一样

最大配置速率计算

上电顺序要求

- 在FPGA驱动FCS_B低电平并输出第一个地址之前,BPI闪存必须准备好进行异步读取,以确保BPI闪存可以输出存储的比特流。

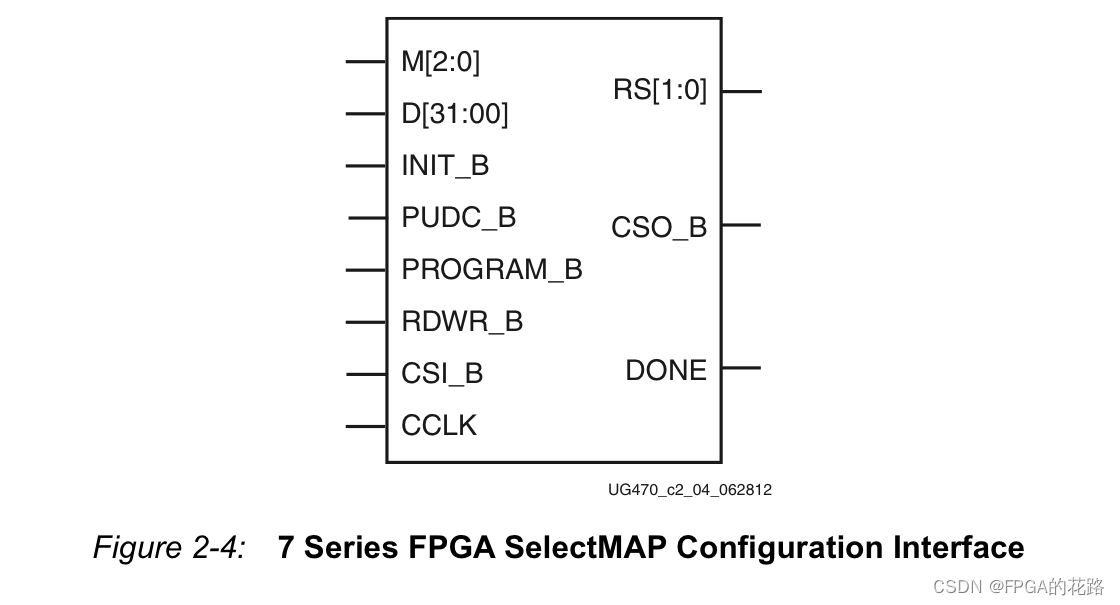

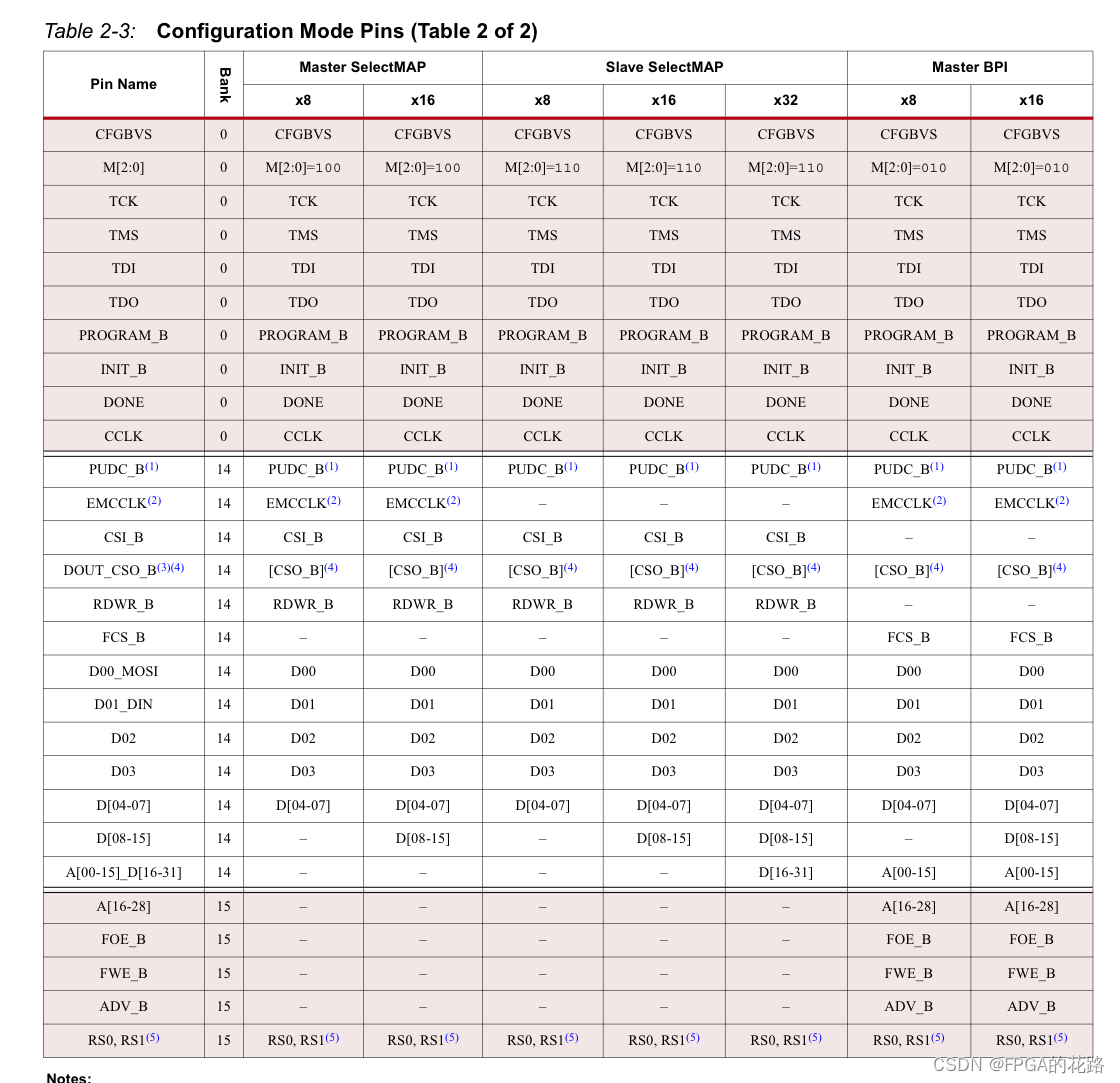

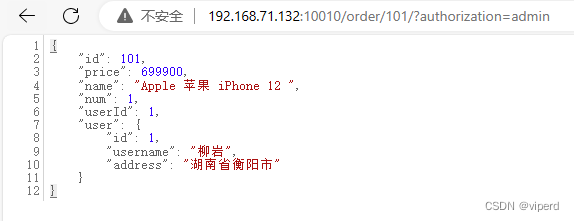

SelectMAP 配置模式

简介

-

总线宽度 8、16、32bits,可以自动识别总线宽度;

-

支持配置和读取操作;

-

读操作只有从 SelectMAP模式支持;

-

CCLK主模式下为输出;从模式下为输入;

-

模式:单器件从模式、多器件菊花链模式、多相同器件模式

接口

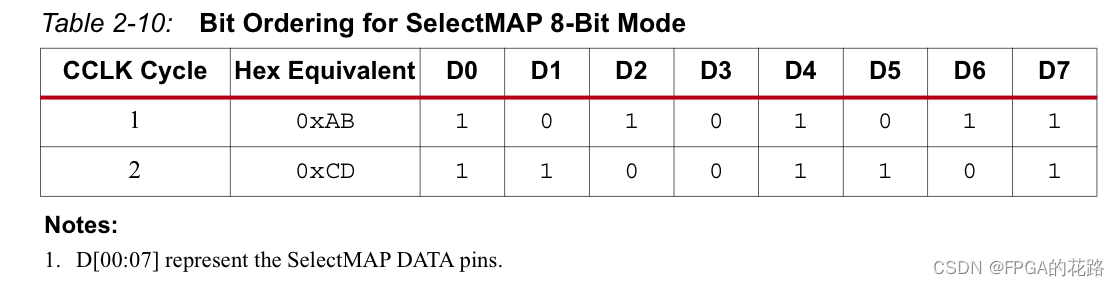

Data Ordering

](https://img-blog.csdnimg.cn/direct/af2631a0e7bb45bfb522036e3d9cbc06.png)

单器件配置模式

连接示例

数据加载

支持连续和非连续数据加载,数据加载由 CSI_B、RDWR_B、CCLK信号控制

-

CSI_B

-

SelectMAP 接口使能,低有效;

-

当不需要SelectMAP和读回操作时,CSI_B可以接地

-

-

RDWR_B

- 输入输出使能,低电平输入(写FPGA),高电平输出(读FPGA);

- CSI_B使能时,RDWR_B保持不变,否则会中断配置和回读操作

-

CCLK

- 所有数据操作同步于CCLK;

- 配置FPGA:FPGA在时钟上升沿采样;

- 回读FPGA:FPGA在时钟上升沿更新数据

连续配置时序

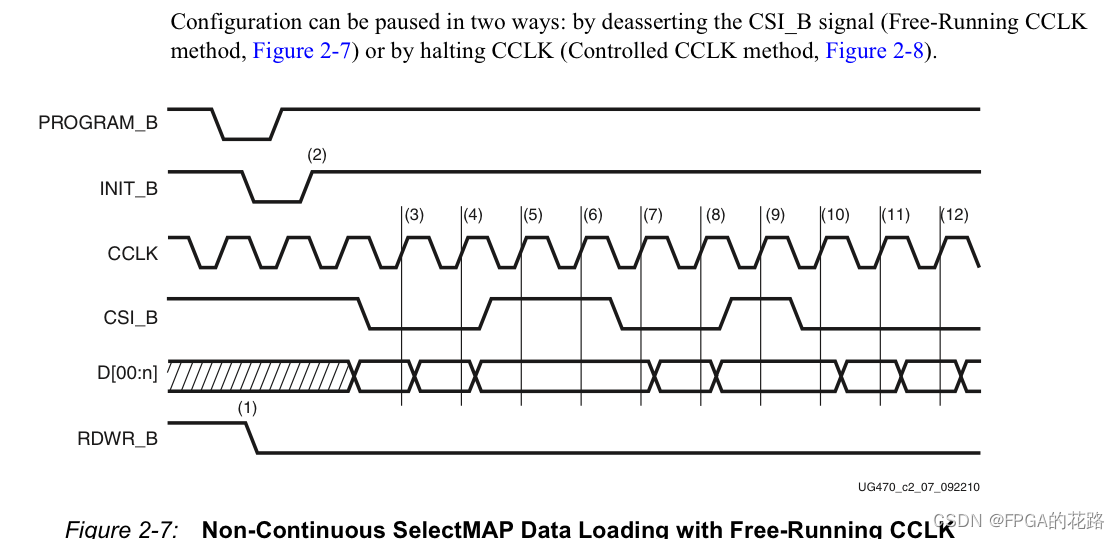

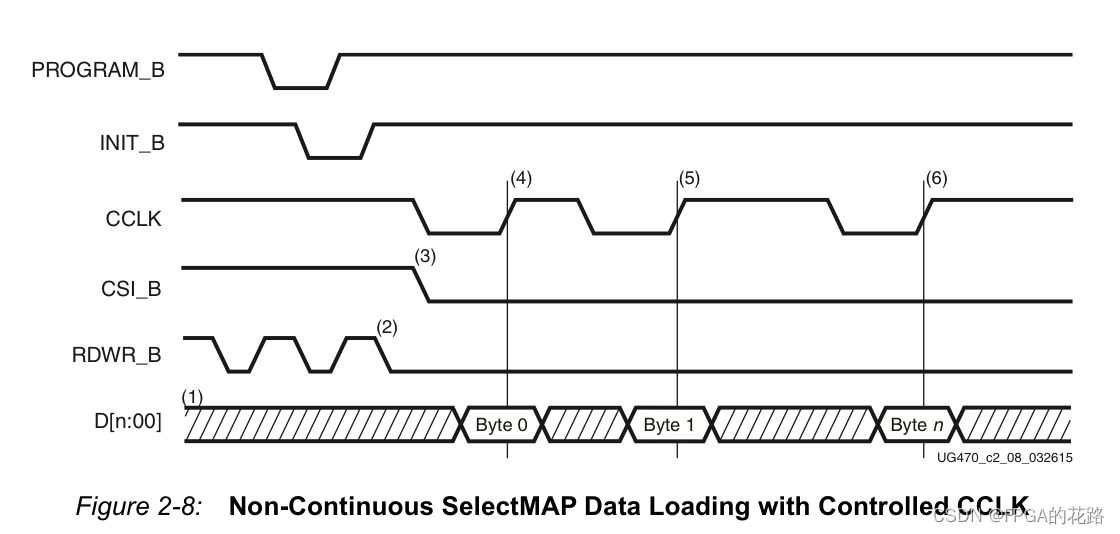

非连续配置时序

两种非连续配置方式:

- 通过控制CSI_B信号;

- 通过控制CCLK信号

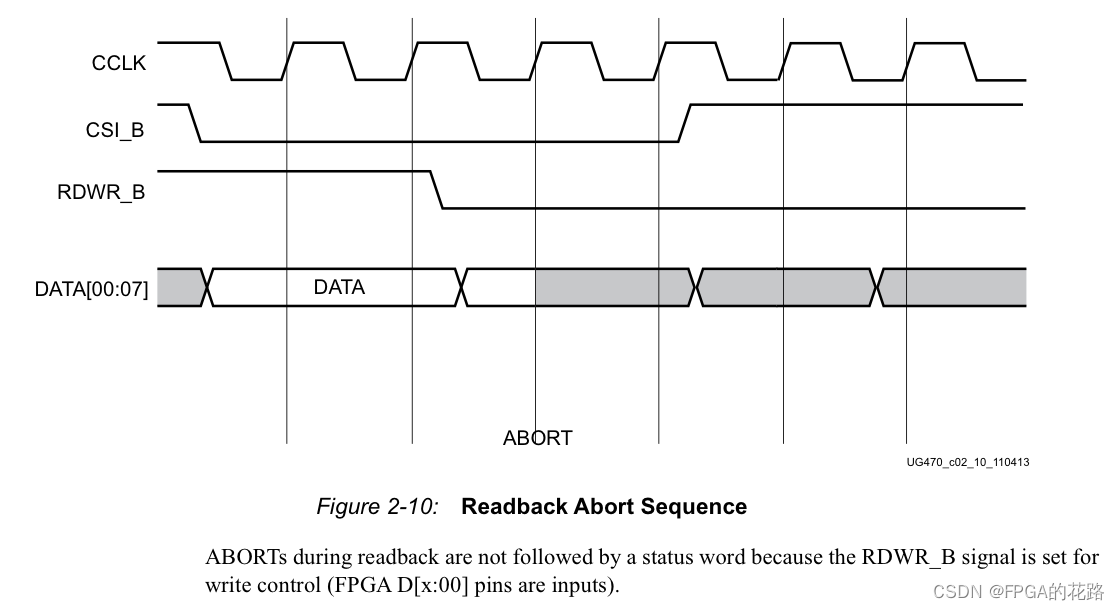

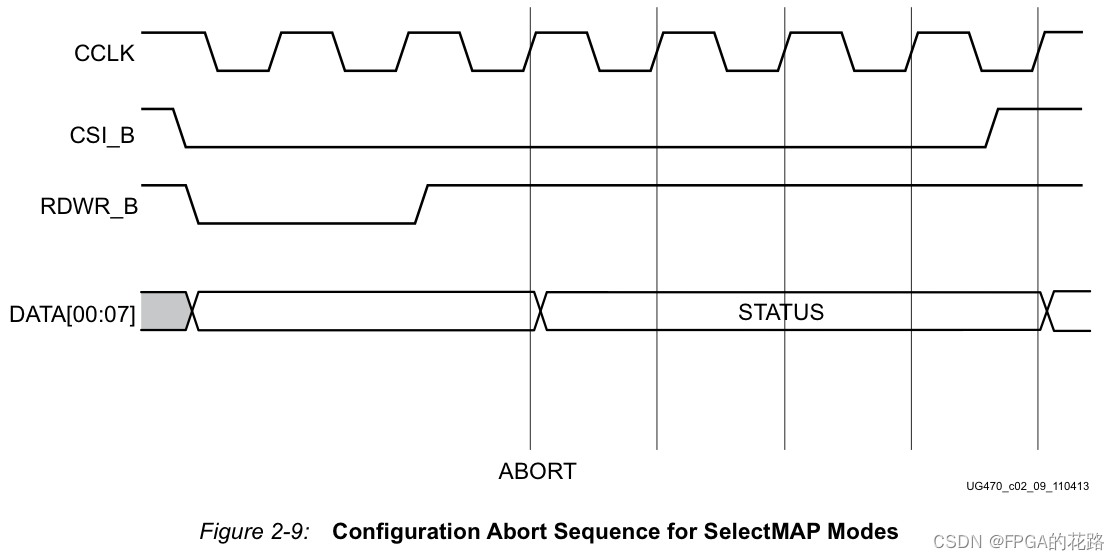

终止操作

- 分为配置终止和回读终止操作;

- 当CSI_B有效时改变RDWR_B触发终止操作;

- 配置终止会持续4个CCLK周期,同时数据线D0-7会返回状态字;回读终止不返回状字;

- 终止操作完成后会恢复配置/回读操作;或者可以通过产生PROGRAM_B低脉冲复位整个器件

时序

状态字定义

状态字数据对齐

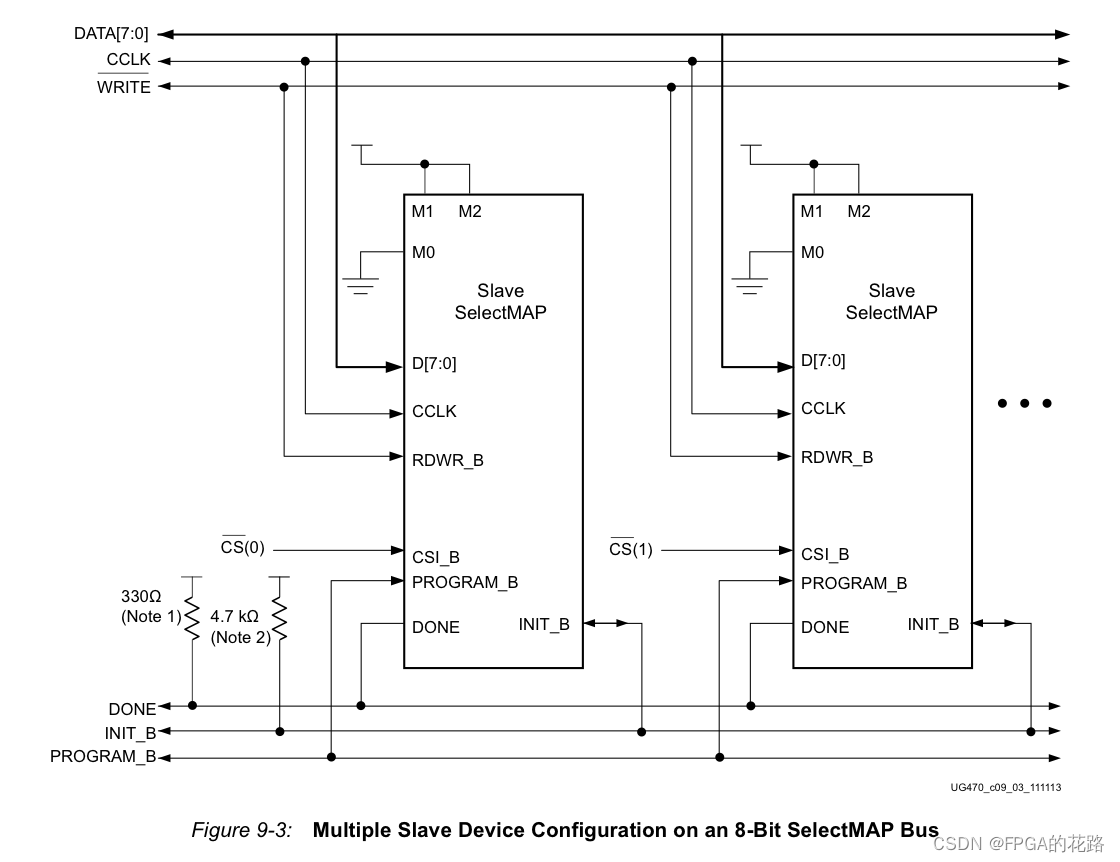

多器件SelectMAP独立配置

- 通过CS单独控制每个器件

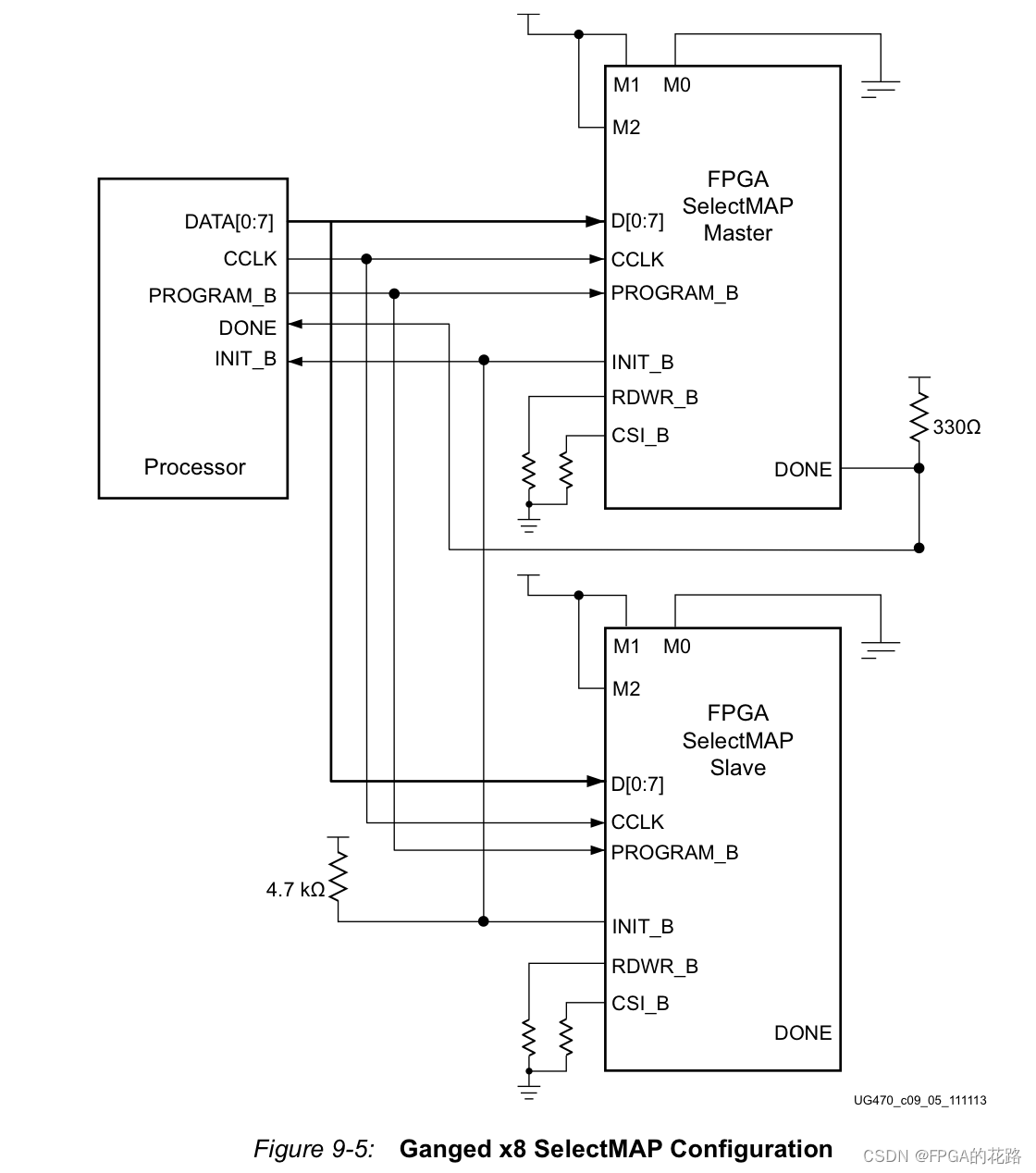

多器件SelectMAP同时配置

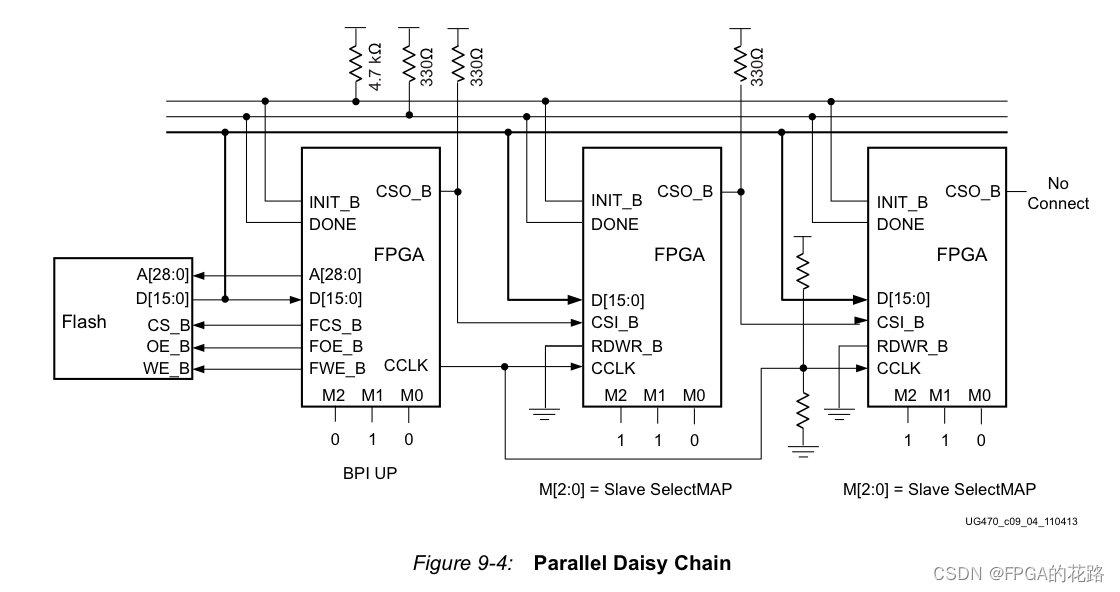

并行菊花链配置

- CS_B为菊花链;

- 第一个器件可以为Master/Slave SelecrMAP、BPI,其他必须都为Slave SelecrMAP

JTAG配置模式

- 无论M[2:0]配置为何值,都支持JTAG在线配置

配置引脚

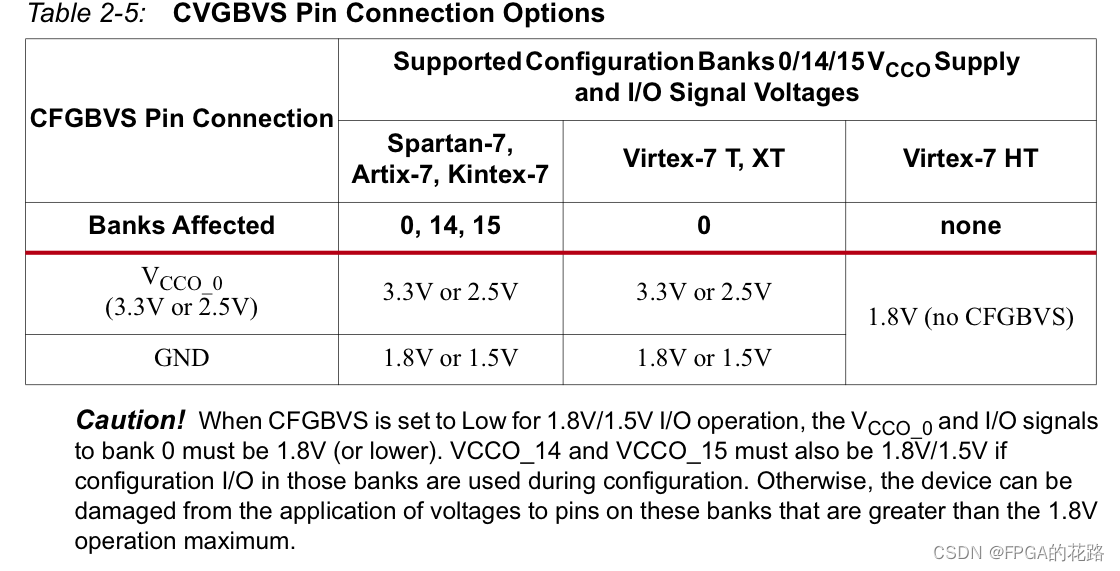

CVGBVS

- 输入引脚;

- CVGBVS决定bank0 I/O支持的电压值,以及配置区间bank14、bank15的I/O所支持的电压值;

- 若I/O工作在1.8V或者更低电压下,CVGBVS接GND;

- 若I/O工作在2.5V/3.3V下,CVGBVS接VCCO_0(3.3V/2.5V);

- 7系列有两种I/O bank类型:high-range (HR I/O) banks 支持3.3,2.5V电压标准;a few lower voltage I/O standards, and high-performance (HP I/O) banks 支持 1.8V 或者更低的电压标准;

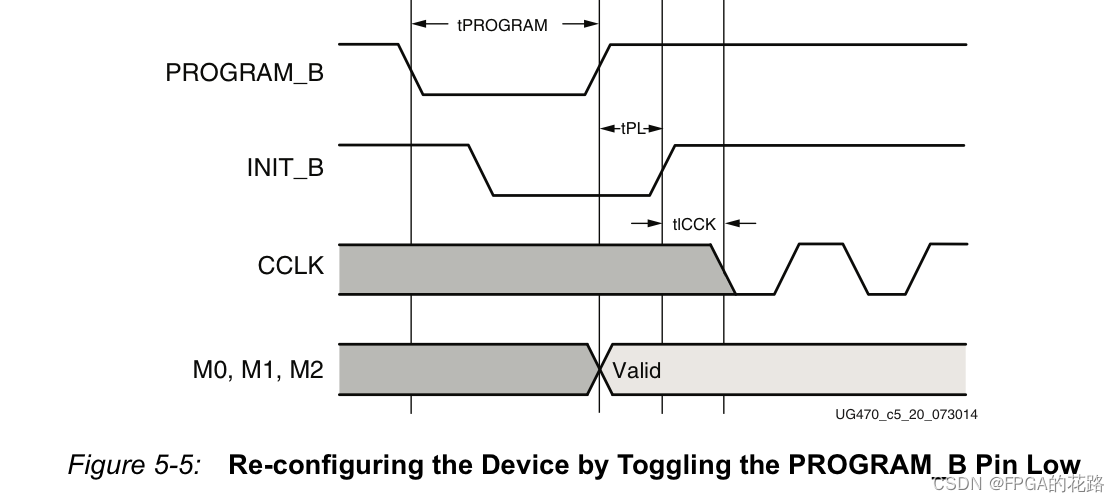

PROGRAM_B

- 输入引脚,下降沿有效,用于复位整个器件;

- 上升沿开始启动配置,但上电时把 PROGRAM_B 保持低电平不会使 FPGA配置保持复位状态,延迟配置时间需要使用 INIT_B 信号配合完成

- 引脚外部需要通过4.7kΩ 以上电阻上拉至VCCO_0

INIT_B

- FPGA 初始化引脚或配置错误信号,低电平有效。当 FPGA 处于配置复位状态或当FPGA 正在初始化(清除)其配置存储器(PROGRAM_B信号为低电平)时或当 FPGA 检测到配置错误时,FPGA 会将该引脚驱动为低电平;

- 在上电期间,可以通过讲该引脚拉低,来延迟上电配置程序的时间 ;

- 当完成初始化后,该引脚被释放,外部上拉电阻讲该引脚拉高,当检测到该信号上升沿之后,FPGA会读取M[2:0]引脚状态,从而确定后续采用哪种配置方式进行配置 ;

- 引脚外部需要通过4.7KΩ以上的电阻上拉至VCCO_0 ;

- M[2:0]被采样之后:INIT_B作为输出,0表示CRC或IDCODE错误(这时DONE为低电平),0或表示回读CRC错误(这时DONE为高电平,且回读CRC使能);1表示没有CRC错误,初始化完成

PUDC_B

- 输入引脚(不可悬空),在配置期间I/O引脚内部上拉电阻使能;

- 低电平,配置期间所有未赋值引脚为高电平;

- 高电平,配置期间所有未赋值引脚为高阻态

VCCBATT

- FPGA内部易失性存储器的电池备用电源,用于存储AES解密器的密钥,如果不需要使用AES易失性密钥存储区域中的解密器密钥,那么将该引脚接地就行,该引脚不是I/O,不受VCCO_0的影响

RS0, RS1

- 输出引脚,RS[1:0]用多镜像配置(MultiBoot)

RDWR_B

- 输入引脚;

- 高电平:FPGA输出数据到SelectMap数据线上;

- 低电平:外部控制器通过SelectMap数据线写数据到FPGA

FCS_B

- 输出引脚,flash片选信号,低有效

FOE_B

- 输出引脚,flash输出使能,低有效

FWE_B

- 输出引脚,flash写使能,低有效

Configuration Details

配置文件格式

总线位宽自动检测

- Serial、JTAG、SPI模式不支持总线位宽自动检测功能;

- 只检测D[7:0]的值,检测到0xBB,若下一次检测到0x11,则为x8;若下一次检测到0x22,则为x16;若下一次检测到0x44,则为x32;然后立即切换总线位宽,开始检测同步字

同步字

- 识别到同步字前没有其他包数据

位交换和总线字序

延迟配置

- 通过 INIT_B保持低电平来延迟配置。当INIT_B拉高后(完成初始化阶段),再次拉低不会延迟配置。

延迟相关信号

配置顺序

Setup

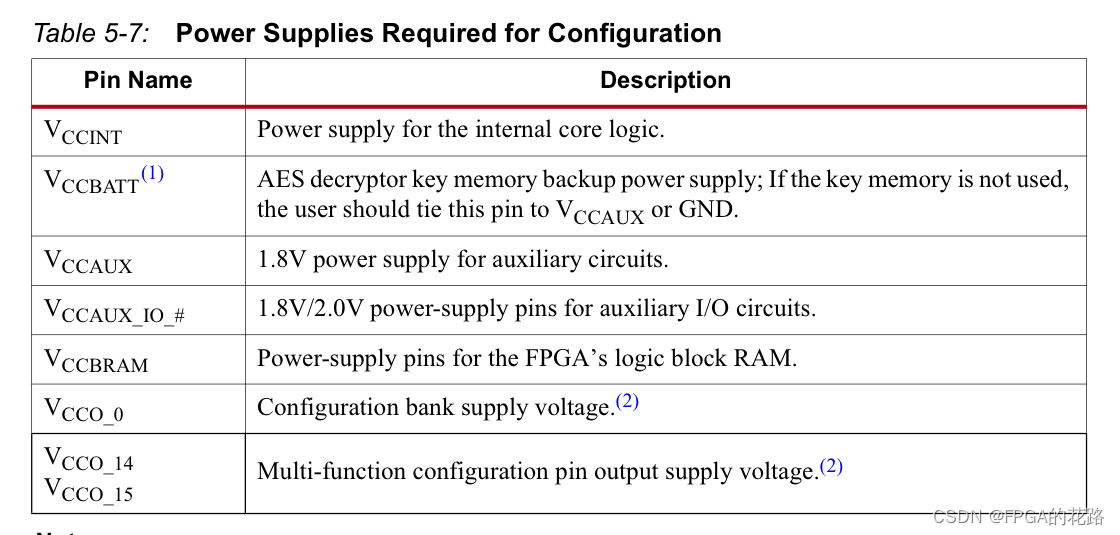

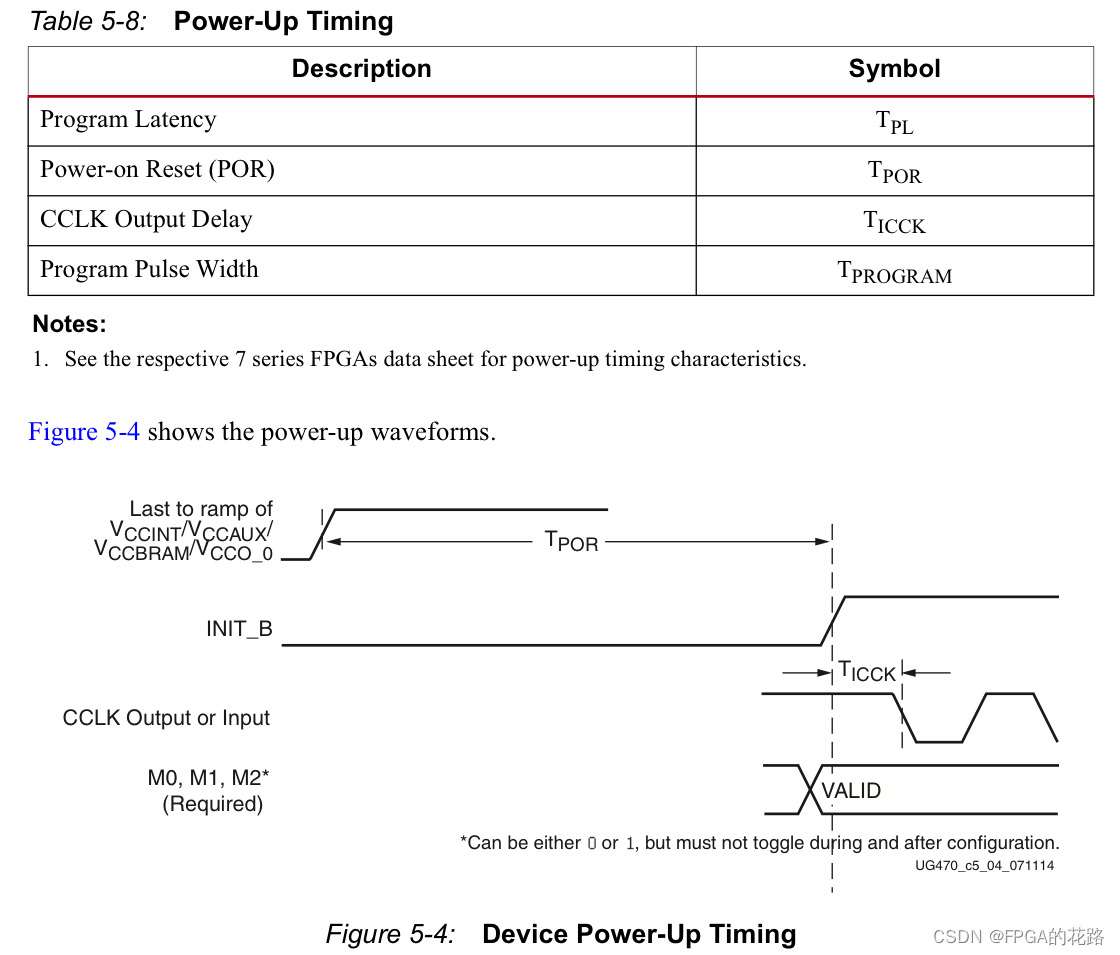

Device Power-Up (Step 1)

- 电源引脚

- 上电时序

Clear Configuration Memory (Step 2, Initialization)

- 以下情况都会触发“清除配置存储”:重新上电、PROGRAM_B低脉冲、JTAG JPROGRAM指令、IPROG指令、fallback重配置;

- BRAM和寄存器都会通过GSR拉高初始化;

- 这段期间,除了少数配置输出引脚,其他I/O通过GTS处于高阻态,如果PUDC_B为低,则为内部上拉

Sample Mode Pins (Step 3)

- INIT_B拉高后,器件采集M[2:0]模式引脚值,驱动CCLK(master模式下),然后在CCLK上升沿采集配置数据引脚值

Bitstream Loading

Synchronization (Step 4)

- 对于BPI模式、SelectMAP模式,同步前需要先自动识别位宽;

- 任何同步字前的数据都会被忽略,除了位宽检测序列;

- 同步阶段对于大多数用户是透明的,因为工具生成的bit包含位宽检测序列及同步字

同步阶段相关信号

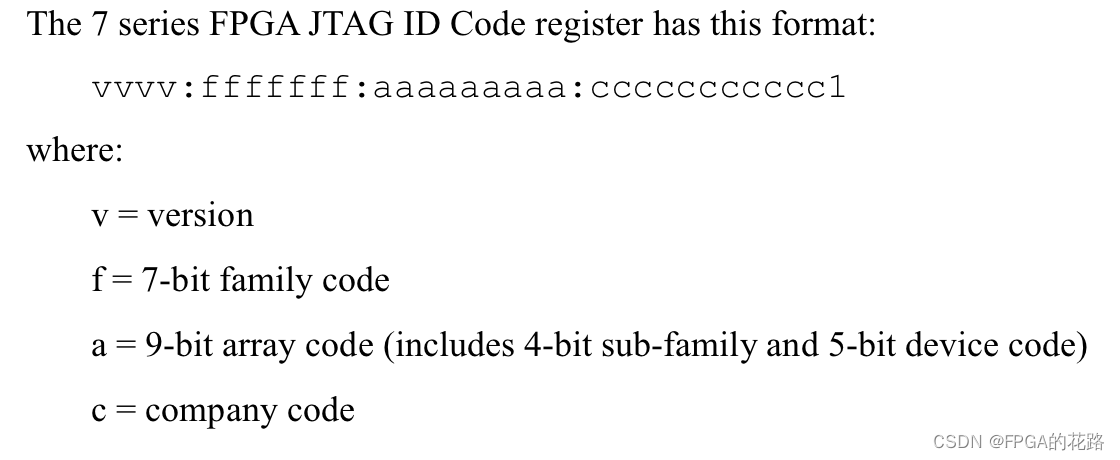

Check Device ID (Step 5)

-

同步之后进行器件ID检验,如果ID不匹配则回退进行重配置

-

7系列 jtag ID Code寄存器格式

Load Configuration Data Frames (Step 6)

- 同步字加载及器件ID检查完成后,开始加载配置数据帧

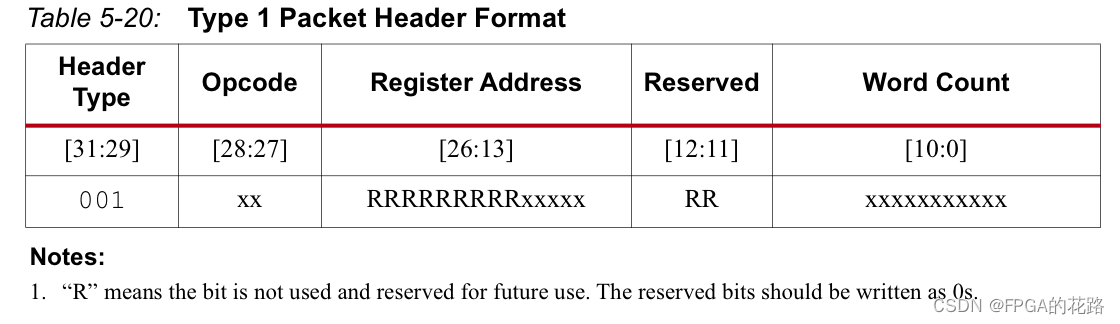

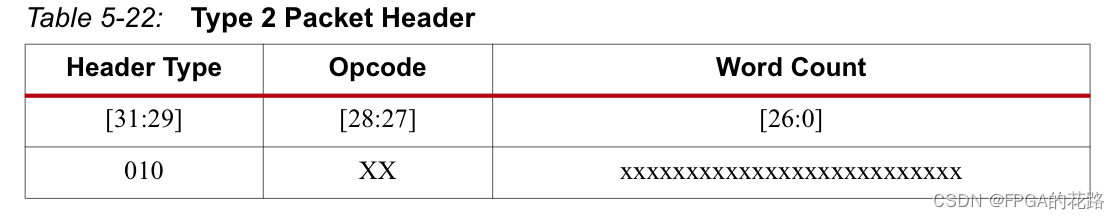

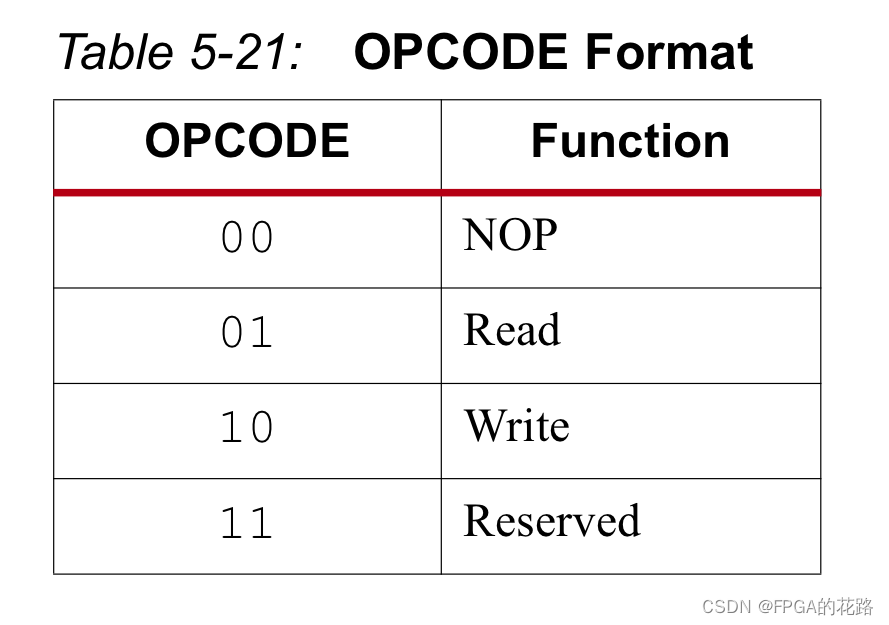

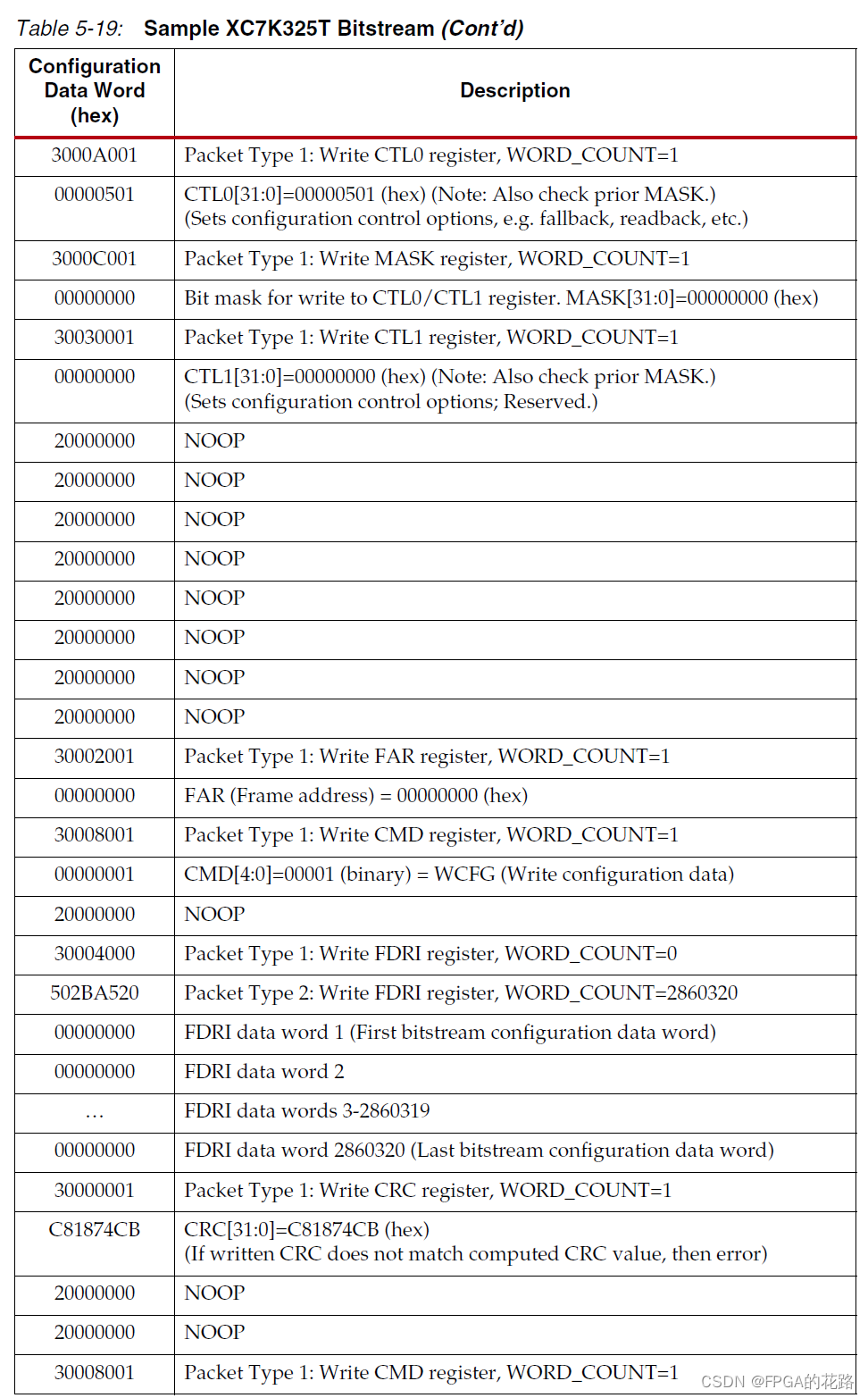

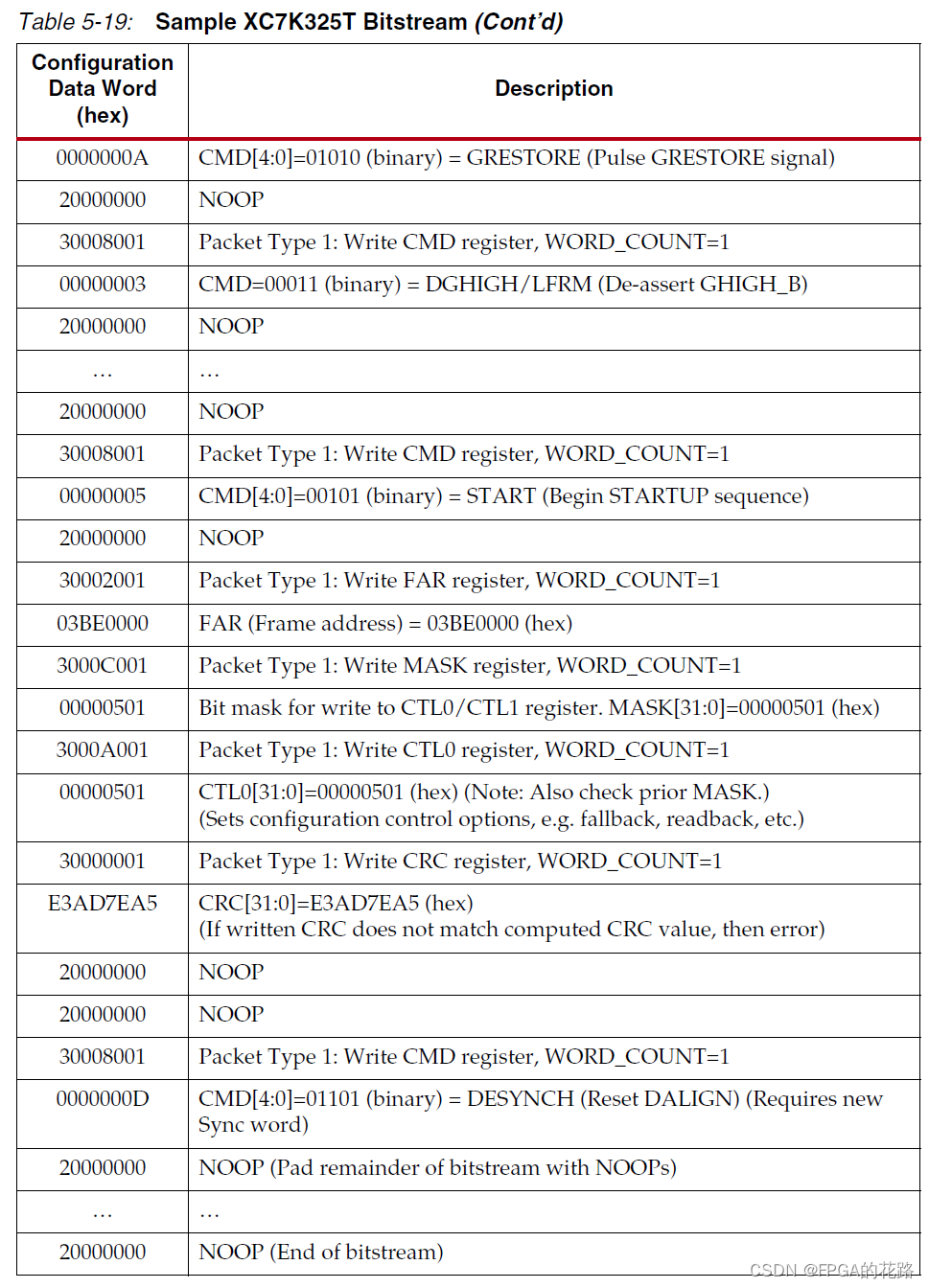

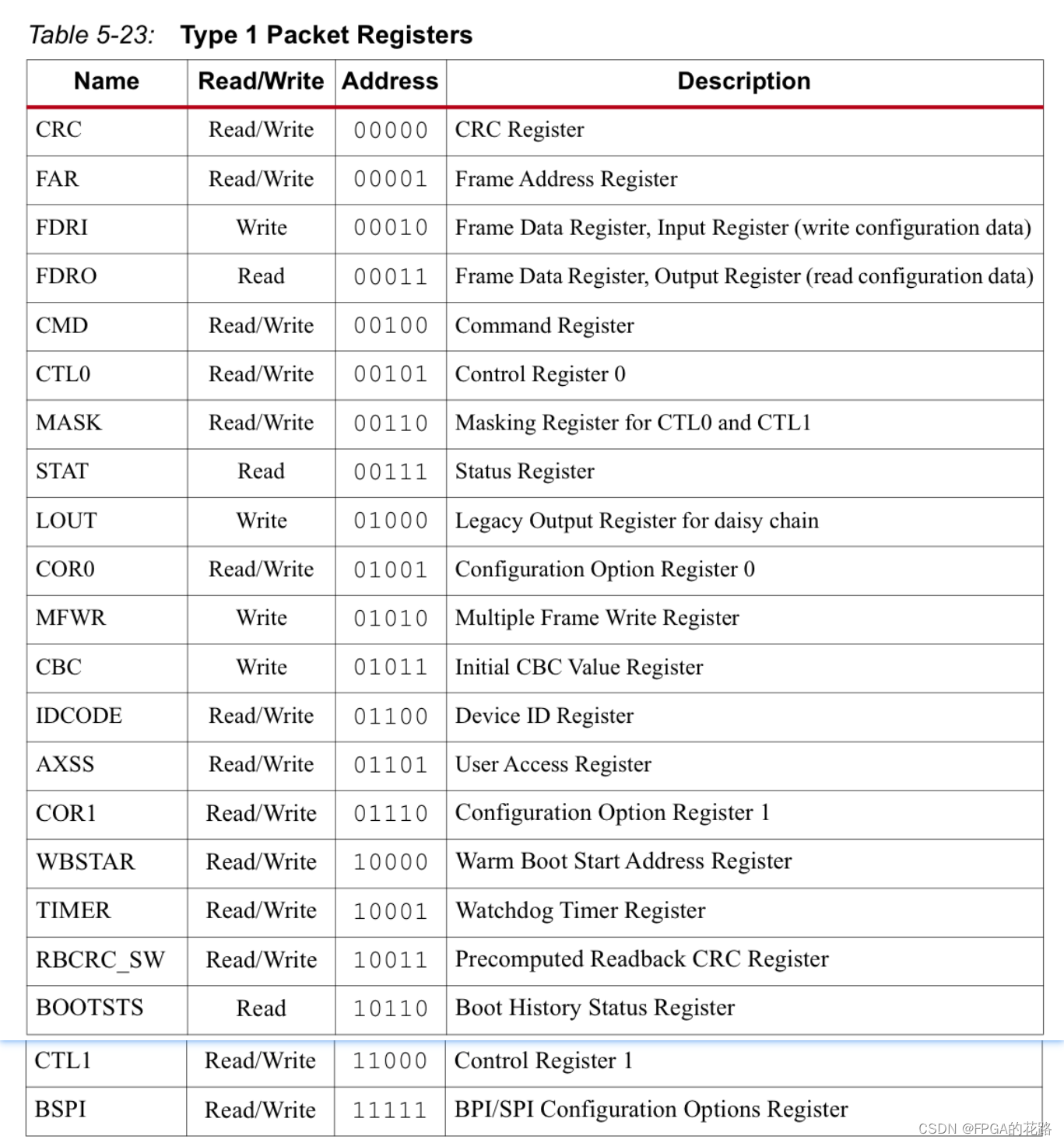

- Configuration Packets :Type1、Type2两种,寄存器地址只用5bit

Cyclic Redundancy Check (Step 7)

- FPGA 计算CRC跟bit里的校验值比较;

- 同步丢失后,后续的指令都被忽略,最配置失败—DONE低,INIT_B高

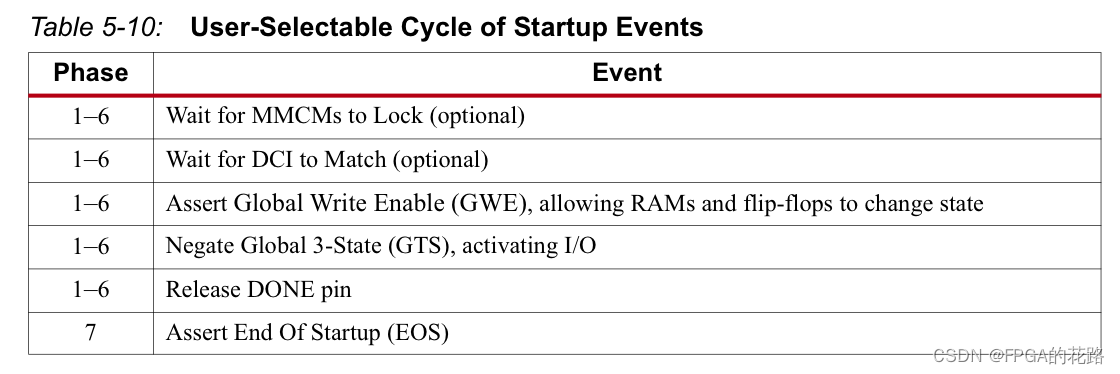

Startup

- DONE置位后要保留足够时间保证能到 phase7,保守时间为64个时钟周期

- 防止DONE、GTS、GWE在MMCMs锁相和DCI匹配前置位

配置过程I/O电平变化(EOS)

- 在End Of Startup后一个CFGCLK发生0-1-0的电平转变过程;

- 避免产生影响:VCCO14、15接2.5/3.3V;或者外部引脚上拉;还可以逻辑设计忽略EOS 后第一个CFGCLK上升沿之后至少200ns不采纳数据

STARTUPE2原语

Bitstream Security

Bitstream Composition

配置寄存器

重配置和多镜像

Fallback MultiBoot

- 回退功能使能:ConfigFallback(通过xdc约束或者bitstream设置);

- 回退重配置时将忽略IPROG,看门狗计时器关闭;

- 重配置失败,配置终止,INIT_B和DONE保持低电平

先加载golden再触发MultiBoot

直接加载MultiBoot

- 对于SPI模式,回退默认使用x1进行golden镜像加载;

- 对于BPI模式,回退默认使用异步读模式进行镜像加载,所以当配置为同步读模式时要注意CCLK,同时要满足异步和同步读模式;

- BPI模式,硬件设计RS引脚要根据upper address进行上拉或者下拉

IPROG

- IPROG(Internal PROGRAM)指令和PROGRAM_B引脚给低脉冲作用类似,区别在于IPROG不复位WBSTAR、TIMER、BSPI和BOOTSTS寄存器值;

- IPROG指令触发初始化,同时INIT和DONE拉低;

- 两种发起指令方式:逻辑控制ICAPE2;生成bit时在golden bit前加入WBSTAR和IPROG指令; 4.当触发回退重新加载时IPROG指令将被忽略

IPROG Using ICAPE2

- 输入配置信息需要位转换;

- 发送流程:同步字->WBSTAR->IPROG

IPROG Embedded in the Bitstream

Status Register for Fallback and IPROG Reconfiguration

- BOOTSTS用于存储配置历史;

- Valid用于只是当前Status是否有效;

- Status_0用于记录最新配置状态; Status_1用于记录上一次配置状态;

- Status_1 表示执行了IPROG,检测到CRC错误;

- Status_0表示回退加载成功,同时也有IPROG,只是回退重配置忽略IPROG指令,但是同样记录状态

WBSTAR Register

- 执行IPROG指令后,FPGA从WBSTAR指示的地址开始读指令

Watchdog Timer

- 两种模式:配置监控、用户逻辑监控;

- 计数到达0,触发回退;

- 计时器寄存器计数时钟为CFGMCLK(65MHz))256分频,一个时钟周期为4000ns,计数器位宽30bits,所以可以计时4230秒;

- 回退重配置时,Watchdog不使能

Configuration Monitor Mode

- TIMER寄存器:TIME_CFG_MON设为1,并设置超时计数值

User Monitor Mode

- TIMER寄存器:TIME_USR_MON设为1,并设置超时计数值

RS Pins

-

除SPI配置模式,RS信号均由WBSTAR寄存器控制输出;

-

当BPI或Master SelectMap模式回退时,输出低电平;

-

在多镜像场景用作为高位地址线;

-

除CCLK外所有BPI引脚均为多功能I/O,配置完成后(DONE为高)均可由用户控制

JTAG高级用法

参考文献

7 Series FPGAs Configuration User Guide (UG470)

相关文章:

Xilinx 7系列FPGA配置(ug470)

Xilinx 7系列FPGA配置(ug470) 配置模式串行配置模式接口从-连接方式主-连接方式串行菊花链(非同时配置)串行配置(同时配置)时序 主SPI配置模式SPIx1/x2 连接图SPIx1模式时序SPIx4 连接图SPI操作指令操作fla…...

3分钟开通GPT-4

AI从前年12月份到现在已经伴随我们一年多了,还有很多小伙伴不会开通,其实开通很简单,环境需要自己搞定,升级的话就需要一张visa卡,办理visa卡就可以直接升级chatgptPLSU 一、虚拟卡支付 这种方式的优点是操作简单&…...

Easticsearch性能优化之索引优化

Easticsearch性能优化之索引优化 一、合理的索引设计二、合理的分片和副本三、合理的索引设置 对于性能优化,Elasticsearch(以下简称ES)的索引优化是提高性能的关键因素之一。合理的设计索引,合理的分片和副本以及合理的缓存设置等…...

安装mysql-8.0.30-winx64(windows 64位)

1.下载 1.1下载地址:https://dev.mysql.com/downloads/mysql/ 2 .下载后解压缩目标文件 2.1之后在根目录下新建my.ini文件,并创建文件夹data (新解压的文件没有my.ini文件,需自行创建 复制以下代码到my.ini文件 以下代码除安装目录和数据的…...

ios xcode 15 PrivacyInfo.xcprivacy 隐私清单

1.需要升级mac os系统到13 兼容 xcode 15.1 2.升级mac os系统到14 兼容 xcode 15.3 3.选择 New File 4.直接搜索 privacy 能看到有个App Privacy 5.右击Add Row 7.直接选 Label Types 8.选中继续添加就能添加你的隐私清单了 苹果官网文档Describing data use in privacy man…...

【物联网】-智能社会的分类

万物感知 感知物理世界,变成数字信号 (温度、空间、触觉、嗅觉、听觉、视觉) 万物互联 将数据变成online,使智能化 (宽联接、广联接、多联接和深联接) 万物智能 基于大数据和人工智能的应用 &#…...

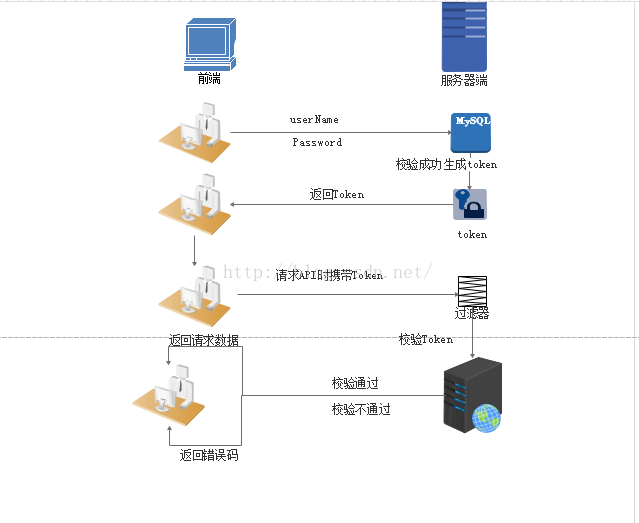

Django高级之-cookie-session-token

Django高级之-cookie-session-token 发展史 1、很久很久以前,Web 基本上就是文档的浏览而已, 既然是浏览,作为服务器, 不需要记录谁在某一段时间里都浏览了什么文档,每次请求都是一个新的HTTP协议, 就是请…...

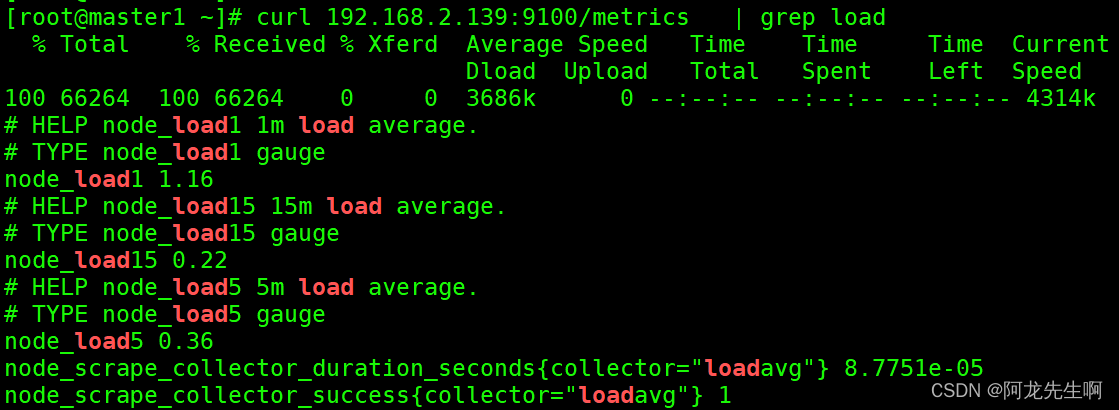

【Prometheus】k8s集群部署node-exporter

目录 一、概述 1.1 prometheus简介 1.2 prometheus架构图 1.3 Exporter介绍 1.4 监控指标 1.5 参数定义 1.6 默认启用的参数 1.7 prometheus如何收集k8s/服务的–三种方式收集 二、安装node-exporter组件 【Prometheus】概念和工作原理介绍-CSDN博客 【云原生】ku…...

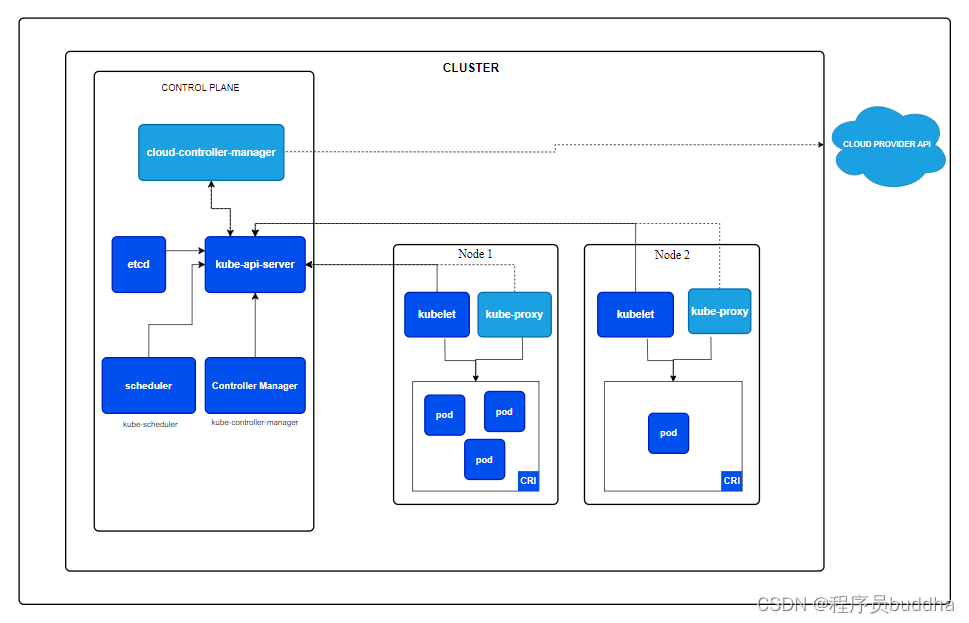

2024年k8s最新版本安装教程

k8s安装教程 1 k8s介绍2 环境搭建2.1 主机准备2.2 主机初始化2.2.1 安装wget2.2.2 更换yum源2.2.3 常用软件安装2.2.4 关闭防火墙2.2.5 关闭selinux2.2.6 关闭 swap2.2.7 同步时间2.2.8 修改Linux内核参数2.2.9 配置ipvs功能 2.3 容器安装2.3.1 设置软件yum源2.3.2 安装docker软…...

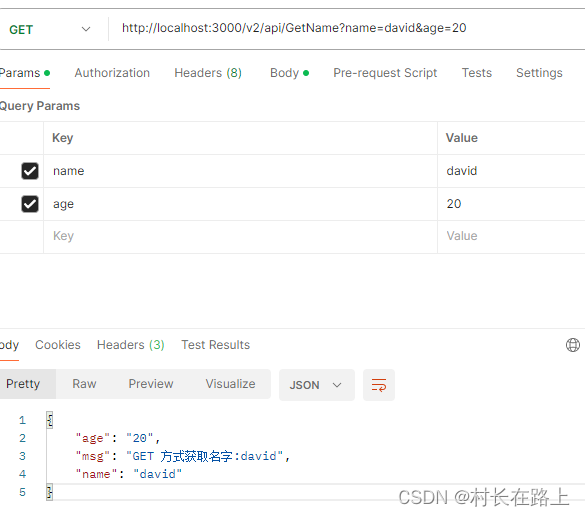

Gin 获取请求参数

POST 请求参数 Gin 获取Post请求URL参数有三种方式 func (c *Context) PostForm(key string) string func (c *Context) DefaultPostForm(key, defaultValue string) string func (c *Context) GetPostForm(key string) (string, bool)大多数情况下使用的是application/x-www…...

安卓 Kotlin 面试题 31-40

🔥 31、简述Kotlin 中的内联类,我们什么时候需要?🔥 有时,业务逻辑需要围绕某种类型创建包装器。 但是,由于额外的堆分配,它会引入运行时开销。 此外,如果包装的类型是原始类型&…...

【洛谷千题详解】P1613 跑路

目录 题目总览 题目描述 输入格式 输出格式 思路分析 AC代码 题目总览 题目描述 小 A 的工作不仅繁琐,更有苛刻的规定,要求小 A 每天早上在 6:00 之前到达公司,否则这个月工资清零。可是小 A 偏偏又有赖床的坏毛病。于是为了保住自己的…...

如何定义resultType和resultMap,它们之间的区别是什么?解释一下<parameterType>的作用和用法。

在MyBatis中,resultType和resultMap都用于将数据库查询结果映射到Java对象,但它们在使用方式和灵活性上有一些区别。 resultType resultType是一个简单的类型别名,它用于指定查询结果应该映射到的Java类型。当数据库表中的列名和Java对象的属…...

Docker:部署微服务集群

1. 部署微服务集群 实现思路: ① 查看课前资料提供的cloud-demo文件夹,里面已经编写好了docker-compose文件 ② 修改自己的cloud-demo项目,将数据库、nacos地址都命名为docker-compose中的服务名 ③ 使用maven打包工具,将项目…...

傅里叶变换pytorch使用

参考视频:1 傅里叶变换原理_哔哩哔哩_bilibili 傅里叶变换是干嘛的: 傅里叶得到低频、高频信息,针对低频、高频处理能够实现不同的目的。 傅里叶过程是可逆的,图像经过傅里叶变换、逆傅里叶变换后,能够恢复到原始图像…...

LeetCode104 二叉树的最大深度

题目 给定一个二叉树 root ,返回其最大深度。二叉树的 最大深度 是指从根节点到最远叶子节点的最长路径上的节点数。 示例 示例 1: 输入:root [3,9,20,null,null,15,7] 输出:3示例 2: 输入:root [1,null,…...

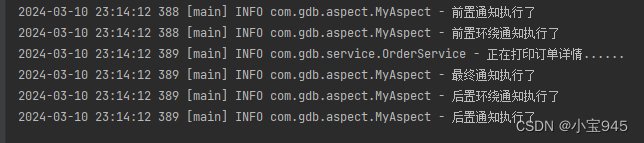

使用Spring的AOP

使用Spring的AOP 一、AOP 的常用注解1.切面类Aspect2.Pointcut3.前置通知Before4.后置通知AfterReturning5.环绕通知Around6.异常通知AfterThrowing7.最终通知After8.切面顺序Order9.启用自动代理EnableAspectJAutoProxy 二、AOP注解方式开发三、AOP 全注解开发四、基于XML配置…...

>)

爬虫之矛---JavaScript基石篇3<JavaScript构造函数的内部机制和应用(2)>

前言: 继续上一篇https://blog.csdn.net/m0_56758840/article/details/136592611 正文: 1.ES6中的类和构造函数的对应关系 A. 介绍ES6引入的类的概念和语法糖 类的概念: ES6引入了类(class)的概念,类是一种抽象的数据类型&…...

_note_05

1.说一说什么是函数重载? 函数签名相同除了 形参不同数据类型 函数签名相同除了 形参不同个数 2.void关键字的作用?返回值是void ,可以写return 吗? 函数无返回,使用void修饰; 可以只使用return使函数结束; 3.按要…...

将格蠹GDK8的cmake3.10升级为cmake3.15

#升级过程# 1、wget https://cmake.org/files/v3.15/cmake-3.15.0-rc1.tar.gz 2、tar -zxvf cmake-3.15.0-rc1.tar.gz 3 、cd cmake-3.15.0-rc1 4、./configure 5、sudo make install 6、reboot 7、查看cmake版本: geduergdk8:~$ cmake --version cmake ve…...

本地离线运行更安全!AI人脸隐私卫士,保护隐私无需上传云端

本地离线运行更安全!AI人脸隐私卫士,保护隐私无需上传云端 在社交媒体分享、企业宣传、新闻报道等场景中,我们常常需要发布包含人物的照片。然而,未经处理的人脸信息一旦公开,就可能面临隐私泄露的风险。手动给照片中…...

通义千问3-Reranker-0.6B应用指南:快速搭建智能问答排序服务

通义千问3-Reranker-0.6B应用指南:快速搭建智能问答排序服务 1. 引言:为什么选择Qwen3-Reranker-0.6B 在信息爆炸的时代,如何从海量文本中快速找到最相关的内容成为一大挑战。Qwen3-Reranker-0.6B作为通义千问家族的最新成员,专…...

游戏虚拟资产交易安全技术解析:以三角洲生态为例

一、引言随着《三角洲》等射击类游戏虚拟经济体系的成熟,哈夫币、战备账号、游戏道具等虚拟资产交易需求激增。据 2026 年游戏行业数据显示,三角洲虚拟资产月交易规模突破 5 亿元,但传统交易平台存在黑币溯源难、账号易封禁、资金无保障等核心…...

)

【2026年最新600套毕设项目分享】微信小程序的电子商城购物平台(30032)

有需要的同学,源代码和配套文档领取,加文章最下方的名片哦 一、项目演示 项目演示视频 二、资料介绍 完整源代码(前后端源代码SQL脚本)配套文档(LWPPT开题报告/任务书)远程调试控屏包运行一键启动项目&…...

把 CTS 权限边界讲透,SAP 传输体系里的角色设计、授权对象与最小权限落地

很多团队在做 CTS 安全治理时,真正出问题的地方并不在 STMS 能不能打开,也不在 SE09 能不能看到请求,而是在权限边界画得太粗。开发、运维、项目负责人、Basis 管理员,本来承担的工作就不一样,结果大家都被塞进一套大而全的角色里,最后形成一种很典型的局面,开发能看不该…...

彻底告别OpenClaw使用焦虑:我给他装上了“透视眼”和“批量克隆模组岳

指令替换 项目需求:将加法指令替换为减法 项目目录如下 /MyProject ├── CMakeLists.txt # CMake 配置文件 ├── build/ #构建目录 │ └── test.c #测试编译代码 └── mypass2.cpp # pass 项目代码 一,测试代码示例 test.c // test.c #includ…...

【价格型需求响应】基于Logistic函数的负荷转移率模型需求响应研究附Matlab代码

✅作者简介:热爱科研的Matlab仿真开发者,擅长数据处理、建模仿真、程序设计、完整代码获取、论文复现及科研仿真。🍎 往期回顾关注个人主页:Matlab科研工作室🍊个人信条:格物致知,完整Matlab代码及仿真咨询…...

ESP32 PlatformIO I/O扩展驱动:统一抽象与线程安全控制

1. 项目概述htcw_esp_io_expander是一个面向 ESP32 系列微控制器(特别是 ESP32-S2/S3/C3/C6)的 I/O 扩展驱动组件,其本质是将 Espressif 官方 ESP-IDF 组件仓库中io_expander模块封装为 PlatformIO 兼容的独立软件包。该组件并非全新实现&…...

DeOldify服务监控方案:Prometheus+Grafana实时跟踪GPU利用率与QPS

DeOldify服务监控方案:PrometheusGrafana实时跟踪GPU利用率与QPS 1. 监控方案概述 在实际的AI服务部署中,仅仅能够运行服务是不够的。我们需要实时了解服务的运行状态、资源使用情况以及性能指标。对于DeOldify这样的深度学习图像上色服务,…...

QTableWidget 表格组件攘

7.1 初识三维模型 7.1.1 三维模型的数据载体 随着计算机图形技术的发展,我们或多或少都会见过或者听说过三维模型。笔者始终记得小时候第一次在电视上看到三维动画《变形金刚:超能勇士》的震撼感受;而现在我们已经可以在手机上玩三维游戏《王…...