景芯2.5GHz A72训练营dummy添加(一)

景芯A72做完布局布线之后导出GDS,然后进行GDS merge,然后用Calibre对Layout添加Dummy。在28nm以及之前的工艺中,Dummy metal对Timing的影响不是很大,当然Star RC也提供了相应的解决方案,可以考虑Dummy metal来抽取RC。但是12nm、7nm、5nm等先进工艺必须考虑dummy对timing的影响。

为什么添加dummy?

版图metal/poly/AA和via等有density的要求,添加dummy是出于良率的考量,是为了减少废片/降低成本。比如,金属密度不一致会导致高低不平,机械研磨(平坦化)的时候,密度过大的地方会把不想磨掉的磨掉,密度小的地方想磨掉的又磨不掉,PO和OD也会有密度要求,制程越小密度问题越明显。另外,添加dummy后,在化学蚀刻时,可以使得金属腐蚀得更均匀,保护走线不被过度腐蚀而断掉。此外,bonding的时候,如果bonding区域和旁边金属密度相差过大,可能会把芯片打裂。

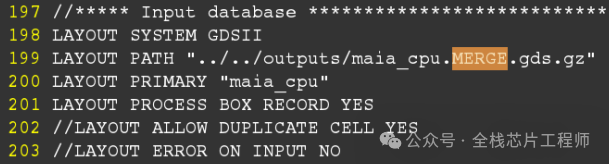

景芯2.5GHz A72用Calibre基于layout merge之后的GDS来添加Dummy(包括metal, via, poly, AA等)的流程。命令如下:

![]()

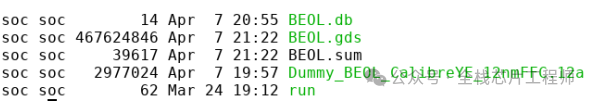

生成文件:

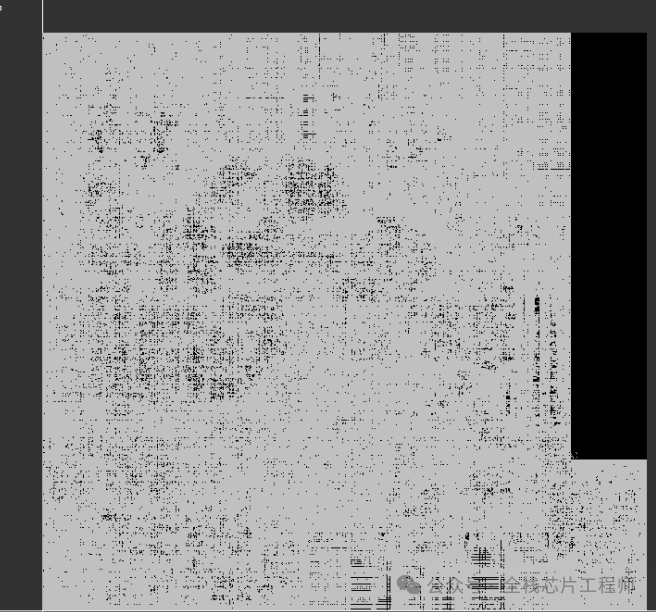

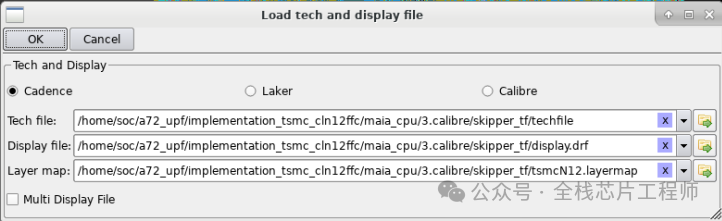

添加tf等文件后:

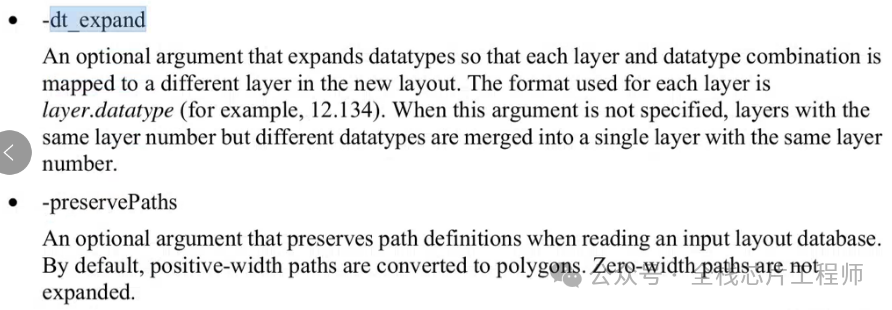

然后我们merger dummy,具体脚本参见景芯服务器,其中几个option如下:

未完待续,下一篇接着聊。

“2.5GHz频率 hierarchy DVFS低功耗A72培训”

一. 培训内容:

2.5GHz hierarchy DVFS低功耗 A72实战

-

项目规模315万instance,2000万Gate count。

-

工具有VCS/Fusion Compiler/VCLP

-

工具有innovus/Starrc/PT/Voltus/formality/LEC/Calibre

-

更详细的培训内容参见本文末尾

二. 培训形式:

-

录播+文档+上机实践,一对一答疑!真实项目flow!

-

VPN远程连接景芯服务器,随时随地、随到随学!

-

景芯合伙人教师皆为10年以上资深大佬!

-

景芯合伙人不仅提供真实项目培训,也提供设计外包、design service!

-

支持对公,可开培训、技术服务发票

三. 课程教学时间

-

教学时间3个月,续期直接6折。

四. 适合的对象

-

追求业界顶尖后端项目能力的后端工程师

-

初级、中级后端工程师的进阶

-

前端设计/验证人员(全栈芯片工程师之路)

-

在校研究生、本科生同学,超越同龄人的法宝

-

Layout版图工程师

-

转行的学员朋友

五. 报名方式

关注公众号全栈芯片工程师,后台私信小编。

六. 价格

-

原价15000元,现价6999元!

-

转发朋友圈、IC微信群立减100元!

-

两人以上组团报名每人减500元!

-

报名截止时间:2024年3月31日!

01

2.5GHz 12nm DVFS A72后端实战

本培训项目是真实项目,低功耗hierarchy UPF设计,价格是知名机构的1/3,全网最低价。DVFS hierarchy低功耗A72后端实战内容简介如下:

1) 根据低功耗需求,编写UPF验证UPF

掌握hierarchy UPF文件编写,掌握Flatten UPF文件编写。

本项目采用hierarchy UPF方式划分了7个power domain、voltage domain,指定power switch cell,其中包括SWITCH TRICKLE、SWITCH HAMMER。掌握低功耗cell的用法,选择合适的isolation cell、level shifter等低功耗cell。

掌握Power gating,Clock gating设计技术。

掌握Multi-VT设计技术,本项目时钟树都是ULVT,动态功耗小,skew小。

掌握DVFS技术,ss0p9 2.5GHz、ss0p72 2.0GHz,,其中sram不支持ss0p63。要做ss0p63的话,给sram vddm单独一个0p7v的电源即可。

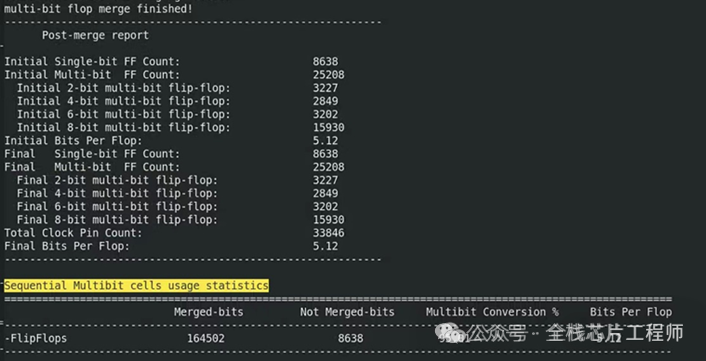

掌握multibit cell的用法,本项目CPU里面的mb高达95%,选择合适的multibit cell得到超高的CPU利用率。INNOVUS里面一般不做mb的merge和split。所以前后一样的,一般综合做multibit的merge split。

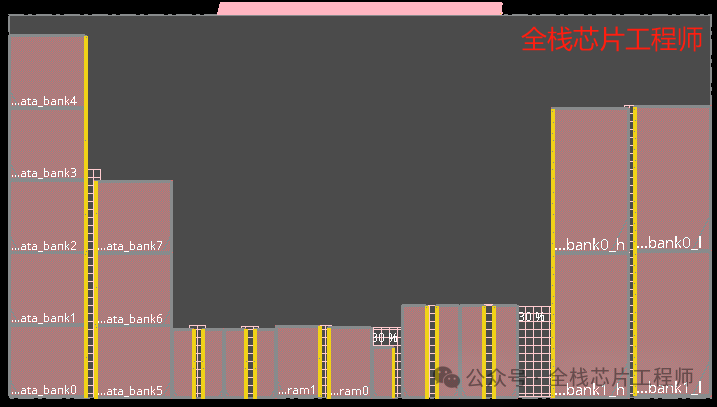

2) 根据top floorplan def进行CPU子系统的partition以及pin assignment。

Top的Power stripe的规划及其push down。

SpecifyBlackBox,将CPU core镜像partition。

手动manual cut the BlackBox的方法,掌握复杂的floorplan设计方法经验。

VerifyPowerDomain,检查低功耗划分以及UPF的正确性。

Pin assignment,根据timing的需求进行合理的pin脚排布,并解决congestion问题。

掌握Timing budget。

掌握利用Mixplace实战CPU的自动floorplan,掌握AI的floorplan方法学。

3) 掌握Fusion compiler DCG,利用fusion compiler来完成DCG综合,进一步优化timing与congestion。

4) 掌握hierarchy ICG的设计方法学,实战关键ICG的设置与否对timing的重大影响。

5) 掌握Stapling技术,实战power switch cell的布局和特殊走线的方法学,掌握CPU子系统的powerplan规划及实现,保证CPU子系统和顶层PG的alignment。

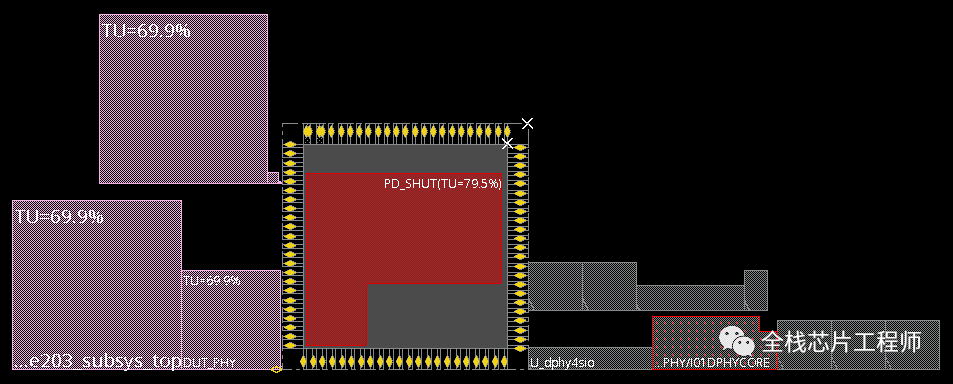

6) 掌握CPU子系统和TOP的时序接口优化。掌握TOP isolation cell的placement以及isolation cell input电学特性检查。

7) 掌握TOP和CPU子系统的clock tree Balance优化处理,common clock path处理。时钟树结构trace和时钟树评价。

8) DRC/LVS

CPU子系统的DRC/LVS检查

TOP系统的DRC/LVS检查

Hierarchy & Flatten LVS检查原理及实现方法

9) 静态时序分析&IR-Drop

DMSA flow

根据Foundry的SOD(signoff doc)的Timing signoff标准建立PT环境。

Star RC寄生抽取及相关项检查

Timing exception分析,包括set_false_path、set_multicyle_path解析。

PT timing signoff的Hierarchical和Flatten Timing检查

PT和PR timing的差异分析、Dummy insertion和with dummy的Timing分析

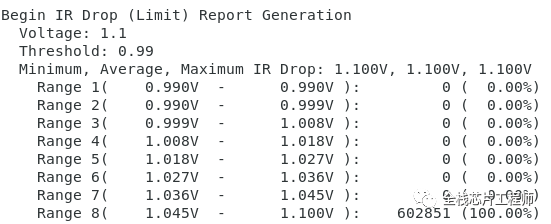

IR-Drop分析

Stampling打起来真是高级手工艺术,全网唯一:

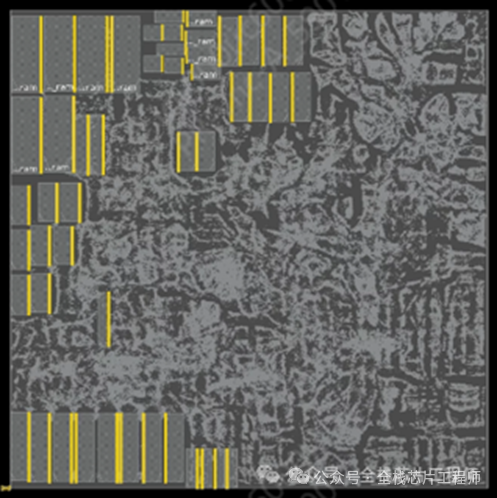

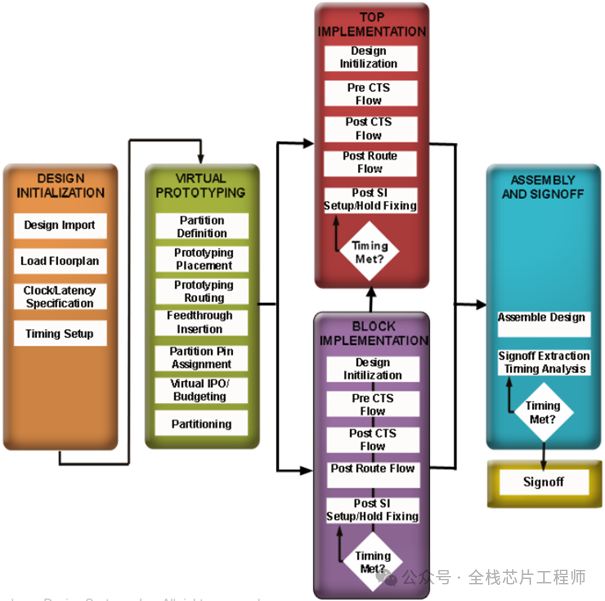

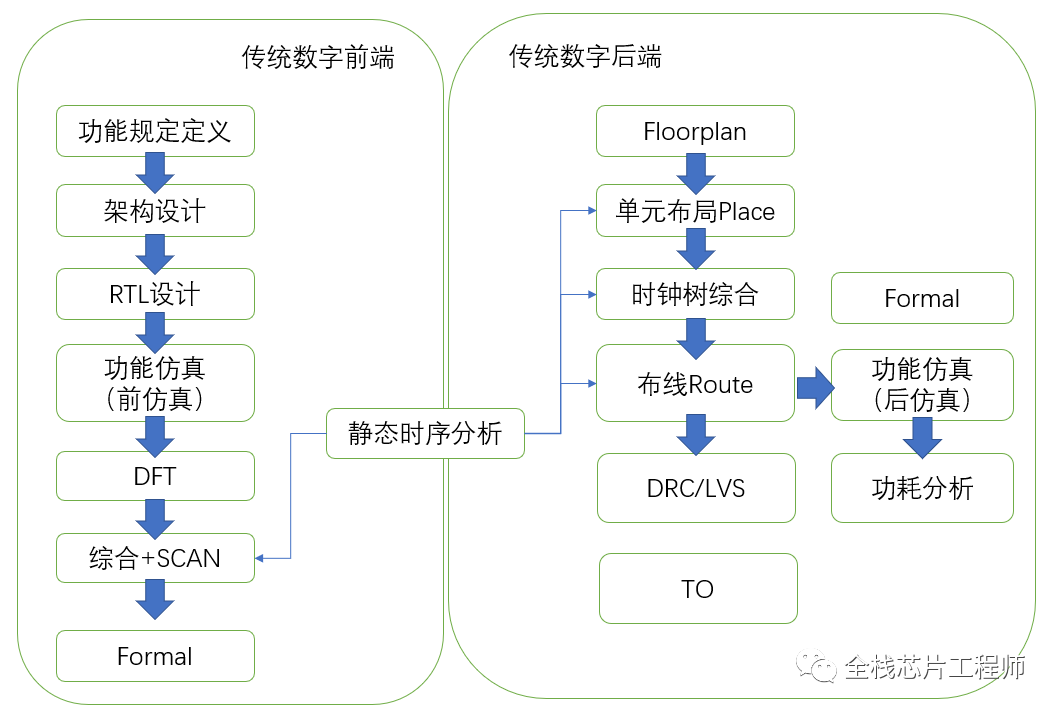

Flow:Partition Flow

时钟结构分析:

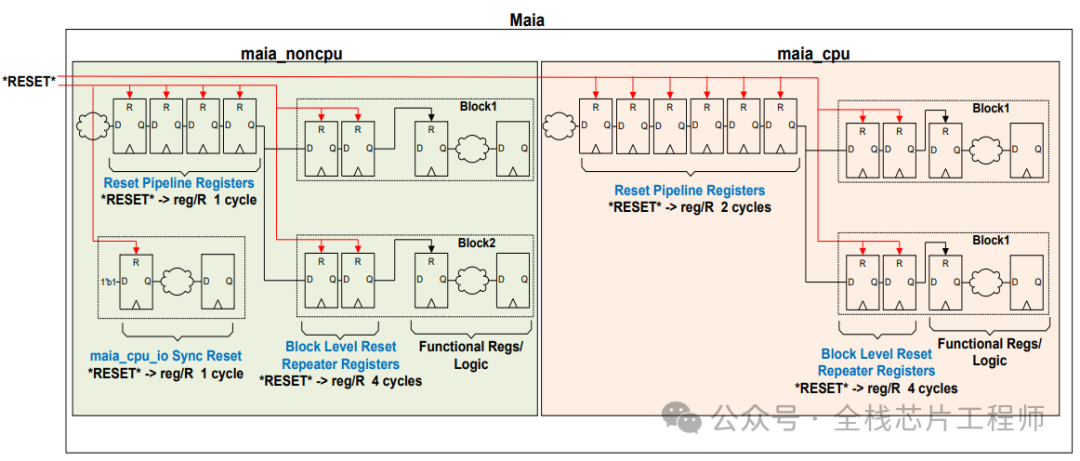

复位结构分析:

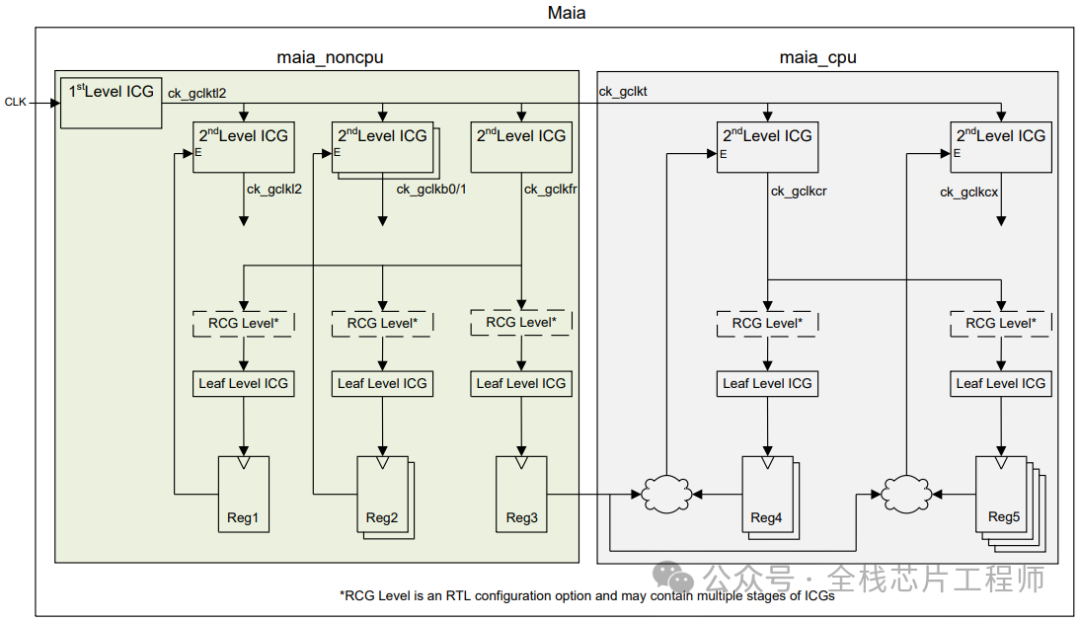

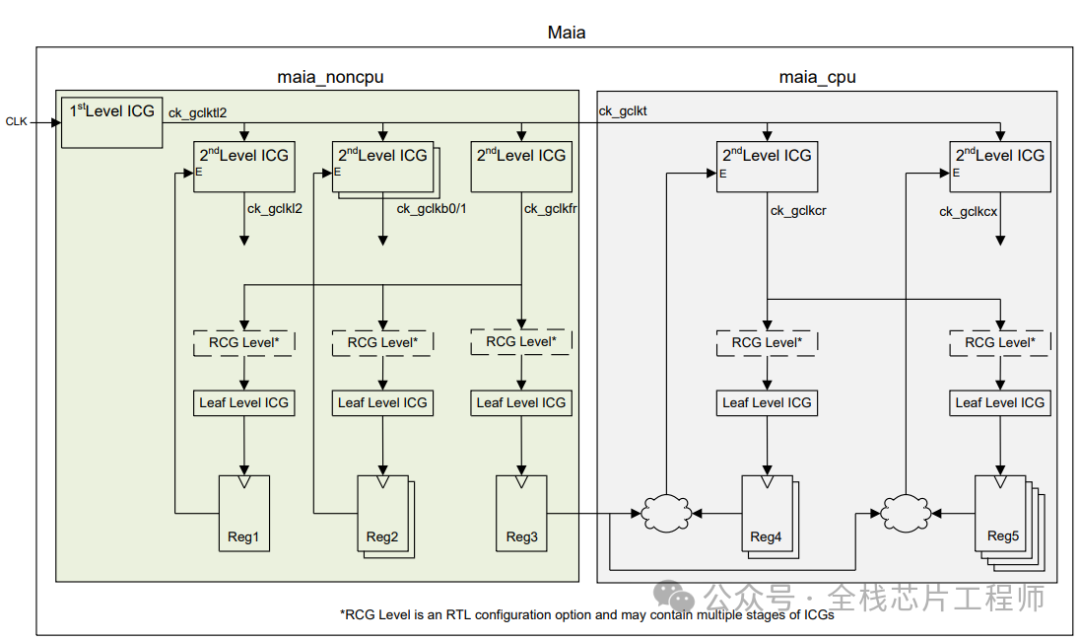

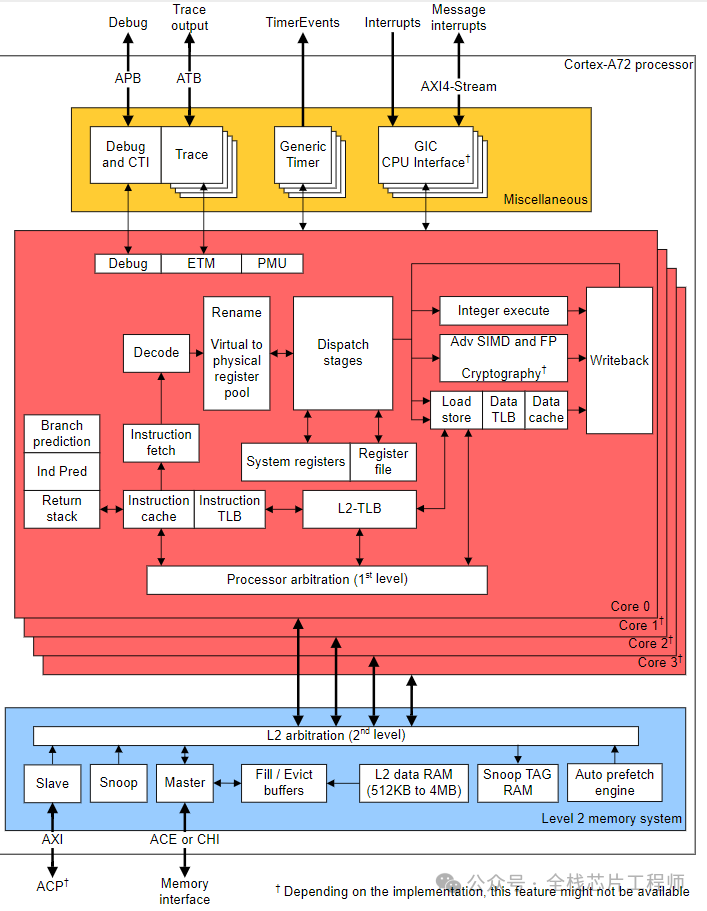

12nm 2.5GHz的A72实战训练营需要特别设置Latency,TOP结构如下,参加过景芯SoC全流程训练营的同学都知道CRG部分我们会手动例化ICG来控制时钟,具体实现参见40nm景芯SoC全流程训练项目,本文介绍下12nm 2.5GHz的A72实战训练营的Latency背景,欢迎加入实战。

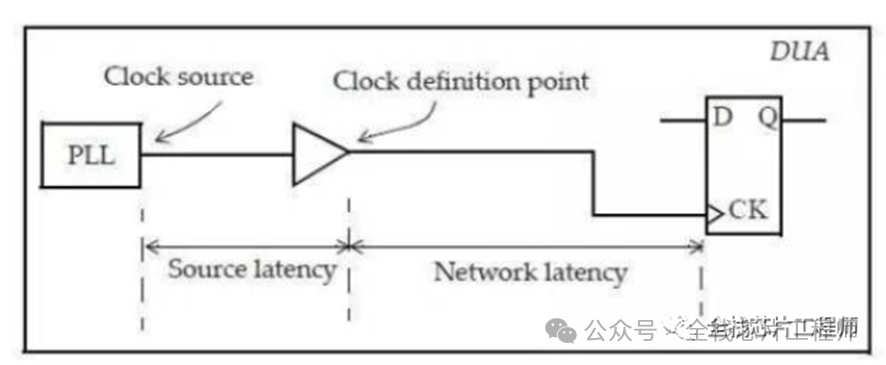

时钟传播延迟Latency,通常也被称为插入延迟(insertion delay)。它可以分为两个部分,时钟源插入延迟(source latency)和时钟网络延迟(Network latency)。

大部分训练营同学表示平时都直接将Latency设置为0了,那latency值有什么用呢?其实这相当于一个target值,CTS的engine会根据你设置的latency值来插入buffer来实现你的latency target值。

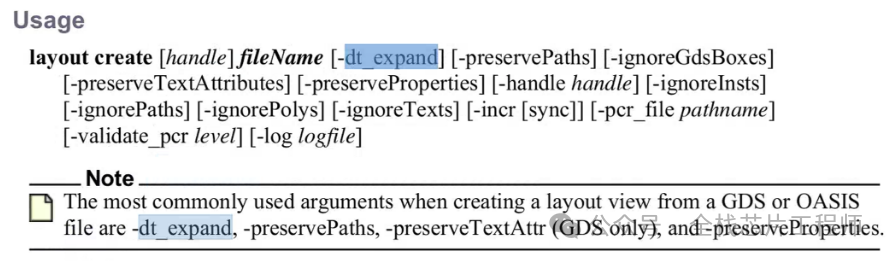

下图分为1st Level ICG和2nd Level ICG,请问这些ICG为什么要分为两层?

请问,为什么不全部把Latency设置为0?2nd Level ICG的latency应该设置为多少呢?

latency大小直接影响clock skew的计算。时钟树是以平衡为目的,假设对一个root和sink设置了400ps的latency值,那么对另外的sink而言,就算没有给定latency值,CTS为了得到较小的skew,也会将另外的sink做成400ps的latency。请问,为何要做短时钟树?因为过大的latency值会受到OCV和PVT等因素的影响较大,并有time derate的存在。

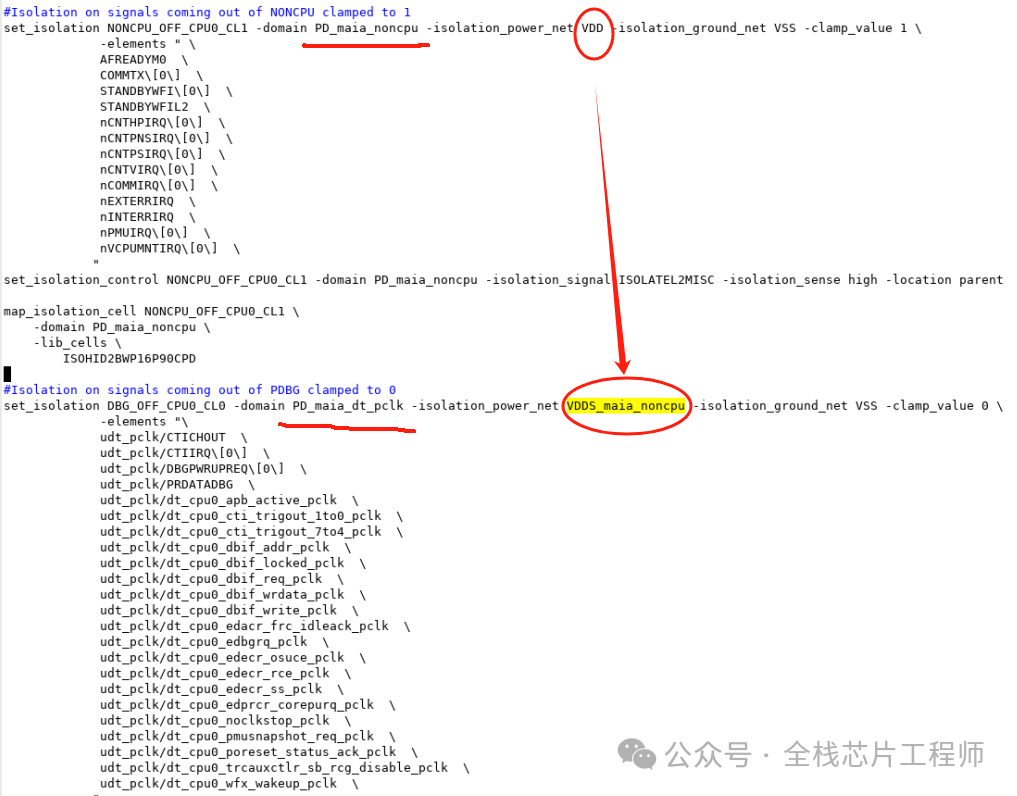

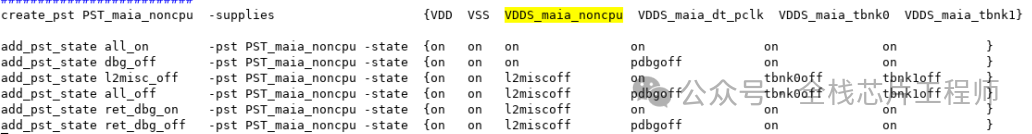

分享个例子,比如,Cortex-A72低功耗设计,DBG domain的isolation为何用VDDS_maia_noncpu供电而不是TOP的VDD?

答:因为dbg的上一级是noncpu,noncpu下面分成dbg和两个tbnk。

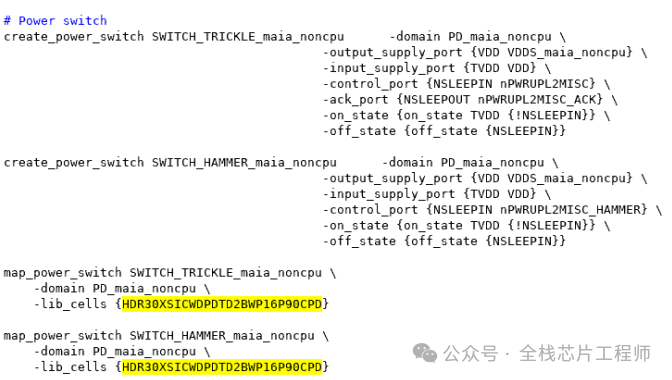

再分享个例子,比如,Cortex-A72低功耗设计,这个switch cell是双开关吗?答:不是,之所以分trickle和hammer,是为了解决hash current大电流,先开trickle,然后再开hammer。

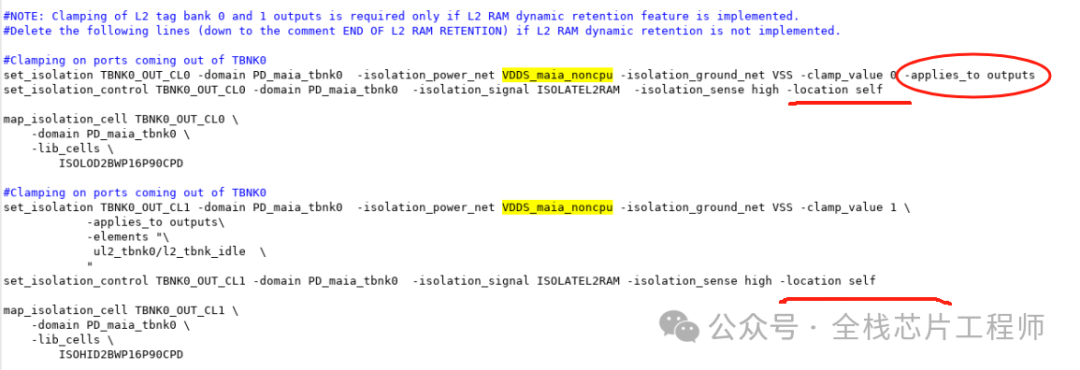

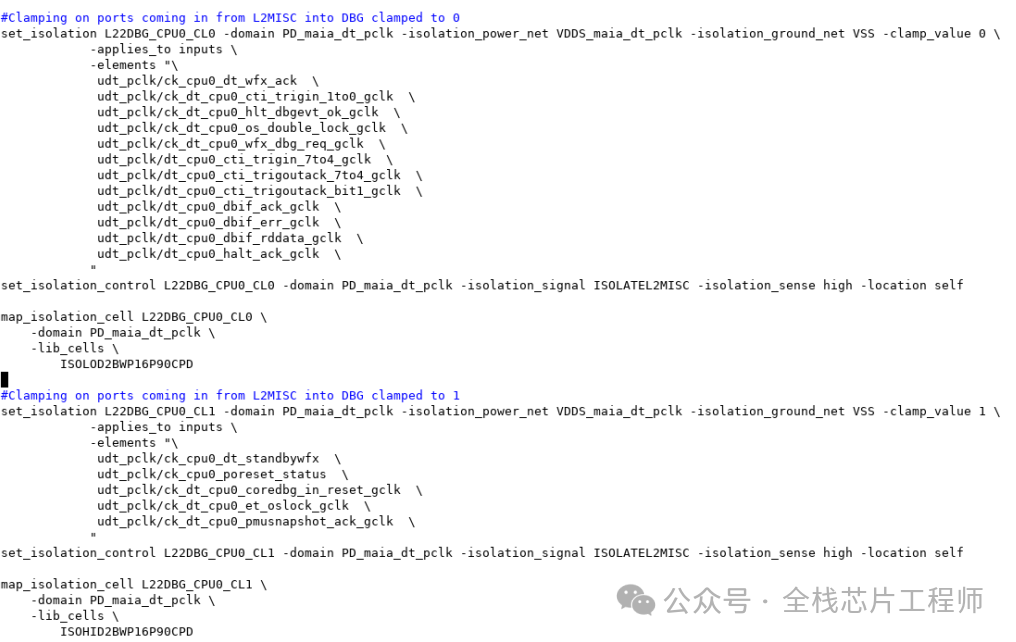

再分享个例子,比如,Cortex-A72进阶版本课程的低功耗例子:请问,如果iso cell输出都要放parent,输入放self,那么下面-applies_to_outputs对应的-location为何是self?

答:这个需要了解CPU的内部设计架构,tbnk掉电 VDDS_maia_noncpu也必然掉电,pst如下,所以-applies_to_outputs对应的-location是可以的,那么注意下debug domain呢?

实际上,没有tbnk到debug domain的信号,因此脚本如下:

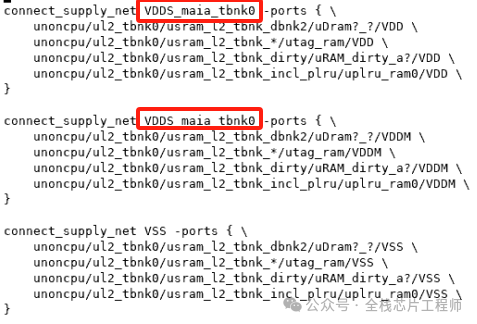

再分享个例子,比如,Cortex-A72进阶版本课程的低功耗例子:为何non_cpu的SRAM的VDD VDDM都接的可关闭电源?SRAM的VDD VDDM分别是常开、和retention电源吧?

答:本来是VDDM作为retention电源设计的,VDD关掉后 VDDM可以供电作为retention使用,但是此处没有去做memory的双电源,sram当成单电源使用,不然sram无法彻底断电。

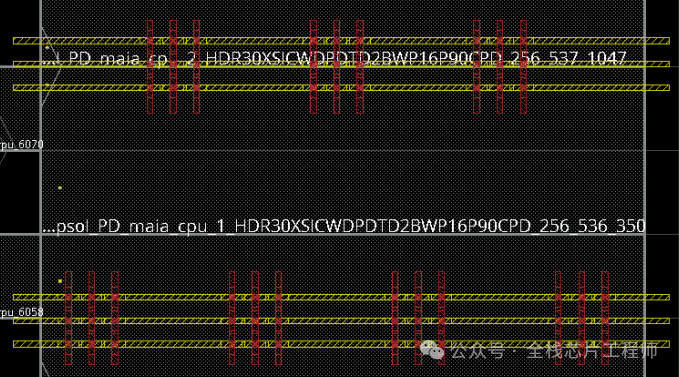

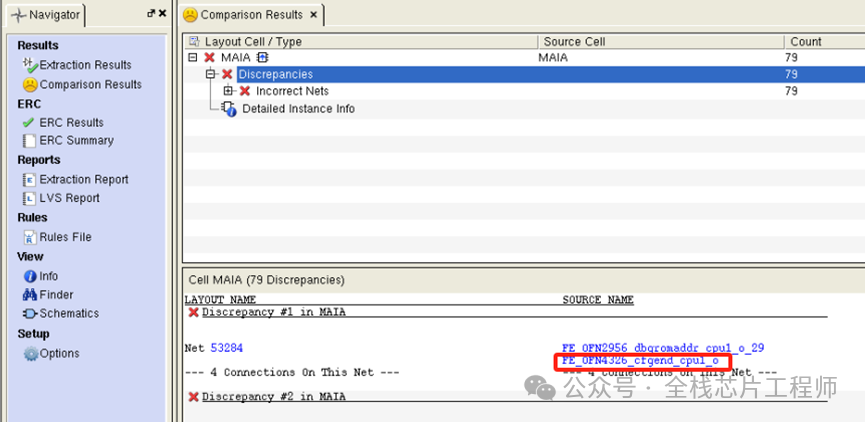

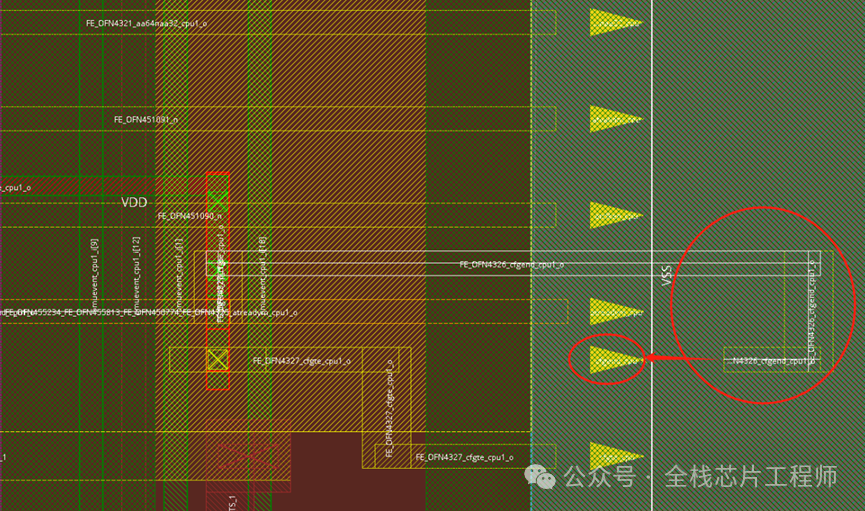

再分享个例子,比如,Cortex-A72基础版课程有学员的Cortex-A72 maia_cpu LVS通过, 但是MAIA顶层LVS比对不过,我们来定位一下。

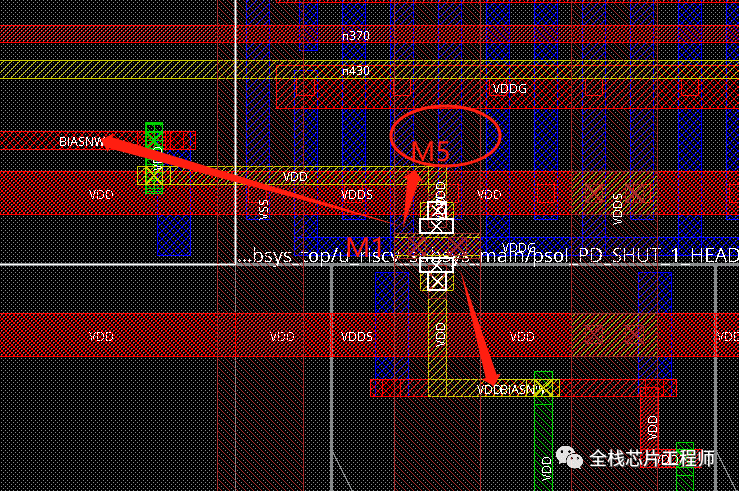

以FE_OFN4326_cfgend_cpu1_o为例,点击下图FE_OFN4326_cfgend_cpu1_o:

找到calibredrv错误坐标:(1949,139)

对应到innovus去看坐标:(1949,139)

看到maia_cpu的pin脚过于密集,造成顶层连接pin脚时候会无法绕线,从而导致innovus从maia_cpu上面走线,形成short。尽管maia_cpu带了blockage,但是invs没有足够的连接pin的routing resource,也就只能在maia_cpu上面去try了。

修改办法很简单,具体操作option参见知识星球。

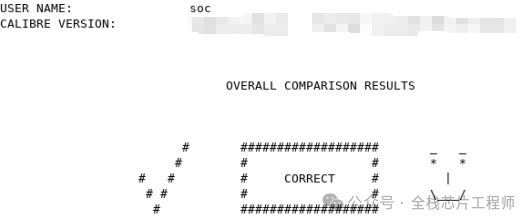

保存db,重新LVS,比对通过。

02

28nm Cortex-A7后端实战

此外,我们提供全网最低价的28nm A7后端设计,价格惊喜!打垮动辄1.5w-2.5w的后端培训价格!

我们再来对比下A72与A7的资源。A72 Gate数目是A7的13倍!如果都采用28nm制程,A72的面积应该是1180790um^2,实际A72采用12nm制程面积是486100um^2,1180790/486100=2.4,符合摩尔定律。

Cortex-A7单核:

Gates=240291 Cells=118421

Cortex-A72单核:

Gates=3125649 Cells=1207766

28nm Cortex-A7单核:

Area=90830.1 um^2

12nm Cortex-A72单核:

Area=486100.9 um^2

28nm A7后端设计课程采用的全国最低价格来推广,本文不做过多介绍,本文重点介绍下先进的12nm A72进阶版本课程。

03

12nm Cortex-A72—DFT实战

开发完成,全国最低价!

04

景芯SoC—全芯片UPF后端实战

景芯SoC培训的全芯片UPF低功耗设计(含DFT设计)

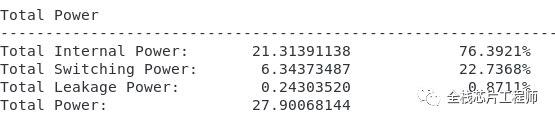

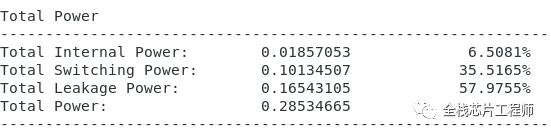

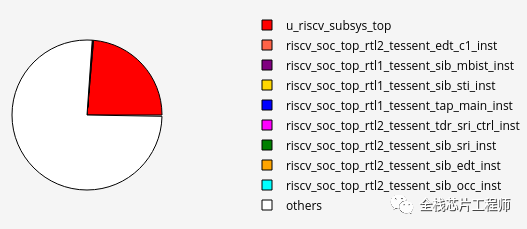

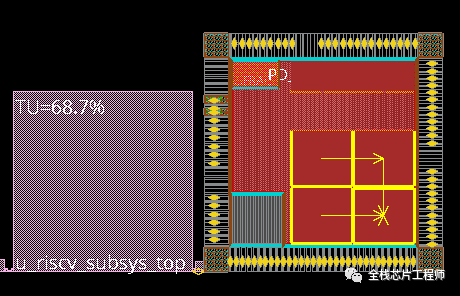

景芯SoC训练营培训项目,低功耗设计前,功耗为27.9mW。

低功耗设计后,功耗为0.285mW,功耗降低98.9%!

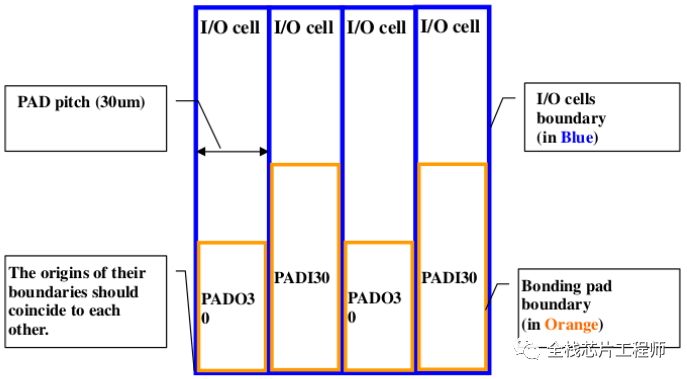

7天冲刺PR训练营有同学问如何给IO添加PAD?请思考景芯SoC的IO和PAD如何实现最佳?

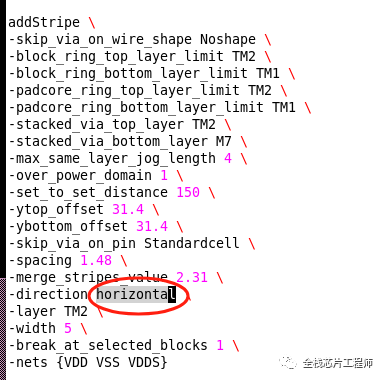

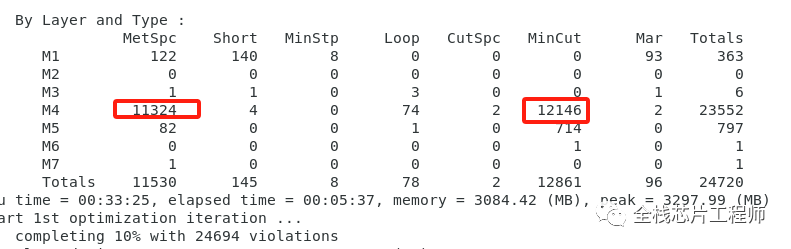

7天冲刺PR训练营有同学问,同样的floorplan,有些同学很快跑完,有些同学则遇到大量DRC问题(EDA工具不停iteration)导致工具始终无法跑完,具体什么问题呢?

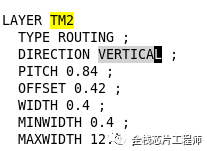

首先,小编发现该同学的stripe把TM2定义为了horizontal,而熟悉景芯工艺的同学知道,TM2的preference direction是VERTICAL。

查询景芯的lef库文件也可以确认:

用错方向有多大影响呢?大家上景芯SoC的后端flow实践一下吧,实践出真知。

7天冲刺PR训练营有同学问,为啥PR花了一天一夜24个小时完成布线还大量DRC错误?小编已经将设计规模尽可能减小以加速PR设计,实际上2小时就可以跑完routing,为何这么慢?原因就是低功耗单元的走线。具体原因及解决办法欢迎加入景芯训练营讨论。

其错误主要集中在M4上,请思考如何解决。

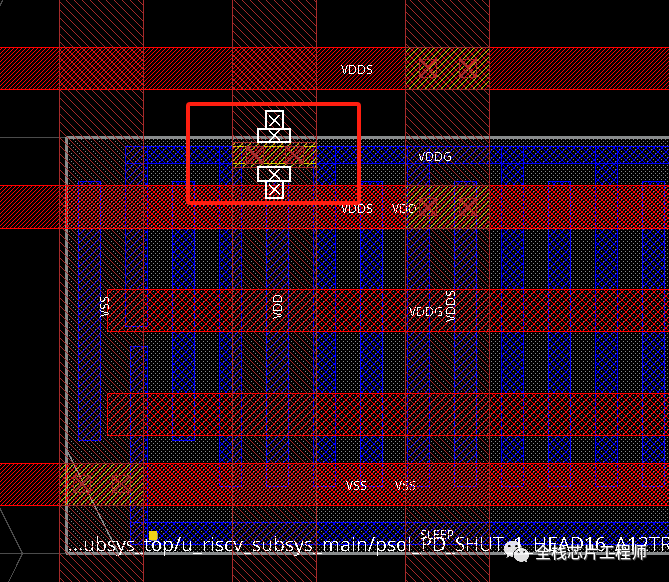

7天冲刺PR训练营有同学问,power switch cell的secondPG pin(VDDG)从M1接出的,而不是M2, 请思考有什么问题?如何解决?

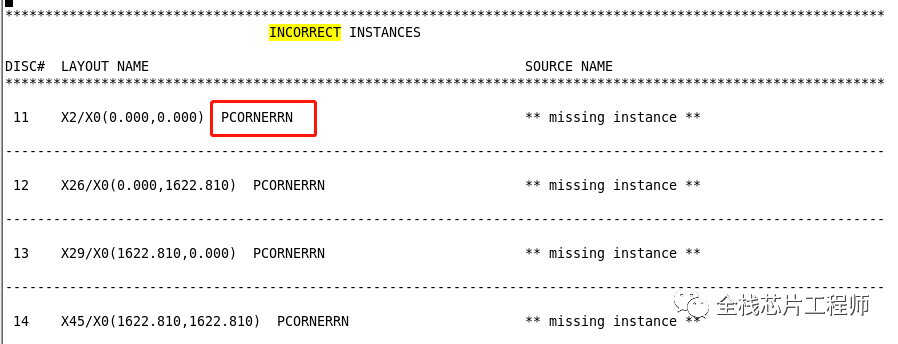

7天冲刺PR训练营有同学问,景芯SoC培训营同学遇到Corner Pad LVS不过怎么处理?

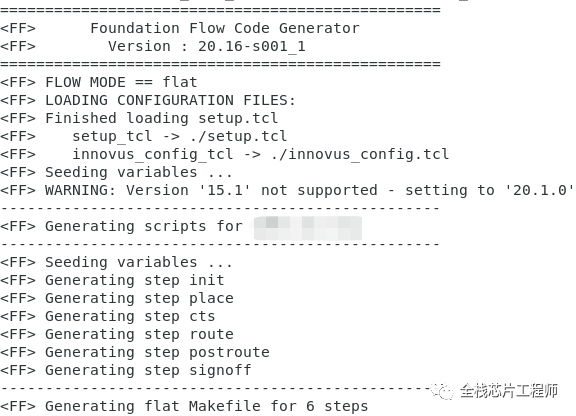

完成景芯SoC培训的前端设计仿真、DFT后,我们来到后端flow,本教程教你一键式跑完数字后端flow。

生成脚本命令如下:

tclsh ./SCRIPTS/gen_flow.tcl -m flat all

生成flow脚本之前需要配置setup.tcl等相关参数,具体参见【全网唯一】【全栈芯片工程师】提供自研的景芯SoC前端工程、DFT工程、后端工程,带你从算法、前端、DFT到后端全流程参与SoC项目设计。

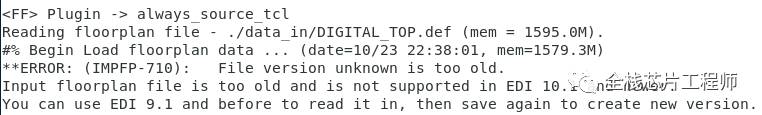

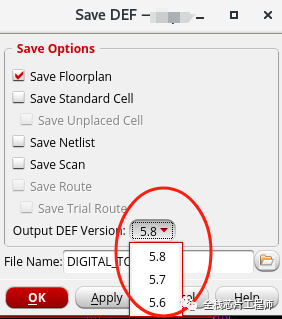

景芯SoC训练营的同学问,为何innovus读取做好的floorplan def文件报Error? 首先看log:

Reading floorplan file - ./data_in/DIGITAL_TOP.def (mem = 1595.0M).

#% Begin Load floorplan data ... (date=10/23 22:38:01, mem=1579.3M)

**ERROR: (IMPFP-710): File version unknown is too old.

以前EDI的时期,我们可以通过定义fp_file的方式来加载floorplan:

set vars(fp_file) "./data_in/DIGITAL_TOP.def"

但是现在innovus升级并放弃了fp_file的加载方式,当然也可以用老版本的EDI9.1及以前版本来加入fp_file,然后转存为新版本,这方式明显没有必要。正如下log提示所说,检查log是非常好的工程师习惯。

Input floorplan file is too old and is not supported in EDI 10.1 and newer.

You can use EDI 9.1 and before to read it in, then save again to create new version.

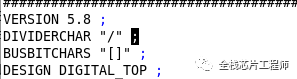

小编的直觉告诉我,先去看看同学保存的def文件是哪个def版本?

同学保存方式如下:

那么请问如何解决?请大家加入景芯训练营实践。

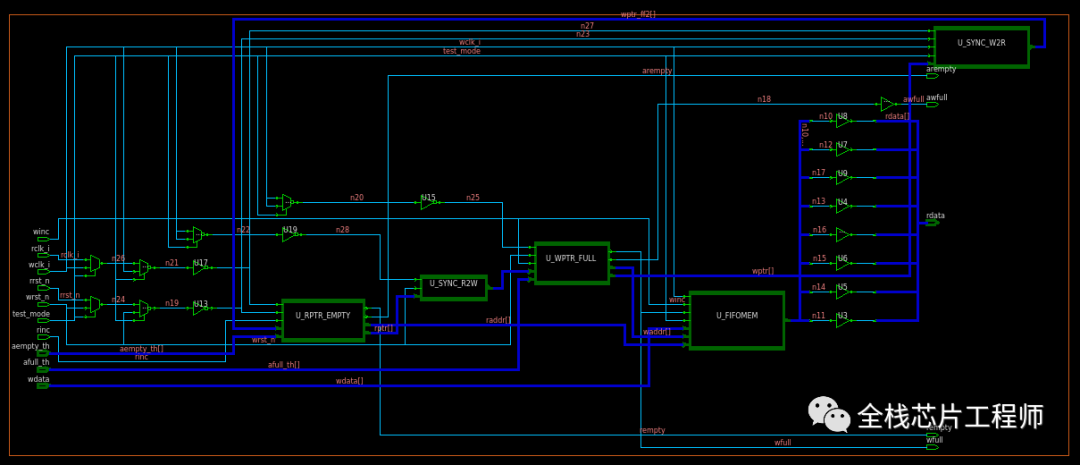

景芯SoC用了很多异步FIFO,关注异步RTL实现的同学,可以抓取异步FIFO出来看一下版图连线:

查看下所有异步FIFO cell的面积;

dbget [dbget top.insts.pstatus unplaced -p].area

查下所有异步FIFO的cell的名字:

dbget [dbget top.insts.pstatus unplaced -p].name

那么怎么抓出异步路径来观察版图走线呢?如何让report_timing呢?更多内容参见知识星球和SoC训练营。

相关文章:

景芯2.5GHz A72训练营dummy添加(一)

景芯A72做完布局布线之后导出GDS,然后进行GDS merge,然后用Calibre对Layout添加Dummy。在28nm以及之前的工艺中,Dummy metal对Timing的影响不是很大,当然Star RC也提供了相应的解决方案,可以考虑Dummy metal来抽取RC。…...

React - 请你说一说setState是同步的还是异步的

难度级别:中高级及以上 提问概率:70% 在React项目中,使用setState可以更新状态数据,而不能直接使用为this.state赋值的方式。而为了避免重复更新state数据,React首先将state添加到状态队列中,此时我们可以通过shouldComponentUpdate这个钩…...

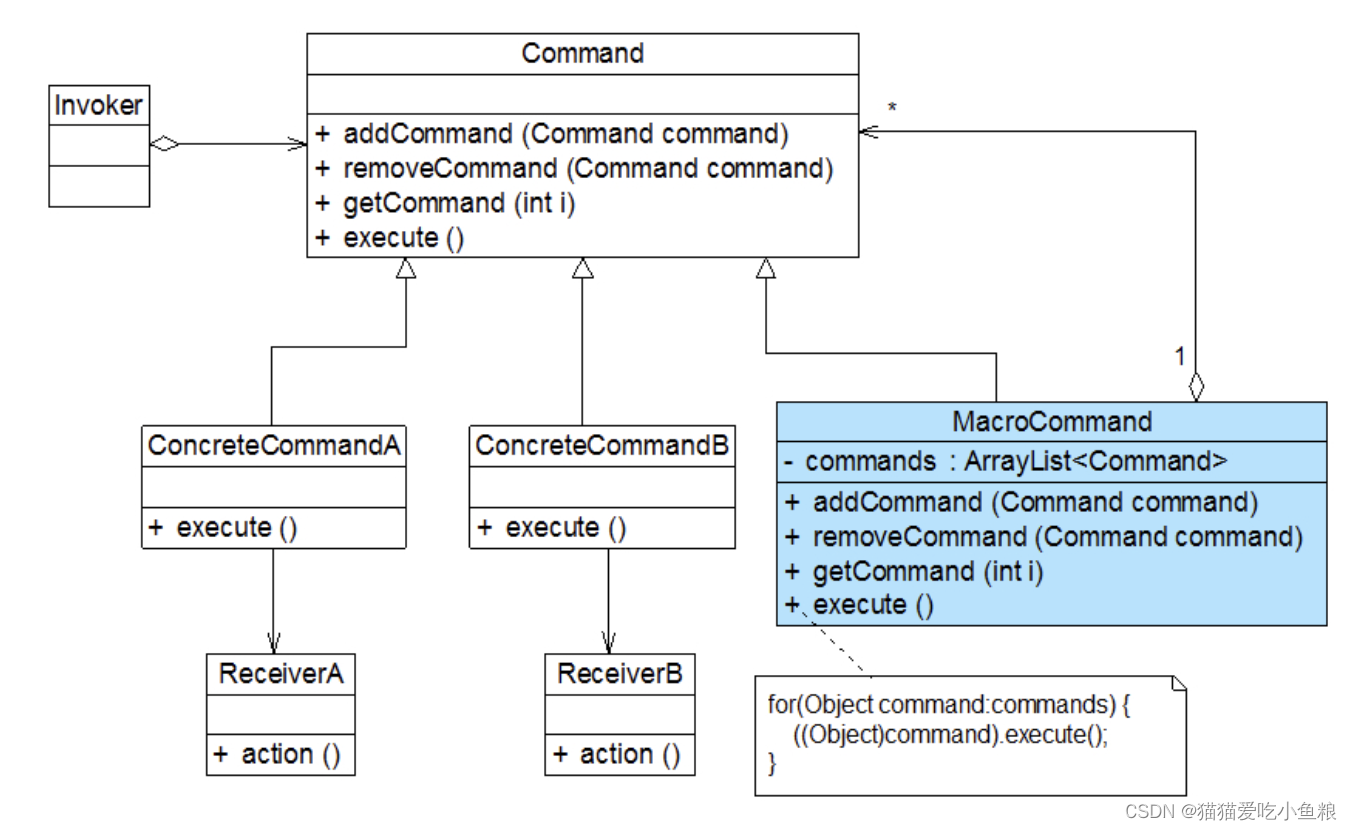

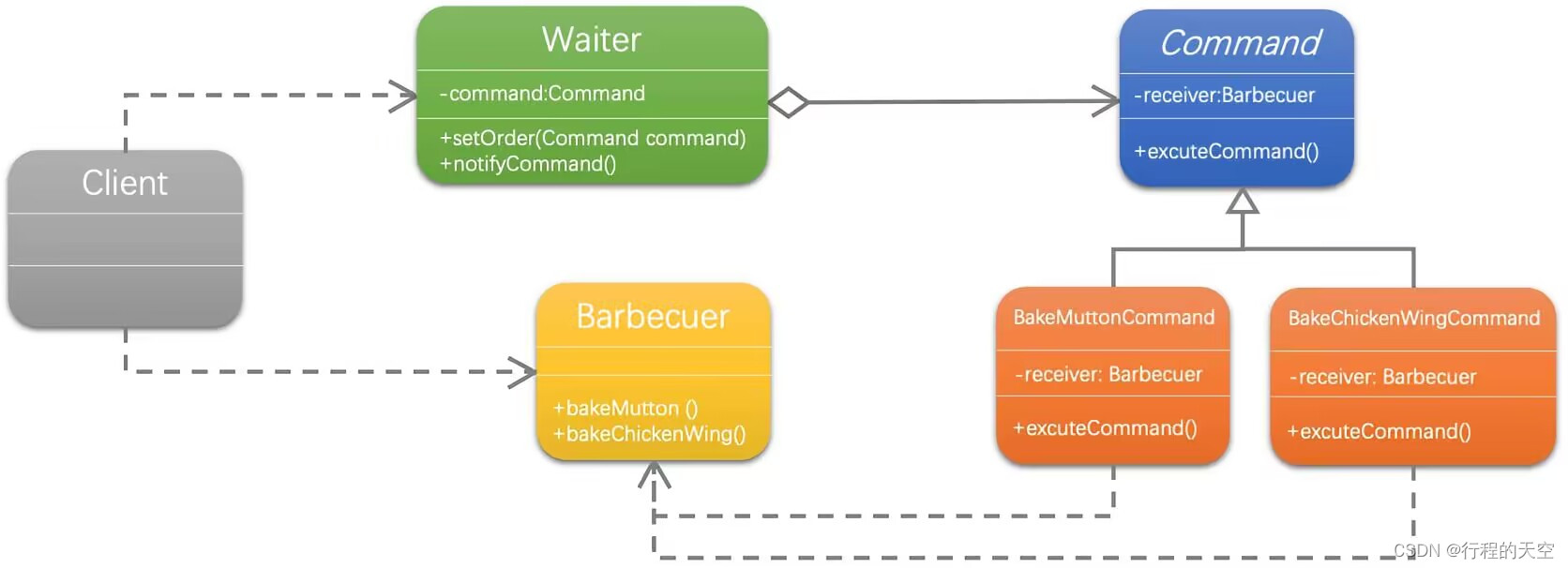

设计模式之命令模式(下)

2)完整解决方案 1.结构图 FBSettingWindow是“功能键设置”界面类,FunctionButton充当请求调用者,Command充当抽象命令类,MinimizeCommand和HelpCommand充当具体命令类,WindowHanlder和HelpHandler充当请求接收者。 …...

【opencv】示例-demhist.cpp 调整图像的亮度和对比度,并在GUI窗口中实时显示调整后的图像以及其直方图。...

#include "opencv2/core/utility.hpp" // 包含OpenCV核心工具库的头文件 #include "opencv2/imgproc.hpp" // 包含OpenCV图像处理的头文件 #include "opencv2/imgcodecs.hpp" // 包含OpenCV图像编码解码的头文件 #include "opencv2/highgui…...

计算机网络---第三天

OSI参考模型与TCP/IP模型 参考模型产生背景: 背景:①兼容性较差,接口不统一 ②不利于排错与维护 ③设备成本高 参考模型概念: 概念:OSI参考模型定义了网络中设备所遵守的层次结构 参考模型优点: 优点…...

怎么防止文件被拷贝,复制别人拷贝电脑文件

怎么防止文件被拷贝,复制别人拷贝电,脑文件 防止文件被拷贝通常是为了保护敏感数据、知识产权或商业秘密不被未经授权的人员获取或传播。以下列出了一系列技术手段和策略,可以帮助您有效地防止文件被拷贝。 1. 终端管理软件: 如安企神、域智…...

流式密集视频字幕

流式密集视频字幕 摘要1 IntroductionRelated Work3 Streaming Dense Video Captioning Streaming Dense Video Captioning 摘要 对于一个密集视频字幕生成模型,预测在视频中时间上定位的字幕,理想情况下应该能够处理长的输入视频,预测丰富、…...

【教程】iOS Swift应用加固

🔒 保护您的iOS应用免受恶意攻击!在本篇博客中,我们将介绍如何使用HTTPCORE DES加密来加固您的应用程序,并优化其安全性。通过以下步骤,您可以确保您的应用在运行过程中不会遭受数据泄露和未授权访问的风险。 摘要 …...

)

新型基础设施建设(新基建)

新型基础设施建设(新基建)主要包括七个方面,即5G基站建设、特高压、城际高速铁路和城市轨道交通、新能源汽车充电桩、大数据中心、人工智能和工业互联网。 以下是新型基础设施的详细内容: 一、5G基站建设。5G网络的扩展和优化&a…...

蓝桥杯 第 9 场 小白入门赛 字符迁移

题目: 3.字符迁移【算法赛】 - 蓝桥云课 (lanqiao.cn) 思路: 此题通过把小写字母映射成数字,进行差分即可。 AC代码: #include<iostream> #include<cstring> #include<algorithm>using namespace std;typed…...

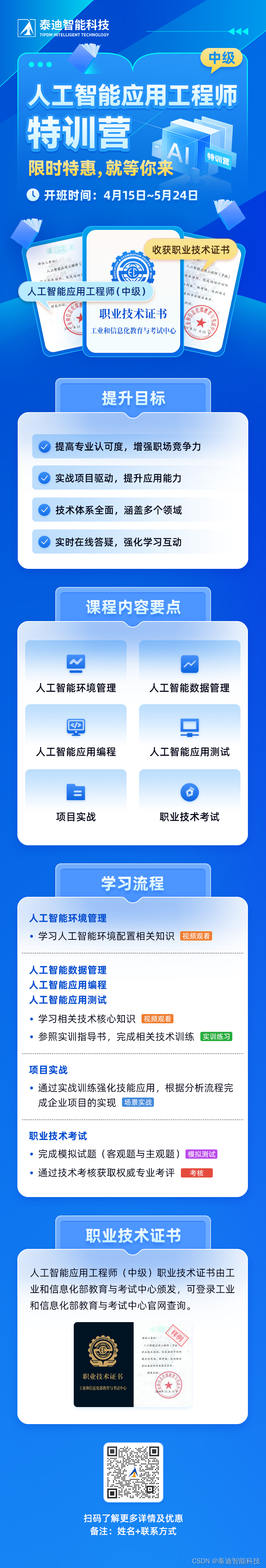

泰迪智能科技人工智能应用工程师(中级)特训营

随着人工智能技术的迅猛发展和应用的不断拓展,掌握人工智能技术已成为现代职业发展和企业创新的关键。为此,人工智能技能提升特训营应运而生,以全面、系统的课程设置,帮助学员深入掌握相关的理论知识,实践操作技能。特…...

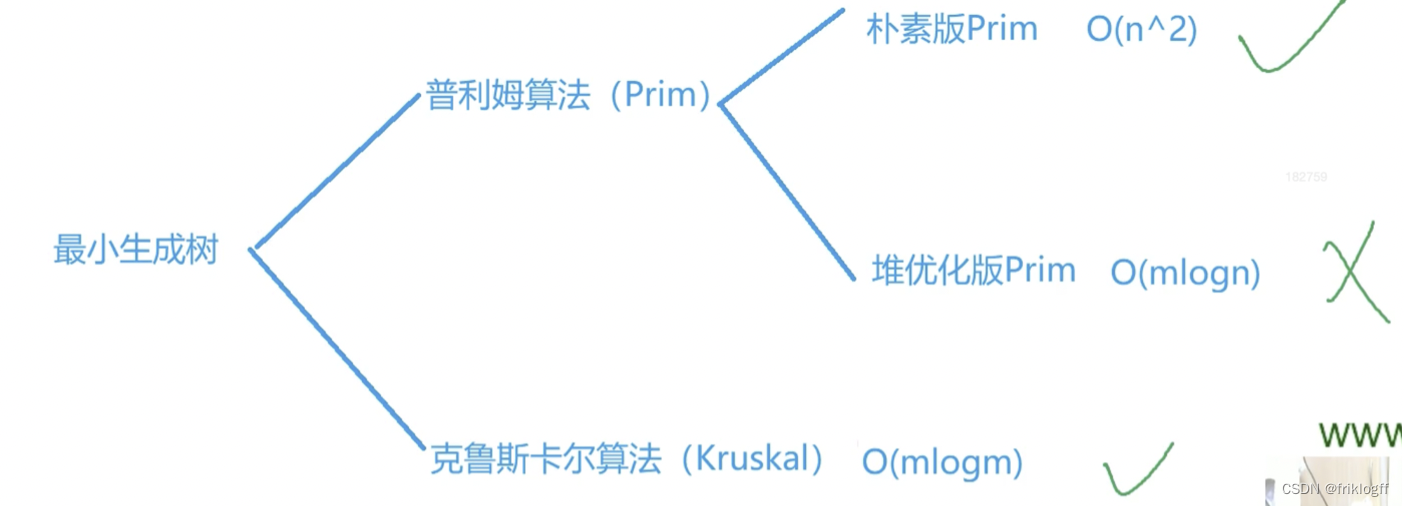

【数据结构】考研真题攻克与重点知识点剖析 - 第 6 篇:图

前言 本文基础知识部分来自于b站:分享笔记的好人儿的思维导图与王道考研课程,感谢大佬的开源精神,习题来自老师划的重点以及考研真题。此前我尝试了完全使用Python或是结合大语言模型对考研真题进行数据清洗与可视化分析,本人技术…...

java的基本数据类型

在Java编程语言中,基本数据类型是构成Java程序的基础元素,它们用于存储简单值。Java的基本数据类型可以分为两大类:原始类型(Primitive Types)和引用类型(Reference Types)。原始类型包括整型、…...

0104练习与思考题-算法基础-算法导论第三版

2.3-1 归并示意图 问题:使用图2-4作为模型,说明归并排序再数组 A ( 3 , 41 , 52 , 26 , 38 , 57 , 9 , 49 ) A(3,41,52,26,38,57,9,49) A(3,41,52,26,38,57,9,49)上的操作。图示: tips::有不少在线算法可视化工具(软…...

烤羊肉串引来的思考--命令模式

1.1 吃羊肉串! 烧烤摊旁边等着拿肉串的人七嘴八舌地叫开了。场面有些混乱,由于人实在太多,烤羊肉串的老板已经分不清谁是谁,造成分发错误,收钱错误,烤肉质量不过关等。 外面打游击烤羊肉串和这种开门店做烤…...

Python 描述符

文章目录 类型:数据描述符:方法描述符:描述符的要包括以下几点:方法描述符实现缓存 描述符(Descriptor)是 Python 中一个非常强大的特性,它允许我们自定义属性的访问行为。使用描述符,我们可以创建一些特殊的属性,在访问这些属性时执行自定义…...

Go语言创建HTTP服务器

Web服务器可提供网页、Web服务和文件,而Go语言为创建Web服务器提供了强大的支持。 1.通过Hello World Web 服务器宣告您的存在 标准库中的net/http包提供了多种创建HTTP服务器的方法,它还提供了一个基本的路由器。 package mainimport ("net/http" )func helloWo…...

【LeetCode热题100】【栈】柱状图中最大的矩形

题目链接:84. 柱状图中最大的矩形 - 力扣(LeetCode) 要找最大的矩形就是要找以每根柱子为高度往两边延申的边界,要作为柱子的边界就必须高度不能低于该柱子,否则矩形无法同高,也就是需要找出以每根柱子为高…...

谷歌浏览器插件开发速成指南:弹窗

诸神缄默不语-个人CSDN博文目录 本文介绍谷歌浏览器插件开发的入门教程,阅读完本文后应该就能开发一个简单的“hello world”插件,效果是出现写有“Hello Extensions”的弹窗。 作为系列文章的第一篇,本文还希望读者阅读后能够简要了解在此基…...

Lakehouse 大数据概念

“Lakehouse” 是一个相对新的概念,是大数据理论中的一个重要发展方向。它试图结合传统的数据湖(Data Lake)和数据仓库(Data Warehouse)的优点,以创造一种更为灵活和强大的数据管理体系。 在传统的大数据架构中,数据湖用于存储原始、未加工的数据,而数据仓库则用于存储…...

教你一招轻松定生物医学论文插图

写生物医学论文时,信号通路图、细胞调控机制图、病理机制图是展示研究逻辑的核心视觉语言,几乎是投稿刚需。但不少科研人都踩过绘图的坑:找不到专业的受体、离子通道、磷酸化符号等矢量图标,只能用基础形状拼凑,结果图…...

)

TVA智能体范式的工业视觉革命(3)

重磅预告:本专栏将独家连载系列丛书《智能体视觉技术与应用》部分精华内容,该书是世界首套系统阐述“因式智能体”视觉理论与实践的专著,特邀美国 TypeOne 公司首席科学家、斯坦福大学博士 Bohan 担任技术顾问。Bohan先生师从美国三院院士、“…...

避坑指南:LVGL Bar控件在RTOS和低内存MCU上的5个常见问题与解决方案

避坑指南:LVGL Bar控件在RTOS和低内存MCU上的5个常见问题与解决方案 在嵌入式开发中,LVGL作为轻量级图形库被广泛应用,但其Bar控件(进度条)在资源受限环境(如FreeRTOS、内存<64KB的MCU)下常出…...

Frenet Corridor Planner:自动驾驶路径规划的核心技术解析

1. Frenet Corridor Planner:自动驾驶路径规划的核心突破在自动驾驶技术栈中,路径规划模块承担着将决策指令转化为可执行轨迹的关键角色。面对城市道路中突然出现的占道车辆或行人,传统基于固定路径的规划方法往往显得力不从心。Frenet Corri…...

【Nginx】Nginx 自定义错误页面全解:从 404 到 502 的用户体验与故障隔离实战

Nginx 自定义错误页面全解:从 404 到 502 的用户体验与故障隔离实战 本文面向已部署过简单 Nginx 服务、了解反向代理概念,但尚未系统掌握其错误处理机制与用户友好降级策略的中高级工程师。我们将彻底拆解 error_page 指令的工作原理、作用域继承、内部重定向行为,揭示为何…...

Tracy安全最佳实践:开发与生产环境的安全配置指南

Tracy安全最佳实践:开发与生产环境的安全配置指南 【免费下载链接】tracy 😎 Tracy: the addictive tool to ease debugging PHP code for cool developers. Friendly design, logging, profiler, advanced features like debugging AJAX calls or CLI s…...

长期项目使用 Taotoken 聚合 API 在模型选型与切换上的便利性体验

🚀 告别海外账号与网络限制!稳定直连全球优质大模型,限时半价接入中。 👉 点击领取海量免费额度 长期项目使用 Taotoken 聚合 API 在模型选型与切换上的便利性体验 在一个持续数月的研发项目中,我们构建了一个需要集成…...

C语言状态模式实战:从设计思想到嵌入式状态机实现

1. 项目概述:从“状态”到“模式”的思维跃迁在嵌入式开发、游戏逻辑、网络协议解析乃至日常的业务流程控制中,我们常常会面对一个核心挑战:如何优雅地管理一个对象随着内部条件改变而表现出的不同行为?比如,一个自动售…...

Cairo高级特性解析:泛型、Trait系统和元编程的深度应用

Cairo高级特性解析:泛型、Trait系统和元编程的深度应用 【免费下载链接】cairo Cairo is the first Turing-complete language for creating provable programs for general computation. 项目地址: https://gitcode.com/gh_mirrors/ca/cairo Cairo作为首个支…...

人工智能领域SCI期刊征稿|中科院2区为主,录用率80%+,对国人极度友好,避坑必看,自引率安全、投稿零压力,审稿高效、录用率拉满,毕业 / 评职必看!

对于AI、计算机视觉、神经网络、计算智能领域的科研人(硕博、青年教师、工程师)而言,发表SCI核心需求是「分区稳、录用易、对国人友好、无预警风险」。本文整理4本人工智能领域优质SCI期刊,涵盖中科院2区(4本ÿ…...