UART 串口通信

第18.1讲 UART串口通信原理讲解_哔哩哔哩_bilibili

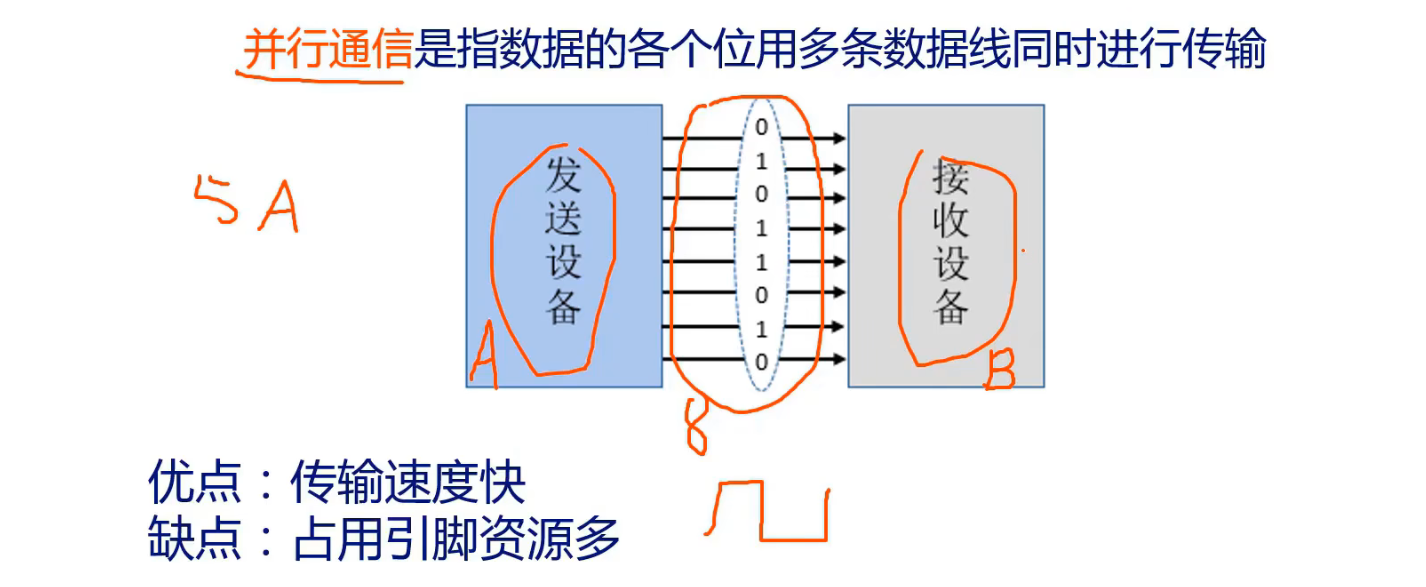

并行通信

一个周期同时发送8bit的数据,占用引脚资源多

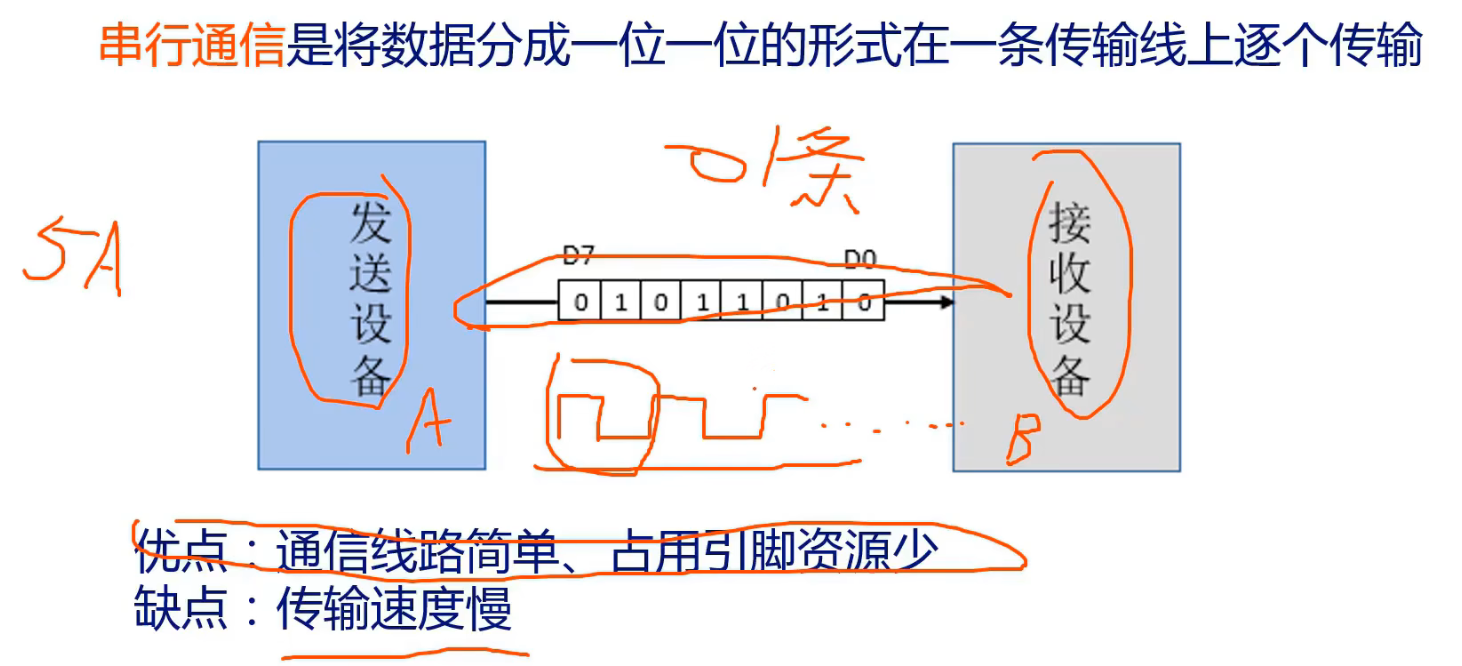

串行通信

串行通信的通信方式:

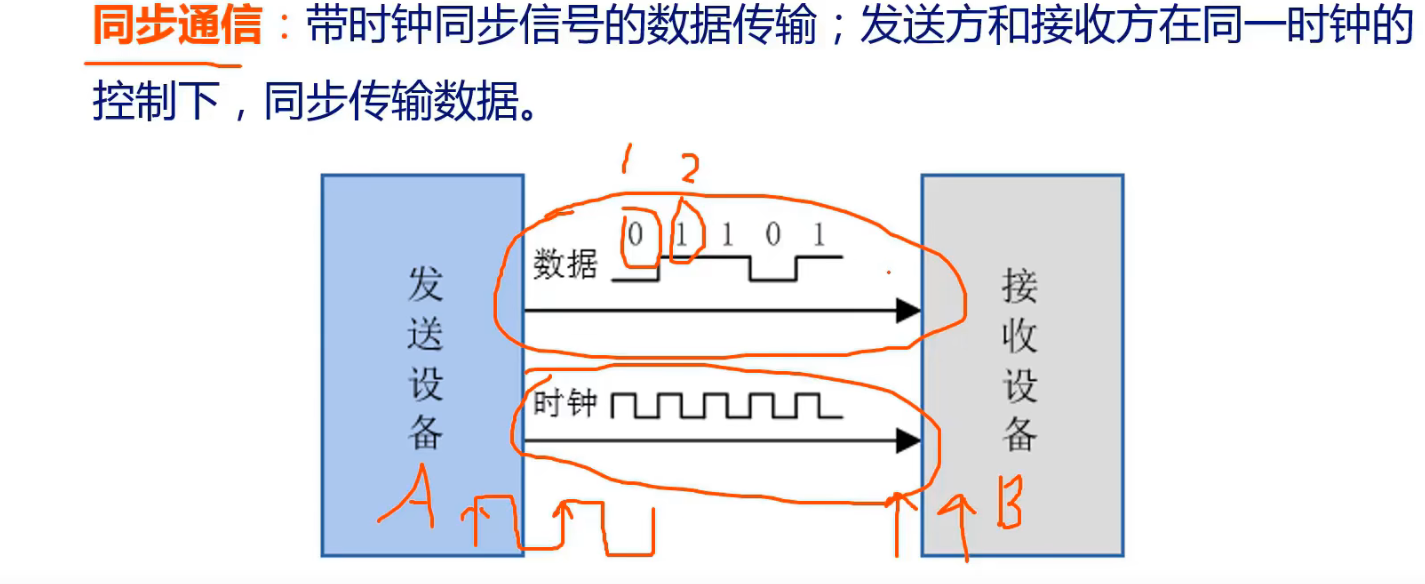

- 同步通信

同一时钟下进行数据传输

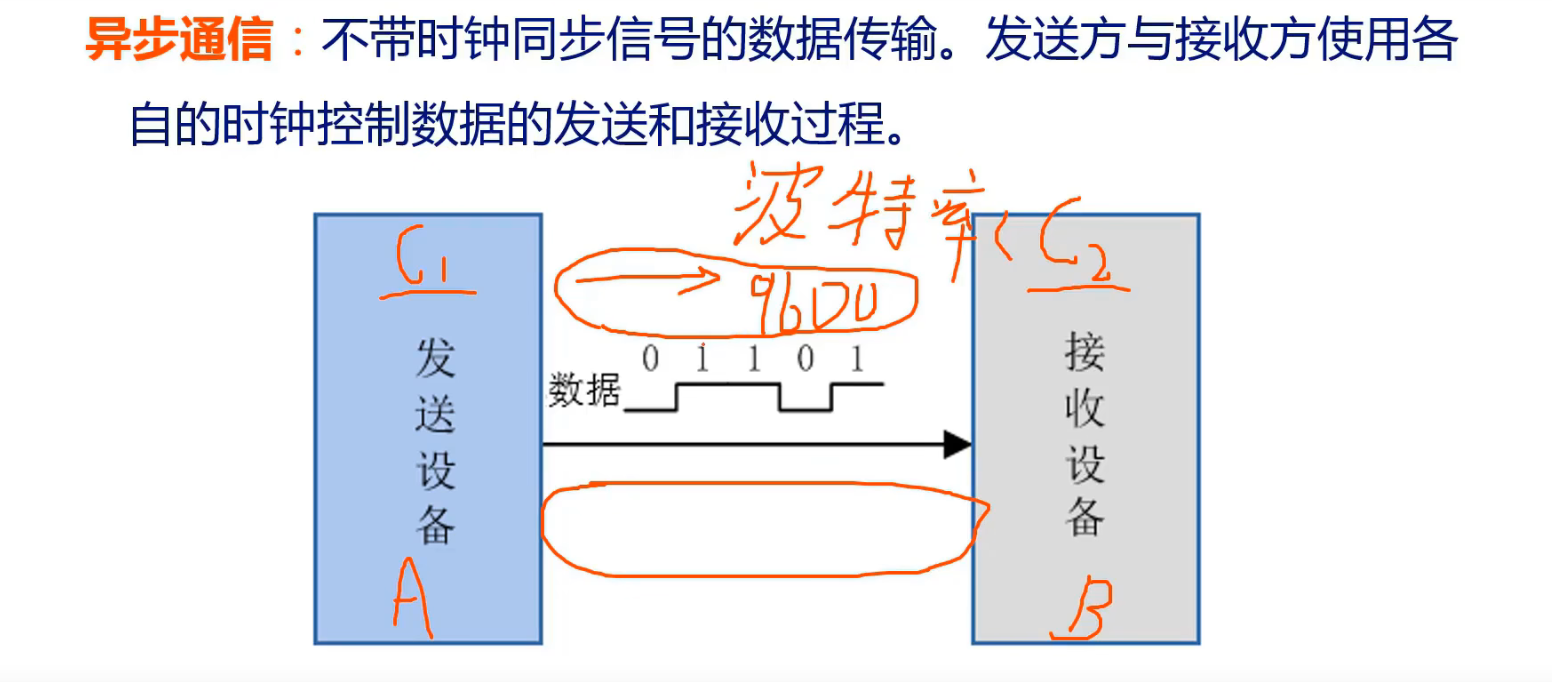

- 异步通信

发送设备和接收设备的时钟不同

但是需要约束波特率(1s内传输的bit数)

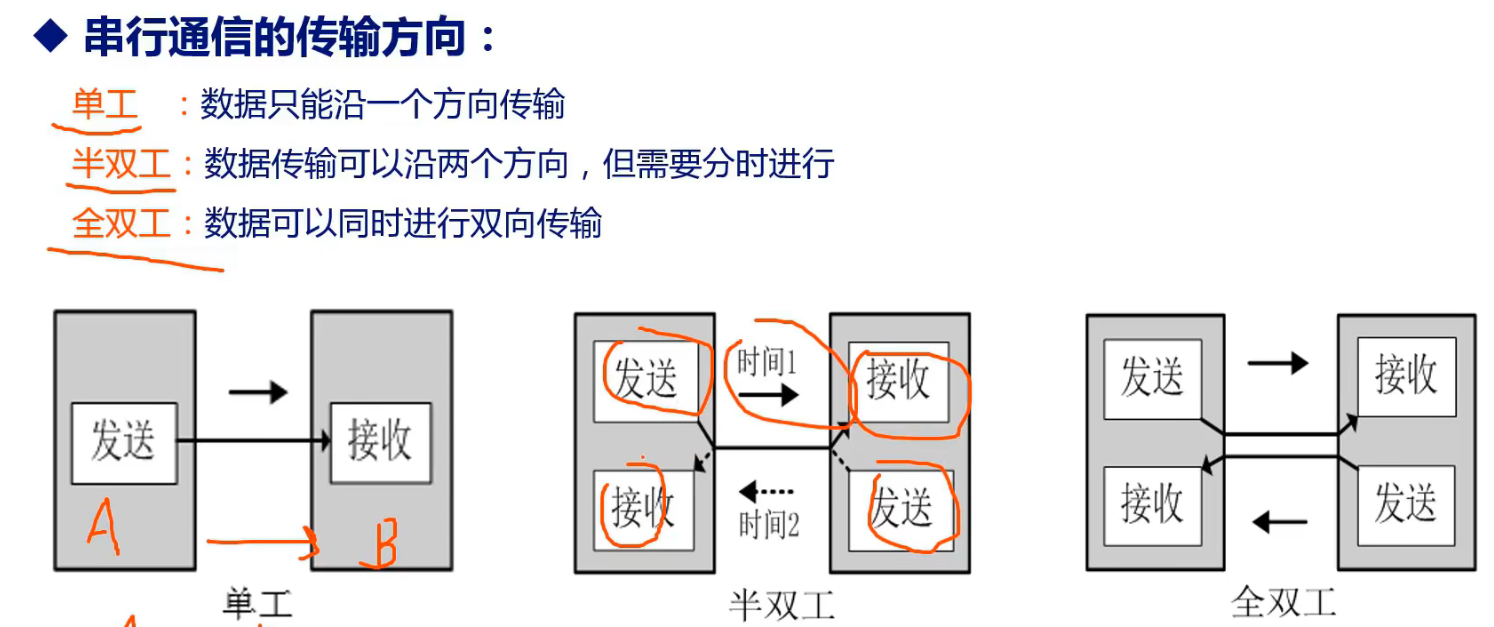

串行通信的传输方向:

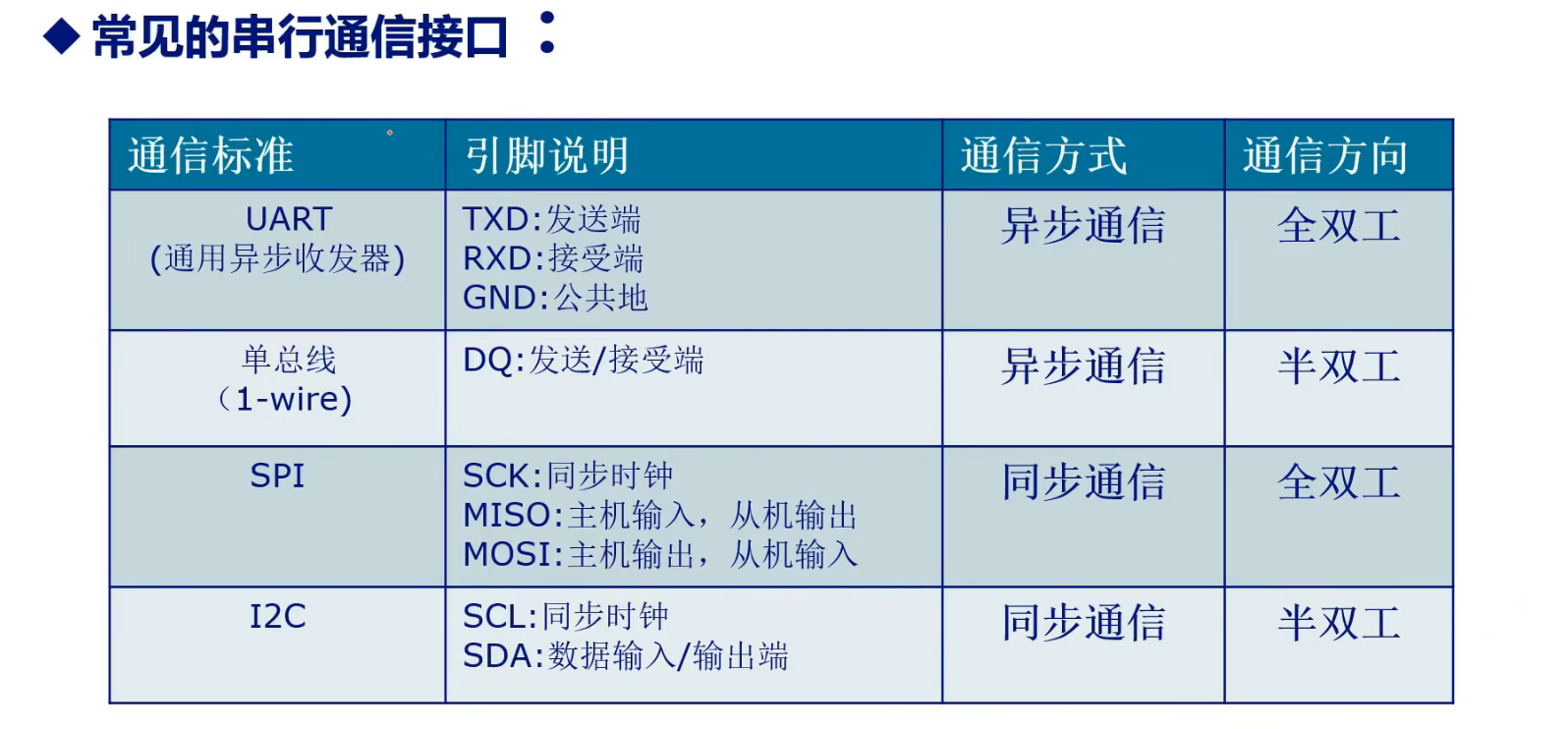

常见串行通信接口:

UART

UART(universal asynchronous receiver-transmitter):通用异步收发传输器

异步串行通信

功能:

- 发送数据时将并行数据转换为串行数据进行传输

- 接收数据时将串行数据转换为并行行数据进行传输

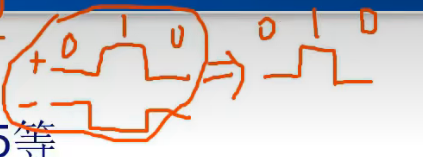

协议层

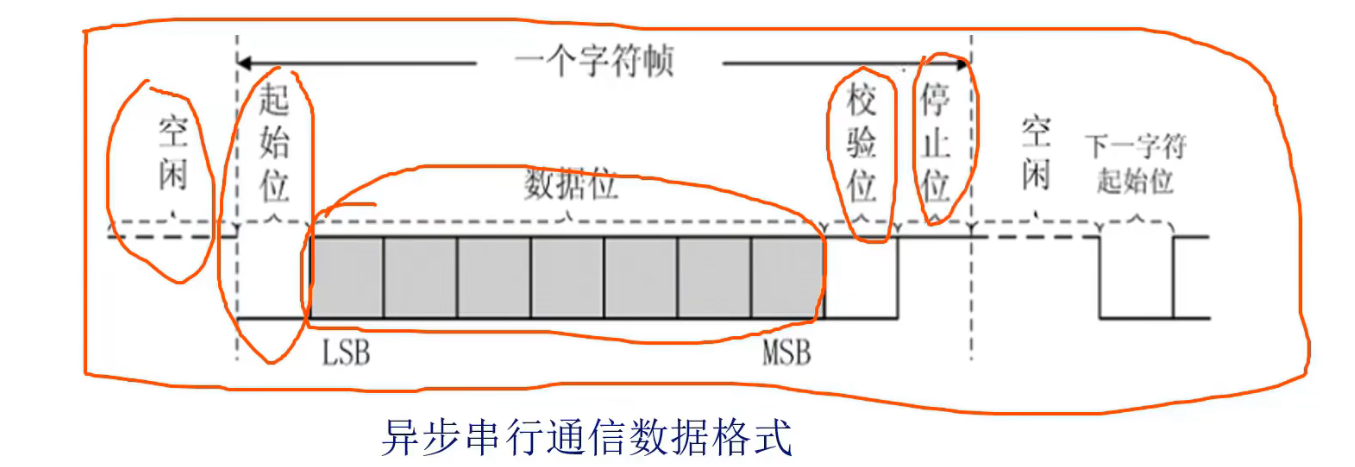

数据格式:

校验位:奇偶校验

UART使用两根信号线实现,一根用于串口发送,另一根负责串口接收

传输速率 波特率

串口通信的速率用波特率表示,它表示每秒传输的二进制数据的位数,单位为bps(位/秒)

9600 19200 38400…

1s=109ns1 s = 10^9 ns 1s=109ns

假设波特率是115200 bit/s

那么发送一个bit需要 10910^9109/ 115200 ns

当频率为50Hz的时候,一个周期为 20 ns

发送一个bit需要的周期数为: 109/115200/2010^9/115200/20109/115200/20= 434

拉低的起始位,拉高的数据为,校验位,停止位都需要434个周期

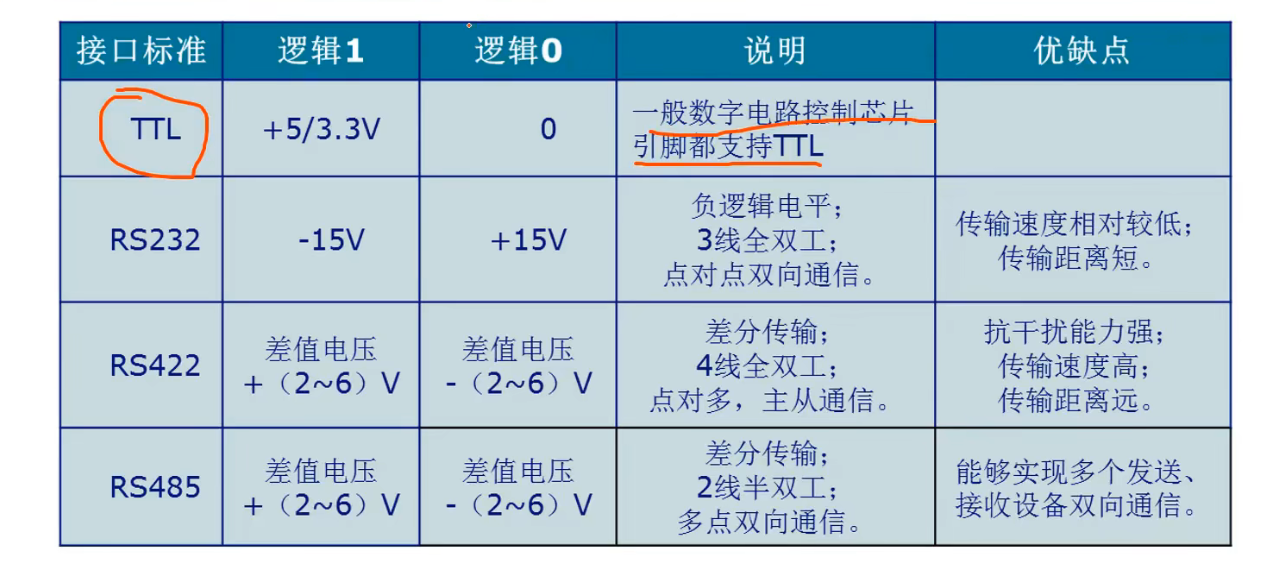

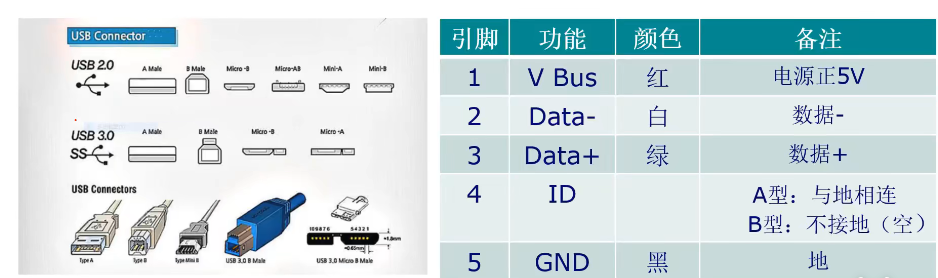

物理层:接口标准

负逻辑电平:

1对应负电压,0对应正电压

3线:TX RX GND

差分传输:

RS232

DB9接口定义

USB接口

Data -/+ 差分信号

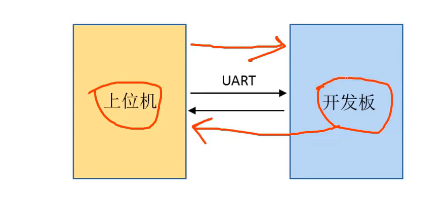

实验

实验任务

开发板与上位机通过串口通信,完成数据环回实验

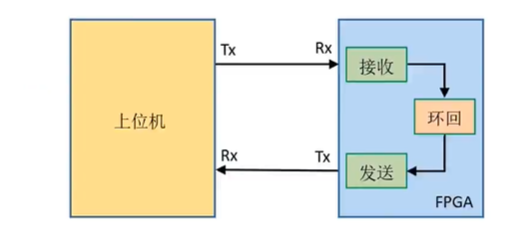

程序设计

串口接收、发送:

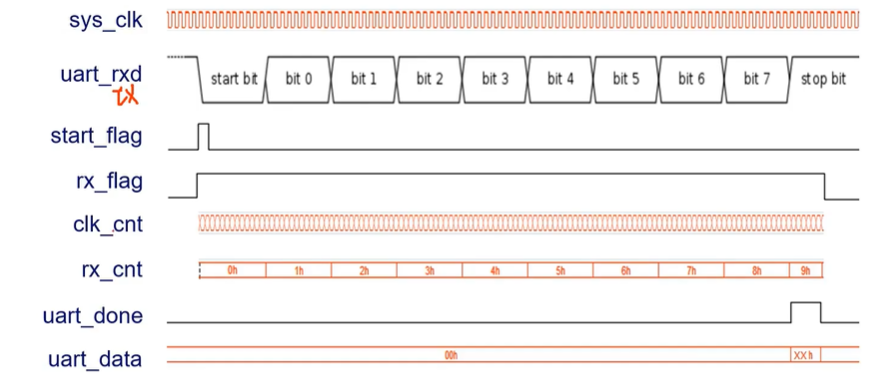

uart_recv

串行转并行

module uart_recv (input clk,input rst,input uart_rxd,output reg [7:0] uart_data,output reg uart_done

);// 抓取接收信号下降沿(获取数据接收的标志)

reg uart_rxd_cur, uart_rxd_pre;

wire start_flag;

assign start_flag = ~uart_rxd_cur & uart_rxd_pre;

always @(posedge clk or posedge rst) beginif(rst) beginuart_rxd_cur <= 1'b0;uart_rxd_pre <= 1'b0;endelse beginuart_rxd_cur <= uart_rxd;uart_rxd_pre <= uart_rxd_cur;end

end// 定义常量

parameter CLK_FREQ = 50000000;

parameter UART_BPS = 115200;

// 不可更改的常量

localparam BPS_CNT = CLK_FREQ / UART_BPS;reg rx_flag;

reg [3:0] rx_cnt;

reg [8:0] clk_cnt;always @(posedge clk or posedge rst) beginif(rst)rx_flag <= 1'b0;else beginif(start_flag)rx_flag <= 1'b1;else if(rx_cnt == 4'd9 && (clk_cnt == BPS_CNT/2))// 8个bit数据传输完成,且经过半个波特的停止位rx_flag <= 1'b0;elserx_flag <= rx_flag;end

end// clk_cnt 计数

always @(posedge clk or posedge rst) beginif(rst)clk_cnt <= 1'b0;else if(rx_flag) beginif(clk_cnt < BPS_CNT - 1)clk_cnt <= clk_cnt + 1'b1;elseclk_cnt <= 9'd0;endelseclk_cnt <= 9'b0;

end// rx_cnt 根据 clk_cnt 计数

always @(posedge clk or posedge rst) beginif(rst)rx_cnt <= 4'd0;else if(rx_flag) beginif(clk_cnt == BPS_CNT - 1)rx_cnt <= rx_cnt + 1'b1;elserx_cnt <= rx_cnt;endelserx_cnt <= 4'b0;end// 在中间值的时候赋值

reg [7:0] rx_data; // 临时寄存器(寄存数据)

always @(posedge clk or posedge rst) beginif(rst)rx_data <= 8'd0;else if(rx_flag) beginif(clk_cnt == BPS_CNT / 2) beginrx_data[rx_cnt - 4'b1] <= uart_rxd_pre;endelserx_data <= rx_data;endelserx_data <= 8'd0;

end// 设置输出数据uart_data和输出完成信号uart_done

always @(posedge clk or posedge rst) beginif(rst) beginuart_data <= 8'd0;uart_done <= 1'b0;endelse if(rx_cnt == 4'd9) beginuart_data <= rx_data;uart_done <= 1'b1;endelse beginuart_data <= 8'd0;uart_done <= 1'b0;end

endendmodule

uart_send

并行转串行

module uart_send (input clk,input rst,input uart_en,input [7:0] uart_din,output reg uart_txd,output uart_rx_busy

);// 抓取uart_en上升沿

reg uart_en_pre, uart_en_cur;

wire en_flag;

assign en_flag = ~uart_en_pre & uart_en_cur;always @(posedge clk or posedge rst) beginif(rst) beginuart_en_pre <= 1'b0;uart_en_cur <= 1'b0;endelse beginuart_en_cur <= uart_en;uart_en_pre <= uart_en_cur; end

endreg [7:0] tx_data;

reg tx_flag;

reg [3:0] tx_cnt;

reg [8:0] clk_cnt;

// 定义常量

parameter CLK_FREQ = 50000000;

parameter UART_BPS = 115200;

// 不可更改的常量

localparam BPS_CNT = CLK_FREQ / UART_BPS;

// 写信号忙

assign uart_rx_busy = tx_flag;// clk_cnt 计数

always @(posedge clk or posedge rst) beginif(rst)clk_cnt <= 1'b0;else if(tx_flag) beginif(clk_cnt < BPS_CNT - 1)clk_cnt <= clk_cnt + 1'b1;elseclk_cnt <= 9'd0;endelseclk_cnt <= 9'b0;

end// tx_cnt 根据 clk_cnt 计数

always @(posedge clk or posedge rst) beginif(rst)tx_cnt <= 4'd0;else if(tx_flag) beginif(clk_cnt == BPS_CNT - 1)tx_cnt <= tx_cnt + 1'b1;elsetx_cnt <= tx_cnt;endelsetx_cnt <= 4'b0;endalways @(posedge clk or posedge rst) beginif(rst) begintx_flag <= 1'b0;tx_data <= 8'd0;endelse beginif(en_flag) begin // 写使能tx_flag <= 1'b1; // 写标志tx_data <= uart_din; // 暂存数据endelse if(tx_cnt == 4'd9 && clk_cnt == (BPS_CNT-BPS_CNT/16)) begin// 传输结束tx_flag <= 1'b0;tx_data <= 8'd0;endelse begintx_flag <= tx_flag;tx_data <= tx_data;endend

end// uart_txd 传输数据

always @(posedge clk or posedge rst) beginif(rst)uart_txd <= 1'b1;else if(tx_flag) beginif(tx_cnt == 4'd0) uart_txd <= 1'b0; // start bit拉低else if(tx_cnt == 4'd9) uart_txd <= 1'b1; // stop bit拉低else uart_txd <= tx_data[tx_cnt - 4'b1]; // 传输数据(cnt比bit位计数多1)endelse uart_txd <= 1'b1;

endendmodule

uart_loopback_top

三个模块对应信号连接

module uart_loopback_top(input sys_clk,input sys_rst,input uart_rxd,output uart_txd

);wire uart_en;

wire [7:0] uart_din;

wire [7:0] uart_data;

wire uart_done;

wire uart_rx_busy;uart_recv uart_recv_u(.clk (sys_clk),.rst (sys_rst),.uart_rxd (uart_rxd),.uart_data (uart_data),.uart_done (uart_done) );uart_send uart_send_u(.clk (sys_clk),.rst (sys_rst),.uart_en (uart_en),.uart_din (uart_din),.uart_txd (uart_txd),.uart_rx_busy (uart_rx_busy)

);uart_loop uart_loop_u(.clk (sys_clk),.rst (sys_rst),.recv_done (uart_done),.recv_data (uart_data),.tx_busy (uart_rx_busy),.send_en (uart_en),.send_data (uart_din)

);endmodule

约束

create_clock -period 20.000 -name clk [get_ports {sys_clk}]#Clock signal

set_property -dict { PACKAGE_PIN L16 IOSTANDARD LVCMOS33 } [get_ports { sys_clk }];#Buttons

set_property -dict { PACKAGE_PIN R18 IOSTANDARD LVCMOS33 } [get_ports { rst }];set_property -dict { PACKAGE_PIN B12 IOSTANDARD LVCMOS18 } [get_ports { uart_rxd }];

set_property -dict { PACKAGE_PIN C12 IOSTANDARD LVCMOS18 } [get_ports { uart_txd }];

这里的约束找不到对应的 zybo 开发板的,并没有跑起来

相关文章:

UART 串口通信

第18.1讲 UART串口通信原理讲解_哔哩哔哩_bilibili 并行通信 一个周期同时发送8bit的数据,占用引脚资源多 串行通信 串行通信的通信方式: 同步通信 同一时钟下进行数据传输 异步通信 发送设备和接收设备的时钟不同 但是需要约束波特率(…...

【硬件】P沟道和N沟道MOS管开关电路设计

场效应管做的开关电路一般分为两种,一种是N沟道,另一种是P沟道,如果电路设计中要应用到高端驱动的话,可以采用PMOS来导通。P沟道MOS管开关电路PMOS的特性,Vgs小于一定的值就会导通,当Vgs<0,即Vs>Vg,管…...

中移杭研一面经历

文章目录 1、常用的Java元注解@Documented@Target@Retention@Override@Deprecated@Inherited@Repeatable@Native2、Java注解的原理3、spring boot starter开发过程1、原理浅谈2、大概步骤3、项目介绍1、常用的Java元注解 @Documented @Documented 是一个标记注解,没有成员变…...

如何成为一名全栈工程师:专业建议与技能要求

作为一名全栈工程师,你需要拥有跨越前端、后端、数据库等多个领域的技能,并能够将它们整合起来构建出完整的应用程序。因此,成为一名全栈工程师需要你掌握多种技术,具备较强的编程能力和系统设计能力。下面,我将从以下…...

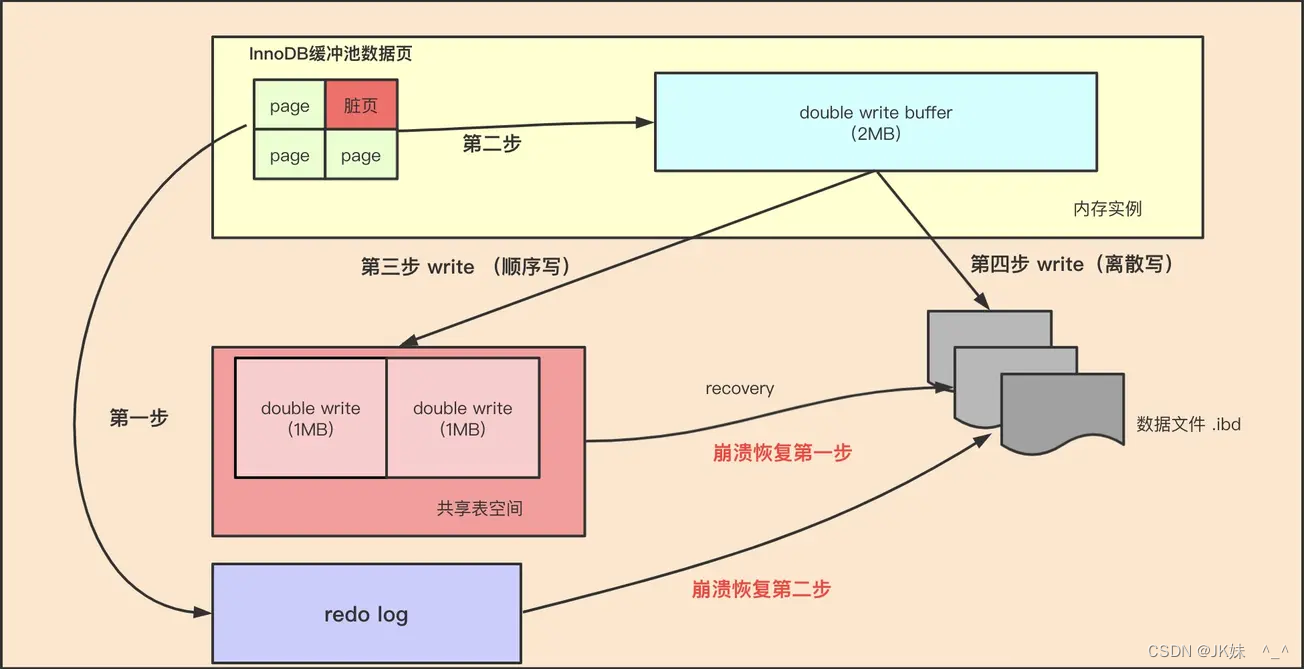

MySQL架构篇

一、进阶学习环境说明 1.1 MySQL服务器环境 Linux虚拟机:CentOS 7 MySQL:MySQL5.7.30 在Linux服务器中安装MySQL: ps.如果有自己的云服务器,可忽略前两步,直接进行第三步 1.2 服务器日志文件说明 MySQL是通过文件系统对…...

Redhat7.6安装weblogic10.3.6(超详细,有图文)

一、环境 linux版本:Redhat 7.6 weblogic版本:WLS10.3.6 jdk版本:jdk1.8.0 下载网址:https://www.oracle.com/technetwork/middleware/weblogic/downloads/index.html 1.安装vsftpd服务,将部署环境使用JDK文件和wls服务文件…...

dashboard疏散主机提示报错:无法疏散主机...处理方法、openstack虚拟机状态卡在重启处理方法、openstack在数据库修改虚拟机状态的方法

文章目录dashboard疏散主机提示报错:无法疏散主机...处理方法报错说明【状态卡在reboot状态】解决方法【登录nova数据库修改虚拟机信息】首先获取nova数据库的密码登录nova数据库并做修改验证信息是否修改成功再次迁移并验证报错说明【虚拟机状态error也会导致疏散失…...

)

力扣:轮转数组(详解)

前言:内容包括:题目,代码实现,大致思路,代码解读 题目: 给定一个整数数组 nums,将数组中的元素向右轮转 k 个位置,其中 k 是非负数。 示例 1: 输入: nums [1,2,3,4,5,6,7], k 3…...

Vue计算属性Computed

30. Vue计算属性Computed 1. 定义 Computed属性是Vue中的一个计算属性,是一种基于其它属性值计算而来的属性值,具有缓存机制,在依赖的属性值发生变化时会重新计算。 使用computed属性可以避免在模板中书写过多的计算逻辑,提高代…...

实验四:搜索

实验四:搜索 1.填格子 题目描述 有一个由数字 0、1 组成的方阵中,存在一任意形状的封闭区域,封闭区域由数字1 包围构成,每个节点只能走上下左右 4 个方向。现要求把封闭区域内的所有空间都填写成2 输入要求 每组测试数据第一…...

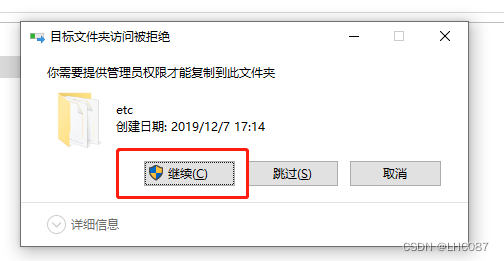

本地开发vue项目联调遇到访问接口跨域问题

本地开发vue项目联调遇到访问接口跨域问题 修改本地的localhost 一:按winr打开运行窗口,输入drivers ,然后回车 二:打开etc文件夹,然后用记事本的方式打开里面的hosts文件, 三:这时我们就可…...

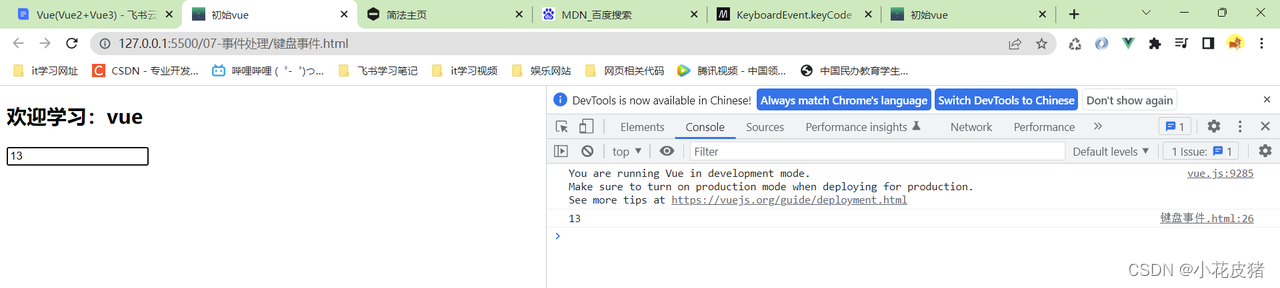

Vue键盘事件的使用

前言 在vue中,我们经常会用到键盘事件,不管是我们按下某个键,其实都是一次键盘事件的调用,下面就介绍下Vue中的键盘事件 先写一段代码,这里我选择的键盘事件是keyup,当然用keydown也是没问题的 问题来了,…...

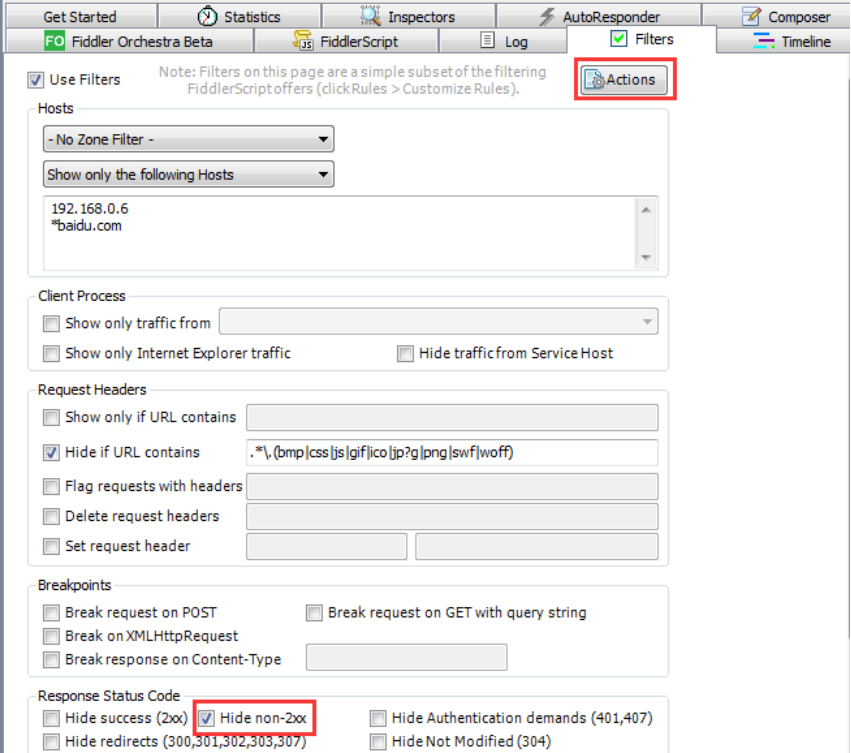

抓包工具fiddler详细使用教程

各位做测试的同学想必对抓包工具fiddler并不陌生,但是很多同学可能没有总结过它的用法,下面我总结了fiddler一些常用的用法。 Web端抓包配置 打开Fiddler,Tools -> Fiddler Options -> HTTPS 配置完后记得要重启Fiddler 选中Decrpt …...

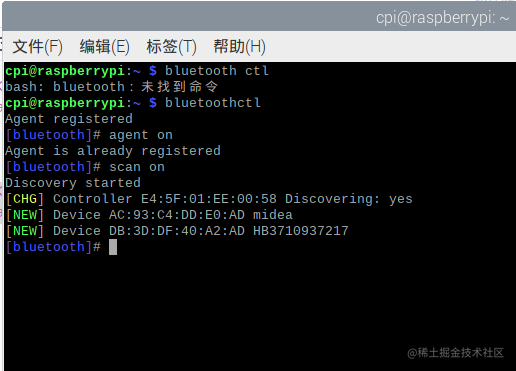

raspberry Pi 连接蓝牙(小爱同学)

参数valueraspberry pi MOdel4B,4Gbbluetooth MOdel小爱同学writeTime2023年 2月11日 下午13:14分raspberry System ModelLinux raspberrypi 5.15.61-v8 #1579 SMP PREEMPT Fri Aug 26 11:16:44 BST 2022 aarch64 GNU/Linux 连接蓝牙 请在小爱同学app上…...

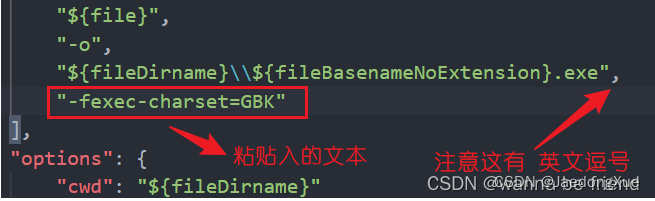

解决launch:program .exe does not exist

二. 程序的运行和调试 1.launch.json 复制下列代码至launch.json,并根据指导做出相对/绝对路径修改 用 IntelliSense 了解相关属性。 {// 使用 IntelliSense 了解相关属性。 // 悬停以查看现有属性的描述。// 欲了解更多信息,请访问: https://go.micros…...

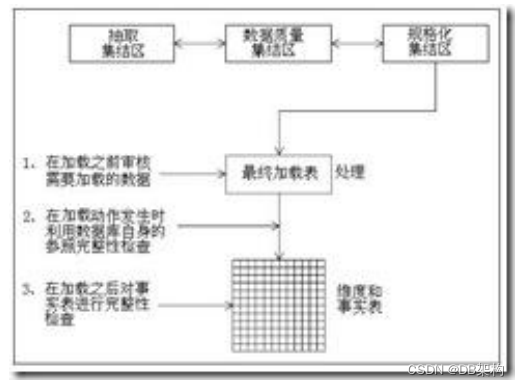

ETL --事实表

每一个事实表通过表的粒度来定义。事实表的粒度是事件度量的定义。我们必须至始至终按照度量如何在 现实世界中理解来规定事实表的粒度。 所有的事实表包含了一组关联到维表的外键,而这些维表提供了事实表度量的上下文。大多数的事实表还 包括了一个或者多个数值型…...

手工数据采集耗时耗力?Smartbi数据填报实现数据收集分析自动化

企业在日常经营管理过程中,往往需要收集很多内外部的信息,清洗整理后再进行存储、分析、呈现、决策支持等各种作业,如何高效收集结构化数据是企业管理者经常要面对的问题。传统手工的数据采集方式不仅耗费了大量人力时间成本,还容…...

应用实战|微信小程序开发示例--多人聊天互动空间

“超能力”数据库~拿来即用,应用开发人员再也不用为撰写API而发愁。MemFire Cloud 为开发者提供了简单易用的云数据库(表编辑器、自动生成API、SQL编辑器、备份恢复、托管运维),很大地降低开发者的使用门槛。 本示例是…...

css:使用filter和backdrop-filter实现高斯模糊效果

背景 今天接到一个需求是,使用高斯模糊的效果对一个页面进行模糊处理,正好借这个机会来整理一下 css3 中高斯模糊的两个 API API介绍 filter 说明: 该 API 是一个过滤器,不仅能实现高斯模糊,还有很多比如颜色偏移、…...

科技大势怎么看 2023怎么干?

2023年,科技的走向依旧是世界各国的关注重点,各国在纷纷设立自己的科技战略目标外,还在潜心研究不同技术领域的科技趋势,试图通过科技占据国际竞争的制高点。 随着我国深入实施创新驱动发展战略,推动产业结构优化升级&…...

【Perplexity教育搜索实战指南】:3大隐藏功能+5个教师必用技巧,90%用户至今未发现

更多请点击: https://codechina.net 第一章:Perplexity教育信息搜索的核心价值与定位 Perplexity 作为新一代AI驱动的信息检索工具,其在教育场景中的核心价值在于将“被动查找”转化为“主动理解”。它不依赖传统关键词匹配,而是…...

HiC-Pro跑完数据后,你的结果文件都看懂了吗?从out文件夹到可视化图谱的完整解读指南

HiC-Pro结果文件全解析:从原始数据到发表级图谱的实战指南 当HiC-Pro顺利完成运行后,面对out文件夹中密密麻麻的文件,很多研究者会陷入"数据沼泽"——明明流程跑通了,却不知道如何从这些中间文件中提取有价值的信息。本…...

从VS2019调试到IIS部署:一个.NET Core Web API的‘完整旅程’与避坑实录

从VS2019调试到IIS部署:一个.NET Core Web API的‘完整旅程’与避坑实录 当第一次尝试将.NET Core Web API从开发环境部署到生产服务器时,许多开发者都会遇到各种预料之外的挑战。本文将以第一人称视角,详细记录我从零开始创建项目、本地调试…...

Vue3后台管理系统终极指南:V3 Admin Vite 5.0快速上手教程

Vue3后台管理系统终极指南:V3 Admin Vite 5.0快速上手教程 【免费下载链接】v3-admin-vite ☀️ A crafted Vue3 admin template | Vue Admin | Vue Template | Vue3 Admin | Vue3 Template | Vue 后台 | Vue 模板 | Vue3 后台 | Vue3 模板 项目地址: https://git…...

NoFences:重新定义Windows桌面管理的开源革命

NoFences:重新定义Windows桌面管理的开源革命 【免费下载链接】NoFences 🚧 Open Source Stardock Fences alternative 项目地址: https://gitcode.com/gh_mirrors/no/NoFences 你是否也曾为杂乱无章的Windows桌面而烦恼?图标散落各处…...

如何在Inkscape中快速实现专业级光线追踪?终极免费光学设计指南

如何在Inkscape中快速实现专业级光线追踪?终极免费光学设计指南 【免费下载链接】inkscape-raytracing An extension for Inkscape that makes it easier to draw optical diagrams. 项目地址: https://gitcode.com/gh_mirrors/in/inkscape-raytracing Inks…...

基于ENVI、eCognition与ArcGIS的南京江北新区土地利用变化监测与驱动分析

1. 南京江北新区土地利用变化监测的技术路线 我第一次接触南京江北新区土地利用监测项目时,被这个区域的快速发展震撼到了。作为国家级新区,这里从2015年设立至今,土地利用格局发生了翻天覆地的变化。要准确捕捉这些变化,我们采用…...

3分钟掌握ncmdump:网易云音乐NCM文件终极解密方案

3分钟掌握ncmdump:网易云音乐NCM文件终极解密方案 【免费下载链接】ncmdump 项目地址: https://gitcode.com/gh_mirrors/ncmd/ncmdump 还在为网易云音乐下载的NCM格式音乐无法在其他播放器使用而烦恼吗?ncmdump这款免费开源工具正是你的完美解决…...

Taskbar11完全指南:解锁Windows 11任务栏自定义的终极解决方案

Taskbar11完全指南:解锁Windows 11任务栏自定义的终极解决方案 【免费下载链接】Taskbar11 Change the position and size of the Taskbar in Windows 11 项目地址: https://gitcode.com/gh_mirrors/ta/Taskbar11 还在为Windows 11任务栏的严格限制感到困扰吗…...

InfluxDB-从时序数据模型到实战:核心原理与Web UI高效入门

1. 时序数据库与InfluxDB初探 第一次接触时序数据库时,我盯着监控大屏上跳动的曲线发愣——这些每秒产生数万条记录的传感器数据,传统数据库根本扛不住。直到同事推荐了InfluxDB,这个专门为时间序列数据设计的数据库,才真正解决了…...