基于AGX ORIN与FPGA K7实现PCIE高速数据通信/Orin与FPGA高速数据传输/XDMA在linux系统使用教程

因最近想学习AGX orin和FPGA实现数据高速通信,借此机会和大家一起学习AGX orin和FPGA

制作不易,记得三连哦,给我动力,持续更新!!!

完整工程文件下载:AGX orin与FPGA实现PCIE完整工程 提取码:985w

在现代高速数据传输领域,PCIe(Peripheral Component Interconnect Express)已经成为了一种广泛应用的技术标准。它不仅提供了高带宽和低延迟的数据传输能力,还在多种应用场景中表现出色。本文将深入探讨如何利用NVIDIA的AGX ORIN平台与Xilinx的FPGA K7,通过PCIe接口实现高速数据通信。

AGX ORIN与FPGA A7的概述

AGX ORIN是NVIDIA最新一代的AI计算平台,具有强大的计算能力和广泛的应用前景,特别是在自动驾驶、机器人和高性能计算等领域。而Xilinx FPGA A7则是FPGA领域的一个重要产品,因其灵活的硬件配置和高效的数据处理能力,广泛应用于信号处理和嵌入式系统中。

本文将详细介绍如何使用他们,并提供具体的技术实现方案,包括:

- 硬件设计与配置:如何配置AGX ORIN和FPGA A7的硬件接口,使其能够通过PCIe进行高速数据通信。

- 驱动程序开发:开发并优化PCIe驱动程序,以支持高效的数据传输。

- 数据传输协议:设计高效的数据传输协议,确保数据传输的高效性和可靠。

一、硬件介绍

FPGA:

本次设计采用的是xilinx家的K7 325T(全称xc7k325tffg900-2L),采用我们自己设计的开发板进行开发,如果芯片一样的读者,也可以直接使用你自己的开发板来设计。下面是325T官方的PCIE资源介绍:

XC7K325TFFG900 的 PCIe 资源

-

内置 PCIe 硬核 (PCIe Hard IP)

- PCIe Gen2 支持: XC7K325TFFG900 支持 PCIe Gen2 标准,提供高达 5 GT/s 的数据传输速率。

- 支持的通道数: 支持 x1、x2、x4 和 x8 通道配置,根据应用需求灵活选择不同的带宽。

-

灵活的配置选项

- 可编程端点和根端口: 支持将 FPGA 配置为 PCIe 端点 (Endpoint) 或根端口 (Root Port),适用于不同的应用场景。

- 多功能支持: 允许实现多功能设备,使单个 PCIe 端点能够支持多个独立功能。

-

高性能 SerDes

- 高达 16 个高速串行解串行器 (SerDes) 通道: 每个通道支持高达 6.6 Gb/s 的数据传输速率,确保了 PCIe 通道的高性能传输能力。

- 集成时钟和数据恢复 (CDR) 电路: 提供稳定的高速数据传输,减少信号抖动和误码率

AGX ORIN:

本次设计的Orin为 JETSON AGX Orin 64G,同理32G的版本也是一样的,下面是总结的AGX Orin的PCIE资源介绍:

AGX Orin 的 PCIe 资源

-

PCIe 版本和速率

- PCIe Gen4 支持: AGX Orin 支持 PCIe 4.0 标准,提供高达 16 GT/s 的数据传输速率,比 PCIe 3.0 的带宽翻倍,适合高带宽需求的应用。

-

PCIe 通道数

- 多达 16 条 PCIe 通道: 允许配置为多种通道组合(如 x16、x8、x4、x2 和 x1),以满足不同设备和应用的带宽需求。

-

灵活的接口配置

- 多功能支持: 支持多种 PCIe 配置和设备树设计,灵活配置端点和根端口角色,适用于多种系统架构和应用需求。

- 多主机支持: 能够配置多个独立的 PCIe 控制器,使其可以同时连接多个 PCIe 设备,提升系统扩展性。

-

高性能和低延迟

- 高吞吐量和低延迟: PCIe 4.0 提供了高吞吐量和低延迟的特点,能够满足实时应用和数据密集型计算的需求。

- 内存访问: 支持直接内存访问 (DMA) 和远程直接内存访问 (RDMA),提高数据传输效率和系统性能。

二、FPGA设计

设计工具

设计开发vivado版本:vivado2019.2

设计语言:verilog、block design

设计需求:

完成 FPGA 与 AGX Orin 的数据交互,并通过 PCIe 接口实现高速数据传输,同时测量和评估通信速度及其性能表现。

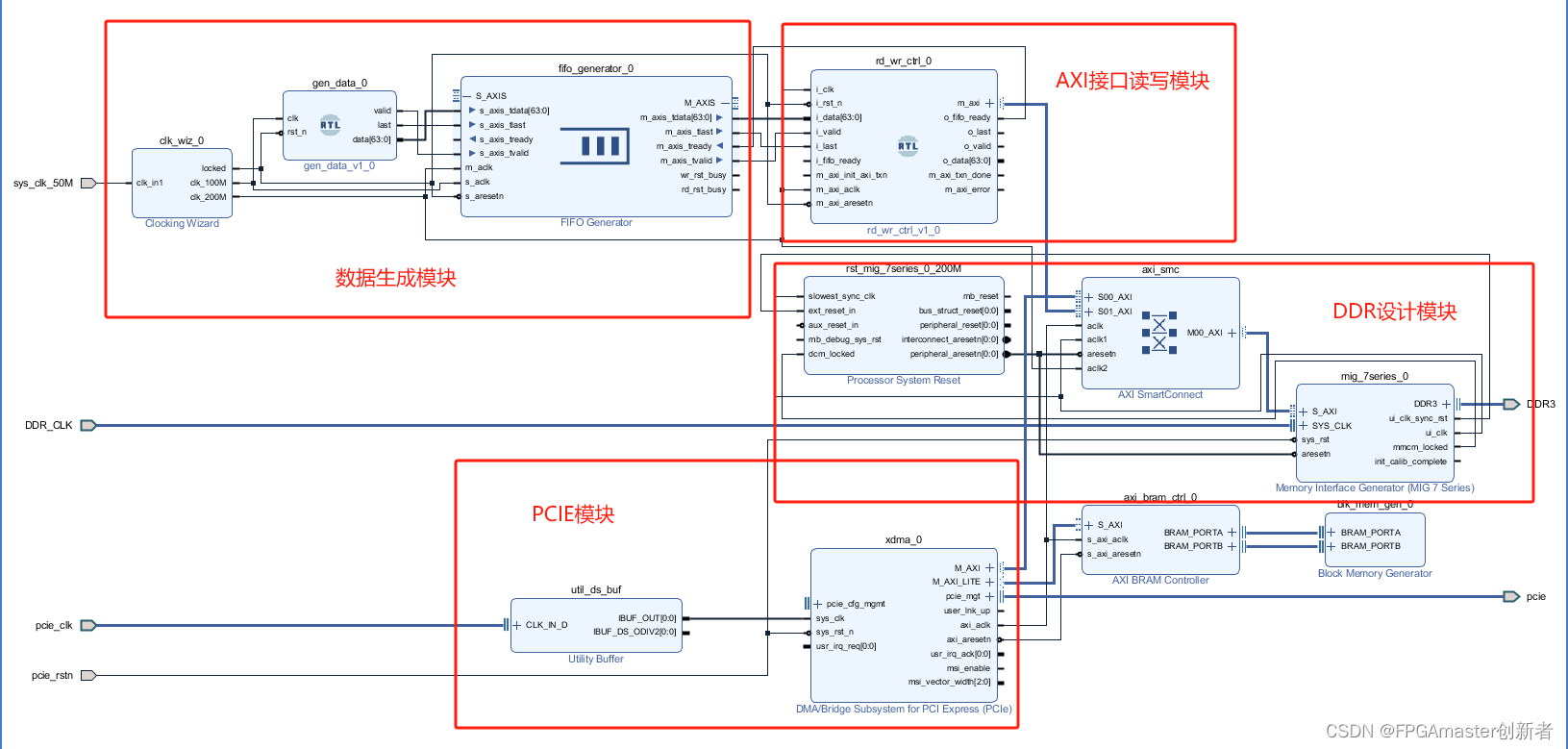

本设计主要是采用vivado中的block design设计,然后其中还添加了自己设计的一些代码:AXI接口读写模块和模拟数据产生模块。整体设计如下所示:

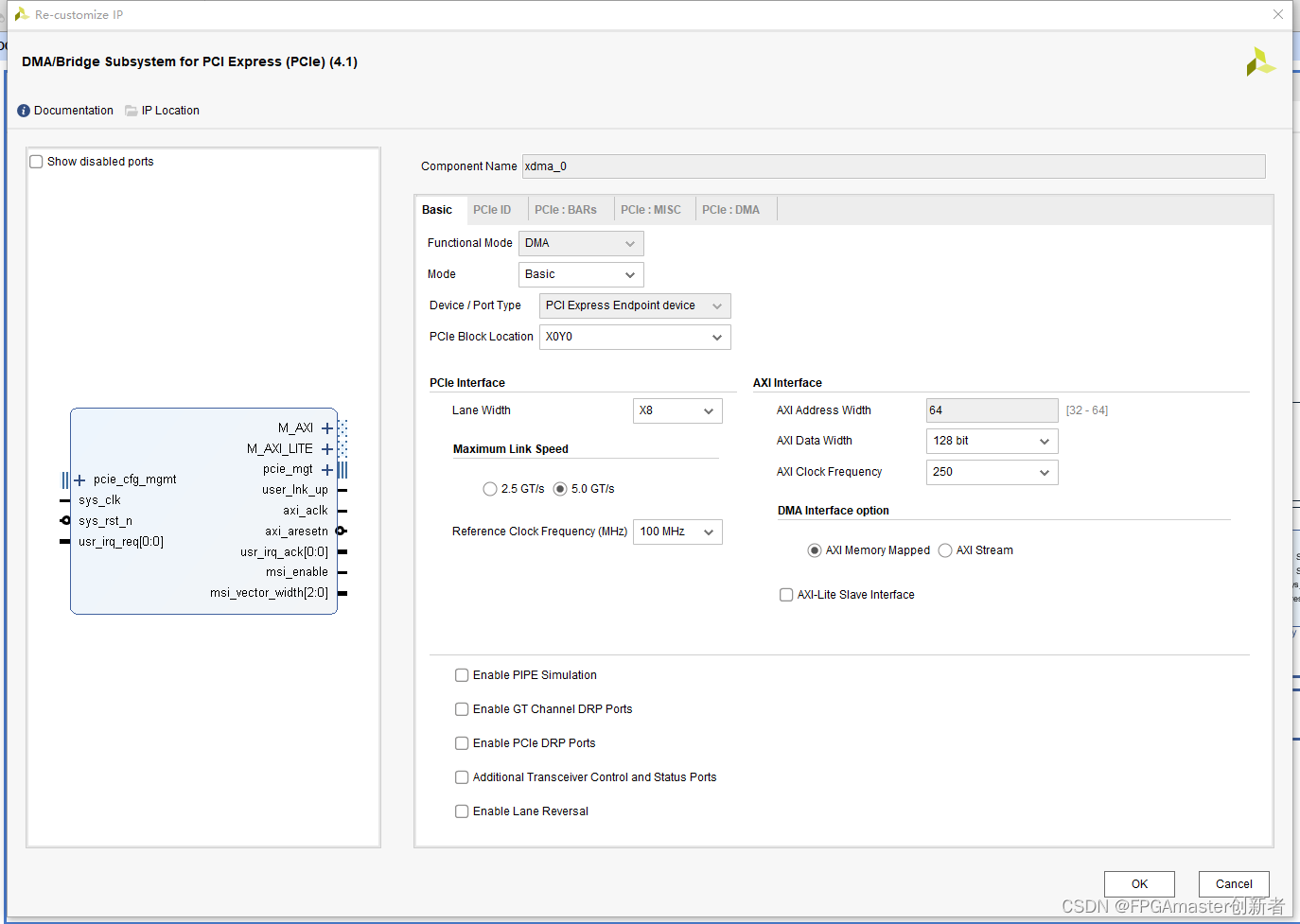

PCIE采用的是xilinx官方的XDMA IP:

主要配置为:PCIE 2.0 x8工作模式 (此芯片的最高配)

三、AGX Orin平台配置

开机:

首先拿到设备之后,根据官方的提示和步骤完成开机步骤,默认安装的ubuntu系统,开机之后就和正常的linux虚机没什么区别了

参考文献:AGX Orin官方开机测试指南

安装xdma驱动(linux版)

驱动下载

可以从官方下载驱动,也可以从我这里下载我使用的版本

官方驱动下载:GitHub - Xilinx/dma_ip_drivers: Xilinx QDMA IP Drivers

本设计使用的驱动:xdma_linux驱动下载

驱动安装

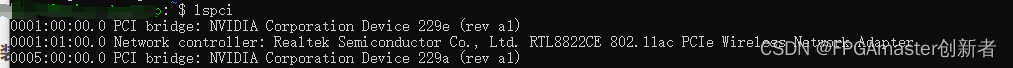

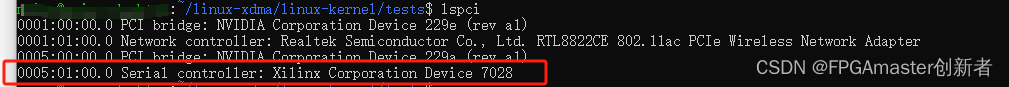

1、检查pci驱动

打开 Linux 终端,输入“lspci”命令并执行, 如下图所示:

可以看到,没有 Xilinx 相关的信息,这是因为没有安装 XDMA 的 Linux 系统驱动。

2、驱动安装

下载好的驱动,存放到AGX orin上面

由于提供的都是源码,需要编译安装然后才能使用。打开终端,输入如下命令:

cd ./dma_ip_drivers/XDMA/linux-kernel/xdma/

sudo apt install build-essential #(如果之前没有安装过 build-essential,需要安装)

sudo make install驱动安装完成后,重启 Linux 系统主机。

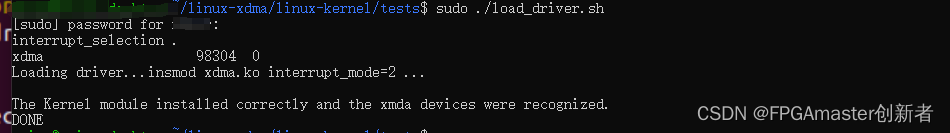

3、加载驱动

现在打开终端,输入如下命令进入 xdma 驱动目录下的 tests 目录:

cd ./dma_ip_drivers/XDMA/linux-kernel/tests该目录提供了驱动加载脚本及应用测试脚本,其中的 load_driver.sh 即为 XDMA 的驱动加载脚

本。执行该脚本前需要先给该脚本赋予可执行权限,然后以 root 身份执行,命令如下:

chmod +x load_driver.sh

sudo ./load_driver.sh

可以看到 XDMA 驱动已正确加载。

4、检测XDMA设备

在终端中输入“lspci”命令

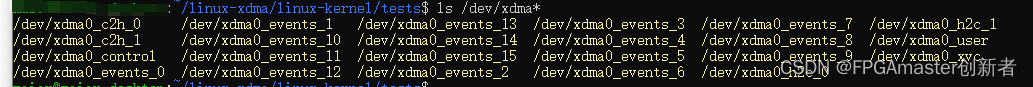

在终端中输入“ls /dev”命令并执行,可以在/dev 目录下看到以 xdma0 开头的设备文件,如下图所示:

以下是每个设备文件的简要说明:

/dev/xdma0_control:用于控制和配置DMA设备。/dev/xdma0_user:用于用户自定义用途。/dev/xdma0_xvc:用于虚拟JTAG功能。/dev/xdma0_events_*:用于处理DMA事件(中断)。/dev/xdma0_c2h_*:用于从卡到主机(Card to Host,简称C2H)的DMA数据传输。/dev/xdma0_h2c_*:用于从主机到卡(Host to Card,简称H2C)的DMA数据传输。

这表明 AGX orin系统已正确安装 XDMA 驱动并检测到了 XDMA 设备。

四、下板测试

把第三章的vivado工程生成的bit文件,烧录到FPGA开发板的FLASH,然后重启AGX orin

1、应用测试

打开终端,输入如下命令进入 xdma 目录下的tests 目录:

cd ./dma_ip_drivers/XDMA/linux-kernel/

cd tests/需要给他们添加可执行权限:

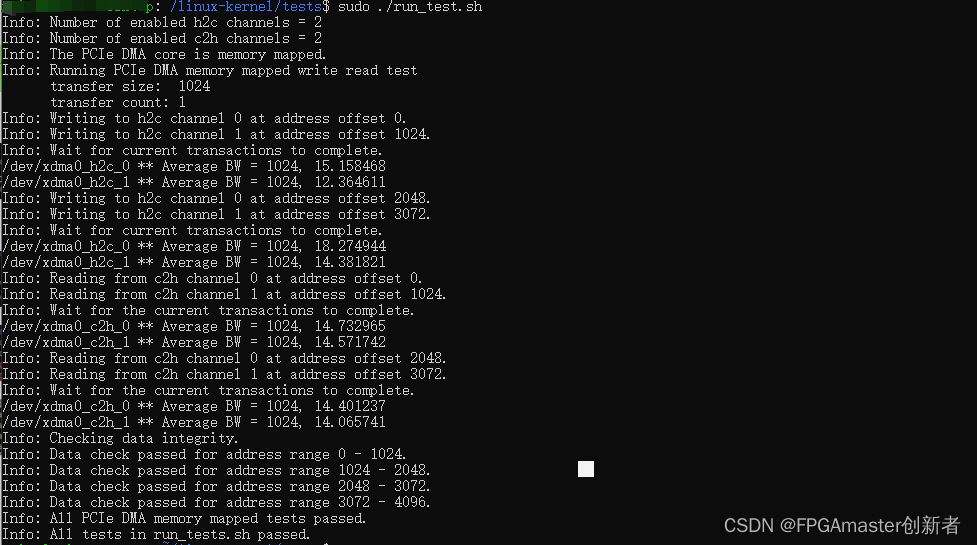

输入如下命令以执行 run_test.sh 脚本:

chmod +x run_test.sh

chmod +x dma_memory_mapped_test.sh

sudo ./run_test.shrun_test.sh 脚本用于测试基本的 XDMA 传输,并具有如下功能:

✓ 检测设计是基于 AXI-MM 接口还是 AXI_ST 接口,并查看启用了多少个通道;

✓ 对所有启用的通道进行基本传输测试;

✓ 检查数据完整性;

✓ 报告通过或失败

测试结果的最后两行 passed 表明我们搭建的基于 XDMA 的 PCIe 通信子系统正确,且 XDMA 驱动安装和驱动示例程序运行正常。

2、PCIE的读和写

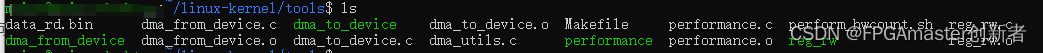

Linux 的 XDMA 测试应用是源码提供的,需要先编译。打开终端,输入如下命令进入 xdma 目录下的tools 目录并编译:

cd ./dma_ip_drivers/XDMA/linux-kernel/

cd tools/

make编译后, tools 目录下有四个 XDMA 相关的测试应用,如下图所示:(第一次进来没有data_rd.bin文件)

dma_to_device

- 这是一个可执行文件,用于将数据从主机内存写入到 FPGA 设备。

dma_from_device

- 这是一个可执行文件,用于从 FPGA 设备读取数据到主机内存。

performance

- 这是一个可执行文件,可能用于测试和评估 DMA 性能

reg_rw

- 这是一个可执行文件,可能用于读取和写入 FPGA 寄存器

测试写入

打开终端,进入tools目录,然后输入以下指令(首先准备好一个测试数据datafile4K.bin):

sudo ./dma_to_device -d /dev/xdma0_h2c_0 -a 0x00000000 -s 2048 -f datafile4K.bin

这个命令将 data_to_write.bin 文件中的数据写入到 /dev/xdma0_h2c_0 设备的地址 0x00000000,长度为 2048 字节。

![]()

表示写入完成!!!

测试读取

打开终端,进入tools目录,然后输入以下指令

sudo ./dma_from_device -d /dev/xdma0_c2h_0 -a 0x00000000 -s 2048 -f data_rd.bin

这个命令从 /dev/xdma0_c2h_0 设备开始的地址 0x00000000 读取 2048 字节的数据,并保存到 data_rd.bin 文件中。

![]()

表示读取完成!!!

验证读写

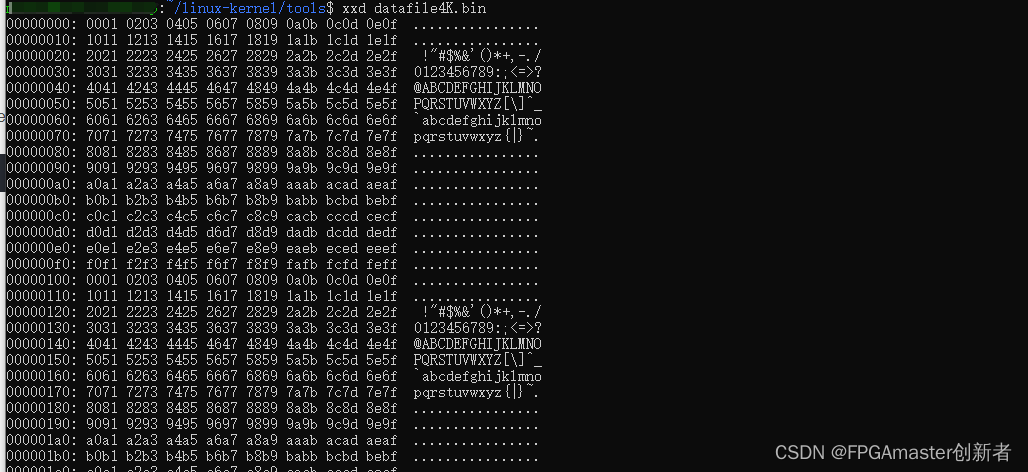

通过xxd命令来打开.bin文件:

首先打开写入的数据文件datafile4K.bin,输入以下指令

xxd datafile4K.bin

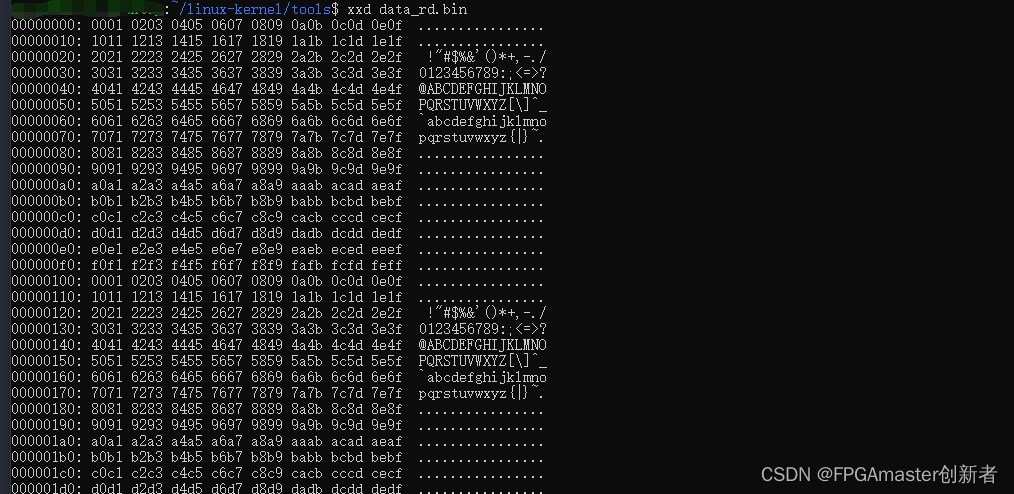

然后再读取从PCIE读取出来的数据data_rd.bin,输入以下指令

xxd data_rd.bin

可以看见写入数据和读出的数据一样

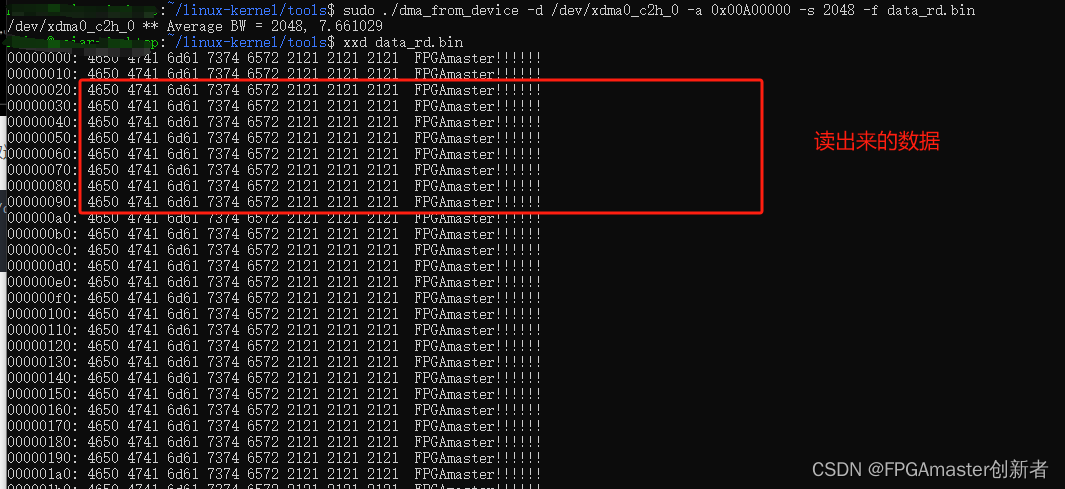

3、读取FPGA写入的数据

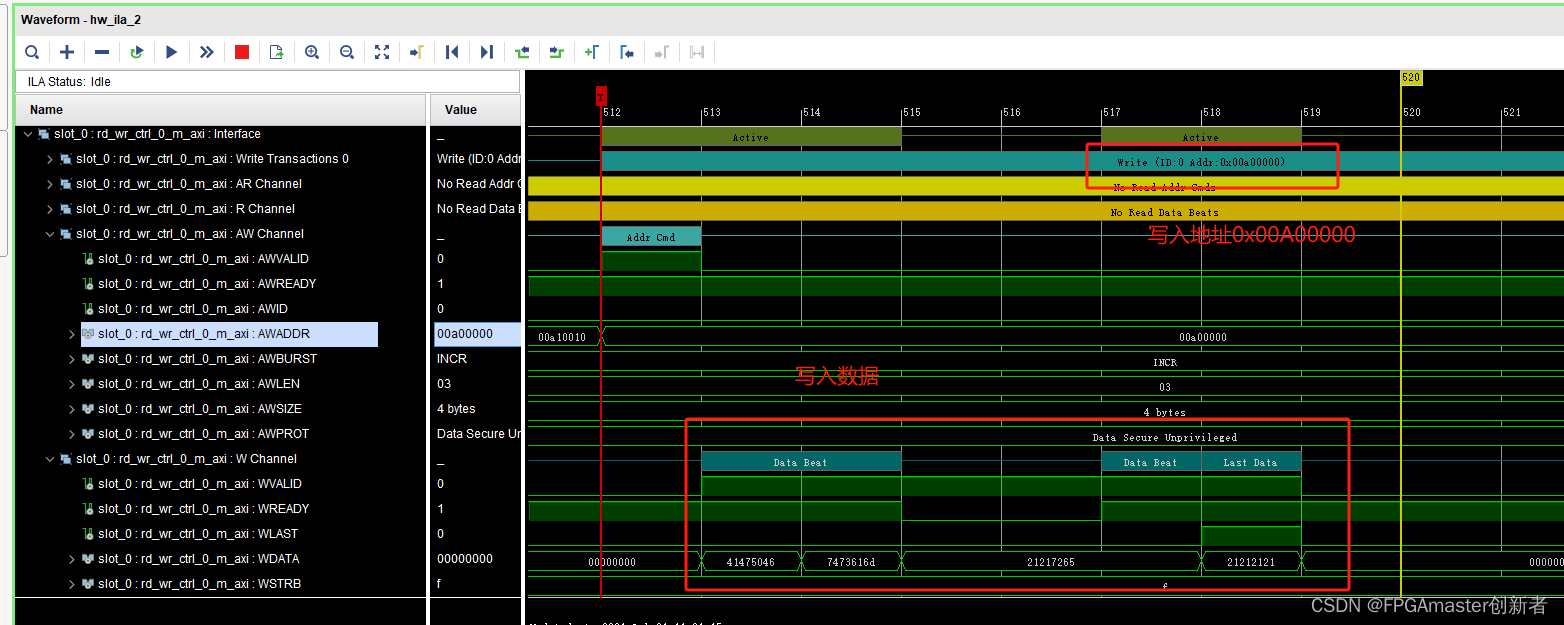

由第二章设计的FPGA工程可以得到,我们通过FPGA端向PCIE不停地写数据,我们先通过vivado的ila来查看写入的数据:

然后我们通过读取指令,来读取这个地址的数据,并通过xxd查看

sudo ./dma_from_device -d /dev/xdma0_c2h_0 -a 0x00A00000 -s 2048 -f data_rd.binxxd data_rd.bin

因大小端的问题,这个数据应该和ila的按字节取反即可

可见和ila抓的完全相同。说明FPGA写入,PCIE读取没问题!!!

五、测试板卡速度

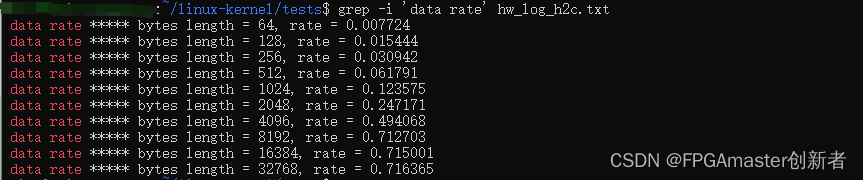

perform_hwcount.sh 脚本用于测试 XDMA 的硬件性能(读写速率),并将测试结果复制到hw_log_h2c.txt和 hw_log_c2h.txt 文本文件。 hw_log_h2c.txt 为写测试结果, hw_log_c2h.txt 为读测试结果。

打开终端,进入tests目录,然后输入以下指令

chmod +x perform_hwcount.sh

sudo ./perform_hwcount.sh 1 1参数 1 1 是指要测试的读写通道数。

然后输入以下命令查看写速度:

grep -i 'data rate' hw_log_h2c.txt

可以看到,对与写速率, 开始时传输长度越大,相应的传输速率 rate 也越大,当传输长度达到一定值时,对传输速率的影响就不大了。

由此可以验证本次设计整体没问题!!,终于大功告成啦!!!

完整工程文件下载:AGX orin与FPGA实现PCIE完整工程 提取码:985w

如果感觉文章对您有用,麻烦三连支持一下,方便下次用到的时候,就可以快速找到我,非常感谢您的支持!!!

相关文章:

基于AGX ORIN与FPGA K7实现PCIE高速数据通信/Orin与FPGA高速数据传输/XDMA在linux系统使用教程

因最近想学习AGX orin和FPGA实现数据高速通信,借此机会和大家一起学习AGX orin和FPGA 制作不易,记得三连哦,给我动力,持续更新!!! 完整工程文件下载:AGX orin与FPGA实现PCIE完整…...

Vue3:全局播放背景音乐

说明:一个全局播放的背景音乐,首页无音乐无音乐图标,在首页互动跳转页面并开始播放音乐,切换页面不需暂停音乐也不会重置音乐,可以通过音乐图标控制暂停或播放。 MusicPlay.vue(音乐组件) <…...

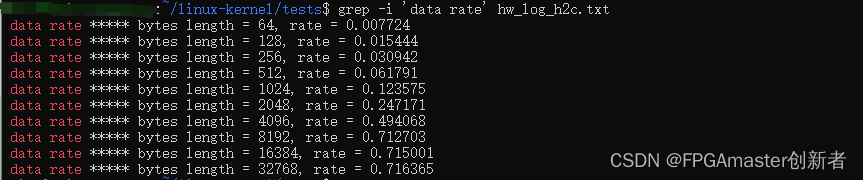

2024年07月03日 Redis部署方式和持久化

Redis持久化方式:RDB和AOF,和混合式 RDB:周期备份模式,每隔一段时间备份一份快照文件,从主线程Fork一个备份线程出来备份,缺点是会造成数据的丢失。 AOF:日志模式,每条命令都以操作…...

成都仅需浏览器即可快速查看的数据采集监控平台!

LP-SCADA数据采集监控平台无需额外客户端,只需要一个标准的Web浏览器,用户可以迅速访问系统并开始使用,同时支持跨平台访问。一个用户可监控多个过程,多个用户可以监控同一过程,真正实现了数据的开放性及过程信号的透明…...

LLM - 神经网络的训练过程

1. 对于回归问题,用损失函数来计算预测值和真实值的差异,一种常用的公式是如下图所示(Mean Square Error),如果损失函数的值越小说明神经网络学习越准确,所以神经网络训练目标是减小损失函数的值, 2. 对于分类问题&…...

【全网最全ABC三题完整版】2024年APMCM第十四届亚太地区大学生数学建模竞赛(中文赛项)完整思路解析+代码+论文

我是Tina表姐,毕业于中国人民大学,对数学建模的热爱让我在这一领域深耕多年。我的建模思路已经帮助了百余位学习者和参赛者在数学建模的道路上取得了显著的进步和成就。现在,我将这份宝贵的经验和知识凝练成一份全面的解题思路与代码论文集合…...

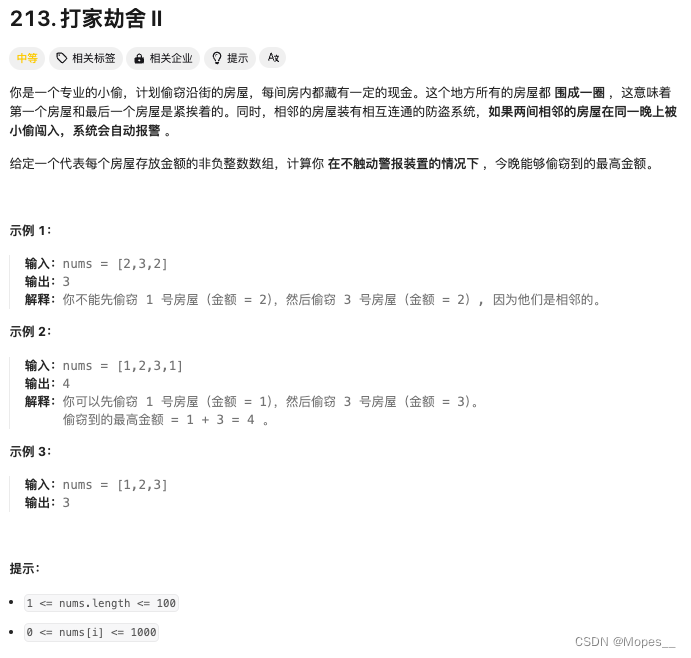

Python | Leetcode Python题解之第213题打家劫舍II

题目: 题解: class Solution:def rob(self, nums: List[int]) -> int:def robRange(start: int, end: int) -> int:first nums[start]second max(nums[start], nums[start 1])for i in range(start 2, end 1):first, second second, max(fi…...

揭秘数据之美:【Seaborn】在现代【数学建模】中的革命性应用

目录 已知数据集 tips 生成数据集并保存为CSV文件 数据预览: 导入和预览数据 步骤1:绘制散点图(Scatter Plot) 步骤2:添加回归线(Regression Analysis) 步骤3:分类变量分析&…...

【宠粉赠书】UML 2.5基础、建模与设计实践

为了回馈粉丝们的厚爱,今天小智给大家送上一套系统建模学习的必备书籍——《UML 2.5基础、建模与设计实践》。下面我会详细给大家介绍这本书,文末留有领取方式。 图书介绍 《UML 2.5基础、建模与设计实践》以实战为主旨,结合draw.io免费软件…...

Python中几个重要的集合

Python中几个重要的集合(Collection)类型,包括列表(List)、元组(Tuple)、集合(Set)和字典(Dictionary) 1. 列表(List) 说…...

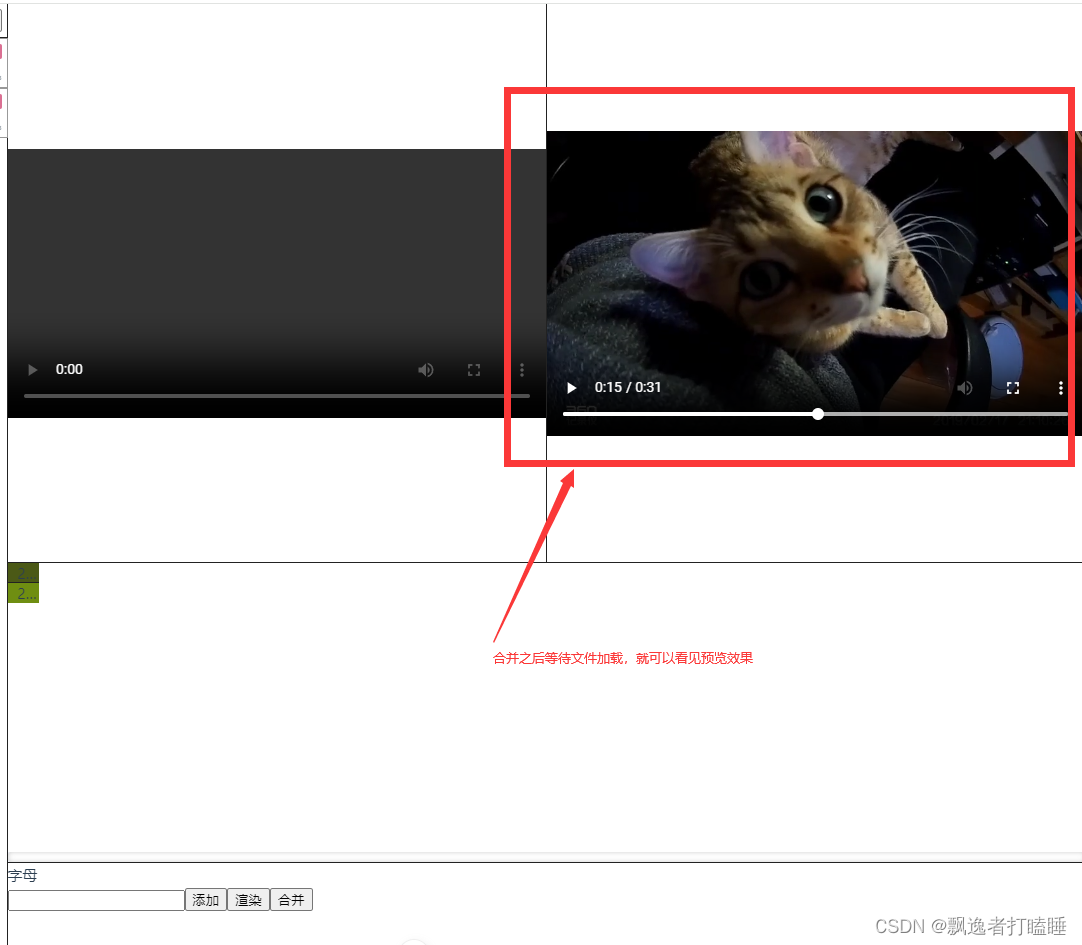

【JS】纯web端使用ffmpeg实现的视频编辑器-视频合并

纯前端实现的视频合并 接上篇ffmpeg文章 【JS】纯web端使用ffmpeg实现的视频编辑器 这次主要添加了一个函数,实现了视频合并的操作。 static mergeArgs(timelineList) {const cmd []console.log(时间轴数据,timelineList)console.log("文件1",this.readD…...

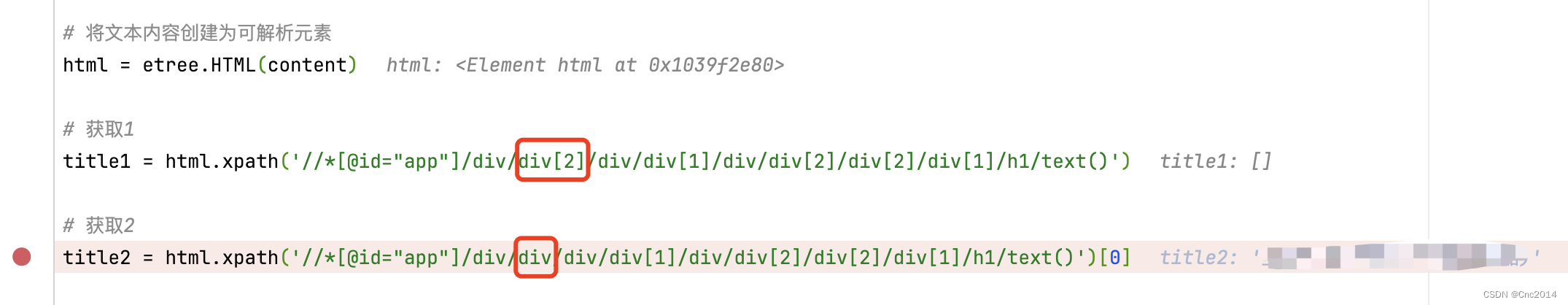

解决Python用xpath爬取不到数据的一个思路

前言 最近在学习Python爬虫的知识,既然眼睛会了难免忍不住要实践一把。 不废话直接上主题 代码不复杂,简单的例子奉上: import requests from lxml import etreecookie 浏览器F12网络请求标头里有 user_agent 浏览器F12网络请求标头里有…...

C#面:如何把一个array复制到arrayist里

要将一个数组复制到ArrayList中,可以使用ArrayList的AddRange方法。以下是一个示例代码: int[] array { 1, 2, 3, 4, 5 }; ArrayList arrayList new ArrayList(); arrayList.AddRange(array); 在上面的代码中,我们首先创建了一个整数类型…...

解决前后端同一个端口跨域问题

前端起了一个代理 如果url是api开头的自动代理访问8080端口(解决前后端端口不一致要么是前端代理,要么是后端加过滤器) proxy:{/api:{target:http://localhost:8080,changeOrigin : true,// 替换去掉路径上的api// rewrite:(path)>path.r…...

《C语言》认识数据类型和理解变量

🌹个人主页🌹:喜欢草莓熊的bear 🌹专栏🌹:C语言基础 目录 前言 一、数据类型的介绍 1.1 字符型 1.2 整形 1.3 浮点型 1.4 布尔类型 1.5 各种数据类型的长度 1.5.1 sizeof操作符 1.5.2 数据类型长度…...

【ARM 常见汇编指令学习 7.1 -- LDRH 半字读取指令】

请阅读【嵌入式开发学习必备专栏】 文章目录 LDRH 使用介绍LDRH(Load Register Half-word)总结 LDRH 使用介绍 在ARMv9架构中,汇编指令LDRH用于从内存中载入数据到寄存器的指令,下面将分别对它进行详细介绍: LDRH&am…...

C++期末整理

课堂笔记 构造与析构 #include <iosteam> #include <cstring> using namespace std;struct Date {int y, m, d;void setDate(int, int, int);Date(int yy, int mm, int dd) {y yy, m mm, d dd;} };class Student { private:char* name;Date birthday; public:…...

技术派Spring事件监听机制及原理

Spring事件监听机制是Spring框架中的一种重要技术,允许组件之间进行松耦合通信。通过使用事件监听机制,应用程序的各个组件可以在其他组件不直接引用的情况下,相互发送和接受消息。 需求 在技术派中有这样一个需求,当发布文章或…...

秋招突击——设计模式补充——简单工厂模式和策略模式

文章目录 引言正文简单工厂模式策略模式策略模式和工厂模式的结合策略模式解析 总结 引言 一个一个来吧,面试腾讯的时候,问了我单例模式相关的东西,自己这方面的东西,还没有看过。这里需要需要补充一下。但是设计模式有很多&…...

SwiftUI中List的liststyle样式及使用详解添加、移动、删除、自定义滑动

SwiftUI中的List可是个好东西,它用于显示可滚动列表的视图容器,类似于UITableView。在List中可以显示静态或动态的数据,并支持垂直滚动。List是一个数据驱动的视图,当数据发生变化时,列表会自动更新。针对List…...

3步释放华硕笔记本潜能:G-Helper轻量化控制工具的极致优化指南

3步释放华硕笔记本潜能:G-Helper轻量化控制工具的极致优化指南 【免费下载链接】g-helper Lightweight Armoury Crate alternative for Asus laptops. Control tool for ROG Zephyrus G14, G15, G16, M16, Flow X13, Flow X16, TUF, Strix, Scar and other models …...

7大应用场景:如何用计算机视觉技术彻底改变足球比赛分析?

7大应用场景:如何用计算机视觉技术彻底改变足球比赛分析? 【免费下载链接】sports computer vision and sports 项目地址: https://gitcode.com/gh_mirrors/sp/sports 在当今数字化体育时代,足球场精准定位技术正以前所未有的方式改变…...

3.25 复试练习

OJ改错填空strcpy--strcpy(dest, src); // 将src复制到deststrcmp--strcmp(s1, s2);返回值含义0两个字符串相等> 0s1 大于 s2< 0s1 小于 s2矩阵质因数问题描述将一个正整数N(1<N<32768)分解质因数。例如,输入90,打印出902*3*3*5。输入说明输…...

)

保姆级教程:用Coze零代码打造一个能聊天的微信公众号机器人(附服务器配置避坑指南)

零基础玩转Coze:从智能体创建到微信公众号部署全指南 在数字化营销日益重要的今天,拥有一个能24小时响应客户需求的智能客服已成为许多企业的标配。但对于没有技术背景的运营和市场人员来说,开发一个功能完善的聊天机器人似乎遥不可及。Coze平…...

DbGate数据库管理工具:Docker一键部署与跨平台远程访问实战

1. 为什么选择DbGateDocker组合 第一次接触DbGate是在一个需要同时管理MySQL和MongoDB的项目中。当时团队里有人用Navicat,有人用DBeaver,数据库类型切换时总要重新适应界面。直到发现这个支持多数据库的开源工具,才真正体会到什么叫"一…...

)

OpenAI Agent SDK实战:5分钟搞定MCP协议接入(附完整代码)

OpenAI Agent SDK与MCP协议深度整合实战指南 在当今AI技术快速迭代的背景下,工具链的标准化与互操作性成为开发者面临的核心挑战之一。OpenAI推出的Agent SDK与MCP协议组合,为构建可扩展的智能体系统提供了工业级解决方案。本文将带您从零开始࿰…...

海康WEBSDK无插件版实战:零基础构建WEB端网络摄像机实时监控系统

1. 环境准备:5分钟搞定基础配置 第一次接触海康WEBSDK无插件版时,我也被那些专业术语吓到过。但实际操作后发现,只要准备好三样东西就能开工:一台能联网的电脑、海康网络摄像机、以及从官网下载的开发包。这里分享几个新手容易踩的…...

嵌入式通信协议SPI/I2C/UART原理与应用

嵌入式通信协议原理图解与技术解析1. 串行通信协议基础1.1 SPI通信协议SPI(Serial Peripheral Interface)是一种全双工、同步串行通信协议,采用主从架构设计。其核心特点包括:四线制结构:SCLK(时钟)、MOSI(主出从入)、MISO(主入从出)、SS(片选…...

VSCode配置STM32标准库开发环境:手把手解决core_cm3.c编译报错与头文件路径问题

VSCode搭建STM32开发环境:解决标准库兼容性与智能感知难题 当开发者从Keil或IAR转向VSCode时,往往会遇到两个棘手的拦路虎:标准库与GCC的兼容性问题,以及代码智能感知的缺失。本文将深入解决这两个核心痛点,带你构建一…...

APScheduler避坑指南:解决定时任务重复执行和时区问题的5种实战方案

APScheduler生产级实战:彻底解决定时任务重复执行与时区混乱的终极方案 凌晨三点,服务器告警铃声突然响起——监控系统显示同一批数据处理任务在短时间内被重复执行了17次。这不是科幻场景,而是某电商平台在使用APScheduler时遇到的真实生产事…...