单周期CPU(三)译码模块(minisys)(verilog)(vivado)

`timescale 1ns / 1ps

//module Idecode32 (input reset,input clock,output [31:0] read_data_1, // 输出的第一操作数output [31:0] read_data_2, // 输出的第二操作数input [31:0] Instruction, // 取指单元来的指令input [31:0] read_data, // 从DATA RAM or I/O port取出的数据input [31:0] ALU_result, // 从执行单元来的运算的结果,需要扩展立即数到32位input Jal, // 来自控制单元,说明是JAL指令 input RegWrite, // 来自控制单元input MemtoReg, // 来自控制单元input RegDst, // 来自控制单元output [31:0] Sign_extend, // 译码单元输出的扩展后的32位立即数input [31:0] opcplus4 // 来自取指单元,JAL中用

);reg[31:0] register[0:31]; // 寄存器组共32个32位寄存器reg[4:0] write_register_address; // 要写的寄存器的号reg[31:0] write_data; // 要写寄存器的数据放这里wire[4:0] read_register_1_address; // 要读的第一个寄存器的号(rs)wire[4:0] read_register_2_address; // 要读的第二个寄存器的号(rt)wire[4:0] write_register_address_1; // r-form指令要写的寄存器的号(rd)wire[4:0] write_register_address_0; // i-form指令要写的寄存器的号(rt)wire[15:0] Instruction_immediate_value; // 指令中的立即数wire[5:0] opcode; // 指令码assign opcode = Instruction[31:26]; // OPassign read_register_1_address = Instruction[25:21]; // rsassign read_register_2_address = Instruction[20:16]; // rtassign write_register_address_1 = Instruction[15:11]; // rd (r-form)assign write_register_address_0 = Instruction[20:16]; // rt (i-form)assign Instruction_immediate_value = Instruction[15:0]; // data, rladr (i-form)wire sign; // 取符号位的值assign sign = Instruction[15]; // 取指令的第15位作为符号位assign Sign_extend[31:16] = (sign) ? {16{1'b1}} : {16{1'b0}}; // 符号扩展,根据符号位填充高位assign Sign_extend[15:0] = Instruction[15:0]; // 将原始的16位立即数填充到低位assign read_data_1 = register[read_register_1_address]; // 从寄存器组中读取第一个源寄存器的数据assign read_data_2 = register[read_register_2_address]; // 从寄存器组中读取第二个源寄存器的数据always @* beginif (Jal) beginwrite_register_address = 5'b11111; // JAL指令的目标寄存器是31号寄存器end else beginif (RegDst) beginwrite_register_address = write_register_address_1; // r-form指令的目标寄存器地址end else beginwrite_register_address = write_register_address_0; // i-form指令的目标寄存器地址endendendalways @* beginif (MemtoReg) beginwrite_data = read_data; // 数据来自数据RAM的输出end else beginwrite_data = ALU_result; // 运算指令的数据来自ALU_resultendendinteger i;always @(posedge clock) beginif (reset == 1) beginfor (i = 0; i < 32; i = i + 1)register[i] <= 0; // 初始化寄存器组,将所有寄存器清零end else if (RegWrite == 1) beginif (write_register_address != 5'b00000) beginregister[write_register_address] <= write_data; // 写入数据到目标寄存器,除了0号寄存器endendendendmodule仿真代码如下

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date:

// Design Name:

// Module Name: idcode32_sim

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module idcode32_sim ();// input reg[31:0] Instruction = 32'b000000_00010_00011_00111_00000_100000; //add $7,$2,$3reg[31:0] read_data = 32'h00000000; // 从DATA RAM or I/O port取出的数据reg[31:0] ALU_result = 32'h00000005; // 需要扩展立即数到32位reg Jal = 1'b0; reg RegWrite = 1'b1;reg MemtoReg = 1'b0;reg RegDst = 1'b1;reg clock = 1'b0 ,reset = 1'b1;reg[31:0] opcplus4 = 32'h00000004; // 来自取指单元,JAL中用// outputwire[31:0] read_data_1;wire[31:0] read_data_2;wire[31:0] Sign_extend;Idecode32 Uid (.reset (reset), // 复位(高电平有效).clock (clock), // CPU时钟.read_data_1 (read_data_1), // 输出的第一操作数.read_data_2 (read_data_2), // 输出的第二操作数.Instruction (Instruction), // 取指单元来的指令.read_data (read_data), // 从DATA RAM or I/O port取出的数据.ALU_result (ALU_result), // 从执行单元来的运算的结果,需要扩展立即数到32位.Jal (Jal), // 来自控制单元,说明是JAL指令 .RegWrite (RegWrite), // 来自控制单元.MemtoReg (MemtoReg), // 来自控制单元.RegDst (RegDst), // 来自控制单元.Sign_extend (Sign_extend), // 扩展后的32位立即数.opcplus4 (opcplus4) // 来自取指单元,JAL中用);initial begin#200 reset = 1'b0;#200 begin Instruction = 32'b001000_00111_00011_1000000000110111; //addi $3,$7,0X8037read_data = 32'h00000000; ALU_result = 32'hFFFF803C;Jal = 1'b0;RegWrite = 1'b1;MemtoReg = 1'b0;RegDst = 1'b0;opcplus4 = 32'h00000008; end#200 begin Instruction = 32'b001100_00010_00100_1000000010010111; //andi $4,$2,0X8097read_data = 32'h00000000; ALU_result = 32'h00000002;Jal = 1'b0;RegWrite = 1'b1;MemtoReg = 1'b0;RegDst = 1'b0;opcplus4 = 32'h0000000c; end#200 begin Instruction = 32'b000000_00000_00001_00101_00010_000000; //sll $5,$1,2read_data = 32'h00000000; ALU_result = 32'h00000004;Jal = 1'b0;RegWrite = 1'b1;MemtoReg = 1'b0;RegDst = 1'b1;opcplus4 = 32'h00000010; end#200 begin Instruction = 32'b100011_00000_00110_0000000100000000; //LW $6,0(0X100)read_data = 32'h0000007B; ALU_result = 32'h00000054;Jal = 1'b0;RegWrite = 1'b1;MemtoReg = 1'b1;RegDst = 1'b0;opcplus4 = 32'h00000014; end#200 begin Instruction = 32'b000011_00000000000000000000000000; //JAL 0000read_data = 32'h00000000; ALU_result = 32'h00000004;Jal = 1'b1;RegWrite = 1'b1;MemtoReg = 1'b0;RegDst = 1'b0;opcplus4 = 32'h00000018; endend always #50 clock = ~clock;

endmodule

仿真波形图如下图

相关文章:

单周期CPU(三)译码模块(minisys)(verilog)(vivado)

timescale 1ns / 1ps //module Idecode32 (input reset,input clock,output [31:0] read_data_1, // 输出的第一操作数output [31:0] read_data_2, // 输出的第二操作数input [31:0] Instruction, // 取指单元来的指令input [31:0] …...

理想化相机模型的相机内参

文章目录 理想化相机模型的相机内参计算1. 相机内参定义2. 根据视角和图像分辨率计算相机内参2.1 计算焦距 fx 和 fy2.2 计算主点 cx 和 cy3. 示例计算3.1 计算 fx3.2 假设 fy = fx(因为没有垂直视场角的信息)3.3 计算主点4. 相机内参矩阵理想化相机模型的相机内参计算 在理…...

【数据脱敏】⭐️SpringBoot 整合 Jackson 实现隐私数据加密

目录 🍸前言 🍻一、Jackson 序列化库 🍺二、方案实践 2.1 环境准备 2.2 依赖引入 2.3 代码编写 💞️三、接口测试 🍹四、章末 🍸前言 小伙伴们大家好,最近也是很忙啊,上次的文章…...

骑砍2霸主MOD开发(18)-多人联机模式开发环境搭建

一.多人联机模式网络拓扑图 二.专用服务器搭建(DedicatedServer) <1.Token生成(用于LobbyServer的校验): 进入多人联机大厅,ALT~打开RGL控制台,输入customserver.gettoken Token文件路径:C:\Users\taohu\Documents\Mount and Blade II Bannerlord\Tokens <2.启动专用服务…...

【HZHY-AI300G智能盒试用连载体验】在华为IoTDA平台上建立设备

目录 华为IoTDA平台 注册IoTDA实例 创建产品 添加设备 本文首发于:【HZHY-AI300G智能盒试用连载体验】 智能工业互联网网关 - 北京合众恒跃科技有限公司 - 电子技术论坛 - 广受欢迎的专业电子论坛! 在上一篇博文中介绍了如何在HZHY-AI300G智能盒创建南向设备&a…...

【LLM】-05-提示工程-部署Langchain-Chat

目录 1、软硬件要求 1.1、软件要求 1.2、硬件要求 1.3、个人配置参考 2、创建cuda环境 3、下载源码及模型 4、配置文件修改 5、初始化知识库 5.1、训练自己的知识库 6、启动 7、API接口调用 7.1、使用openai 参考官方wiki,本文以Ubuntu20.04_x64…...

【漏洞复现】Next.js框架存在SSRF漏洞(CVE-2024-34351)

0x01 产品简介 ZEIT Next.js是ZEIT公司的一款基于Vue.js、Node.js、Webpack和Babel.js的开源Web应用框架。 0x02 漏洞概述 ZEIT Next.js 13.4版本至14.1.1之前版本存在代码问题漏洞,该漏洞源于存在服务器端请求伪造 (SSRF) 漏洞 0x03 搜索引擎 body"/_nex…...

【2024最新华为OD-C/D卷试题汇总】[支持在线评测] 小区小朋友统计(100分) - 三语言AC题解(Python/Java/Cpp)

🍭 大家好这里是清隆学长 ,一枚热爱算法的程序员 ✨ 本系列打算持续跟新华为OD-C/D卷的三语言AC题解 💻 ACM银牌🥈| 多次AK大厂笔试 | 编程一对一辅导 👏 感谢大家的订阅➕ 和 喜欢💗 🍿 最新华为OD机试D卷目录,全、新、准,题目覆盖率达 95% 以上,支持题目在线…...

Vuex看这一篇就够了

💝💝💝欢迎来到我的博客,很高兴能够在这里和您见面!希望您在这里可以感受到一份轻松愉快的氛围,不仅可以获得有趣的内容和知识,也可以畅所欲言、分享您的想法和见解。 非常期待和您一起在这个小…...

Kafka集群创建

这样就创建好了docker4个镜像,三个node,一个manager。 其中,浏览器访问的是manager对应的那个url,直接在里面加Cluster...

2024.7.22 作业

1.将双向链表和循环链表自己实现一遍,至少要实现创建、增、删、改、查、销毁工作 循环链表 looplinklist.h #ifndef LOOPLINKLIST_H #define LOOPLINKLIST_H#include <myhead.h>typedef int datatype;typedef struct Node {union {int len;datatype data;}…...

如何使用aiohttp或requests-async等库并发地执行多个HTTP请求

在Python中,要并发地执行多个HTTP请求,可以使用aiohttp这样的异步HTTP客户端库,因为它支持异步编程,能够显著提高IO密集型任务的性能,比如网络请求。requests-async并不是一个广泛认知的库(虽然可能存在类似…...

Golang | Leetcode Golang题解之第257题二叉树的所有路径

题目: 题解: func binaryTreePaths(root *TreeNode) []string {paths : []string{}if root nil {return paths}nodeQueue : []*TreeNode{}pathQueue : []string{}nodeQueue append(nodeQueue, root)pathQueue append(pathQueue, strconv.Itoa(root.V…...

关于css中flex布局垂直居中失效问题的原因

项目中遇到用flex进行页面布局后,使用上下居中设置:align-item: center; 目标效果如下: 但是失效,不起作用,如下图所示: 各种排查过后发现设置了子模块 align-self 属性,这会覆盖容器上的 al…...

用Redisson写一个库存扣减的方法

使用Redisson来处理库存操作可以确保在高并发环境下库存数据的一致性和完整性。以下是使用Redisson实现库存管理的一些通用方法,包括获取库存、扣减库存、设置库存等。我们将使用Redisson的ReentrantLock来确保并发安全。 首先,确保你已经正确设置了Red…...

第2节课:文本内容与格式化——HTML中的文本处理技巧

目录 文本内容与格式化:段落和标题:构建文本基础段落 <p>标题 <h1> 到 <h6> 格式化:强调和样式加粗 <b>斜体 <i>下划线 <u> 列表:组织内容无序列表 <ul>有序列表 <ol>定义列表 &…...

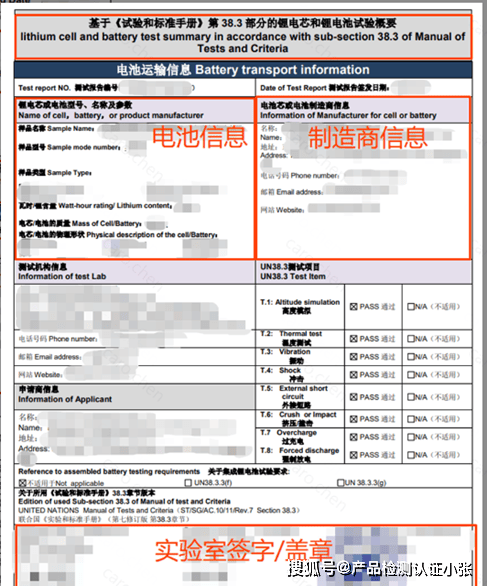

temu平台电池/锂电池UN38.3资质合规解析

UN38.3资质合规解析 为满足相关法律法规和商品运输安全需求含锂电池商品需要提供对应的UN38.3资质。截至7月29日,相关类目下UN38.3资质待上传或上传失败的商品可能面临下架。 -01什么是UN38.3- 1)UN38.3是指由联合国危险货物运输专家委员会编写的《试验…...

Huawei、Cisco 路由中 RIP 协议 summary 的用法

华为路由中 RIP summary summary用来使能 RIP 有类聚合,聚合后的路由以使用自然掩码的路由形式发布。undo summary用来取消有类聚合以便在子网之间进行路由,此时,子网的路由信息就会被发布出去。路由聚合降低了路由表中路由信息量。说明 有类…...

)

智能图像信息提取(飞桨OCR+ERNIE-Layout)

嘿,技术大佬们,今天我要分享的是一个超级棒的OCR技术方案,它结合了飞桨OCR和ERNIE-Layout,绝对是图像信息提取的利器! 线上体验地址:智能图像信息提取(飞桨OCRERNIE-Layout) 它基于ERNIE -Layout和多版本Pa…...

Ubuntu 24.04 LTS Noble安装 FileZilla Server

FileZilla Server 是一款使用图形用户界面快速创建 FTP 服务器的软件。它有助于测试需要 FTP 服务器功能的各种项目。虽然早期的 FileZilla FTP 服务器仅适用于 Windows 和 macOS,但现在我们也可以在 Linux(例如 Ubuntu 24.04)上安装 FileZil…...

从鱼眼到广角:相机畸变公式的实战拆解与参数调优

1. 相机畸变:从鱼眼到广角的视觉魔法 第一次用鱼眼镜头拍照片时,我被画面边缘夸张的弯曲效果震撼到了——直线变成了弧线,方形门框变成了圆润的拱门。这种"变形魔法"其实就是相机畸变最直观的体现。作为算法工程师,我花…...

云原生环境中的混沌工程实践指南

云原生环境中的混沌工程实践指南 引言 混沌工程是一种主动验证系统可靠性的方法,通过在生产环境中注入故障来发现潜在的系统弱点。本文将深入探讨如何在云原生环境中实施混沌工程。 一、混沌工程概述 1.1 核心概念 ┌───────────────────────…...

惠普OMEN游戏本终极性能优化:OmenSuperHub开源工具完全指南

惠普OMEN游戏本终极性能优化:OmenSuperHub开源工具完全指南 【免费下载链接】OmenSuperHub 使用 WMI BIOS控制性能和风扇速度,自动解除DB功耗限制。 项目地址: https://gitcode.com/gh_mirrors/om/OmenSuperHub 还在为惠普OMEN游戏本官方软件的臃…...

QMCDecode:轻松解锁QQ音乐加密音频的Mac专属神器

QMCDecode:轻松解锁QQ音乐加密音频的Mac专属神器 【免费下载链接】QMCDecode QQ音乐QMC格式转换为普通格式(qmcflac转flac,qmc0,qmc3转mp3, mflac,mflac0等转flac),仅支持macOS,可自动识别到QQ音乐下载目录,默认转换结…...

如何免费解锁Cursor AI Pro功能:终极三步激活指南

如何免费解锁Cursor AI Pro功能:终极三步激活指南 【免费下载链接】cursor-free-vip [Support 0.45](Multi Language 多语言)自动注册 Cursor Ai ,自动重置机器ID , 免费升级使用Pro 功能: Youve reached your trial r…...

DESIGN.md,让AI设计不跑偏

使用 AI 设计工具时,最烦人的问题之一,就是输出不稳定。你明明已经告诉它:颜色怎么用、字体怎么搭、按钮要什么风格。可它生成几次之后,还是会偷偷改一点,最后做出来的界面风格前后不一致。DESIGN.md 就是为了解决这个…...

超越基础扫描:实战解析Tessent ATPG中的Clock PO与RAM Sequential Patterns如何提升故障覆盖率

超越基础扫描:实战解析Tessent ATPG中的Clock PO与RAM Sequential Patterns如何提升故障覆盖率 在数字电路测试领域,达到95%以上的故障覆盖率曾是许多DFT工程师的终极目标,直到他们遇到了时钟驱动输出和嵌入式RAM模块。这些特殊结构如同电路…...

音乐歌词获取终极指南:如何3分钟搞定全网歌曲歌词的完整方案

音乐歌词获取终极指南:如何3分钟搞定全网歌曲歌词的完整方案 【免费下载链接】163MusicLyrics 云音乐歌词获取处理工具【网易云、QQ音乐】 项目地址: https://gitcode.com/GitHub_Trending/16/163MusicLyrics 你是否曾经为了找到一首心爱歌曲的完整歌词而花费…...

终极Windows 11优化指南:使用Win11Debloat开源工具提升系统性能的完整方案

终极Windows 11优化指南:使用Win11Debloat开源工具提升系统性能的完整方案 【免费下载链接】Win11Debloat A simple, lightweight PowerShell script that allows you to remove pre-installed apps, disable telemetry, as well as perform various other changes …...

MASA模组全家桶汉化包:3329条专业翻译,彻底告别英文界面困扰

MASA模组全家桶汉化包:3329条专业翻译,彻底告别英文界面困扰 【免费下载链接】masa-mods-chinese 一个masa mods的汉化资源包 项目地址: https://gitcode.com/gh_mirrors/ma/masa-mods-chinese 还在为Minecraft技术模组的英文界面而头疼吗&#x…...