【Verilog】期末复习

数字逻辑电路分为哪两类?它们各自的特点是什么?

组合逻辑电路:任意时刻的输出仅仅取决于该时刻的输入,而与电路原来的状态无关

没有记忆功能,只有从输入到输出的通路,没有从输出到输入的回路

时序逻辑电路:电路的输出不仅与当前时刻输入的变量的取值有关,而且与电路的原状态(即过去的输入情况)有关

Verilog HDL描述数字逻辑电路的建模方式有哪几种?它们各自的特点是什么?

数据流建模:数据不会存储,输入信号经过组合逻辑电路传到输出时类似于数据流动,而不会在其中存储,通过assign连续赋值语句进行描述

行为级建模:从电路外部行为的角度对其进行描述,抽象,(过程语句,语句块,过程赋值语句,条件分支,循环)

结构化建模:将硬件电路描述成一个分级子模块系统,通过逐层调用这些子模块构成功能复杂的数字逻辑电路和系统的一种描述方式

模块级建模

门级

开关级

解释名词

FPGA--Field Programmable Gate Array 现场可编程门阵列

ASIC--Application Specific Integrated Circuit 专用集成电路

IP--Intellectual Property 知识产权

RTL--Register Transfer Level 寄存器传输级

EDA--Electronic Design Automation 电子设计自动化

写出下面程序中变量x、y、z、a、b的类型

assign z=x&y;

initialbegina=4'b1010;b=8'hff;endwire:x、y、z

reg:a、b

分别通过阻塞赋值和非阻塞赋值语句描述如下电路

阻塞

module block(input wire din,input wire clk,output reg[3:0] q );always@(posedge clk)beginq[3]=q[2];q[2]=q[1];q[1]=q[0];q[0]=din;endmodule block(input wire din,input wire clk,output reg[3:0] q );always@(posedge clk)beginq[3]<=q[2];q[2]<=q[1];q[1]<=q[0];q[0]<=din;end

画出下面程序的仿真波形图,并通过串行语句实现

parameter T=10;initialforkwave=0;#T wave=1;#(2*T) wave=0;#(3*T) wave=1;#(4*T) wave=0;#(5*T) wave=1;join

parameter T=10;initialbeingwave=0;#T wave=1;#T wave=0;#T wave=1;#T wave=0;#T wave=1;endparameter T=10;initialbeginwave=0;while(1)#10 wave=~wave;end

2输入8位加法器,a b sum cin cout

module eight_bits_fulladder(sum,cout,a,b,c,cin);output[7:0] sum;output cout;input[7:0] a,b;input cin;assign {cout,sum}=a+b+cin; endmodulemodule eight_bits_fulladder_tb;reg cin;reg[7:0] a,b;wire cout;wire[7:0] sum;eight_bits_fulladder U1(sum,cout,a,b,cin);initialbegin a=8'b0;b=8'b0;cin=0;#10 a=8'b0;b=8'b0;cin=1;#10 a=8'b0;b=8'b1;cin=0;#10 a=8'b0;b=8'b1;cin=1;#10 a=8'hfe;b=8'h1;cin=0;#10 a=8'hfe;b=8'h1;cin=1;end endmodule

设计一个带复位端并且可以对输入的clk进行任意分频

module addr(count,clk,rst,qout);input clk,rst;output reg[31:0] count;output wire qout;always@(posedge clk)beginif(!rst) count<=0;else count<=count+1;endassign qout=count[0]; endmodulemodule addr_tb;reg clk,rst;wire[31:0] count;wire qout;addr U1(count,clk,rst,qout);always #10 clk=~clk;initialbeginclk=0;rst=0;#20 rst=1;#100 rst=0;#20 rst=1;end endmodule

module addr_tb;reg clk,rst;wire[31:0] count;wire qout;addr U1(count,clk,rst,qout);always #10 clk=~clk;initialbeginclk=0;rst=0;#20 rst=1;#90 rst=0;#20 rst=1;end endmodule

设计串行输入的8位移位寄存器,复位信号rst(低电平有效),1位数据输入datain,8位数据输出dataout,方向控制direction,请设计该串行寄存器模块

module shift(rst,clk,datain,dataout,direction);input datain;input rst,clk;input direction;output reg[7:0]dataout;always@(posedge clk or negedge rst)if(!rst)dataout<=8'b0;elseif(direction)dataout<={datain,dataout[7:1]};elsedataout<={dataout[6:0],datain}; endmodulemodule shift_tb;reg rst,clk,datain,direction;wire[7:0] dataout;shift U2(rst,clk,datain,dataout,direction);always#5 clk=~clk;initialbeginrst=0;clk=0;datain=0;direction=0;#5 rst=1;datain=1;#80 datain=0;direction=1;#80 datain=1;end endmodule

请使用verilog描述一个容量为256*8bit的ROM存储器,其中,输入时钟clk(上升沿有效),地址线为addr,片选信号cs低电平有效,输出数据为dout

module rom(clk,addr,cs,dout);input clk;input cs;input [7:0] addr;output [7:0] dout;reg[7:0] dout;reg[255:0] rom [7:0];initialbeginrom[0]=8'b0000_0000;rom[1]=8'b0000_0001;rom[2]=8'b0000_0010;rom[3]=8'b0000_0011;rom[4]=8'b0000_0100;rom[5]=8'b0000_0101;rom[6]=8'b0000_0110;rom[7]=8'b0000_0111;endalways@(posedge clk)beginif(cs) dout<=8'bzzzz_zzzz;else dout<=rom[addr];end endmodulemodule rom_tb;reg clk,cs;reg[7:0] addr;wire[7:0] dout;rom U1(clk,addr,cs,dout);initialbeignclk=0;addr=0;cs=0;endalways #10 clk=~clk;initialbeginrepeat(7) #20 addr=addr+1;end endmodule

设计一个检测序列1001

状态寄存器:在clk,rst控制下,由次态产生现态

C1:根据当前输入和现态,产生次态

C2:(输入)、现态产生输出

moore

module seqdata_moore(clk,rst,din,dout);input clk,rst,din;output dout;reg dout;reg[2:0] present_state,next_state;parameter s0=3'b000,s1=3'b001,s2=3'b010;s3=3'b011,s4=3'b100;always@(posedge clk or posedge rst)beginif(rst) prensent_state=s0;else present_state=next_state;endalways@(*)begincase(present_state)s0: if(din==1) next_state=s1;else next_state=s0;s1: if(din==0) next_state=s2;else next_state=s1;s2: if(din==0) next_state=s3;else next_state=s1;s3: if(din==1) next_state=s4;else next_state=s0;s4: if(din==1) next_state=s1;else next_state=s2;default: next_state=s0;endcaseendalways@(*)beginif(present_state==s4) dout=1;else dout=0;end endmodulemodule seqdata_moore_tb;reg clk,rst,din;wire dout;seqdata_moore U1(clk,rst,din,dout);always #5 clk=~clk;initialbeginclk=0;rst=1;din=0;#5 rst=0;#10 din=1;;#10 din=0;#20 din=1;#20 din=0;#30 din=1;#10 din=0;#20 din=1;end endmodulemealy

module seqdata_mealy(clk,rst,din,dout);input clk,rst,din;output dout;reg dout;reg[2:0] present_state,next_state;parameter s0=3'b000,s1=3'b001,s2=3'b010;s3=3'b011,s4=3'b100;always@(posedge clk or posedge rst)beginif(rst) prensent_state=s0;else present_state=next_state;endalways@(*)begincase(present_state)s0: if(din==1) begin next_state=s1; dout=0;endelse begin next_state=s0;dout=0;ends1: if(din==0) begin next_state=s2;dout=0; endelse begin next_state=s1;dout=0;ends2: if(din==0) begin next_state=s3;dout=0;endelse begin next_state=s1;dout=0;ends3: if(din==1) begin next_state=s1;dout=1;else begin next_state=s0;dout=0;default: begin next_state=s0;dout=0;endendcaseendendmodule

相关文章:

【Verilog】期末复习

数字逻辑电路分为哪两类?它们各自的特点是什么? 组合逻辑电路:任意时刻的输出仅仅取决于该时刻的输入,而与电路原来的状态无关 没有记忆功能,只有从输入到输出的通路,没有从输出到输入的回路 时序逻辑电路&…...

C#都可以找哪些工作?

在国内学习C#,可以找的工作主要是以下4个: 1、游戏开发 需要学习C#编程、Unity引擎操作、游戏设计和3D图形处理等。 2、PC桌面应用开发 需要学习C#编程、WinForm框架/WPF框架、MVVM设计模式和UI/UX设计等。 3、Web开发 需要学习C#编程、ASP.NET框架…...

机器学习Python使用scikit-learn工具包详细介绍

一、简介 Scikit-learn是一个开源的机器学习库,用于Python编程语言。它建立在NumPy、SciPy和matplotlib这些科学计算库之上,提供了简单有效的数据挖掘和数据分析工具。Scikit-learn库包含了许多用于分类、回归、聚类和降维的算法,包括支持向量…...

蓝桥杯真题 - 扫雷 - 题解

题目链接:https://www.lanqiao.cn/problems/549/learning/ 个人评价:难度 1 星(满星:5) 前置知识:无 整体思路 按题意模拟;为了减少不必要的“数组越界”判断,让数组下标从 1 1 1…...

vue3项目结合Echarts实现甘特图(可拖拽、选中等操作)

效果图: 图一:选中操作 图二:上下左右拖拽操作 本案例在echarts示例机场航班甘特图的基础上修改 封装ganttEcharts组件,测试数据 airport-schedule.jsonganttEcharts代码: 直接复制粘贴可测…...

Log4j2 插件的简单使用

代码: TestPlugin.java package com.chenjiacheng.webapp.plugins;import org.apache.logging.log4j.core.LogEvent; import org.apache.logging.log4j.core.config.plugins.Plugin; import org.apache.logging.log4j.core.lookup.StrLookup;/*** Created by chenjiacheng on …...

Linux之RPM和YUM命令

一、RPM命令 1、介绍 RPM(RedHat Package Manager).,RedHat软件包管理工具,类似windows里面的setup,exe是Liux这系列操作系统里而的打包安装工具。 RPMI包的名称格式: Apache-1.3.23-11.i386.rpm “apache’” 软件名称“1.3.23-11” 软件的版本号&am…...

读取硬件板子上的数据

SSCOM工具,先要安装一个插件 这样就可以读到设备数据...

Cesium 实例化潜入潜出

Cesium 实例化潜入潜出 1、WebGL Instance 的原理 狭义的的WebGL 中说使用 Instance, 一般指使用 glDrawArraysInstanced 用于实例化渲染的函数。它允许在一次绘制调用中渲染多个相同的几何体实例,而无需为每个实例发起单独的绘制调用。 Three.js 就是使用这种方…...

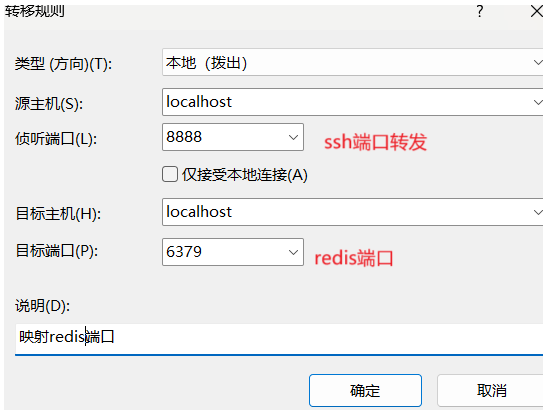

java引入jedis并且关于开放redis端口问题

博主主页: 码农派大星. 数据结构专栏:Java数据结构 数据库专栏:数据库 JavaEE专栏:JavaEE 软件测试专栏:软件测试 关注博主带你了解更多知识 目录 1. 引入jedis 编辑 2. 关于java客户端开放redis端口问题 3. 连接redis服务器 redis服务器在官网公开了使用的协议: resp…...

【人工智能】用Python实现情感分析:从简单词典到深度学习方法的演进

《Python OpenCV从菜鸟到高手》带你进入图像处理与计算机视觉的大门! 解锁Python编程的无限可能:《奇妙的Python》带你漫游代码世界 情感分析是自然语言处理(NLP)中的一个重要任务,其目的是通过分析文本内容,识别出其中的情感极性,如正面、负面或中性。随着技术的不断…...

关系型数据库的完整性和一致性

完整性 1.实体完整性 - 每一个实体都是独一无二的,没有冗余 --主键/唯一索引 2.参照完整性 - 外键 3.域完整性 - 存储的数据都是有效的数据 --数据类型/数据长度/非空约束/检查约束/ 检查约束: alter table tb_score add constraint ck_score_scmar…...

设计模式の命令访问者迭代器模式

文章目录 前言一、命令模式二、访问者模式三、迭代器模式 前言 本篇是关于设计模式中命令模式、访问者模式、以及迭代器模式的学习笔记。 一、命令模式 命令模式是一种行为型设计模式,其核心目的在于将命令的发送者和接受者解耦,提供一个中间层对命令进行…...

信息系统项目管理 -冲突管理

信息系统项目管理题 冲突管理: 项目管理信息系统包括()软件,用于监督资源的使用情况,协助确保合适的资源适时、适地的用于合适活动。 A资源管理或进度计划 BCRM系统 C采购系统或智能分析 DBOM系统 答案:A …...

Gmsh有限元网格剖分(Python)---点、直线、平面的移动

Gmsh有限元网格剖分(Python)—点、直线、平面的移动和旋转 最近在学习有限元的网格剖分算法,主要还是要参考老外的开源Gmsh库进行,写一些博客记录下学习过程,方便以后回忆嘞。 Gmsh的官方英文文档可以参考:gmsh.pdf 但咋就说&a…...

山景BP1048增加AT指令,实现单片机串口控制播放音乐(一)

1、设计目的 山景提供的SDK是蓝牙音箱demo,用户使用ADC按键或者IR遥控器,进行人机交互。然而现实很多场景,需要和单片机通信,不管是ADC按键或者IR接口都不适合和单片机通信。这里设计个AT指令用来和BP1048通信。AT指令如下图所示…...

SMMU软件指南SMMU编程之全局错误和最小配置

安全之安全(security)博客目录导读 目录 一、全局错误 二、最小配置 一、全局错误 与编程接口相关的全局错误会报告到适当的 SMMU_(*_)GERROR 寄存器,而不是通过基于内存的事件队列。这些错误通常是严重的,例如导致 SMMU 停止向前推进。例如…...

CPU条件下Pytorch、jupyter环境配置

一、创建虚拟环境 查看虚拟环境 conda env list 创建python虚拟环境 conda create -n minist python3.11 激活虚拟环境 conda activate minist 查看虚拟环境下有哪些包 pip list 二、安装pytorch 切换清华源 conda config --add channels https://mirrors.tuna.tsing…...

【自用】通信内网部署rzgxxt项目_01,后端pipeDemo部署(使用nssm.exe仿照nohup)

做完这些工作之后,不要忘记打开 Windows Server 的防火墙端口,8181、8081、8080、22、443、1521 做完这些工作之后,不要忘记打开 Windows Server 的防火墙端口,8181、8081、8080、22、443、1521 做完这些工作之后,不要…...

Ubuntu 安装实时内核指南

在运行需要高精度和低延迟响应的机器人驱动程序时,安装一个具备实时内核(Real-Time Kernel)的 Ubuntu 系统是至关重要的。若缺乏实时系统的支持,高频率的控制指令可能会导致机器人运动轨迹不流畅,甚至产生抖动现象。以…...

解锁AI编程新范式:Continue插件的颠覆性开发体验

解锁AI编程新范式:Continue插件的颠覆性开发体验 【免费下载链接】continue ⏩ Source-controlled AI checks, enforceable in CI. Powered by the open-source Continue CLI 项目地址: https://gitcode.com/GitHub_Trending/co/continue 你是否曾在深夜调试…...

LuckyLilliaBot架构解析:NTQQ OneBot API插件的深度技术实现指南

LuckyLilliaBot架构解析:NTQQ OneBot API插件的深度技术实现指南 【免费下载链接】LuckyLilliaBot NTQQ的OneBot API插件 项目地址: https://gitcode.com/gh_mirrors/li/LuckyLilliaBot LuckyLilliaBot是一款基于OneBot 11协议的开源QQ机器人框架,…...

)

深入解读XDMA驱动:从/dev节点看透RK3588与FPGA的PCIe数据流(H2C/C2H通道详解)

深入解读XDMA驱动:从/dev节点看透RK3588与FPGA的PCIe数据流(H2C/C2H通道详解) 当你在RK3588开发板上执行ls /dev/xdma0_*命令时,那些神秘的字符设备节点背后隐藏着一套精密的PCIe通信体系。作为连接ARM SoC与FPGA的高速数据通道&…...

:事务+视图+触发器+索引+三大范式+数据库优化+数据的导入导出)

MySQL(4):事务+视图+触发器+索引+三大范式+数据库优化+数据的导入导出

文章目录一、事务二、视图三、触发器四、索引五、关系型数据库三大范式六、Mysql数据库的优化七、数据的导入和导出一、事务 1.什么是事物? 将一组增删改查看成一个执行单元,要么全成功,要么有一个失败,数据库就会回滚ÿ…...

基于python的民宿预定管理系统设计与实现j470j

目录同行可拿货,招校园代理 ,本人源头供货商功能需求分析用户端功能房东端功能管理员端功能技术实现要点扩展功能建议项目技术支持源码获取详细视频演示 :文章底部获取博主联系方式!同行可合作同行可拿货,招校园代理 ,本人源头供货商 功能需求分析 民宿…...

Local SDXL-Turbo保姆级教程:导出为ONNX格式进一步优化推理速度

Local SDXL-Turbo保姆级教程:导出为ONNX格式进一步优化推理速度 1. 引言:为什么需要导出ONNX? 如果你已经体验过Local SDXL-Turbo那“打字即出图”的畅快感,可能会想:这速度已经很快了,还能不能再快一点&…...

告别手速焦虑:Python大麦网自动抢票脚本终极指南

告别手速焦虑:Python大麦网自动抢票脚本终极指南 【免费下载链接】Automatic_ticket_purchase 大麦网抢票脚本 项目地址: https://gitcode.com/GitHub_Trending/au/Automatic_ticket_purchase 还在为心仪演出门票秒光而烦恼吗?每次热门演唱会开票…...

)

别再死记硬背了!用eNSP模拟一个500人公司的真实网络(含VLAN、MSTP、VRRP完整配置)

从零构建500人企业网络:eNSP实战中的VLAN、MSTP与VRRP深度解析 当你第一次面对企业级网络规划时,是否曾被各种协议和配置弄得晕头转向?本文将以一个真实的500人企业网络为蓝本,带你用华为eNSP模拟器完成从需求分析到最终实现的完整…...

)

别再只改默认密码了!Nacos 1.x/2.x 生产环境安全加固保姆级清单(附漏洞自查脚本)

Nacos生产环境安全加固全指南:从基础配置到漏洞防御 在微服务架构盛行的今天,Nacos作为服务发现和配置管理的核心组件,其安全性直接影响整个系统的稳定性。许多团队在部署Nacos时往往只满足于修改默认密码,却忽视了完整的安全防护…...

MinerU智能文档理解镜像:财务报表自动识别实战体验

MinerU智能文档理解镜像:财务报表自动识别实战体验 1. 引言:财务文档处理的痛点与机遇 在财务工作中,我们经常需要处理各种格式的财务报表——PDF扫描件、Excel截图、纸质文档照片等。传统的手工录入方式不仅效率低下,还容易出错…...