Verilog学习方法—基础入门篇(一)

前言:

在FPGA开发中,Verilog HDL(硬件描述语言)是工程师必须掌握的一项基础技能。它不仅用于描述数字电路,还广泛应用于FPGA的逻辑设计与验证。对于初学者来说,掌握Verilog的核心概念和基本语法,是深入FPGA开发的第一步。本篇文章将从Verilog基础入门的角度,帮助你快速建立学习框架,逐步掌握Verilog的使用方法。

1. 了解Verilog的基本概念

1.1 什么是Verilog?

Verilog HDL(Verilog Hardware Description Language)是一种用于描述和模拟数字电路的硬件描述语言(HDL)。它最初由Gateway Design Automation公司开发,并在1995年成为IEEE标准(IEEE 1364)。Verilog既可以用于设计(描述硬件结构),也可以用于仿真(测试逻辑功能),在FPGA开发中占据重要地位。

1.2 Verilog vs. 其他语言

许多初学者会将Verilog与软件编程语言(如C/C++、Python)进行比较,然而它们的本质不同:

- C/C++等编程语言是用于描述指令执行的过程(顺序执行)。

- Verilog HDL用于描述硬件的结构和行为(并行执行)。

此外,Verilog是事件驱动的语言,它依赖时序、时钟、触发条件等概念,这也是与软件编程的一个重要区别。

2. Verilog的基本语法

学习Verilog时,首先要掌握模块(module)、端口(ports)、数据类型、运算符、过程块等基本语法。

2.1 模块(Module)

Verilog的基本单位是模块(module),每个模块可以看作是一个功能单元,类似于C语言的函数。模块包含输入输出端口、逻辑描述等。

示例:基本的Verilog模块

module and_gate (input a, input b, output y);assign y = a & b; // 按位与操作

endmodule

module和endmodule关键字用于定义一个模块。input和output定义输入、输出信号。assign语句用于连续赋值,它适用于组合逻辑电路。

2.2 数据类型

Verilog的数据类型主要分为网线类型(wire)和寄存器类型(reg):

- wire:表示组合逻辑电路中的信号连接,不存储值。

- reg:用于存储数据,通常在时序逻辑电路中使用。

示例:

wire a, b, y; // 定义wire类型变量

reg clk, rst; // 定义reg类型变量

2.3 过程块(always块)

在时序逻辑电路中,always 语句用于描述触发逻辑,如时钟驱动的寄存器。

示例:D 触发器

module d_flipflop (input clk, input d, output reg q);always @(posedge clk) // 在时钟上升沿触发q <= d; // 非阻塞赋值

endmodule

always @(posedge clk):在时钟上升沿触发代码块。<=非阻塞赋值,表示时序逻辑。

3. Verilog编写基本流程

在实际项目中,Verilog代码的开发一般遵循以下流程:

- 编写Verilog代码(如模块、信号连接等)。

- 功能仿真(使用仿真工具验证设计正确性,如ModelSim、Vivado Simulator)。

- 综合(Synthesis)(将Verilog代码转换为FPGA硬件电路)。

- 实现(Implementation)(FPGA工具优化和布局布线)。

- 下载到FPGA(烧录bit文件到FPGA板子)。

对于初学者来说,可以先使用仿真工具,如ModelSim或Vivado,学习如何调试Verilog代码。

4. 入门学习建议

(1)掌握基本语法:

从最基础的module、wire、reg等概念入手,编写简单组合逻辑和时序逻辑电路。

(2)从简单电路开始练习:

可以从逻辑门(AND、OR、XOR等)、多路选择器、计数器等常见模块开始练习。

(3)学会使用仿真工具:

初学者可以使用Vivado或Quartus等FPGA开发环境,学习如何编写**测试激励(testbench)**进行仿真。

(4)阅读官方文档和经典书籍:

推荐阅读《Verilog HDL 入门与实践》、《FPGA设计实战》等书籍,提高对Verilog的理解。

5. 结语

Verilog HDL是FPGA开发的基础语言,掌握它需要耐心和实践。本篇文章介绍了Verilog的基本概念、语法结构以及学习方法,希望能帮助初学者快速入门。在接下来的文章中,我们将深入探讨Verilog的模块化设计、时序逻辑描述以及测试方法,敬请关注!

如果你对FPGA开发和Verilog学习感兴趣,欢迎关注宸极教育,我们提供系统的FPGA课程,帮助你从零开始掌握FPGA开发技能!🚀🚀🚀

相关文章:

Verilog学习方法—基础入门篇(一)

前言: 在FPGA开发中,Verilog HDL(硬件描述语言)是工程师必须掌握的一项基础技能。它不仅用于描述数字电路,还广泛应用于FPGA的逻辑设计与验证。对于初学者来说,掌握Verilog的核心概念和基本语法࿰…...

本地jar包添加到 maven

进入到 你的 maven bin文件夹下 执行cmd ,然后执行命令 mvn install:install-file -Dfilepath/to/your/artifact.jar -DgroupIdyour.group.id -DartifactIdyour-artifact-id -Dversion1.0 -Dpackagingjar 替换path/to/your/artifact.jar为你的JAR文件路径…...

C# Unity 唐老狮 No.6 模拟面试题

本文章不作任何商业用途 仅作学习与交流 安利唐老狮与其他老师合作的网站,内有大量免费资源和优质付费资源,我入门就是看唐老师的课程 打好坚实的基础非常非常重要: 全部 - 游习堂 - 唐老狮创立的游戏开发在线学习平台 - Powered By EduSoho 如果你发现了文章内特殊的字体格式,…...

项目工坊 | Python驱动淘宝信息爬虫

目录 前言 1 完整代码 2 代码解读 2.1 导入模块 2.2 定义 TaoBao 类 2.3 search_infor_price_from_web 方法 2.3.1 获取下载路径 2.3.2 设置浏览器选项 2.3.3 反爬虫处理 2.3.4 启动浏览器 2.3.5 修改浏览器属性 2.3.6 设置下载行为 2.3.7 打开淘宝登录页面 2.3.…...

Java8-Stream流介绍和使用案例

Java 8 引入了 Stream API,它提供了一种高效且声明式的方式来处理集合数据。Stream 的核心思想是将数据的操作分为中间操作(Intermediate Operations)和终端操作(Terminal Operations),并通过流水线&#x…...

的参数,“zh_CN.UTF-8“, “chs“, “chinese-simplified“的差异。)

setlocale()的参数,“zh_CN.UTF-8“, “chs“, “chinese-simplified“的差异。

在 C/C 中,setlocale() 函数的参数 zh_CN.UTF-8、chs 和 chinese-simplified 均用于设置中文简体环境,但它们的语义、平台支持和编码行为存在显著差异: 1. zh_CN.UTF-8(推荐) 含义: zh_CN: 中文&…...

docker 安装达梦数据库(离线)

docker安装达梦数据库,官网上已经下载不了docker版本的了,下面可通过百度网盘下载 通过网盘分享的文件:dm8_20240715_x86_rh6_rq_single.tar.zip 链接: https://pan.baidu.com/s/1_ejcs_bRLZpICf69mPdK2w?pwdszj9 提取码: szj9 上传到服务…...

FastGPT 引申:如何基于 LLM 判断知识库的好坏

文章目录 如何基于 LLM 判断知识库的好坏方法概述示例 Prompt声明抽取器 Prompt声明检查器 Prompt 判断机制总结 下面介绍如何基于 LLM 判断知识库的好坏,并展示了如何利用声明抽取器和声明检查器这两个 prompt 构建评价体系。 如何基于 LLM 判断知识库的好坏 在知…...

关于2023新版PyCharm的使用

考虑到大家AI编程的需要,建议大家安装新版Python解释器和新版PyCharm,下载地址都可以官网进行: Python:Download Python | Python.org(可以根据需要自行选择,建议选择3.11,保持交流版本一致&am…...

Leetcode 112: 路径总和

Leetcode 112: 路径总和 问题描述: 给定一个二叉树的根节点 root 和一个目标和 targetSum,判断是否存在从根节点到叶子节点的路径,使路径上所有节点的值相加等于目标和 targetSum。 适合面试的解法:递归 解法特点: …...

华为云IAM 用户名和IAM ID

账号 当您首次使用华为云时注册的账号,该账号是您的华为云资源归属、资源使用计费的主体,对其所拥有的资源及云服务具有完全的访问权限,可以重置用户密码、分配用户权限等。账号统一接收所有IAM用户进行资源操作时产生的费用账单。 账号不能…...

Compose Multiplatform+Kotlin Multiplatfrom 第四弹跨平台

文章目录 引言功能效果开发准备依赖使用gradle依赖库MVIFlow设计富文本显示 总结 引言 Compose Multiplatformkotlin Multiplatfrom 今天已经到compose v1.7.3,从界面UI框架上实战开发看,很多api都去掉实验性注解,表示稳定使用了!…...

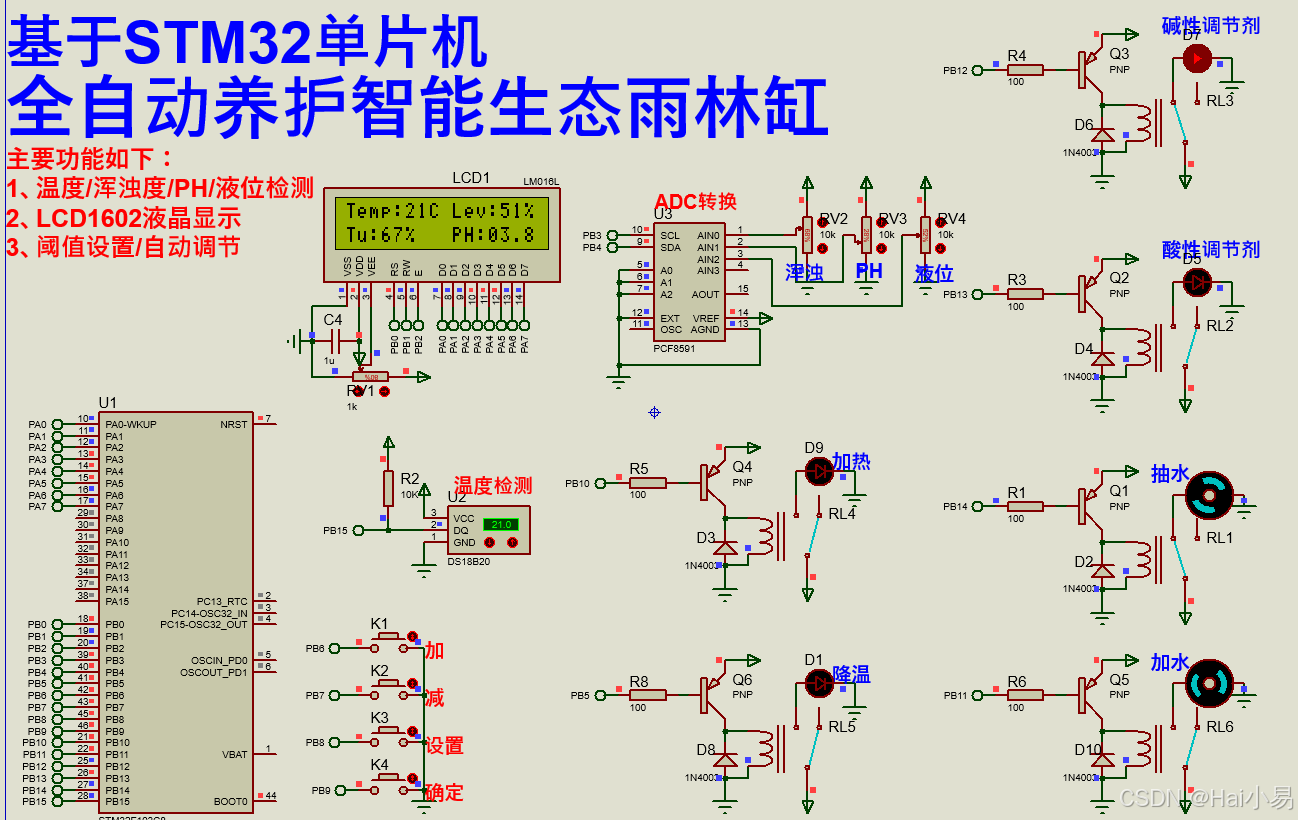

【Proteus仿真】【STM32单片机】全自动养护智能生态雨林缸

文章目录 一、功能简介二、软件设计三、实验现象联系作者 一、功能简介 本项目使用Proteus8仿真STM32单片机控制器,使用按键、LCD1602液晶、DS18B20模块、PCF8591 ADC、浑浊传感器、PH传感器、液位传感器、继电器、水泵、酸碱调节剂、加热降温装置等。 主要功能&am…...

GBT32960 协议编解码器的设计与实现

GBT32960 协议编解码器的设计与实现 引言 在车联网领域,GBT32960 是一个重要的国家标准协议,用于新能源汽车与监控平台之间的数据交互。本文将详细介绍如何使用 Rust 实现一个高效可靠的 GBT32960 协议编解码器。 整体架构 编解码器的核心由三个主要组…...

SolidWorks 转 PDF3D 技术详解

在现代工程设计与制造流程中,不同软件间的数据交互与格式转换至关重要。将 SolidWorks 模型转换为 PDF3D 格式,能有效解决模型展示、数据共享以及跨平台协作等问题。本文将深入探讨 SolidWorks 转 PDF3D 的技术原理、操作流程及相关注意事项,…...

OpenMCU(二):GD32E23xx FreeRTOS移植

概述 本文主要描述了GD32E230移植FreeRTOS的简要步骤。移植描述过程中,忽略了Keil软件的部分使用技巧。默认读者熟练使用Keil软件。本文的描述是基于OpenMCU_FreeRTOS这个工程,该工程已经下载放好了移植GD32E230 FreeRTOS的所有文件 OpenMCU_FreeRTOS工程…...

题解ABCDEFG)

Codeforces Round 835 (Div. 4)题解ABCDEFG

Problem - A - Codeforces 题意:你有 t 组数据,每组有两两不同的三个数 a,b,c,现在需要你求出他们的中位数。 思路:模拟即可 // Code Start Here int t;cin >> t;while(t--){vector<int> a(3);for(int i 0;i<3…...

NO1.C++语言基础|四种智能指针|内存分配情况|指针传擦和引用传参|const和static|c和c++的区别

1. 说⼀下你理解的 C 中的四种智能指针 智能指针的作用是管理指针,可以避免内存泄漏的发生。 智能指针就是一个类,当超出了类的作用域时,就会调用析构函数,这时就会自动释放资源。 所以智能指针作用的原理就是在函数结束时自动释…...

SQLite Having 子句详解

SQLite Having 子句详解 引言 SQLite 是一款轻量级的数据库管理系统,广泛应用于移动设备、嵌入式系统和各种桌面应用程序。在 SQL 查询中,HAVING 子句是用于过滤结果集的关键部分,尤其是在使用 GROUP BY 子句进行分组操作时。本文将详细解析 SQLite 中的 HAVING 子句,包括…...

Python数据分析面试题及参考答案

目录 处理 DataFrame 中多列缺失值的 5 种方法 批量替换指定列中的异常值为中位数 使用正则表达式清洗电话号码格式 合并两个存在部分重叠列的 DataFrame 将非结构化 JSON 日志转换为结构化表格 处理日期列中的多种非标准格式(如 "2023 年 12 月 / 05 日") 识…...

的3D视觉原理与应用)

从‘看见’到‘看懂’:手把手拆解RGB-D摄像头(如Intel Realsense)的3D视觉原理与应用

从‘看见’到‘看懂’:手把手拆解RGB-D摄像头的3D视觉原理与应用 当你第一次看到RGB-D摄像头生成的彩色点云在屏幕上旋转时,那种将现实世界数字化的震撼感令人难忘。但真正让这种设备发挥价值的,是理解它如何将光信号转化为三维坐标的完整技术…...

在自动化测试场景中利用Taotoken实现多模型API调用与成本控制

🚀 告别海外账号与网络限制!稳定直连全球优质大模型,限时半价接入中。 👉 点击领取海量免费额度 在自动化测试场景中利用Taotoken实现多模型API调用与成本控制 对于工程团队而言,自动化测试是保障软件质量的关键环节。…...

)

别再只用ARIMA了!用Facebook Prophet快速搞定业务时间序列预测(附Python实战代码)

用Facebook Prophet三行代码完成高精度业务预测:电商场景实战指南 当市场部门的同事又在周五下午5点发来"下周销售预测急用"的邮件时,你是否还在为ARIMA模型的参数调优焦头烂额?时间序列预测本应是数据科学中最具商业价值的技能之一…...

惠普战66内存硬盘升级全攻略:从选条到安装,手把手教你避开新手常踩的坑

惠普战66内存硬盘升级全攻略:从选条到安装,手把手教你避开新手常踩的坑 当你发现电脑运行速度变慢,多开几个网页就开始卡顿,或是存储空间频频告急时,升级内存和硬盘可能是最具性价比的解决方案。作为惠普战66系列的用户…...

告别Hello World:用Scala REPL在Ubuntu上实战计算级数,附完整代码与权限避坑

从Hello World到实战:用Scala REPL在Ubuntu上高效计算级数 当Java开发者第一次接触Scala时,往往会被其函数式编程范式和简洁语法所吸引。但真正要将其应用于实际问题解决时,却常因环境配置和实战经验不足而却步。本文将带你跳过传统语法学习阶…...

从平面到立体:用ImageToSTL将照片变为可触摸的3D模型

从平面到立体:用ImageToSTL将照片变为可触摸的3D模型 【免费下载链接】ImageToSTL This tool allows you to easily convert any image into a 3D print-ready STL model. The surface of the model will display the image when illuminated from the left side. …...

中国科学技术大学学位论文LaTeX模板:5个高效排版技巧与终极指南

中国科学技术大学学位论文LaTeX模板:5个高效排版技巧与终极指南 【免费下载链接】ustcthesis LaTeX template for USTC thesis 项目地址: https://gitcode.com/gh_mirrors/us/ustcthesis 如果你正在准备中国科学技术大学的学位论文,那么ustcthesi…...

3步搞定Football Manager面部包管理:NewGAN-Manager完全指南

3步搞定Football Manager面部包管理:NewGAN-Manager完全指南 【免费下载链接】NewGAN-Manager A tool to generate and manage xml configs for the Newgen Facepack. 项目地址: https://gitcode.com/gh_mirrors/ne/NewGAN-Manager 你是否厌倦了在Football M…...

项目推荐:深入理解与掌握正交频分复用技术)

OFDM仿真(Matlab)项目推荐:深入理解与掌握正交频分复用技术

OFDM仿真(Matlab)项目推荐:深入理解与掌握正交频分复用技术 【下载地址】OFDM仿真matlab完整可运行 本资源提供了一个完整的OFDM(正交频分复用)仿真代码,基于Matlab平台开发。该仿真代码包含了OFDM系统中的多个关键模块࿰…...

给项目选YOLO模型别再纠结了:从参数量、训练曲线到mAP,手把手教你根据数据集做决策

YOLO模型选型实战指南:从参数解析到场景适配的决策方法论 在目标检测领域,YOLO系列模型凭借其出色的实时性能,已成为工业界和学术界的首选架构之一。然而,面对从YOLOv5到YOLOv9的多个版本迭代,以及每个版本中不同规模的…...