初学Verilog语言基础笔记整理(实例点灯代码分析)持续更新~

实例:点灯学习

一、Verilog语法学习

1. 参考文章

刚接触

Verilog,作为一个硬件小白,只能尝试着去理解,文章未完…持续更新。

参考博客文章:

- Verilog语言入门学习(1)

- Verilog语法

- 【

Verilog】一文带你了解Verilog基础语法 - 子墨祭的文章 - 知乎 - 关于Verilog中的几种赋值语句

这里抄点,那里扣点,整理了一下,感谢以上各位作者。具体的实例项目是同事给的,他让我学着编出个流水灯,这不要我的命嘛,慢慢学吧。

你还可以在哪里看到这篇文章:

- 知乎

2. Verilog模块

Verilog的基本设计单元是“模块”。一个模块是由两部分组成的,一部分描述接口,另一部分描述逻辑功能,即定义输入是如何影响输出的。下面举例说明:

可以看到模块由关键字module....endmodule 确定。

module 模块名(接口信号);

//信号声明

//功能描述

endmodule

要求: 1. 模块名具有意义;2. 一个.v文件只有一个模块。

3. Verilog语法

Verilog是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

Verilog和C的区别:

Verilog是硬件描述语言,编译下载到FPGA之后,会生成电路,所以Verilog全部是并行处理与运行的C语言是软件语言,编译下载到单片机CPU之后,还是软件指令,而不会根据代码生成相应的硬件电路,而单片机CPU处理软件指令需要取址、译码、执行,是串行执行的。

**可综合描述:**综合tool能够Verilog描述转化(complie)成基本的数字电路底层cell(与或非gate,寄存器等)的描述。

assign y = a & b;

**不可综合描述:**综合tool不能把Verilog描述转换为基本的数字电路底层cell的描述。

$display("hello word.\n")

Verilog设计仿真与实现:通过EDA TOOL,可以在计算机上对Verilog设计的功能进行仿真。

数字电路设计方法学:

Bottom-Up:从底层cell开始,逐渐往上加功能;top-Down:从底层结构,协议算法开始,向下逐步划分功能模块;再细分各功能模块与IO。

目前,基于Verilog的数字电路通常使用TOP-Down的设计方法。因为数字IP/IC的规模很大,需要先抽象思维再细化;

Verilog给数字电路的设计的抽象思维提供了一种设计语言,但是:数字设计和软件设计不同的,需要Think in Hardware,写代码前先设计电路结构。Verilog的功能描述:

Top-Dowan描述数字电路功能:通过模块module的层次化设计,实现一个复杂的数字逻辑功能

Verilog逻辑值:

逻辑电路中有四种值,即四种状态:

- 逻辑0:表示低电平,对应电路的

GND; - 逻辑1:表示高电平,对应电路的

VCC; - 逻辑X:表示未知,有可能是高电平,也有可能是低电平;

- 逻辑Z:表示高组态,外部没有激励信号是一个悬空状态;

Verilog的数字进制

Verilog数字进制格式包括二进制、八进制、十进制和十六进制,一般常用的为二进制、十进制和十六进制。

- 二进制表示如下:

4'b0101表示4位二进制数字0101 - 十进制表示如下:

4'd2表示4位十进制数字2 - 十六进制表示如下:

4'ha表示4位十六进制数字a

当没有指定数字的位宽与进制时,默认为32位的十进制,比如100,实际上表示的值为

32'd100

4. Verilog语法详细介绍

(1)标识符:

用于定义code中的各种名字,比如:信号,module,define,parameter;

- 标识符由:字符,数字,下划线组成;

- 首字母必须是字母或者下划线;

- 标识符是区分大小写的;

- 信号名字与信号功能相对应;

不建议大小写混合使用,普通内部信号建议全部小写,参数定义建议大写

- 用有意义的有效的名字如

sum、cpu_addr等- 用下划线区分词语组合,如

cpu_addr- 采用一些前缀或后缀

- 比如:时钟采用

clk前缀:clk_50m,clk_cpu;低电平采用_n后缀:enable_n- 统一缩写,如全局复位信号

rst- 同一信号在不同层次保持一致,如同一时钟信号必须在各模块保持一致。

- 自定义的标识符不能与保留字(关键字)同名

- 参数统一采用大写,如定义参数使用

SIZE

(2)关键字

优先记录常用关键字:

| 关键字 | 含义 |

|---|---|

module | 模块开始定义 |

input | 输入端口定义 |

output | 输出端口定义 |

inout | 双向端口定义 |

parameter | 信号的参数定义 |

wire | wire信号定义 |

reg | reg信号定义 |

| always | 产生reg信号语句的关键字 |

assign | 产生wire信号语句的关键字 |

begin | 语句的起始标志 |

end | 语句的结束标志 |

posedge、negedge | 时序电路的标志 |

case | Case语句起始标记 |

default | Case语句的默认分支标志 |

endcase | Case语句结束标志 |

if | if/else语句标志 |

else | if/else语句标记 |

for | for语句标记 |

endmodule | 模块结束定义 |

(3)注释:

-

注释一行:以//开始,到行末;

-

注释多行:以

/*开始,到*/为止的所有内容;

(4)数据类型:

主要有三大类数据类型,

- 寄存器类型;

- 线网类型;

- 参数类型;

线性数据:用于连续赋值语句(assign)描述组合逻辑或者module间的信号连接线;

1) 寄存器类型

寄存器类型表示一个抽象的数据存储单元,它只能在always语句和initial语句中被赋值,并且它的值从一个赋值到另一个赋值过程中被保存下来。

如果语句描述的是时序逻辑,即always语句带有时钟信号,则该寄存器变量对应为寄存器;如果该过程语句描述的是组合逻辑,即always语句不带有时钟信号则该寄存器变量对应为硬件连线

寄存器类型的缺省值是x(未知状态)。

寄存器数据类型有很多种,如reg、integer、real等,其中最常用的就是reg类型

reg [31:0] delay_cnt; // 延时计数器

reg key_flag; // 按键标志wire [3:0] din;

reg [3:0] d0; //4bit

reg d1;//1bit

initial begin //过程赋值语句d1 = 0;#10;d1 = 1;

end

always(posedge clk)begin //clk端一般就是寄存器if(d1) d0 <= din;

end

2)线网类型

线网表示Verilog结构化元件间的物理连线。

值由驱动元件的值决定,例如连续赋值或门的输出。

如果没有驱动元件连接到线网,线网的缺省值为z(高阻态)。

线网类型,如tri和wire等,其中最常用的就是wire类型,它的使用方法如下:

wire data_en; //数据使能信号

wire [7:0] data;//数据wire a;//1bit位宽

wire [3:0] b; //4bit

wire [7:0] c;//8bit

assign a = 1'b0;//连续赋值语句

assign c = 8'h5a;//8bit的十六进制数

//tri0、tri1:带下拉、上拉电阻的特性,没有驱动时,会由默认的值为0/1,一般综合代码不用

tri0 s0;

tri1 [20:0] s1;

3)参数类型

参数其实就是一个常量,常被用于定义状态机的状态、数据位宽和延迟大小等

可以在编译时修改参数的值,因此又常被用于一些参数可调的模块中,使用户在实例化模块时,可以根据需要配置参数。

在定义参数时,可以一次定义多个+参数,参数与参数之间需要用逗号隔开。

要注意的是参数的定义是局部的,只在当前模块中有效。

parameter DATA_WIDTH = 8;//数据位宽为8

(5)Verilog运算符

1)算术运算符

+

-

*

/

%

Verilog实现乘除比较浪费组合逻辑资源,尤其是除法。一般2的指数次幂的乘除法使用移位运算来完成运算.

非2的指数次幂的乘除法一般是调用现成的IP,QUARTUS/ISE等工具软件会有提供,不过这些工具软件提供的IP也是由最底层的组合逻辑(与或非门等)搭建而成的。

2)关系运算符

>

<

>=

<=

==

!=

用来进行条件判断,在进行关系运算符时,如果声明的关系是假的,则返回值是0,如果声明的关系是真的,则返回值是1;

所有的关系运算符有着相同的优先级别,关系运算符的优先级别低于算术运算符的优先级别。

3)逻辑运算符

!

&&

||

连接多个关系表达式,可实现更加复杂的判断,一般不单独使用,都需要配合具体语句来实现完整意思。

4)条件运算符

?

:

从两个输入中选择一个作为输出的条件选择结构,功能等同于always中的if-else语句。

5)位运算符

~

&

|

^

直接对应数字逻辑中的与、或、非门等逻辑门

位运算符一般用在信号赋值上。

6)移位运算符

<<

>>

移位运算符包括左移位运算符和右移位运算符,这两种移位运算符都用0来填补移出的空位。

一般使用左移位运算代替乘法,右移位运算代替除法,但是只能表示2的指数次幂的乘除法。

7)拼接运算符

{a,b}

可以把两个或多个信号的某些位拼接起来进行运算操作

5. 阻塞赋值(Blocking)和非阻塞赋值(Non-Blocking)

(1)阻塞赋值

在一个always块中,后面的语句会受到前语句的影响,具体来说,在同一个always中,一条阻塞赋值语句如果没有执行结束,那么该语句后面的语句就不能被执行,即被“阻塞”。

也就是说always块内的语句是一种顺序关系

符号“=”用于阻塞的赋值(如:b=a;),阻塞赋值“=”在begin和end之间的语句是顺序执行,属于串行语句。其后面的赋值语句从概念上来讲是在前面一条语句赋值完成之后才执行的。

(2)非阻塞赋值

符号"<="用于非阻塞赋值(如:b<=a;),非阻塞赋值是由时钟节拍决定,在时钟上升到来时,执行赋值语句右边,然后将begin-end之间的所有赋值语句同时赋值到赋值语句的左边。

begin-end之间的所有语句,一起执行,且是个时钟只执行一次,属于并行执行语句。

非阻塞赋值的操作过程可以看作两个步骤:

- 赋值开始的时候,计算

RHS(等号右边的表达式); - 赋值结束的时候,更新

LHS(等号左边的表达式)。

非阻塞的概念是指,在计算非阻塞赋值的RHS以及LHS期间,允许其他的非阻塞赋值语句同时计算RHS和更新LHS。

6. assign和always的区别

assign语句使用时不能带时钟;always语句可以带时钟,也可以不带时钟;- 在

always不带时钟是,逻辑功能和assign完全一致,都是只产生组合逻辑。 - 比较简单的组合逻辑推荐使用

assign语句,比较复杂的组合逻辑推荐使用always语句。

(1)带时钟和不带时钟的always

always语句可以带时钟,也可以不带时钟。

- 在

always不带时钟时,逻辑功能和assign完全一致,虽然产生的信号定义为reg类型,但是该语句产生的还是组合逻辑; - 在

always带时钟信号时,这个逻辑语句才能产生真正的寄存器。

(2)latch

latch指锁存器,是一种对脉冲点平敏感的存储单元电路

锁存器和寄存器都是基本存储单元,锁存器是电平触发的存储器,寄存器是边沿触发的存储器。

两者的基本功能是一样的,都可以存储数据。

锁存器是组合逻辑产生的,而寄存器是在时序电路中使用,由时钟触发产生的。

latch的主要危害是产生毛刺(glitch),这种毛刺对一级电路是很危险的。并且其隐蔽性很强,不易查出。

在设计中,应尽量避免

latch的使用。

代码里出现latch的两个原因是在组合逻辑中,if或者case语句不完整的描述,比如if缺少else分支,case缺少default分支,导致代码在综合过程中出现了latch。解决办法就是if必须带else分支,case必须带default分支。

只有不带时钟的always语句if语句或者case语句不完整才会产生latch,带时钟的语句if或者case语句不完整描述不会产生latch。

7. 状态机

Verilog是硬件描述语言,硬件电路是并行执行的,当需要按照流程或者步骤来完成某个功能是,代码中通常会使用很多个if嵌套语句来实现,这样就增加了代码的复杂度,以及降低了代码的可读性,这个时候就可以使用状态机来编写代码。

状态机相当于一个控制器,它将一项功能的完成分解为若干步,每一步对应二进制的一个状态,通过预先设计的顺序在各状态之间进行转换,状态转换的过程就是实现逻辑功能的过程。

状态机,全程是有限状态机(Finite State Machine,缩写为FSM),是一种在有限状态之间按一定规律转换的时序电路,可以认为是组合逻辑和时序逻辑的一种组合。状态机通过控制各个状态的跳转来控制流程,使得整个代码看上去更加清晰易懂,在控制复杂流程的时候,状态机优势明显,因此基本上都会用到状态机,如SDRAM控制器等。

根据状态机的输出是否与输入条件相关,可将状态机分为两大类,即摩尔(Moore)状态机和米勒(Mealy)型状态机

Mealy状态机:组合逻辑的输出不仅取决于当前状态,还取决于输入状态

Moore状态机:组合逻辑的输出只取决于当前状态

(1)三段式状态机

根据状态机的实际写法,状态机还可以分为一段式、和二段式和三段式状态机。

- 一段式:整个状态机写到一个

always模块里面,在该模块中即描述状态转移,又描述状态的输入和输出。

不推荐,一般都会要求把组合逻辑和时序逻辑分开,组合逻辑和时序逻辑混合在一起不利于代码维护和修改

- 二段式:用两个

always模块来描述状态机,其中一个always模块采用同步时序描述状态转移;另一个模块采用组合逻辑判断状态转移条件,描述状态转移规律以及输出,需要定义两个状态,现态和次态,然后通过现态和次态的转换来实现时序逻辑。 - 三段式:在两个

always模块描述方法基础上,使用三个always模块,一个always模块采用同步时序描述状态转移,一个always采用组合逻辑判断状态转移条件,描述状态转移规律,另一个always模块描述状态输出(可以用组合电路输出,也可以时序电路输出)。- 三段式状态机的基本格式是:

- 第一个

always语句实现同步状态跳转; - 第二个

always语句采用组合逻辑判断状态转移条件; - 第三个

always语句描述状态输出(可以用组合电路输出,也可以时序电路输出)。

- 第一个

- 三段式状态机的基本格式是:

8. 模块化设计

划分模块的基本原则是子模块功能相对独立、模块内部联系尽量紧密、模块间的连接尽量简单。

在进行模块化设计中,对于复杂的数字系统,我们一般采用自顶向下的设计方式。可以把系统划分成几个功能模块,每个功能模块再划分成下一层的子模块;每个模块的设计对应一个module,一个module设计成一个Verilog程序文件。因此,对一个系统的顶层模块,我们采用结构化的设计,即顶层模块分别调用了各个功能模块。

FPGA逻辑设计中通常是一个大的模块中包含了一个或多个功能子模块,Verilog通过模块调用或称为模块实例化的方式来实现这些子模块与高层模块的连接,有利于简化每一个模块的代码,易于维护和修改。

如果子模块内部使用parameter定义了一些参数,Verilog也支持对参数的例化(也叫参数的传递),即顶层模块可以通过例化参数来修改子模块内定义的参数。

子模块名是指被例化模块的模块名,而例化模块名相当于标识,当例化多个相同模块时,可以通过例化名来识别哪一个例化,一般命名为“u_”+“子模块名”

参数的例化,参数的例化是在模块例化的基础上,增加了对参数的信号定义

// 例子

time_count #(.MAX_NUM (TIME_SHOW) // 参数例化

)u_time_count(.clk (sys_clk),.rst_n (sys_rst_n), // 信号例化.flag (add_flag)

);

9. Verilog的编程规范

工程的组织形式一般包括如下几个部分,分别是doc、par、rtl和sim四个部分

doc:一般存放工程相关的文档,包括该项目用到的datasheet(数据手册)、设计方案等。par:主要存放工程文件和使用到的一些IP文件rtl:主要存放工程的rtl代码,是工程的核心,文件名与module名称应当一致,建议按照模块的层次分开存放sim:主要存放工程的仿真代码,复杂的工程里面,仿真也是不可或缺的部分,可以极大减少调试的工作量。

(1)文件头声明

每一个Verilog文件的开头,都必须有一段声明的文字。包含文件的版权、作者、创建日期,以及内容简介等等

//*************************************Copyright(c)*******************//

// FileName:

// Last modified Date:

// Last Version:

// Descriptions:

//*******************************************************************//

(2)输入输出定义

module led(input sys_clk, // 系统时钟input sys_rst_n , // 系统复位output reg [3:0] led // 4位LED灯

);

- 一行只定义一个信号

- 信号全部对齐

- 同一组的信号放在一起

(3)parameter定义

module中的parameter声明,不建议随处乱放,将parameter定义放在紧跟着module的输入输出定义之后- parameter等常量命名全部使用大写

(4)wire/reg定义

一个module中的wire/reg变量声明需要集中放在一起,不建议随处乱放

- 将

reg与wire的定义放在紧跟着parameter之后 - 建议具有相同功能的信号集中放在一起

- 信号需要对齐,

reg和位宽需要空2格,位宽和信号名字至少空四格 - 位宽使用降序描述,

[6:0] - 时钟使用前缀

clk,复位使用后缀rst - 一行只定义一个信号

(5)信号命名

- 内部信号不要使用大写,也不要使用大小写混合,建议全部使用小写

- 模块名字使用小写

- 异步信号,使用

_a作为信号后缀

(6)always块

- 一个

always需要配一个begin和end always前面需要有注释- 一个

always和下一个always空一行即可,不要空多行 - 时序逻辑使用非阻塞赋值

(7)assign块

assign的逻辑不能太复杂,否则易读性不好assign前面需要有注释- 组合逻辑使用阻塞赋值

(8)空格 和 TAB

- 由于不同的解释器对于

TAB翻译不一致,所以建议不使用TAB,全部使用空格

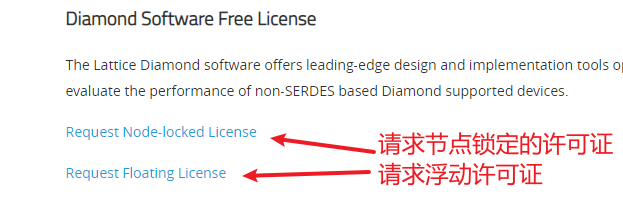

二、环境Lattice Dimond环境的搭建

-

从

Lattice的官网下载Dimond,下一步下一步安装; -

获取电脑的

MAC地址,注意是有线网卡的MAC地址,不能是无线的; -

在官网申请免费的证书,这里有问题,官网不会跳出来,所以是请同事帮忙生成的;

-

打开软件添加证书文件,即可。

-

Lattice官网链接

-

证书申请网址

(有的会跳出来什么联系管理员,我这里是把IP改为马来西亚打开网址的)

填写物理网卡MAC地址质料:

新建工程项目:

选择芯片,我的板子上的芯片是:

生成项目文件夹:

添加Verilog文件;

这样就可以编写Verilog代码了。

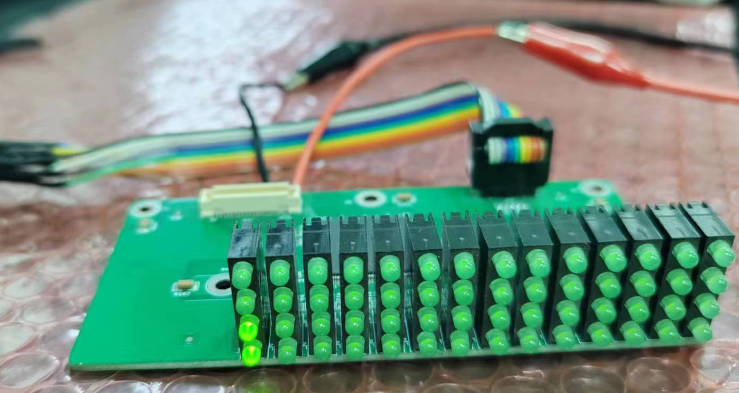

三、点灯实例分析

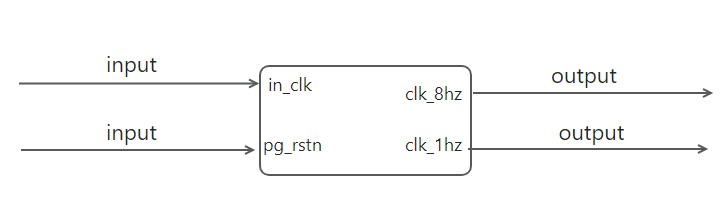

同事给出的一段实例,能够点亮两个灯;

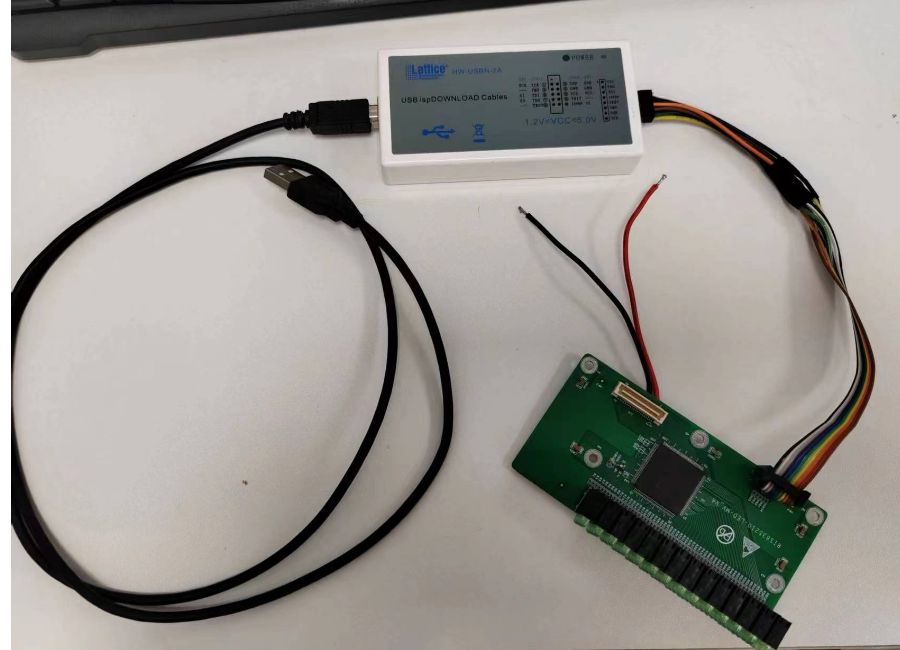

实例环境硬件如下:

- 电脑

- 可调电源

module clk_div

(

in_clk,

clk_8hz,

clk_1hz,

pg_rstn

);input in_clk;

output clk_8hz;

output clk_1hz;

input pg_rstn; reg [4:0] count0_r;

reg [8:0] count1_r;

reg [9:0] count2_r;reg div0_clk;

reg div1_clk;

reg div2_clk;wire clk_1hz;

wire clk_8hz;assign clk_1hz = count2_r[9];

assign clk_8hz = count2_r[6];always @(posedge in_clk or negedge pg_rstn) //25M--1M

beginif (!pg_rstn)begindiv0_clk<= 1'b1;count0_r <= 5'b0; endelse if (count0_r==5'b11001)begindiv0_clk<=1'b1; count0_r<=5'b0;end elsebegincount0_r<=count0_r+1'b1;div0_clk<= 1'b0; end

endalways @(posedge div0_clk or negedge pg_rstn) //1M--1k

beginif (!pg_rstn)begincount1_r <= 9'b0;div1_clk <= 1'b0;endelse if (count1_r==9'h1ff)begindiv1_clk<=~div1_clk; count1_r<=9'h0;endelsecount1_r<=count1_r+1'b1;

endalways @(posedge div1_clk or negedge pg_rstn) //1k--1Hz

beginif (!pg_rstn)begincount2_r <= 10'b0;endelse if (count2_r==10'h3ff)begin count2_r <= 10'b0; endelsebegincount2_r <= count2_r+1'b1;end

endOSCH #("10.23") osc_int (.STDBY(1'b0),.OSC(clk_i),.SEDSTDBY());endmodule

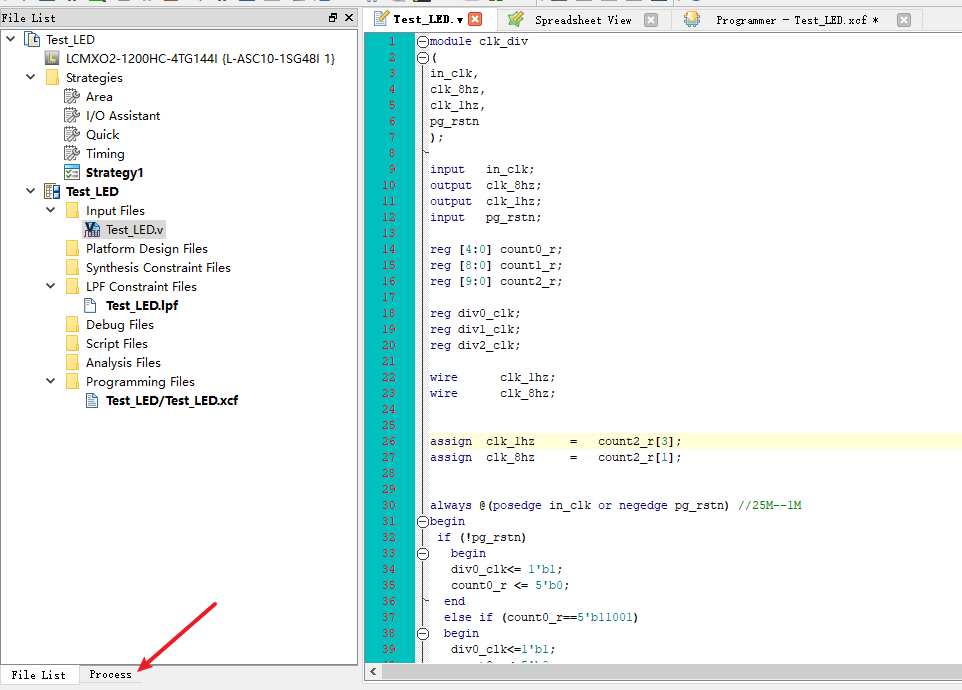

1. 实例代码分析

module clk_div

(

in_clk,

clk_8hz,

clk_1hz,

pg_rstn

);

input in_clk;

output clk_8hz;

output clk_1hz;

input pg_rstn;

....

endmodule

这一段是接口定义,定义了两个输出信号clk_8hz、clk_1hz,代表两个灯不同的频率。两个输入信号in_clk、pg_rstn指芯片的时钟和复位。

模块由关键字module....endmodule 确定。

clk_div模块名

reg [4:0] count0_r;//5bit

reg [8:0] count1_r;//9bit

reg [9:0] count2_r;//10bit

reg定义寄存器,寄存器数据类型有很多种,如reg、integer、real等,其中最常用的就是reg类型。

reg div0_clk;

reg div1_clk;

reg div2_clk;

默认位宽是1。

wire clk_1hz;

wire clk_8hz;

wire定义的是线网,线网指的是Verilog结构化元件间的物理连线

assign clk_1hz = count2_r[9];

assign clk_8hz = count2_r[6];

-

assign产生wire信号语句的关键字,连续赋值语句assign -

比较简单的组合逻辑推荐使用

assign语句,比较复杂的组合逻辑推荐使用always语句。 -

reg与wire的区别详细

always @(posedge in_clk or negedge pg_rstn) //25M--1M

beginif (!pg_rstn)begindiv0_clk<= 1'b1;//一位二进制数1count0_r <= 5'b0;//五位二进制数0endelse if (count0_r==5'b11001)//五位二进制数11001begindiv0_clk<=1'b1;count0_r<=5'b0;end

-

时序逻辑 ,带异步复位 ;

-

posedge是上升沿,电平从低到高跳变 -

negedge是下降沿,电平从高到低跳变 -

参考文章

文章持续更新,由于刚接触,所以很多东西也分析不错来,之后慢慢补充。

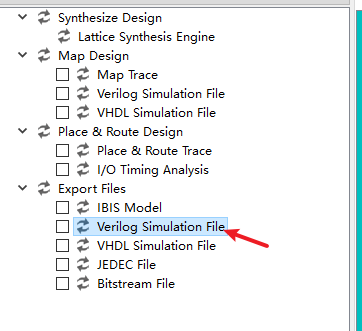

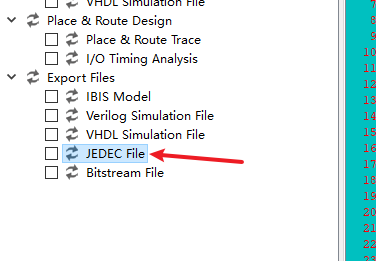

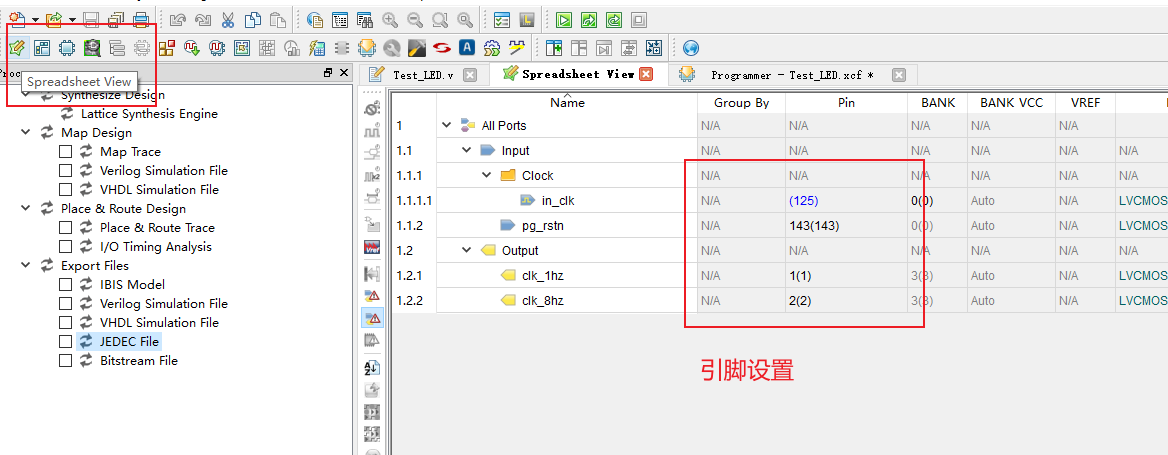

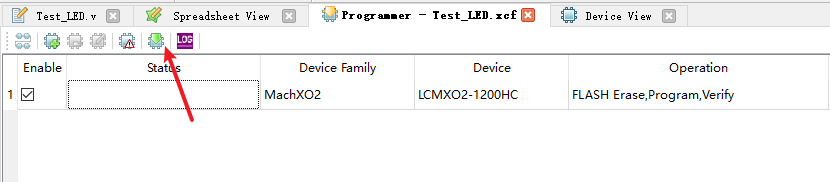

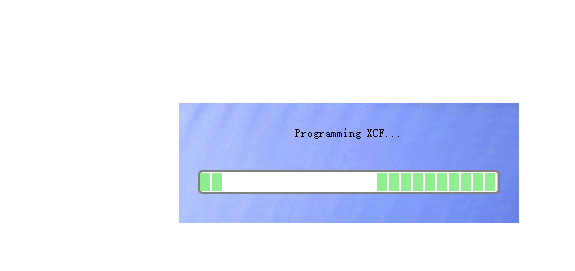

2. 编译运行

- 编译代码

- 生成

JED文件

- 引脚设置

- 找到项目中的

.jed文件

- 设备上电,插上烧录器插上电脑。点击烧录

- 等待

- 完成

四、总结

这东西对于像我这样跨专业的初学者来说真难,慢慢学吧,之后会找有关书或者视频,更新Verilog语言的基础学习笔记。

相关文章:

初学Verilog语言基础笔记整理(实例点灯代码分析)持续更新~

实例:点灯学习 一、Verilog语法学习 1. 参考文章 刚接触Verilog,作为一个硬件小白,只能尝试着去理解,文章未完…持续更新。 参考博客文章: Verilog语言入门学习(1)Verilog语法【Verilog】一文…...

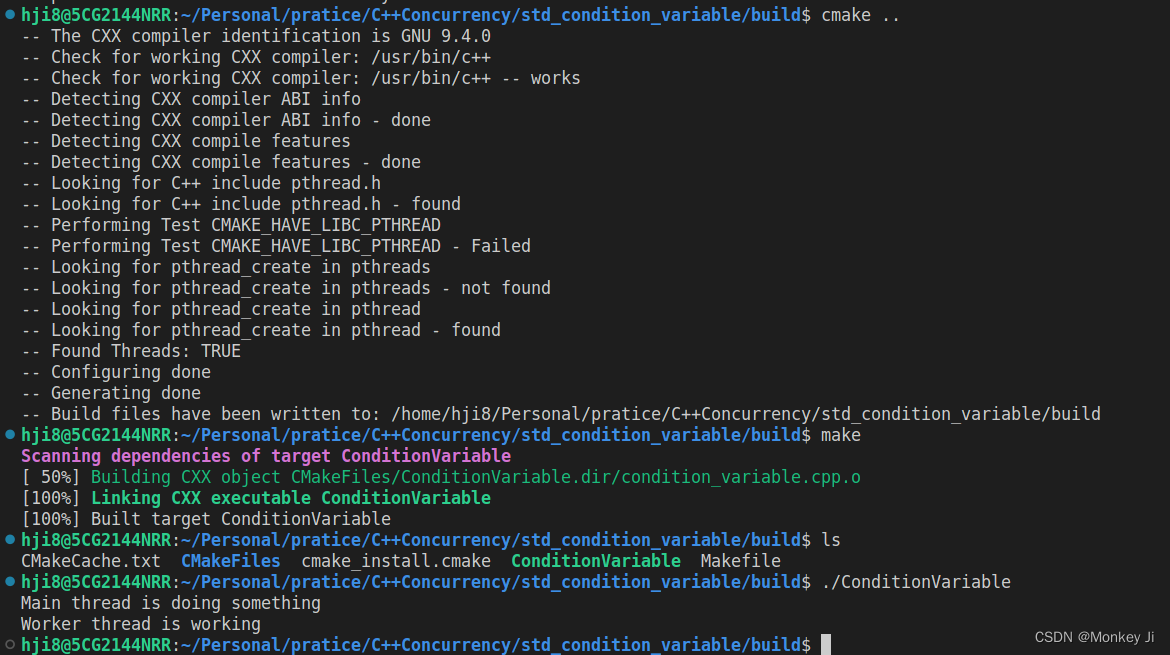

关于 std::condition_variable

一. std::condition_variable是什么? std::condition_variable 是 C 标准库提供的一个线程同步的工具,用于实现线程间的条件变量等待和通知机制。 条件变量的发生通常与某个共享变量的状态改变相关。 在多线程编程中,条件变量通常和互斥锁…...

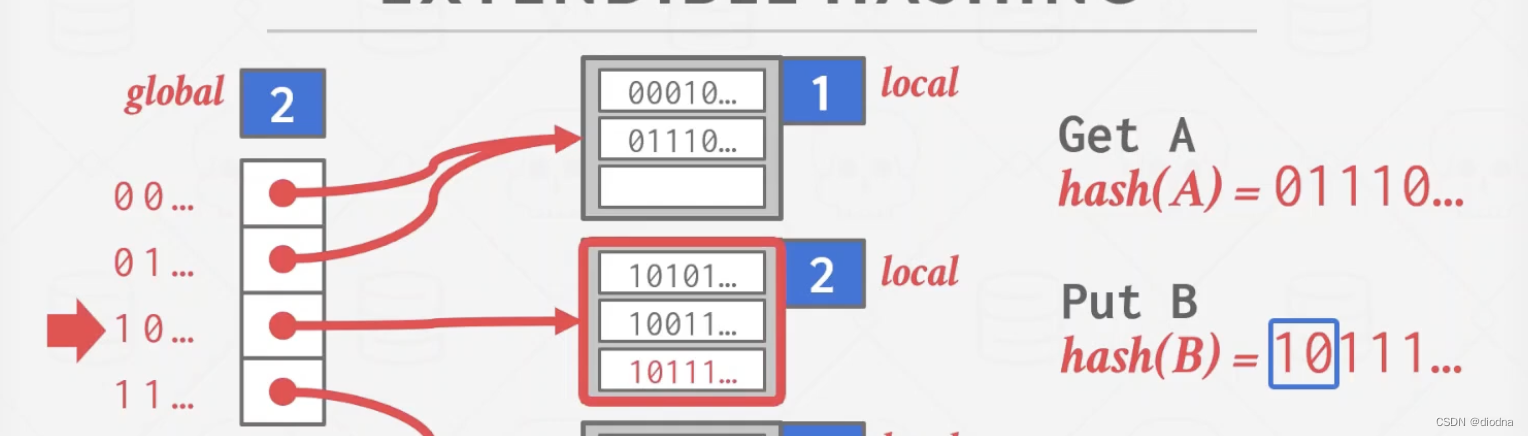

可拓展哈希

可拓展哈希 借CMU 15445的ppt截图来说明问题。 我们传统静态hash的过程是hash函数后直接将值存入对应的bucket,但是在可扩展hash中,得查询Directory(左),存入directory指向的bucket(右)。 下面…...

Java 版 spring cloud 工程系统管理 +二次开发 工程项目管理系统源码

工程项目各模块及其功能点清单 一、系统管理 1、数据字典:实现对数据字典标签的增删改查操作 2、编码管理:实现对系统编码的增删改查操作 3、用户管理:管理和查看用户角色 4、菜单管理:实现对系统菜单的增删改查操…...

通过伴随矩阵怎么求逆矩阵

设矩阵A为n阶方阵,其伴随矩阵为Adj(A),则A的逆矩阵为: A⁻ (1/|A|) Adj(A) |A|为A的行列式 Adj(A)为A的伴随矩阵 具体步骤如下: 求出A的行列式|A| 求出A的伴随矩阵 Adj(A) 。伴随矩阵的定义为:对于A的第i行第j列…...

巡检机器人之仪表识别系统

作者主页:爱笑的男孩。 博客简介:分享机器学习、深度学习、python相关内容、日常BUG解决方法及Windows&Linux实践小技巧。 如发现文章有误,麻烦请指出,我会及时去纠正。有其他需要可以私信我或者发我邮箱:zhilong666foxmail.c…...

)

面试官反感的求职者(下)

上期给大家总结了面试中常见的一些问题,今天就接着上次的话题再给大家说说HR反感的求职者,希望同学们可以自省,避免踩雷。小编从如信银行考试中心了解到的有: 第一、缺乏个性者 这种考生在答题中往往表现得千篇一律,从…...

-生存曲线(LM曲线)(补充篇))

可视化绘图技巧100篇分析篇(二)-生存曲线(LM曲线)(补充篇)

目录 前言 知识储备 生存分析中的基本概念 生存分析 (survival analysis) 事件 (event)...

【100%通过率 】【华为OD机试python】钟表重合时刻【 2023 Q1考试题 A卷|100分】

华为OD机试- 题目列表 2023Q1 点这里!! 2023华为OD机试-刷题指南 点这里!! ■ 题目描述 钟表是日常生活中不可缺少的时间度量计, 其时针、分针、秒针三者的转动速度满足特定规律(见备注)。 现在输入时刻 time ,请计算出时刻 time 小时和 time+1 小时之间, 时针和分针…...

Java线程池编码示例

第1步:自定义线程实现类 Java中多线程编码时,定义线程类有两种方式: 继承Thread类实现Runnable接口(由于Java的单继承特性,一般推荐使用此方式) public class BizThread implements Runnable {private int …...

如何优化Android 4.x系统设置字体大小

android4.x系统设置字体大小导致应用布局混乱的解决方案 在前几年,Android系统的设置界面还是相对简单的,用户可以通过设置菜单进行各种系统设置,如字体大小、壁纸、铃声等。但是随着用户对系统功能的需求越来越多,Android系统也在…...

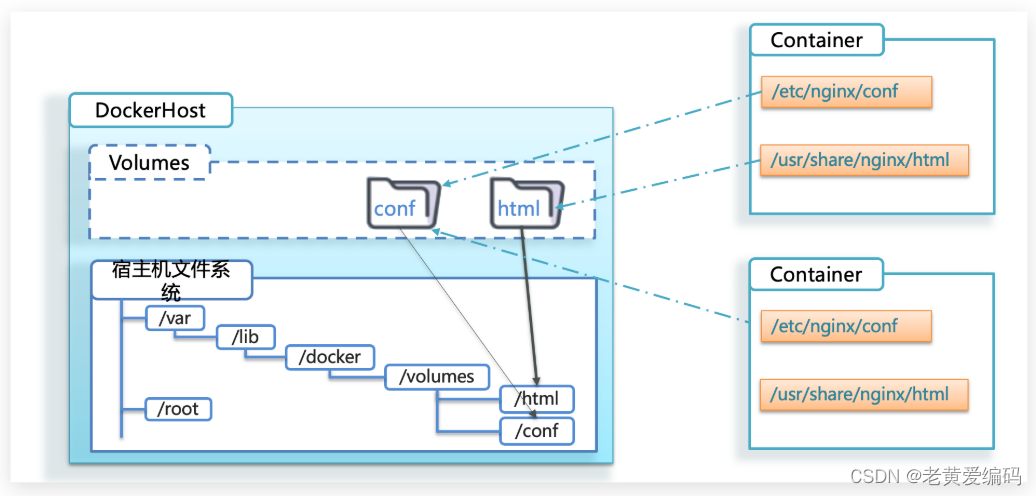

Docker安装、Docker基本操作

一、Dokcer安装 1.安装 # 1、yum 包更新到最新,需要几分钟时间(注意:也可以直接跨过) sudo yum update # 2、作用:安装需要的软件包, yum-util 提供yum-config-manager功能,另外两个是devicemapper驱动依赖的 sudo yum install -y yum-util…...

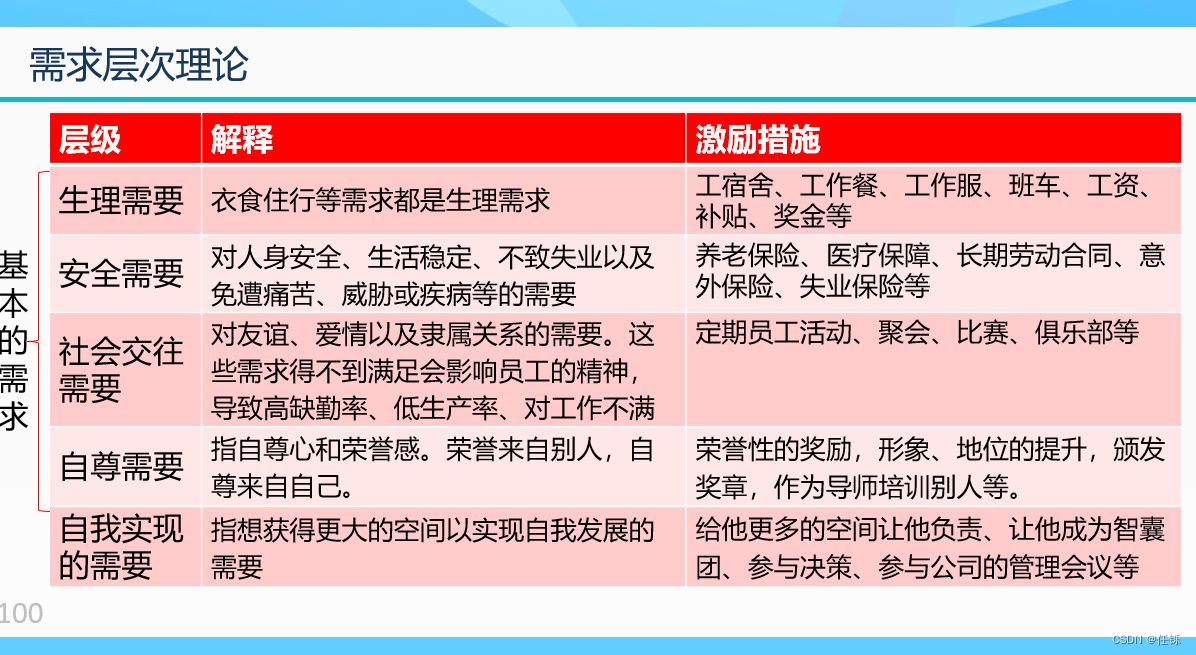

系统集成项目管理工程师知识点总结

项目经理的五种权利: 职位权力: 来源于管理者在组织中的职位和职权。罚权力: 使用降职、扣薪、惩罚、批评、威胁等负面手段的能力。奖励权力: 给予下属奖励的能力专家权力: 来源于个人的专业技能。参照(号…...

【游戏里的网络同步分析】马里奥制造2 多人模式

前置知识 先说几个游戏设计的术语。 PlayerAgent是玩家控制的网络游戏中的角色形象,也是代表在游戏空间中的玩家,被唯一PlayerController所拥有,被所有用户可观测到。 在马里奥制造2中,PlayerAgent一共有四种:马里奥 …...

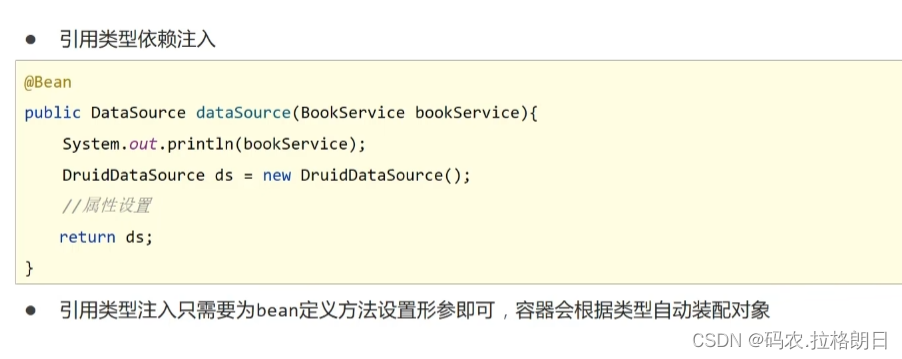

SSM框架学习-注解开发第三方bean管理

1. 复习xml配置文件管理第三方bean 在Spring中,可以使用依赖注入(Dependency Injection)来管理和使用第三方Bean。Spring提供了多种方式来进行依赖注入,比如构造函数注入、Setter方法注入、字段注入等。下面以Setter方法注入为例&…...

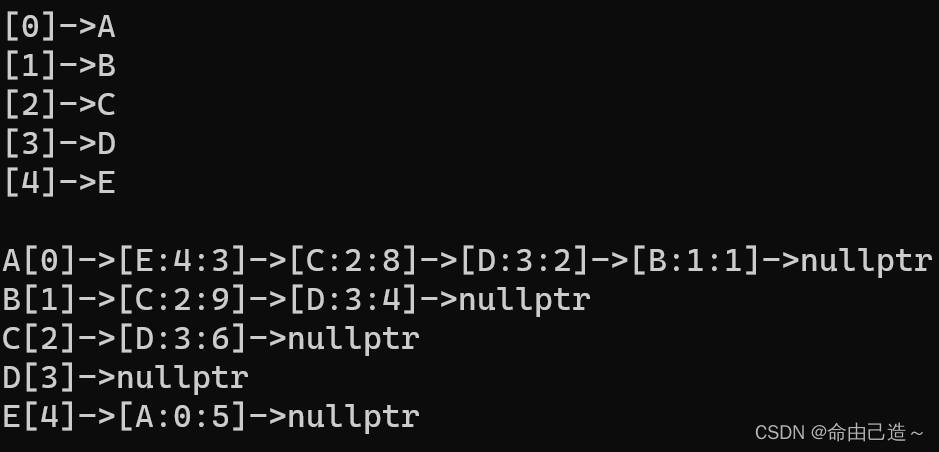

【数据结构与算法】图——邻接表与邻接矩阵

文章目录 一、图的基本概念二、图的存储结构2.1 邻接矩阵2.2 邻接表2.3 邻接矩阵的实现2.4 邻接表的实现 三、总结 一、图的基本概念 图(Graph)是由顶点的有穷非空集合和顶点之间边的集合组成,通常表示为:G(V,E&#…...

网安笔记02 密码学基础

密码学概述 • 1.1、密码学的基本概念 密码编码学 : 密码编制 密码分析学 : 密码破译 密码学 : 研究密码保护 通信手段的科学, 密码编码学密码分析学 密码技术: 把可理解的消息伪装为不可理解的消息,再复原成原消息的科学 概…...

open3d io操作

目录 1. read_image, write_image 2. read_point_cloud, write_point_cloud 3. 深度相机IO操作 4. Mesh文件读取 1. read_image, write_image 读取jpg. png. bmp等文件 image_io.py import open3d as o3dif __name__ "__main__":img_data o3d.data.JuneauIma…...

【Linux】Linux安装Redis(图文解说详细版)

文章目录 前言第一步,下载安装包第二步,上传安装包到/opt下(老规矩了,安装包在opt下)第三步,解压安装包第四步,编译第五步,安装第六步,配置redis第七步,设置开…...

setTimeout不准时,CSS精准实现计时器功能

实际开发过程中,我们会经常遇到,首次进入页面进行相应提示,然后指定时间后自动消失或者前端时钟展示等需求。 按照传统方案,我们可以使用 setTimeout 实现。但其存在:实际延时比设定值更久的情况。 setTimeout 不准时…...

被OpenClaw的MCP协议彻底刷新认知:一个协议统一所有AI工具调用的底层逻辑

做AI Agent开发的同学,几乎都踩过工具调用的"天坑":为了让大模型对接不同的外部能力,你需要为每一个API、每一套业务系统、每一类数据库写专属的适配代码;换一个大模型厂商,之前的工具调用逻辑几乎全部作废&…...

Qwen2.5-72B-Instruct-GPTQ-Int4惊艳效果:多语言混合输入+统一语义理解测试

Qwen2.5-72B-Instruct-GPTQ-Int4惊艳效果:多语言混合输入统一语义理解测试 1. 模型概述 Qwen2.5-72B-Instruct-GPTQ-Int4是Qwen大型语言模型系列的最新版本,代表了当前开源大模型领域的顶尖水平。这个经过GPTQ 4-bit量化的720亿参数指令调优模型&#…...

GraceTheme定义“优雅大气”的WordPress主题新标准

网站不仅是信息的载体,更是品牌气质的延伸。无论是企业官网、个人博客还是作品集展示,如何在茫茫网海中脱颖而出,给用户留下深刻的第一印象?答案往往就藏在网站的“气质”之中。如果你正在寻找一款能够完美平衡美学设计与功能实用性的WordPr…...

3步掌握Dify工作流:从零到精通的完整指南

3步掌握Dify工作流:从零到精通的完整指南 【免费下载链接】Awesome-Dify-Workflow 分享一些好用的 Dify DSL 工作流程,自用、学习两相宜。 Sharing some Dify workflows. 项目地址: https://gitcode.com/GitHub_Trending/aw/Awesome-Dify-Workflow …...

3个实战场景:如何用RegRipper3.0快速分析Windows注册表

3个实战场景:如何用RegRipper3.0快速分析Windows注册表 【免费下载链接】RegRipper3.0 RegRipper3.0 项目地址: https://gitcode.com/gh_mirrors/re/RegRipper3.0 Windows注册表分析工具RegRipper3.0是数字取证和事件响应领域的利器,它能从Window…...

7大核心优势!D3KeyHelper暗黑3智能宏工具全面解析:从手动操作到自动化体验的升级之路

7大核心优势!D3KeyHelper暗黑3智能宏工具全面解析:从手动操作到自动化体验的升级之路 【免费下载链接】D3keyHelper D3KeyHelper是一个有图形界面,可自定义配置的暗黑3鼠标宏工具。 项目地址: https://gitcode.com/gh_mirrors/d3/D3keyHelp…...

从根源到优化:Visual C++ Redistributable AIO工具的5个技术维度解析

从根源到优化:Visual C Redistributable AIO工具的5个技术维度解析 【免费下载链接】vcredist AIO Repack for latest Microsoft Visual C Redistributable Runtimes 项目地址: https://gitcode.com/gh_mirrors/vc/vcredist 问题溯源:运行库故障的…...

实战构建多房间直播平台:基于快马AI生成核心业务代码框架

今天想和大家分享一个实战项目的搭建过程——多房间直播平台。这个项目涉及高并发、实时交互等典型直播场景需求,正好用InsCode(快马)平台来快速验证核心功能。以下是具体实现思路和关键设计: 整体架构设计 直播平台的核心在于实时性和扩展性。采用前后端…...

3步解锁专业翻译:DeepL免费插件零成本使用全攻略

3步解锁专业翻译:DeepL免费插件零成本使用全攻略 【免费下载链接】bob-plugin-akl-deepl-free-translate **DeepL免秘钥,免启服务**,双击使用,免费无限次使用,(**新增DeepL单词查询功能**)根据网页版JavaScript加密算法逆向开发的bobplugin;所以只要官网的算法不改,…...

如何解决多显示器壁纸管理的三大痛点:Superpaper跨平台解决方案实战指南

如何解决多显示器壁纸管理的三大痛点:Superpaper跨平台解决方案实战指南 【免费下载链接】superpaper A cross-platform multi monitor wallpaper manager. 项目地址: https://gitcode.com/gh_mirrors/su/superpaper 在多显示器工作环境中,你是否…...