【FPGA】Verilog:组合电路设计 | 三输入 | 多数表决器

前言:本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载的示例:表决器(三人表决器)。

- 功能特性: 采用 Xilinx Artix-7 XC7A35T芯片

- 配置方式:USB-JTAG/SPI Flash

- 高达100MHz 的内部时钟速度

- 存储器:2Mbit SRAM N25Q064A SPI Flash(样图旧款为N25Q032A)

- 通用IO:Switch :x8LED:x16Button:x5DIP:x8 通用扩展IO:32pin

- 音视频/显示: 7段数码管:x8 VGA视频输出接口 Audio音频接口

- 通信接口:UART:USB转UART Bluetooth:蓝牙模块

- 模拟接口: DAC:8-bit分辨率 XADC:2路12bit 1Msps ADC

目录

Ⅰ. 前置知识

0x00 表决器

0x01 真值表表示

0x02 卡诺图表示

0x03 逻辑表达式:

Ⅱ. Verilog实现

0x00 新建工程并添加的IP包

0x01 利用IP器件创建电路

0x02 Test Bench——添加仿真激励文件

0x03 仿真记录与分析

Ⅲ. 解释说明

Ⅰ. 前置知识

0x00 表决器

以三人表决器为例说明多人表决电路的原理。

设三人表决器中输入为A、B、C,同意用1表示,不同意用0表示。输出为F,A、B、C三者中多数同意,提案通过,否则提案不被通过;通过用1表示,不通过用0表示。

0x01 真值表表示

| 输入 | 输出 | ||

| A | B | C | F |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

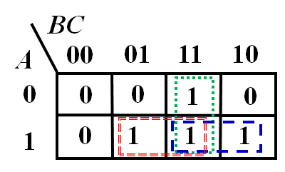

0x02 卡诺图表示

0x03 逻辑表达式

过程:写输出表达式即把输出结果为一的输入相加。如上F的一的有四个,把结果为一对应的输入写出即可,再化简,可通过卡诺图以及逻辑表达式化简。

可用狄摩根律转化为与非形式

若此步有不清楚的可留言

Ⅱ. Verilog实现

在本次Verilog实现表决器的功能中,我们学习如何利用他人封装好的组件型IP器件进行设计,故选择为工程添加所需IP包的方法。

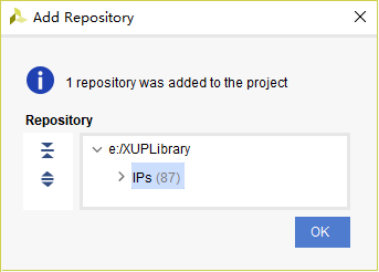

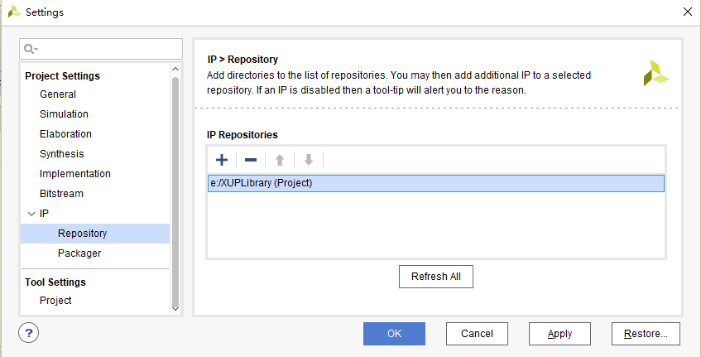

0x00 新建工程并添加的IP包

在工程settings中IP的Repository中选择所需IP包的存放目录

点击Select,在图所示对话框中点击ok

Repositories自动更新如图:

点击OK完成IP包的添加

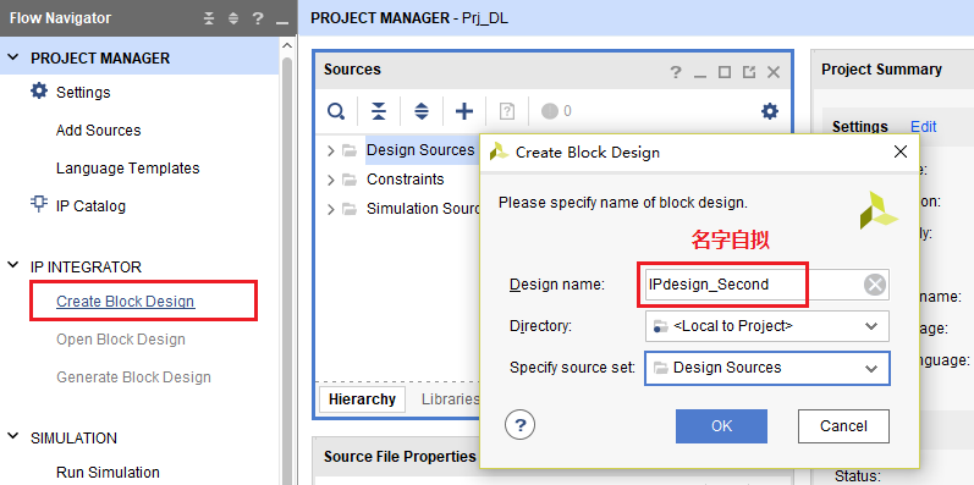

0x01 利用IP器件创建电路

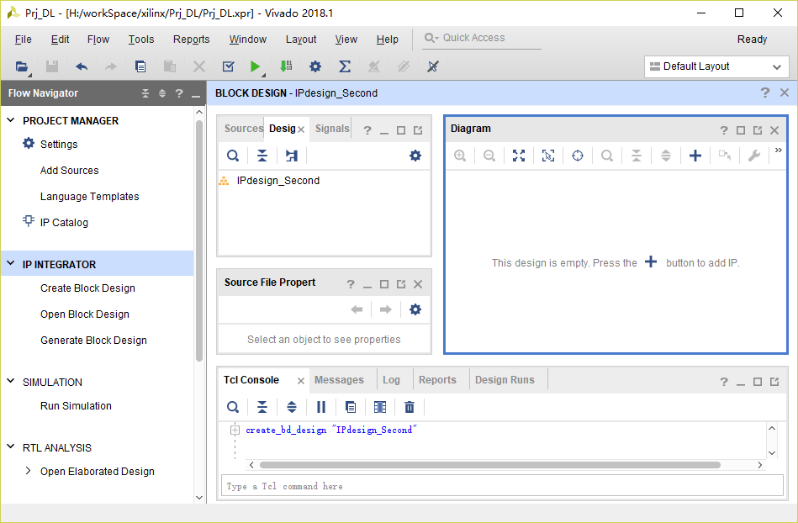

点击Flow Navigator中的IP INTEGRATOR下Create Block Design,为电路设计命名:

点击OK后工程自动更新至如图:

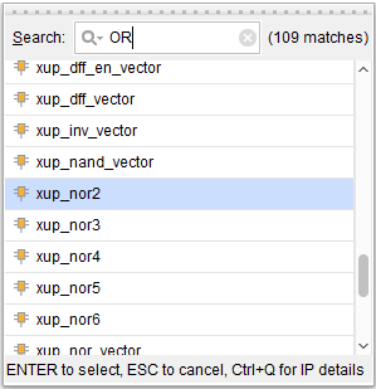

在Diagram窗中点击![]() 按钮,添加IP器件。

按钮,添加IP器件。

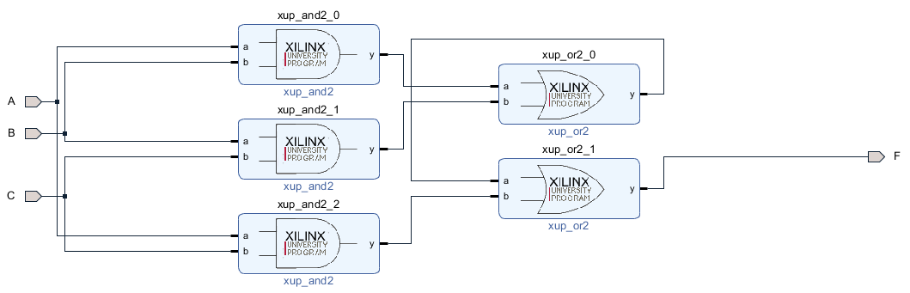

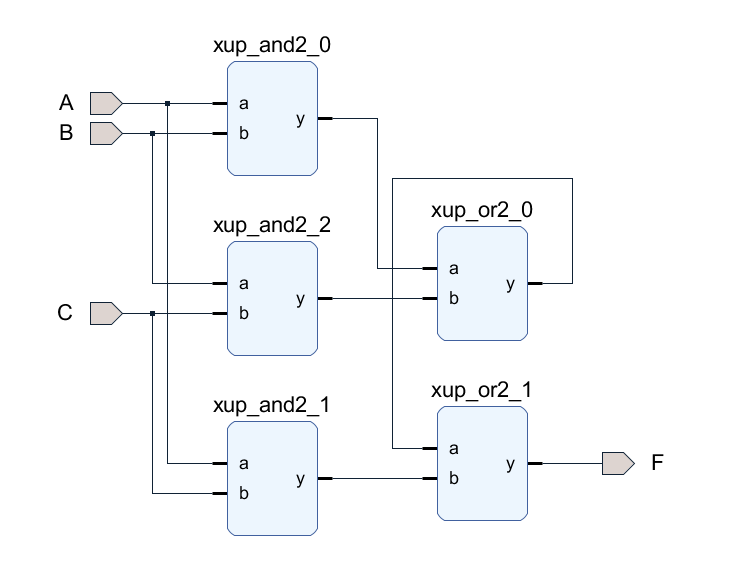

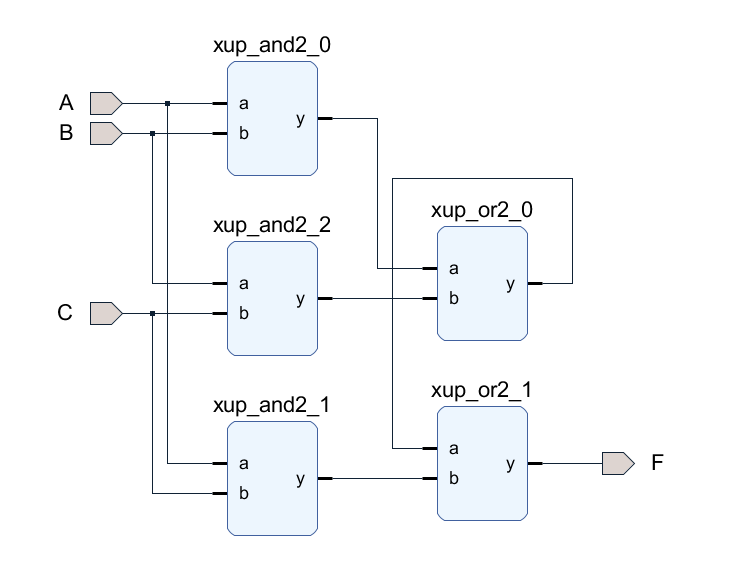

根据原理中的F=AB+BC+CA,本实验添加两种基本器件:AND和OR,

如图:

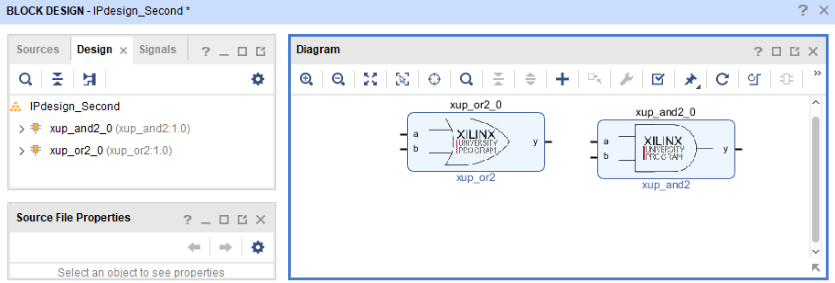

完成后Design窗自动更新至下图效果:

在Diagram窗,完成器件添加

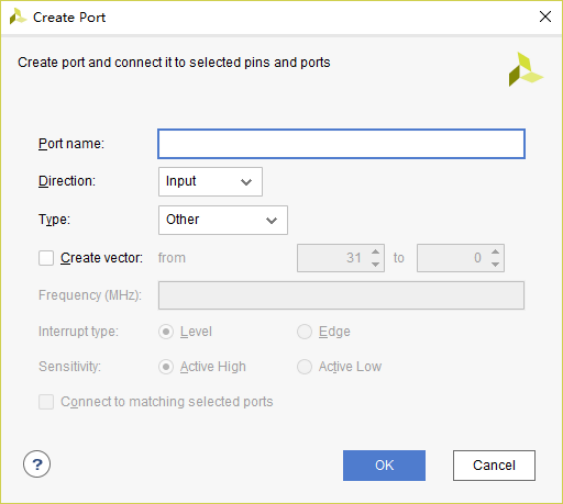

之后添加基本引脚:

增加输入引脚3个,命名自拟

可以为A、B、C,输出1个,可以命名为F。

完成连线,如图:

点击![]() 检查布线的正确性

检查布线的正确性

另外,可点击![]() 可以自动优化布线,但这一步并不是必须的

可以自动优化布线,但这一步并不是必须的

可得出下图:

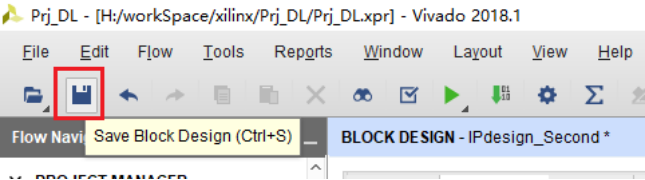

点击【保存】按钮,保存电路设计文件:

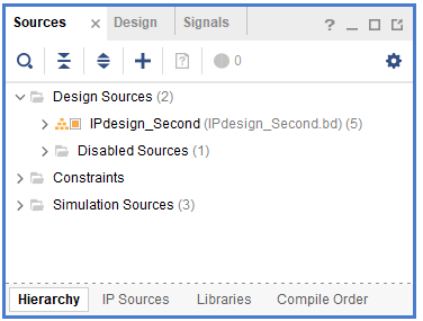

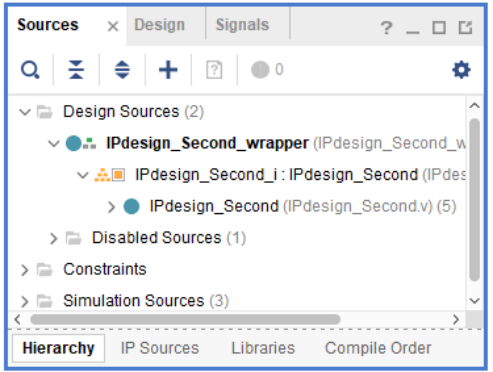

在Sources栏可以看到新增的文件如图:

点击该新增文件,如图:

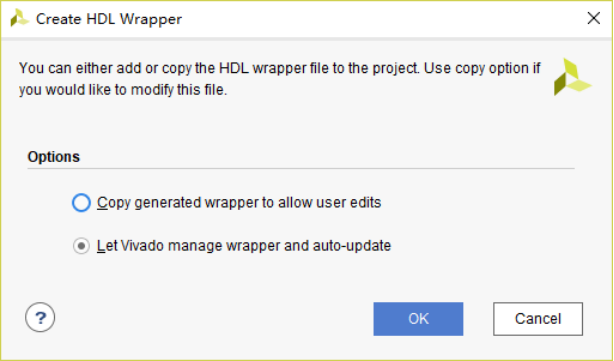

点击Create HDL Wrapper菜单。利用默认项,可让Vivado自动生成代码,如图:

Source栏会自动更新至如图效果:

0x02 Test Bench——添加仿真激励文件

`timescale 1ns / 1ps

module sim4Second( );

reg inA;reg inB;reg inC;

wire outF;

IPdesign_Second_wrapper test(.A(inA),.B(inB),.C(inC),.F(outF));

always begininA = 0;inB = 0;inC=0; #100;inA = 0;inB = 0;inC=1; #100;inA = 0;inB = 1;inC=0; #100;inA = 0;inB = 1;inC=1; #100;inA = 1;inB = 0;inC=0; #100; inA = 1;inB = 0;inC=1; #100;inA = 1;inB = 1;inC=0; #100;inA = 1;inB = 1;inC=1; #100;end

endmodule0x03 仿真记录与分析

| 输入 | 输出 | ||||

| 周期 | 时间 | A | B | C | F |

| 1 | 0-100ns | 0 | 0 | 0 | 0 |

| 2 | 100ns-200ns | 0 | 0 | 1 | 0 |

| 3 | 200ns-300ns | 0 | 1 | 0 | 0 |

| 4 | 300ns-400ns | 0 | 1 | 1 | 1 |

| 5 | 400ns-500ns | 1 | 0 | 0 | 0 |

| 6 | 500ns-600ns | 1 | 0 | 1 | 1 |

| 7 | 600ns-700ns | 1 | 1 | 0 | 1 |

| 8 | 700ns-800ns | 1 | 1 | 1 | 1 |

Ⅲ. 解释说明

本篇博客旨在学习如何利用他人封装好的组件型IP器件进行设计,从而理解在vivado中,Block Design仅仅是用以设计的直观,最终还是需要生成Verilog等硬件描述语言后才能进一步完成后续设计。

同时,本实验中,生成的IPdesign_Second_wrapper这个module其实是调用了IPdesign_Second,这种调用属于模块化设计方法,因此仿真激励文件中语句IPdesign_Second_wrapper test(参数); 其实信号会继续传递给IPdesign_Second 子模块; 请在仿真界面中调出不同模块的引脚波形进行观察理解。

若不使用导入IP包的方法,设计文件可书写如下:

`timescale 1 ps / 1 psmodule design_1_wrapper(A,B,C,F);input A;input B;input C;output F;wire A;wire B;wire C;wire F;design_1 design_1_i (.A(A),.B(B), .C(C),.F(F));

endmodule

相关文章:

【FPGA】Verilog:组合电路设计 | 三输入 | 多数表决器

前言:本章内容主要是演示Vivado下利用Verilog语言进行电路设计、仿真、综合和下载的示例:表决器(三人表决器)。 功能特性: 采用 Xilinx Artix-7 XC7A35T芯片 配置方式:USB-JTAG/SPI Flash 高达100MHz 的内部…...

【安全等保】安全等保二级和三级哪个高?哪个费用更高?

等保政策已经严格落地执行了,各大企业纷纷接到了过等保的通知,但有的估计是第一次听到等保,对于等保相关政策都是非常蒙圈的。这不不少企业相关负责人在问,安全等保二级和三级哪个高?哪个费用更高?这里我们…...

)

C++ STL学习记录(v1)

C STL学习记录一. 什么是STL1.1 STL的诞生1.2 STL基本概念1.3 STL的六大组件1.4 STL中的容器、算法、迭代器1.5 容器、算法、迭代器实践一. 什么是STL 1.1 STL的诞生 STL建立的目的就是为了解决软件界复用性的需求。C的面向对象和泛型编程思想,目的就是为了复用性的…...

开发中遇到的问题

1.当写一个导出功能时,因为编码写URL地址&参数的时候,用反转字符串的时候换行了,造成地址拼接不成,一直报错,后来发现是编码格式造成的,已解决。 解决方案:不换行或者用 “”拼接 2.当本地…...

Javascript笔记

数据类型 基本类型(primitive value) 简单的数据段,包括 Undefined, Null, Boolean, Number, String初始化只使用2原始字面量形式,如果使用new则会创建Object无法加入新的属性 引用类型(reference value) 可能由多个值构成的对象判断类型 typeofinstanc…...

配置及优化)

Elasticsearch(ES)配置及优化

在Elasticsearch中,索引的大小和存储能力取决于多个因素,包括文档大小、索引的分片数、硬件规格、查询负载和其他因素。索引和分片配置:索引和分片的数量和配置会对查询并发性能产生影响。如果索引和分片的数量太少,可能会导致查询…...

一文看懂Java语言与Java生态圈

Java语言与Java生态圈 1、Oracle JDK与Open JDK之间的关系 Oracle JDK Java最早是由SUN公司发明,Oracle JDK之前叫SUN JDK,显而易见,这是在2009年Oracle收购SUN公司之前,收购之后被名为Oracle JDK,实际上࿰…...

GitHub 上有什么嵌入式方面的项目?

原文直达,喜欢就点个赞吧! GitHub 上有什么嵌入式方面的项目? - CodeAllen的回答 - 知乎 https://www.zhihu.com/question/27835930/answer/2871624679 前言 对于GitHub,可能做互联网开发的同学会更加熟悉,尤其是前端࿰…...

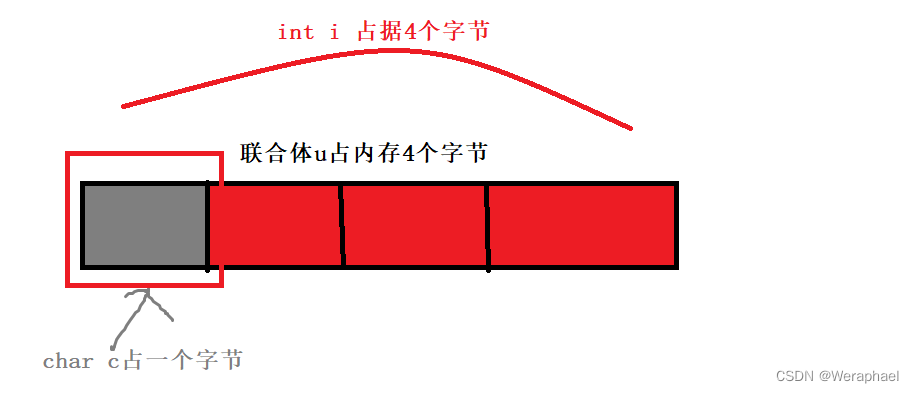

【C语言进阶】结构体、位段、枚举和联合

👦个人主页:Weraphael ✍🏻作者简介:目前是C语言学习者 ✈️专栏:C语言航路 🐋 希望大家多多支持,咱一起进步!😁 如果文章对你有帮助的话 欢迎 评论💬 点赞&a…...

markdown和latex常用部分参考@注脚@链接跳转@csdn

文章目录refmarkdown和latex常用部分参考typora文档基础语法扩展语法链接内联链接的方式将链接提取出来链接示例typora的支持LinksInline LinksInternal Links🎈Reference LinksURLs文章内部跳转(Heading IDs)🎈My Great Heading注脚(Footnotes)…...

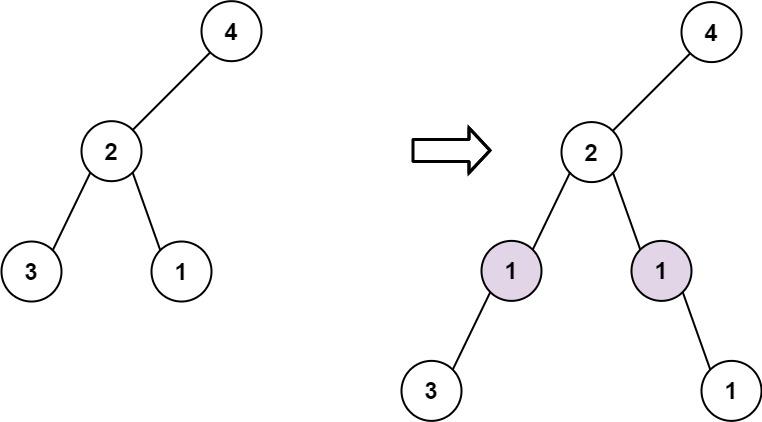

Java 在二叉树中增加一行

623. 在二叉树中增加一行中等给定一个二叉树的根 root 和两个整数 val 和 depth ,在给定的深度 depth 处添加一个值为 val 的节点行。注意,根节点 root 位于深度 1 。加法规则如下:给定整数 depth,对于深度为 depth - 1 的每个非空树节点 cur…...

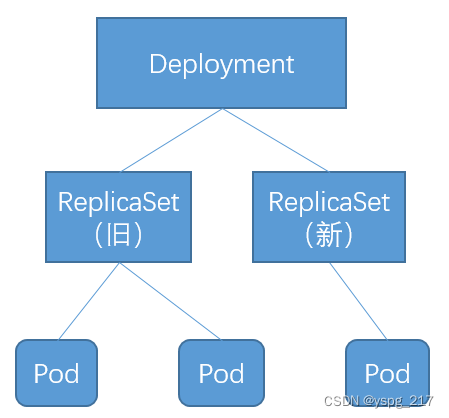

kubernetes(k8s) 知识总结(第2期)

1. “控制器”思想 kube-controller-manager 是一系列控制器的集合,这些控制器被放在 Kubernetes 项目的 pkg/controller 目录,这些控制器都以独有的方式负责某种编排功能。它们都遵循一个通用的编排模式——控制循环。 以 Deployment 为例介绍它对控…...

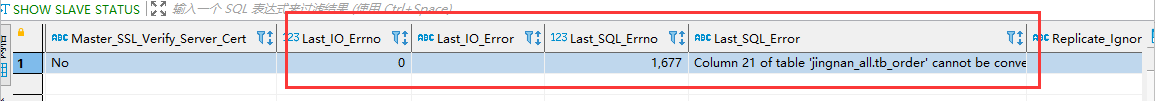

windows-Mysql的主从数据库同步设置

复制原有的mysql修改my.ini配置文件 修改端口号修改从数据的地址和从数据库的数据存放地址安装从数据库进入从数据库的bin目录,打开命令窗口输入命令:mysqld.exe install mysql-back --defaults-file "C:\ProgramData\MySQL\MySQL Server 5.7-back\…...

Docker逃逸

文章目录原理环境搭建Docker 环境判断Docker 容器逃逸特权模式逃逸如何判断是否为特权模式逃逸docker.sock挂载逃逸逃逸Remote API未授权访问未授权访问逃逸容器服务缺陷逃逸影响版本环境搭建逃逸脏牛漏洞逃逸参考原理 docker其实就是一个linux下的进程,它通过Name…...

k8s项目部署

k8s命令k8s项目部署部署流程实现导出相应的yaml文件 kubectl create deployment 名字--image镜像-o yaml --dry-runclient > 文件名 例: kubectl create deployment nginx --imagenginx -o yaml --dry-runclient > m1.yaml导出已经部署后的yaml文件 kubectl g…...

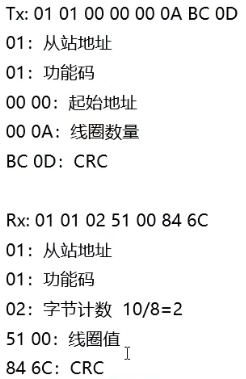

Modbus通信协议学习笔记

Modbus主从设备 主控设备(Modbus Master):工控机、PLC、触摸屏等等 从设备(Modbus Slave):PLC、Modbus采集模块、带485通讯的传感器、仪器仪表等等 Modbus物理接口:串口(RS232、RS4…...

ubuntu重启、关机命令

// // // //之前用linux系统, 一键解决也是可以的,反正我每次用命令(泪目…),中间崩了好几次,换回win,此篇也做记录 // // // 重启命令 以下所有命令在root根目录下输入(普通用户&…...

Xshell 7 连接云服务器的步骤和出现的错误

一、工具准备云服务器Xshell 7二、使用 Xshell 7 连接数据库三、新建会话属性后,没有自动弹出 SSH 用户名要求输入四、SSH 用户身份验证不能输入 Password五、Xshell 连接 centos 7 服务器 报错提示 “ssh服务拒绝了密码,请再试一次“,但是密…...

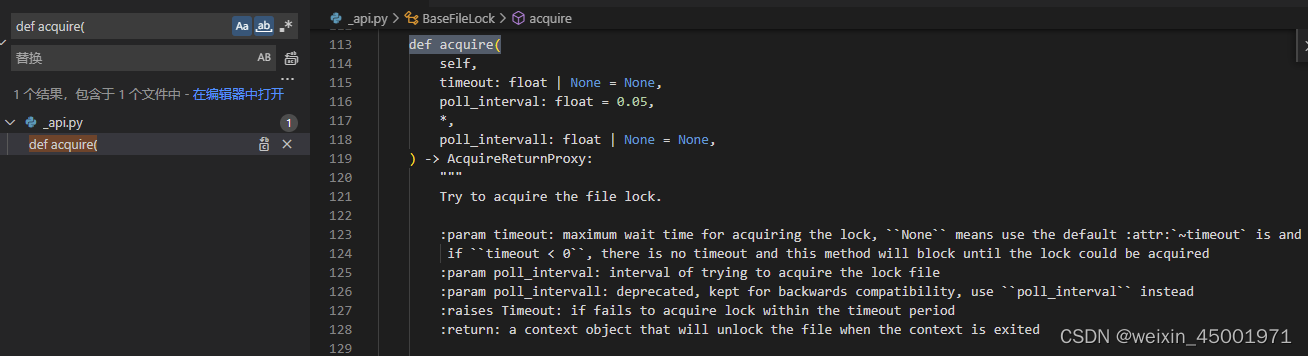

Python多进程同步——文件锁

多个进程共享同一份资源(共享内存、文件等)时,会涉及到资源竞争问题。为了解决这种问题,一般采取的措施是进程在访问资源前加锁保护,避免多个进程同时读写。本文介绍的Python文件锁可以用来解决多进程的同步问题。 目录…...

实现 element-plus 表格多选时按 shift 进行连选的功能

前言 element-plus表格提供了多选功能,可单击勾选一条数据,可全选。 现在有个很合理的需求,希望实现类似于文件系统中shift连续选择功能,并且在表格排序后,依照排序后的顺序连选。 一、el-table 多选表格基本使用 1、…...

从国赛H题到实战:构建远程幅频特性测试系统的硬件设计精要

1. 从竞赛到实战的硬件设计转型 参加电子设计竞赛的朋友们都知道,国赛H题这类题目往往能给我们带来宝贵的实战经验。2017年的这道远程幅频特性测试装置题目,看似是一个具体的竞赛任务,实则蕴含了许多通用硬件设计原理。我在实际项目中多次运用…...

XOutput 终极指南:让老旧游戏手柄重获新生的完整教程

XOutput 终极指南:让老旧游戏手柄重获新生的完整教程 【免费下载链接】XOutput DirectInput to XInput wrapper 项目地址: https://gitcode.com/gh_mirrors/xo/XOutput XOutput 是一个强大的开源工具,专门解决 Windows 平台上游戏控制器兼容性难题…...

3个步骤掌握APK Installer:在Windows上直接安装Android应用的终极指南

3个步骤掌握APK Installer:在Windows上直接安装Android应用的终极指南 【免费下载链接】APK-Installer An Android Application Installer for Windows 项目地址: https://gitcode.com/GitHub_Trending/ap/APK-Installer 你是否厌倦了在Windows电脑上使用笨重…...

【DeepSeek+Grafana可视化实战指南】:20年SRE亲授5大避坑法则与实时指标监控黄金配置

更多请点击: https://intelliparadigm.com 第一章:DeepSeekGrafana可视化实战导论 DeepSeek 系列大模型(如 DeepSeek-V2、DeepSeek-Coder)在推理服务中产生丰富的运行时指标——包括 token 吞吐量、P99 延迟、GPU 显存占用、请求…...

【Amazon Quick 桌面 AI 助手初体验】把重复造轮子的活交给 Quick 大显身手

🪪 本文作者:许业宝 ✍️ 作者信息: 🌞 VSTECS云解决方案架构师 | AWS APN Ambassador | 🪪 AWS Community Builder | 亚马逊云科技技能云博主 | UGL ⭐ 已获得 AWS 认证大满贯(13 个…...

)

别再死记SGD公式了!用PyTorch手把手带你复现一个‘会滚下山’的优化器(附完整代码)

从零构建PyTorch SGD优化器:可视化梯度下降的物理直觉 想象你站在一座云雾缭绕的山顶,手中握着一颗钢珠。当你松开手指,钢珠会沿着最陡峭的路径滚向谷底——这正是梯度下降算法的核心隐喻。本文将带你用PyTorch重建这个直观过程,不…...

极域电子教室破解终极指南:5步重获电脑控制权

极域电子教室破解终极指南:5步重获电脑控制权 【免费下载链接】JiYuTrainer 极域电子教室防控制软件, StudenMain.exe 破解 项目地址: https://gitcode.com/gh_mirrors/ji/JiYuTrainer 你是否曾在上机课时被极域电子教室的全屏广播困住,想要操作电…...

Go语言Beego框架如何用_Go语言Beego框架入门教程【高效】

Beego Controller 靠约定式反射自动注册,需嵌入 beego.Controller、方法名首字母大写且以 HTTP 动词开头、文件置于 controllers/ 目录下;路由参数用 :id 形式绑定到同名 string 参数;模板路径为 views/{小写控制器名}/{小写方法名}.html&…...

Illustrator脚本自动化终极指南:如何节省设计师90%重复工作时间

Illustrator脚本自动化终极指南:如何节省设计师90%重复工作时间 【免费下载链接】illustrator-scripts Adobe Illustrator scripts 项目地址: https://gitcode.com/gh_mirrors/il/illustrator-scripts Adobe Illustrator脚本自动化是每个设计师都应该掌握的生…...

)

告别手写代码!用Simulink+STM32CubeMX给F103点个灯(保姆级图文教程)

零代码玩转STM32:Simulink与CubeMX联动的LED控制实战指南 在嵌入式开发领域,传统的手写代码方式正逐渐被模型化设计工具所革新。想象一下,只需拖拽几个功能模块,设置几个参数,就能让STM32微控制器按照你的想法工作——…...