基于FPGA实现BPSK 调制

目录

- 一、 任务介绍

- 二、基本原理

- 三、基于FPGA实现BPSK 调制

- 四、源码

一、 任务介绍

BPSK 调制在数字通信系统中是一种极重要的调制方式,它的抗干扰噪声性能及通频带的利用率均优先于 ASK 移幅键控和 FSK 移频键控。因此,PSK 技术在中、高速数据传输中得到了十分广泛的应用。

二、基本原理

PSK 信号是用载波相位的变化表征被传输信息状态的,通常规定 0 相位载波和π相位载波分别代表传 1 和传 0,其时域波形示意图如图 2-1 所示。设二进制单极性码为 an,其对应的双极性二进制码为 bn,则 BPSK 信号的一般时域数学表达式为:

由(2-1)式可见,BPSK 信号是一种双边带信号我们知道,BPSK 信号是用载波的不同相位直接去表示相应的数字信号而得出的,在这种绝对移相的方式中,由于发送端是以某一个相位作为基准的,因而在接收系统也必须有这样一个固定基准相位作参考。如果这个参考相位发生变化,则恢复的数字信息就会与发送的数字信息完全相反,从而造成错误的恢复。这种现象常称为 BPSK 的“倒π”现象,因此,实际中一般不采用 BPSK 方式,而采用差分移相(2DPSK)方式。

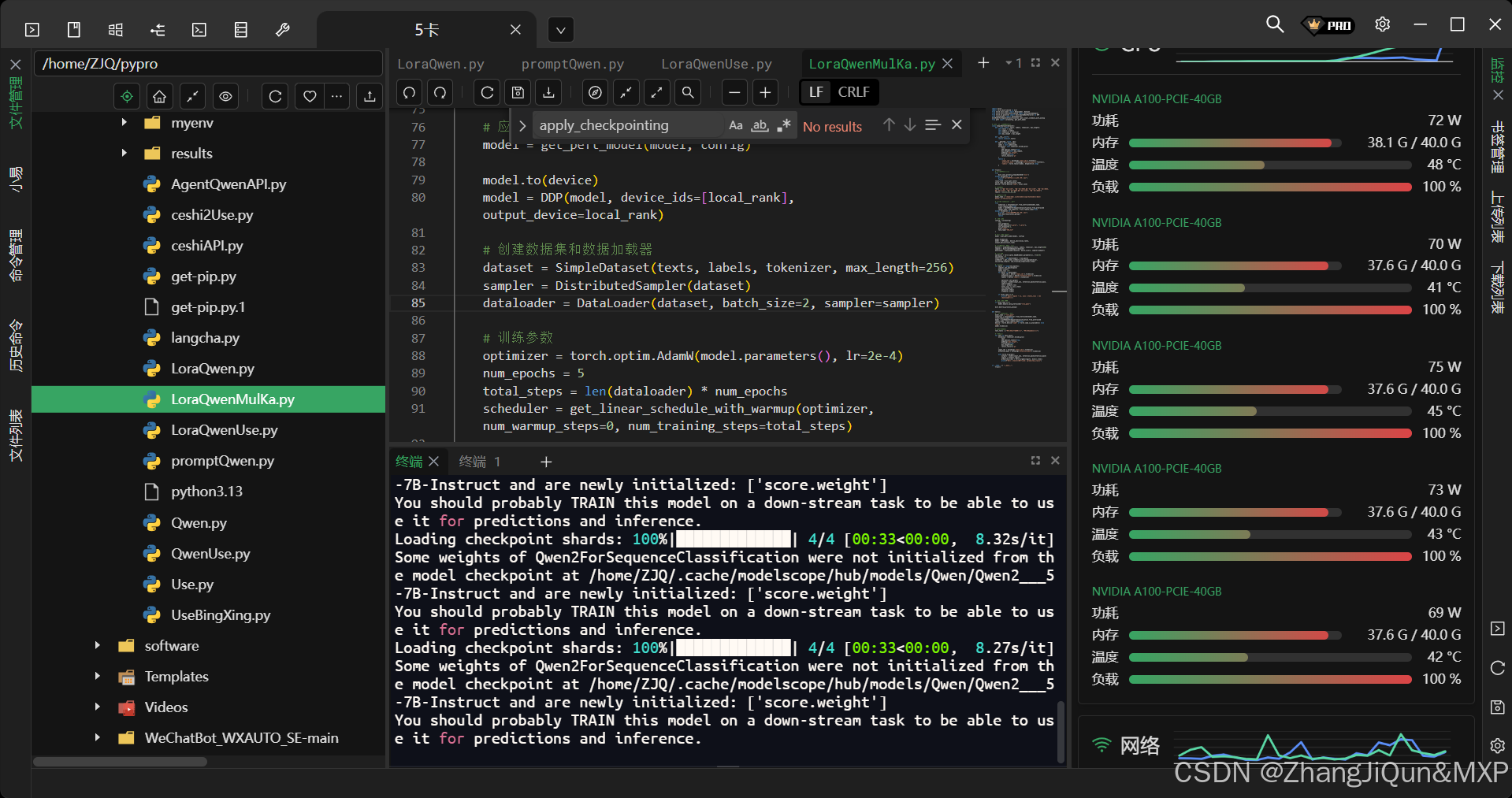

三、基于FPGA实现BPSK 调制

1、 创建工程文件,选择对应 BYS3 的型号;

2、添加一个顶层文件;

3、 创建一个 RAM IP 核用来存放 DDS 数据,此步骤为 DDS 的使用;

4、添加相应matlab生成的coe 文件;

5、 IP 核创建完成后,进行离线仿真验证 IP 核,创建一个仿真文件:找到 Simulation 目录,右击刚刚创建的仿真文件,选择 Set as Top,找到生成的 IP 核,复制框选的代码,作为例化的模板;将 IP 核例化到仿真文件中,再添加测试的模拟时钟和地址累加,如下图可以看到 douta 的正弦波波形;单载波离线仿真完成。

6、接下来创建约束 XDC 文件,代码在实验代码部分;

7、逻辑分析仪的使用,先点击 run synthesis 结束没有报错后 点开 Open

synthesis 再点击 Set Up DeBug,确认信号线都已添加;

8、添加完成后点击生成 bit,再点击 program devic,选择芯片,最后点击 program;

9、点击 run 出现波形,片上示波器使用步骤完成:

四、源码

veirilog HDL TOP 层代码代码:

module BPSK(

input clk, input reset, output sclk, //AD

output cs_n, //AD

output led, input sdata, //AD

output sinout1,//DA

output sync_n, //DA

output sysclk,//DA

output sinout2

);

reg [7:0]addr;

wire [7:0] sin;

reg clk_10m;

reg [1:0] cont;

wire [7:0] data;

sin sin_rom (

.clka(clk_10m), // input wire clka

.ena(1'b1), // input wire ena

.addra(addr), // input wire [7 : 0] addra

.douta(sin) // output wire [7 : 0] douta

);

always @(negedge clk_10m)

if(~reset)

addr <= 0;

else //if(sync_n==1)

addr <= addr + 1500;

clk_freq clk_freq(

.clk(clk),

.rst_n(reset),

.clk_10m(clk_10m)

);

always @(negedge clk or negedge reset)

begin

if(!reset)

cont <=0;

else

cont <=cont+2'b01;

end

adc_adc081s021 adc_adc081s021(

cs_n,sclk,data, cont[1], reset,sdata

);

DAC_deltasigma DAC_deltasigma

(

.DACout(sinout2),

.DACin(sin), // .DACin(data),

.Clk(clk_10m),

.Reset(reset)

);

DAC_dac081s101 DAC_dac081s101

(

.DACout(sinout1),

.sync_n(sync_n),

.DACin(sin),

.Clk(clk_10m),

.Reset(reset),

.sysclk(sysclk)

);

PN 码

reg [24:0]cnt;

wire pn_clk;

wire pn_out;

always @(negedge clk_10m) //时钟四分频

begin

if(~reset)

cnt<=0;

else

cnt<=cnt+1;

end

assign pn_clk =cnt[1];

code_gen U_code_gen(

.clk(clk_10m),

.grst_n(reset),

.ms_flag(1'b0),

.num(6'b000110),

.pn_clk(pn_clk),

.pn_out(pn_out)

);

reg [7:0] bpsk;

always @(negedge clk_10m)

bpsk<= pn_out?(~sin):sin;

assign led = &(pn_out|bpsk|sin);

endmodule

adc_adc081s021 模块代码:

module adc_adc081s021(

cs_n,sclk, data, clk, reset, sdata

);

output sclk;

output cs_n;

output [7:0] data;

input clk;

input reset;

input sdata;

reg sclk;

reg cs_n;

reg count;

reg [4:0] bits;

reg [7:0] data;

always @(negedge clk or negedge reset)

begin

if(!reset)

begin

count<=0;

end

else

begin

count<=count+1;

end

end

always @(negedge clk or negedge reset)

begin

if(!reset)

begin

sclk<=0;

end

else

begin

if(count==1)

sclk<=~sclk;

end

end

always @(negedge sclk or negedge reset)

begin

if(!reset)

begin

cs_n<=1'b1;

data<=0;

bits<=0;

end

else

case(bits)

5'd0:

begin

if(cs_n)

begin

bits <= 5'd0;

cs_n <=0;

end

else

bits <= 5'd1;

end

5'd1:

begin

bits <= 5'd2;

cs_n<=1'b0;

end

5'd2:

begin

bits <= 5'd3;

cs_n<=1'b0;

end

5'd3:

begin

bits <= 5'd4;

cs_n <= 1'b0;

end

5'd4:

begin

data[7]<= sdata;

bits <= 5'd5;

cs_n<=1'b0;

end

5'd5:

begin

data[6]<= sdata;

bits <= 5'd6;

cs_n<=1'b0;

end

5'd6:

begin

data[5]<= sdata;

bits <= 5'd7;

cs_n <=1'b0;

end

5'd7:

begin

data[4]<= sdata;

bits <= 5'd8;

cs_n <=1'b0;

end

5'd8:

begin

data[3]<= sdata;

bits <= 5'd9;

cs_n <=1'b0;

end

5'd9:

begin

data[2]<= sdata;

bits <= 5'd10;

cs_n <= 1'b0;

end

5'd10:

begin

data[1]<= sdata;

bits <= 5'd11;

cs_n <= 1'b0;

end

5'd11:

begin

data[0]<= sdata;

bits <= 5'd12;

cs_n<=1'b0;

end

5'd12:

begin

bits <= 5'd13;

cs_n<=1'b0;

end

5'd13:

begin

bits <= 5'd14;

cs_n<=1'b0;

end

5'd14:

begin

bits <= 5'd15;

cs_n<=1'b0;

end

5'd15:

begin

bits <= 5'd16;

cs_n<=1'b1;

end

5'd16:

begin

bits <= 5'd17;

cs_n<=1'b1;

end

5'd17:

begin

bits <= 5'd18;

cs_n<=1'b1;

end

5'd18:

begin

bits <= 5'd19;

cs_n<=1'b1;

end

5'd19:

begin

bits <= 5'd0;

cs_n<=1'b1;

end

endcase

end

endmodule

DAC_deltasigma 模块代码:

`define MSBI 7

module DAC_deltasigma(DACout, DACin, Clk, Reset);

output DACout; // This is the average output that feeds low pass filter

reg DACout; // for optimum performance, ensure that this ff is in IOB

input [`MSBI:0] DACin; // DAC input (excess 2**MSBI)

input Clk;

input Reset;

reg [`MSBI+2:0] DeltaAdder; // Output of Delta adder

reg [`MSBI+2:0] SigmaAdder; // Output of Sigma adder

reg [`MSBI+2:0] SigmaLatch; // Latches output of Sigma adder

reg [`MSBI+2:0] DeltaB; // B input of Delta adder

always @(SigmaLatch) DeltaB = {SigmaLatch[`MSBI+2], SigmaLatch[`MSBI+2]} << (`MSBI+1);

always @(DACin or DeltaB) DeltaAdder = DACin + DeltaB;

always @(DeltaAdder or SigmaLatch) SigmaAdder = DeltaAdder + SigmaLatch;

always @(posedge Clk or negedge Reset)

begin

if(!Reset)

begin

SigmaLatch <= 1'b1 << (`MSBI + 1);

DACout <= 1'b0;

end

else

begin

SigmaLatch <= SigmaAdder;

DACout <= SigmaLatch[`MSBI+2];

end

end

endmodule

DAC_dac081s101 模块代码:

module DAC_dac081s101(

DACout, sync_n, DACin,

Clk, Reset, sysclk

);

output DACout; // This is the average output that feeds low pass filter

output sync_n;

reg DACout; // for optimum performance, ensure that this ff is in IOB

reg sync_n;

output sysclk;

input [7:0] DACin;

input Clk;

input Reset;

//reg [15:0] reg1;

reg [3:0] bits;

reg sysclk;

always @(negedge Clk or negedge Reset)

begin

if(~Reset)

begin

sysclk <= 0;

end

else

sysclk<=~sysclk;

end

always @(negedge sysclk or negedge Reset)

begin

if(!Reset)

begin

bits <= 4'b0;

DACout <= 1'b0;

sync_n<=1'b1;

end

else

case(bits)

4'd0:

begin

DACout <= 0;

if(sync_n)

begin

bits <= 4'd0;

sync_n <=0;

end

else

bits <= 4'd1;

end

4'd1:

begin

DACout <= 0;

bits <= 4'd2;

sync_n<=1'b0;

end

4'd2:

begin

DACout <= 0;

bits <= 4'd3;

sync_n<=1'b0;

end

4'd3:

begin

DACout <= DACin[7];

//DACout <= 0;

bits <= 4'd4;

sync_n<=1'b0;

end

4'd4:

begin

DACout <= DACin[6];

// DACout <= 0;

bits <= 4'd5;

sync_n<=1'b0;

end

4'd5:

begin

DACout <= DACin[5];

bits <= 4'd6;

sync_n<=1'b0;

end

4'd6:

begin

DACout <= DACin[4];

bits <= 4'd7;

sync_n<=1'b0;

end

4'd7:

begin

DACout <= DACin[3];

bits <= 4'd8;

sync_n<=1'b0;

end

4'd8:

begin

DACout <= DACin[2];

bits <= 4'd9;

sync_n<=1'b0;

end

4'd9:

begin

DACout <= DACin[1];

bits <= 4'd10;

sync_n<=1'b0;

end

4'd10:

begin

DACout <= DACin[0];

bits <= 4'd11;

sync_n<=1'b0;

end

4'd11:

begin

// DACout <= DACin[0];

DACout <= 0;

bits <= 4'd12;

sync_n<=1'b0;

end

4'd12:

begin

// DACout <= DACin[0];

DACout <= 0;

bits <= 4'd13;

sync_n<=1'b0;

end

4'd13:

begin

DACout <= 0;

bits <= 4'd14;

sync_n<=1'b0;

end

4'd14:

begin

DACout <= 0;

bits <= 4'd15;

sync_n<=1'b0;

end

4'd15:

begin

DACout <= 0;

bits <= 4'd0;

sync_n<=1'b1;

end

endcase

end

endmodul

相关文章:

基于FPGA实现BPSK 调制

目录 一、 任务介绍二、基本原理三、基于FPGA实现BPSK 调制四、源码 一、 任务介绍 BPSK 调制在数字通信系统中是一种极重要的调制方式,它的抗干扰噪声性能及通频带的利用率均优先于 ASK 移幅键控和 FSK 移频键控。因此,PSK 技术在中、高速数据传输中得…...

深入理解 ResponseBodyAdvice 及其应用

ResponseBodyAdvice 是 Spring MVC 提供的一个强大接口,允许你在响应体被写入 HTTP 响应之前对其进行全局处理。 下面我将全面介绍它的工作原理、使用场景和最佳实践。 基本概念 接口定义 public interface ResponseBodyAdvice<T> {boolean supports(Metho…...

)

Java 基础 - 反射(1)

文章目录 引入类加载过程1. 通过 new 创建对象2. 通过反射创建对象2.1 触发加载但不初始化2.2 按需触发初始化2.3 选择性初始化控制 核心用法示例1. 通过无参构造函数创建实例对象2. 通过有参构造函数创建实例对象3. 反射通过私有构造函数创建对象, 破坏单例模式4. …...

Spring Boot中Spring MVC相关配置的详细描述及表格总结

以下是Spring Boot中Spring MVC相关配置的详细描述及表格总结: Spring MVC 配置项详解 1. 异步请求配置 spring.mvc.async.request-timeout 描述:设置异步请求的超时时间(单位:毫秒)。默认值:未设置&…...

flink Shuffle的总结

关于 ** 5 种 Shuffle 类型** 的区别、使用场景及 Flink 版本支持的总结: * 注意:下面是问AI具体细节与整理学习 1. 核心区别 Shuffle 类型核心特点使用场景Flink 版本支持Pipelined Shuffle流式调度,纯内存交换,低延迟(毫秒级…...

在排序数组中查找元素的第一个和最后一个位置 --- 二分查找

目录 一:题目 二:算法原理分析 三:代码实现 一:题目 题目链接: 34. 在排序数组中查找元素的第一个和最后一个位置 - 力扣(LeetCode) 二:算法原理分析 三:代码实现 c…...

631SJBH中小型企业的网络管理模式的方案设计

1.1、研究现状 我国很多企业信息化水平一直还处在非常初级的阶段,有关统计表明,真正实现了计算机较高应用的企业在全国1000多万中小企业中所占的比例还不足10%幢3。大多数企业还停留在利用互联网进行网上查询(72.9%)、…...

)

NO.85十六届蓝桥杯备战|动态规划-经典线性DP|最长上升子序列|合唱队形|最长公共子序列|编辑距离(C++)

经典线性dp问题有两个:最⻓上升⼦序列(简称:LIS)以及最⻓公共⼦序列(简称:LCS),这两道题⽬的很多⽅⾯都是可以作为经验,运⽤到别的题⽬中。⽐如:解题思路&…...

0410 | 软考高项笔记:项目管理概述

以下是不同组织结构中项目经理的角色、工作特点以及快速记忆的方法: 不同组织结构中项目经理的角色和工作特点 组织结构项目经理的角色工作特点职能型组织项目协调者、辅助管理者权力有限,主要负责协调部门间的工作,项目成员向部门经理汇报…...

Vue3的Composition API与React Hooks有什么异同?

Vue3的一个重大更新点就是支持Composition API,而且也被业界称为hooks,那么Vue3的“Hooks”与React的Hooks有这么区别呢? 一、核心相似点 1. 逻辑复用与代码组织 都解决了传统类组件或选项式 API 中逻辑分散的问题,允许将相关逻…...

LangChain4j(1):初步认识Java 集成 LLM 的技术架构

LangChain 作为构建具备 LLM 能力应用的框架,虽在 Python 领域大放异彩,但 Java 开发者却只能望洋兴叹。LangChain4j 正是为解决这一困境而诞生,它旨在借助 LLM 的强大效能,增强 Java 应用,简化 LLM 功能在Java应用中的…...

JDK 21 的新特性有哪些?带你全面解读 Java 的未来

引言:从 JDK 21 看 Java 的进化之路 Java 是一门历久弥新的语言,每一次版本更新都在强化它的生态体系。2023 年发布的 JDK 21,作为长期支持版本(LTS),带来了许多令人兴奋的新特性。不论你是开发者、架构师…...

【C++算法】53.链表_重排链表

文章目录 题目链接:题目描述:解法C 算法代码: 题目链接: 143. 重排链表 题目描述: 解法 模拟 找到链表的中间节点 快慢双指针 把后面的部分逆序 双指针,三指针,头插法 合并两个链表 合并两个有…...

多卡分布式训练:torchrun --nproc_per_node=5

多卡分布式训练:torchrun --nproc_per_node=5 1. torchrun 实现规则 torchrun 是 PyTorch 提供的用于启动分布式训练作业的实用工具,它基于 torch.distributed 包,核心目标是简化多进程分布式训练的启动和管理。以下是其主要实现规则: 进程启动 多进程创建:torchrun 会…...

系统架构设计师之系统设计模块笔记

一、系统设计概述 定义与目标 系统设计是根据系统分析结果,制定系统构建蓝图的过程,核心目标是合理分配功能需求、优化资源使用、确保系统高内聚低耦合,并满足性能、安全、可扩展等非功能需求。主要内容 概要设计:将功能需求分配…...

Elasticsearch:加快 HNSW 图的合并速度

作者:来自 Elastic Thomas Veasey 及 Mayya Sharipova 过去,我们曾讨论过搜索多个 HNSW 图时所面临的一些挑战,以及我们是如何缓解这些问题的。当时,我们也提到了一些计划中的改进措施。本文正是这项工作的成果汇总。 你可能会问…...

图片中文字无法正确显示的解决方案

图片中文字无法正确显示的解决方案 问题描述 在 Linux 系统中生成图片时,图片中的文字(如中文)未能正确显示,可能表现为乱码或空白。这通常是由于系统缺少对应的字体文件(如宋体/SimSun),或者…...

数据结构:通俗解释AOE 网中事件的最早发生时间和最迟发生时间

1. 事件的最早发生时间 在 AOE 网(Activity On Edge Network,边表示活动的网络)中,事件的最早发生时间指从源点(起点)到该事件结点的最长路径长度(即所需时间)。它决定了所有以该事…...

C# 看门狗策略实现

using System; using System.Threading;public class Watchdog {private Timer _timer;private volatile bool _isTaskAlive;private readonly object _lock new object();private const int CheckInterval 5000; // 5秒检测一次private const int TimeoutThreshold 10000; …...

操作系统上添加 ollama 作为系统服务的步骤)

在 openEuler 24.03 (LTS) 操作系统上添加 ollama 作为系统服务的步骤

以下是在 openEuler 操作系统上添加 ollama 作为系统服务的步骤: 创建 systemd 服务文件 sudo vi /etc/systemd/system/ollama.service将以下内容写入服务文件(按需修改参数): [Unit] DescriptionOllama Service Afternetwork.…...

Elasticsearch中的基本全文搜索和过滤

Elasticsearch中的基本全文搜索和过滤 知识点参考: https://www.elastic.co/guide/en/elasticsearch/reference/current/full-text-filter-tutorial.html#full-text-filter-tutorial-range-query 1. 索引设计与映射 多字段类型(Multi-Fields) ÿ…...

基于VSCode的Qt开发‘#include ui_test.h’报错没有该文件

笔者在基于VSCode进行Qt开发时,test.ui文件是在Qt软件中绘制的,导致本项目无法使用这个ui文件,报错如标题。事实上,本工程中也确实没有生成这个头文件。出现这个错误的原因是ui文件没有被编译为c头文件。 要生成 ui_test.h 文件&…...

Python常用排序算法

1. 冒泡排序 冒泡排序是一种简单的排序算法,它重复地遍历要排序的列表,比较相邻的元素,如果他们的顺序错误就交换他们。 def bubble_sort(arr):# 遍历所有数组元素for i in range(len(arr)):# 最后i个元素是已经排序好的for j in range(0, …...

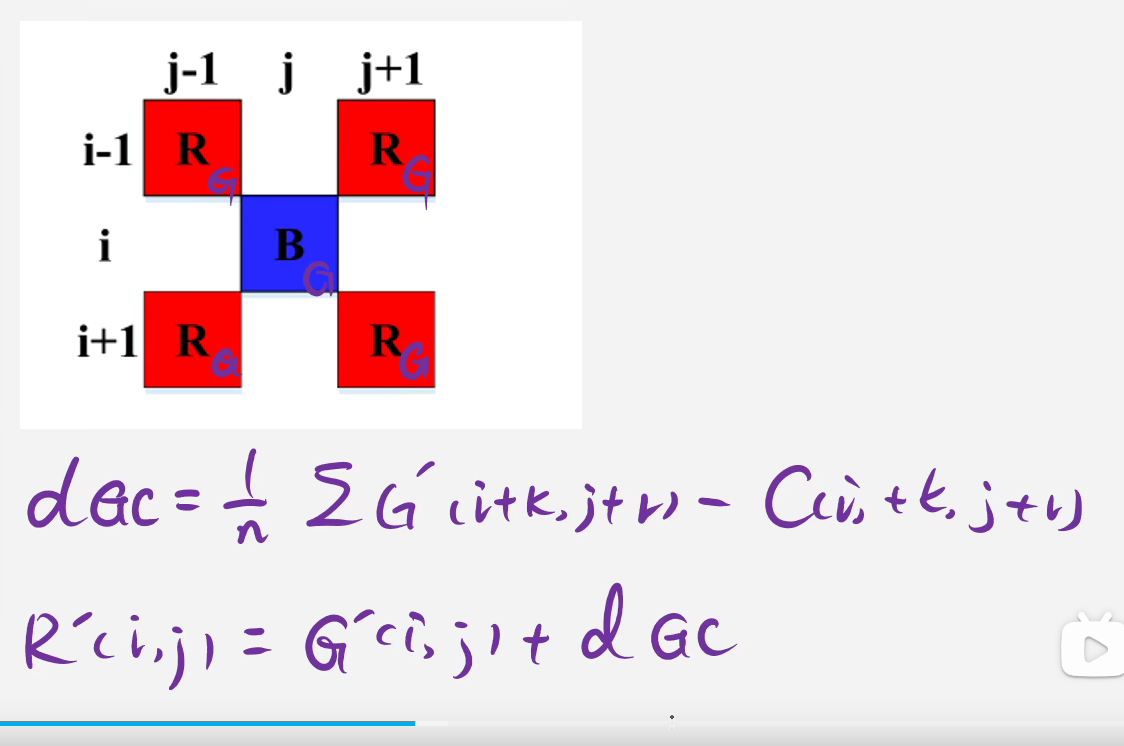

ISP--Demosaicking

文章目录 前言算法解释简单的线性插值代码实现 色差法和色比法基于方向加权的方法RB缺失的G通道的插值RB缺失的BR的插值G缺失的BR的插值代码实现 基于边缘检测的方法计算缺失的G计算缺失的RB值/计算缺失的G值 前言 人眼之所以有能感受到自然界的颜色,是因为人眼的感…...

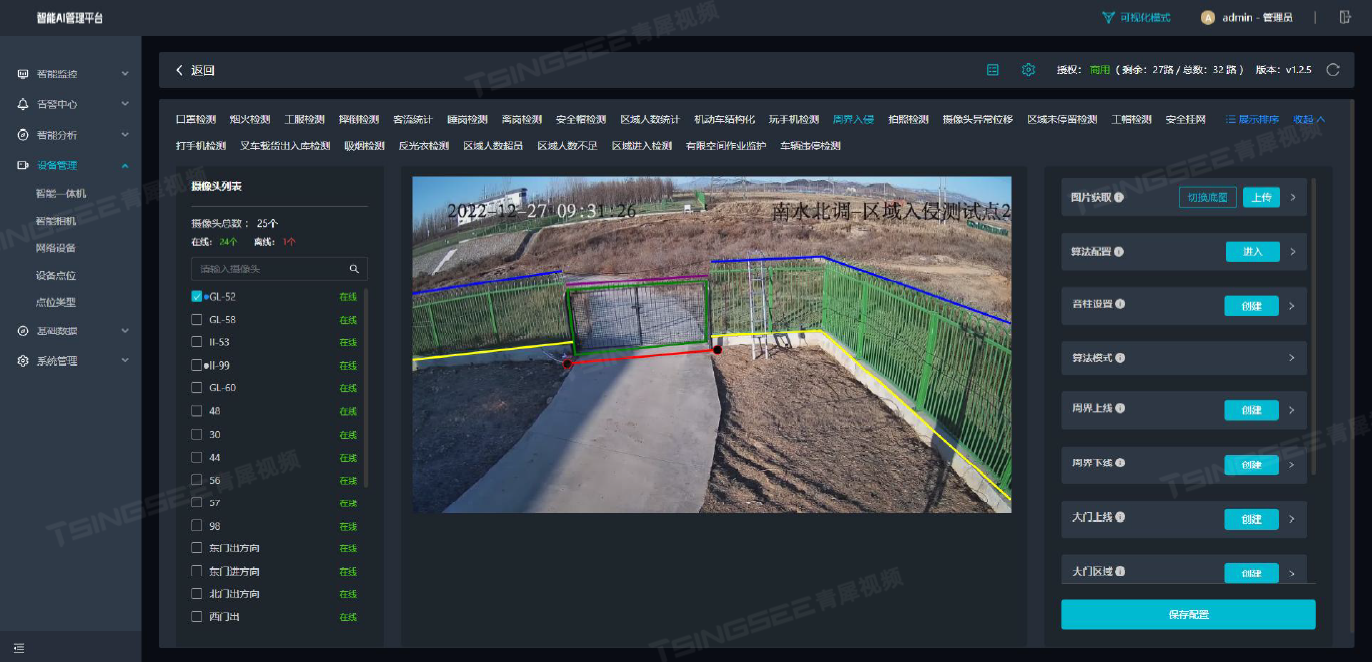

国标GB28181协议EasyCVR视频融合平台:5G时代远程监控赋能通信基站安全管理

一、背景介绍 随着移动通信行业的迅速发展,无人值守的通信基站建设规模不断扩大。这些基站大多建于偏远地区,周边人迹罕至、交通不便,给日常的维护带来了极大挑战。其中,位于空旷地带的基站设备,如空调、蓄电池等&…...

vue watch 和 watchEffect的区别和用法

在 Vue.js 里,watch 和 watchEffect 都用于响应式地追踪数据变化并执行相应操作,不过它们在使用方式、应用场景等方面存在差异。 1. watch watch 是 Vue 提供的一个选项,用于监听特定数据的变化。当监听的数据发生变化时,会触发…...

SQL 不走索引的常见情况

在 SQL 查询中,即使表上有索引,某些情况下数据库优化器也可能决定不使用索引。以下是常见的不走索引的情况: 1. 使用否定操作符 NOT IN ! 或 <> NOT EXISTS NOT LIKE 2. 对索引列使用函数或运算 -- 不走索引 SELECT * FROM user…...

git配置 gitcode -- windows 系统

版本 $ git --version git version 2.49.0.windows.1检查现有的 SSH 密钥 打开git-bash终端,执行以下命令查看是否已经生成过 SSH 密钥: ls -al ~/.ssh如果看到类似 id_rsa 和 id_rsa.pub(或者其他命名的密钥对)文件࿰…...

基于Kubeadm实现K8S集群扩缩容指南

一、集群缩容操作流程 1.1 缩容核心步骤 驱逐节点上的Pod 执行kubectl drain命令驱逐节点上的Pod,并忽略DaemonSet管理的Pod: kubectl drain <节点名> --ignore-daemonsets # 示例:驱逐worker233节点 kubectl drain worker233 --ignor…...

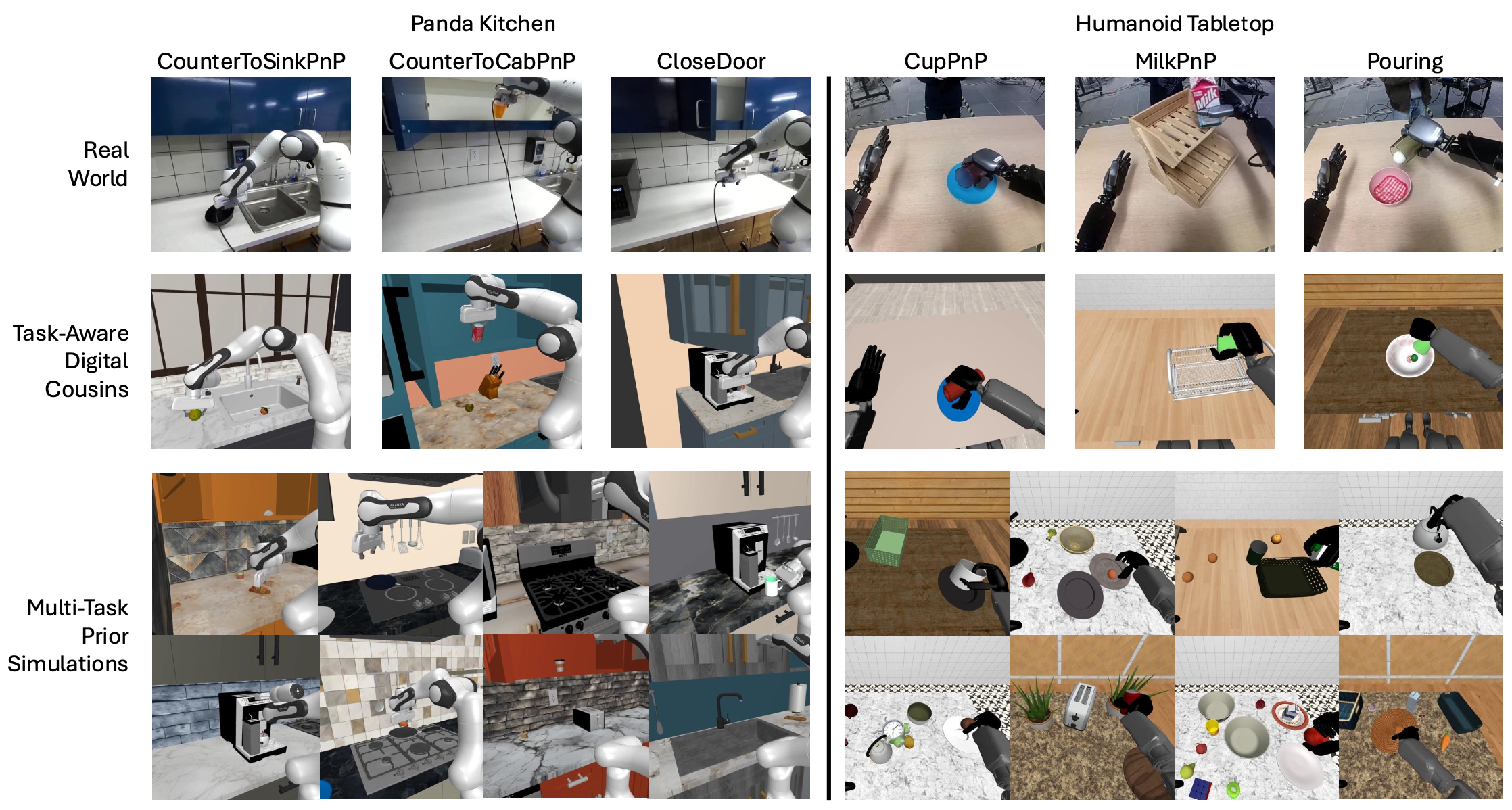

模拟-与-现实协同训练:基于视觉机器人操控的简单方法

25年3月来自 UT Austin、Nvidia、UC Berkeley 和纽约大学的论文“Sim-and-Real Co-Training: A Simple Recipe for Vision-Based Robotic Manipulation”。 大型现实世界机器人数据集在训练通才机器人模型方面拥有巨大潜力,但扩展现实世界人类数据收集既耗时又耗资…...