【数字IC设计】VCS仿真DesignWare IP

DesignWare介绍

DesignWare是SoC/ASIC设计者最钟爱的设计IP库和验证IP库。它包括一个独立于工艺的、经验证的、可综合的虚拟微架构的元件集合,包括逻辑、算术、存储和专用元件系列,超过140个模块。DesignWare和 Design Compiler的结合可以极大地改进综合的结果,并缩短设计周期。Synopsys在DesignWare中还融合了更复杂的商业IP(无需额外付费)目前已有:8051微控制器、PCI、PCI-X、USB2.0、MemoryBIST、AMBA SoC结构仿真、AMBA总线控制器等IP模块。

DesignWare中还包括一个巨大的仿真模型库,其中包括170,000多种器件的代时序的功能级仿真模型,包括FPGAs (Xilinx, Altera,…), uP, DSP, uC, peripherals, memories, common logic, Memory等。还有总线(Bus-Interface)模型PCI-X, USB2.0, AMBA, Infiniband, Ethernet, IEEE1394等,以及CPU的总线功能仿真模型包括ARM, MIPS, PowerPC等。

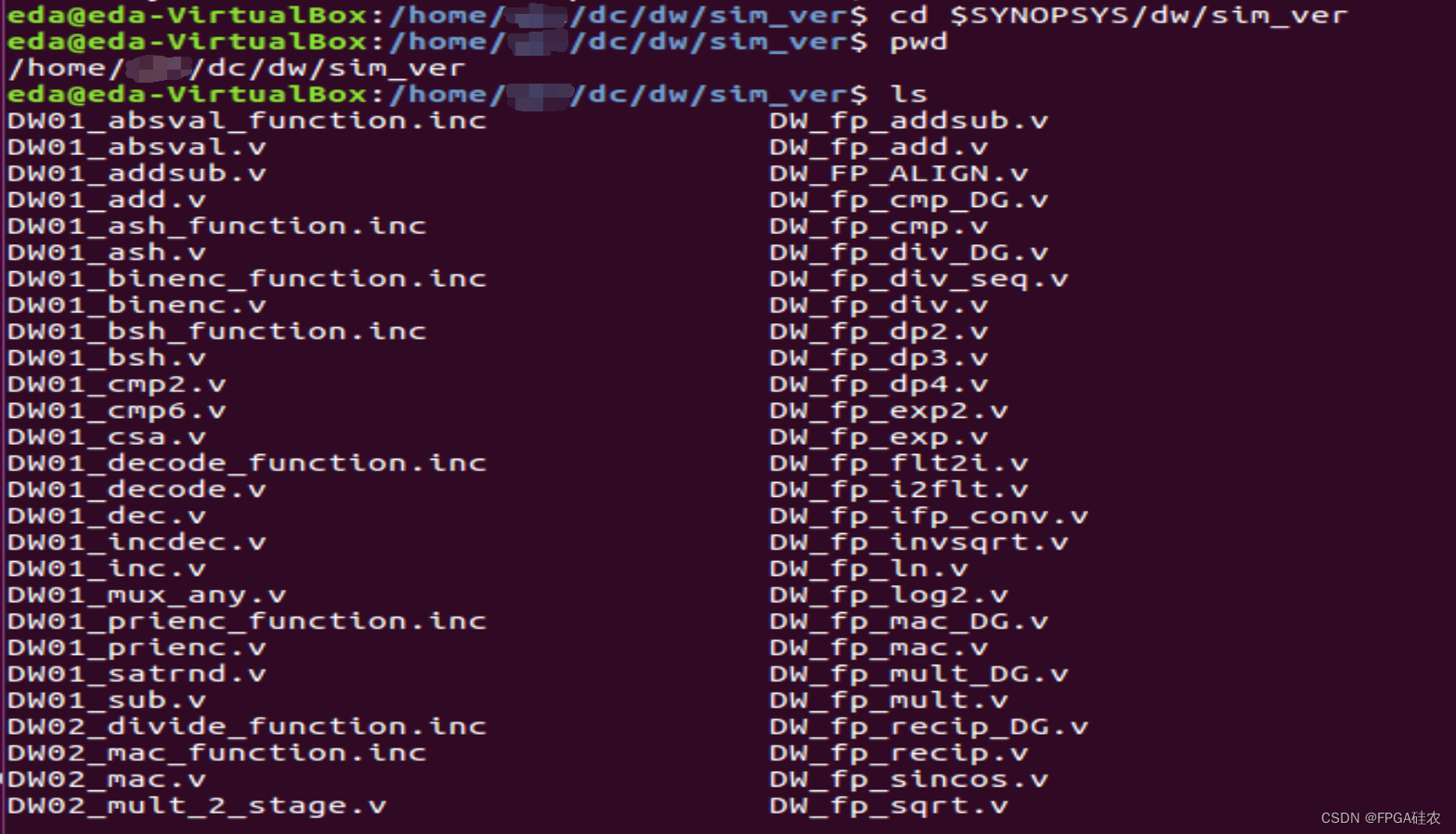

如上图所示,在安装了DC综合工具后,我们可以在$SYNOPSYS/dw/sim_ver路径下找到Design Ware的仿真库文件。

下面以举两个例子,来说明如何在vcs仿真中使用dw ip库。

ram仿真

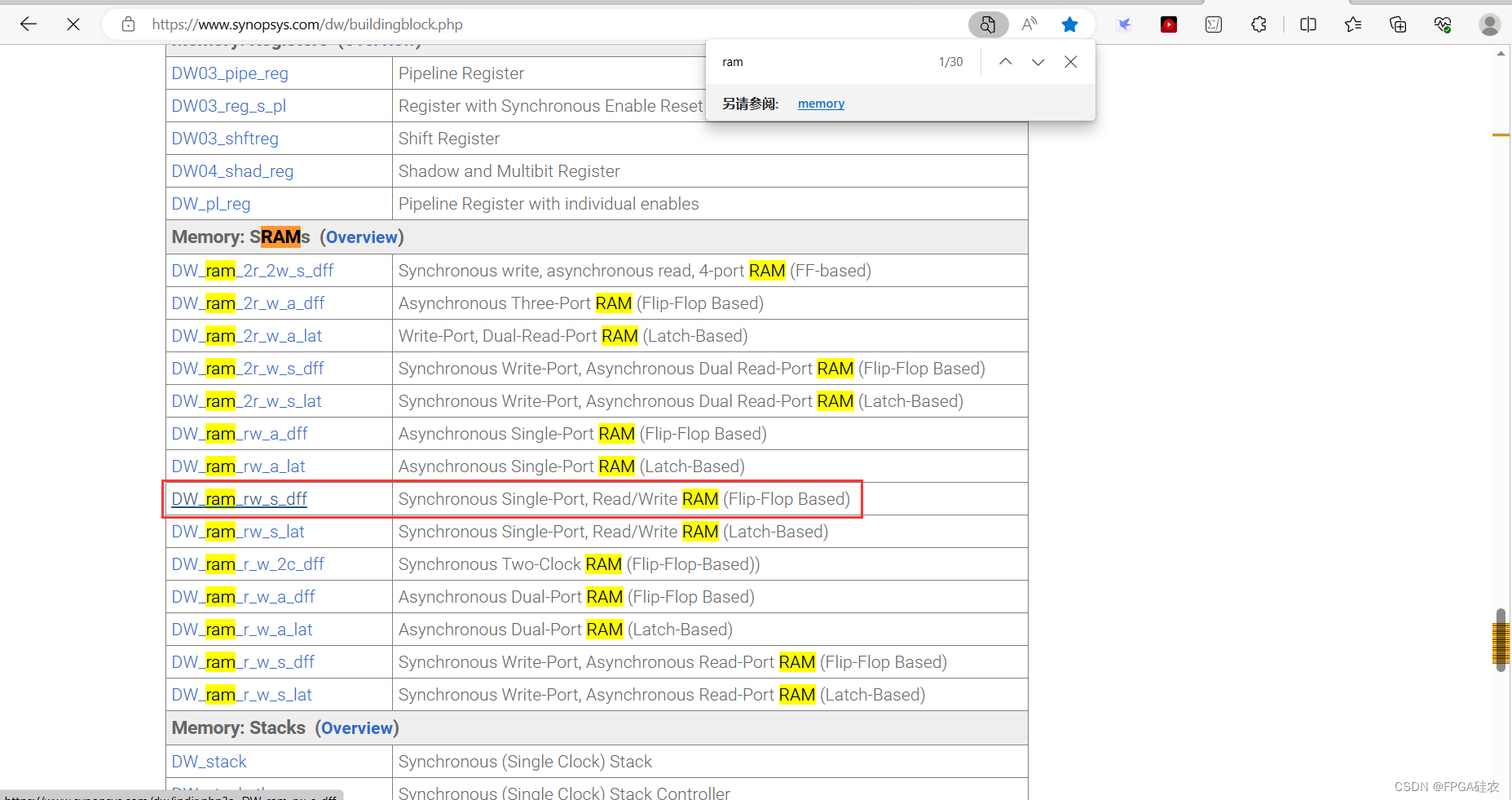

打开网站链接,搜索并找到下图所示的ram ip核。

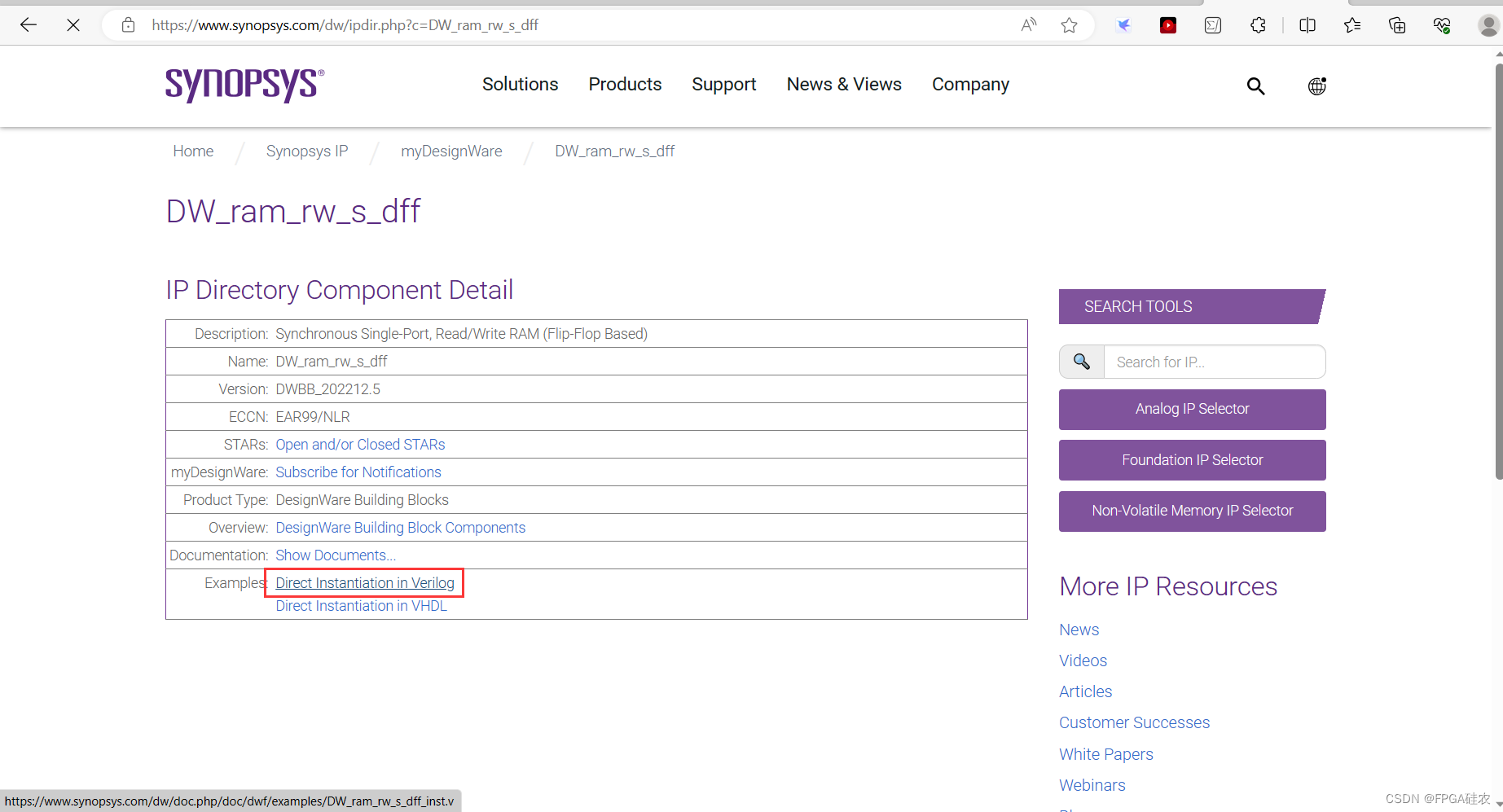

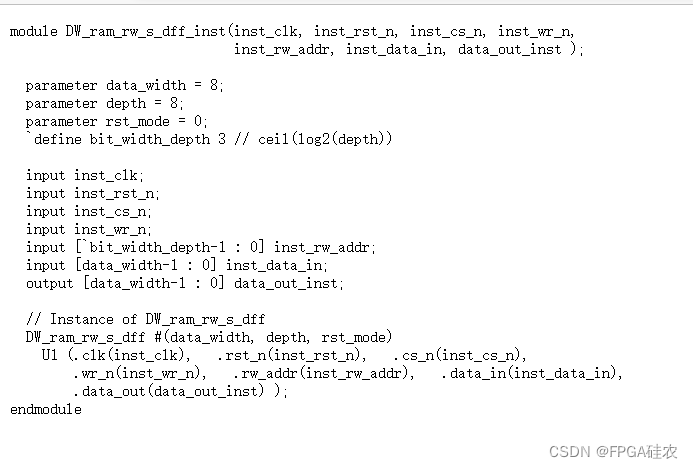

点击下图所示区域,得到例化该IP核的示例代码:

编写测试代码如下:

module test;

parameter DATA_WIDTH = 8;

parameter DEPTH = 8;

parameter ADDR_WIDTH = $clog2(DEPTH);

parameter RST_MODE = 0;

//signal define

reg clk;

reg rst_n;

reg cs_n;

reg wr_n;

reg wr_busy;

reg start;

reg [2:0] rw_addr;

reg [DATA_WIDTH-1:0] data_in;

wire [DATA_WIDTH-1:0] data_out;

wire done;

//clk generate

initial beginclk = 1'b0;forever begin#5 clk = ~clk;end

end

//reset and chip enable

initial beginrst_n = 1'b0;cs_n = 1'b1; #100cs_n = 1'b0;rst_n = 1'b1;

end

//start generate

initial beginstart = 1'b0;#123start = 1'b1;#10start = 1'b0;

end

always@(posedge clk or negedge rst_n) beginif(~rst_n) beginwr_busy <= 1'b0;endelse if(start) beginwr_busy <= 1'b1;endelse if(wr_busy && rw_addr == DEPTH-1) beginwr_busy <= 1'b0;end

end

//wr_n, write enable

always@(posedge clk or negedge rst_n) beginif(~rst_n) beginwr_n <= 1'b1;endelse if(start) beginwr_n <= 1'b0;endelse if(wr_busy) beginif(rw_addr == DEPTH-1) beginwr_n <= 1'b1;endelse beginwr_n <= 1'b0;endend

end

//rw_addr

always@(posedge clk or negedge rst_n) beginif(~rst_n) beginrw_addr <= 0;endelse if(start) beginrw_addr <= 0;endelse if(wr_busy) beginrw_addr <= rw_addr + 1'b1;endelse if(rw_addr!=DEPTH-1) beginrw_addr <= rw_addr + 1'b1;end

end

//data_in

always@(posedge clk or negedge rst_n) beginif(~rst_n) begindata_in <= 0;endelse if(wr_busy) begindata_in <= data_in + 8'd3;end

end

assign done = (wr_n == 1'b1 && rw_addr == DEPTH-1) ? 1'b1 : 1'b0;

//

initial begin$fsdbDumpfile("ram.fsdb");$fsdbDumpvars(0);

end

initial begin#1000$finish;

end

//ram inst

DW_ram_rw_s_dff_inst U

(.inst_clk(clk),.inst_rst_n(rst_n),.inst_cs_n(cs_n),.inst_wr_n(wr_n),.inst_rw_addr(rw_addr),.inst_data_in(data_in),.data_out_inst(data_out)

);

endmodule

编写makefile脚本如下:

all: listfile com sim verdi cleanlistfile:find -name "*.v" > filelist.fcom:vcs -full64 -cpp g++-4.8 -cc gcc-4.8 -LDFLAGS -Wl,--no-as-needed -sverilog -debug_access -timescale=1ns/10ps \-f filelist.f -l com.log -kdb -lca -y ${SYNOPSYS}/dw/sim_ver +libext+.vsim:./simv -l sim.logverdi:verdi -f filelist.f -ssf *.fsdb -nologo &clean:rm -rf csrc *.log *.key *simv* *.vpd *DVE*rm -rf verdiLog *.fsdb *.bak *.conf *.rc *.f其中,make com加入了选项:

-y ${SYNOPSYS}/dw/sim_ver +libext+.v

这里,-y lib_dir用于指定搜索模块定义的verilog库目录; 在源代码中找不到相应模块或UDP定义的模块时,在定义的目录中查找对应的文件; +libext与-y配合,用来指定查找的文件的后缀,例如+libext+.v表示查找.v文件。

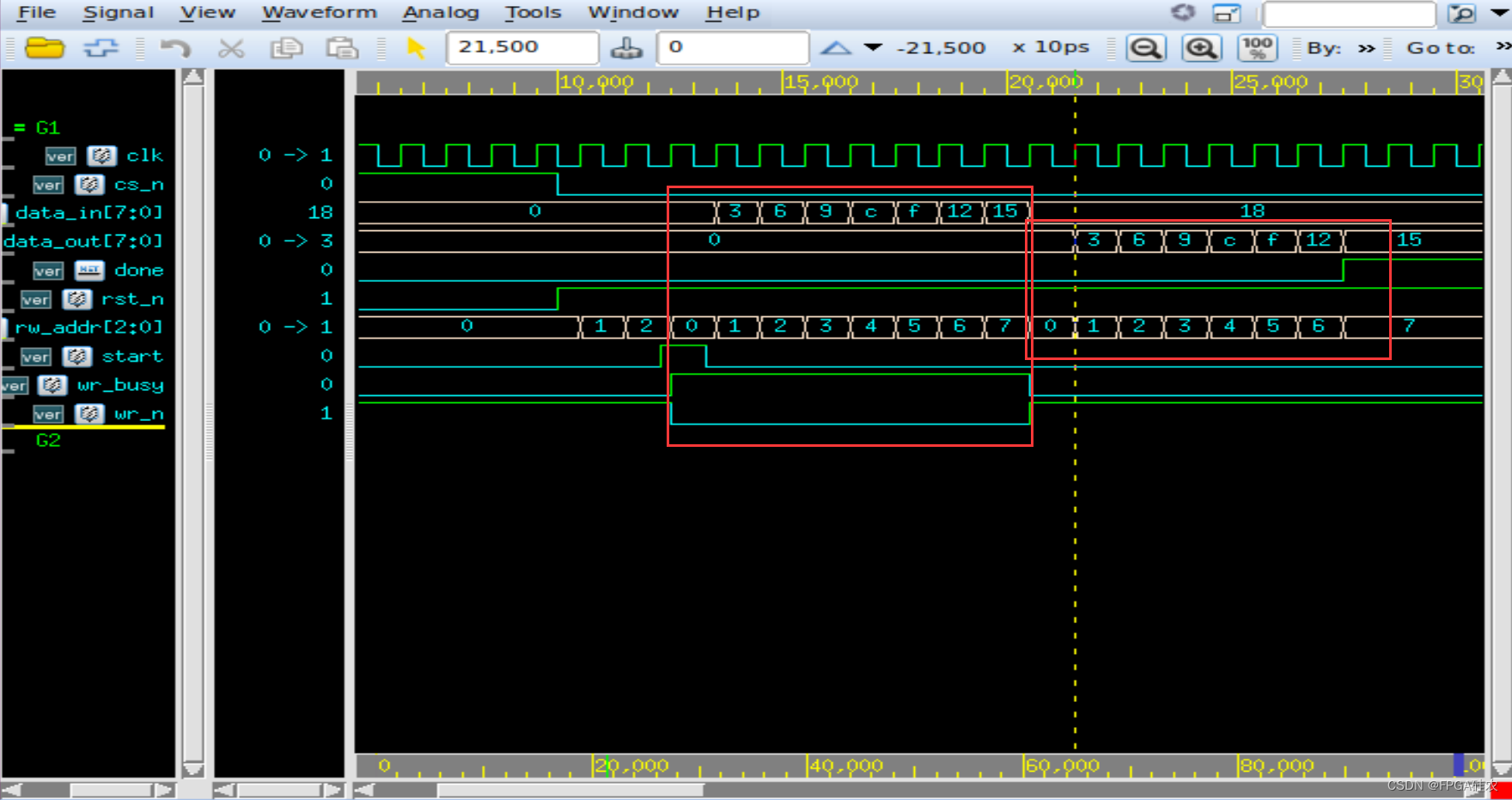

仿真结果如下图所示:

仿真bin2gray

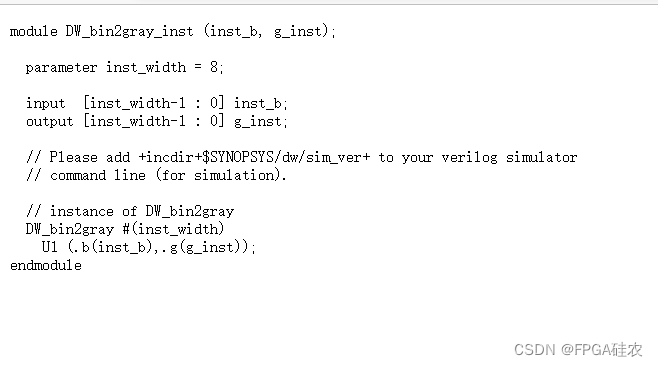

按照仿真ram相同的步骤操作,得到例化该模块的示例代码:

需要注意的是,在例化该模块时,需要加入+incdir+$SYNOPSYS/dw/sim_ver+编译选项,这是因为在使用该IP的时候还需要用到相关的inc文件。

代码:

module test;

parameter DATA_WIDTH = 8;

reg [DATA_WIDTH-1:0] bin;

wire [DATA_WIDTH-1:0] gray;initial beginbin = 8'd0;forever begin#10 bin = $urandom % 256;end

end

initial begin$fsdbDumpfile("top.fsdb");$fsdbDumpvars(0);

end

initial begin#1000$finish;

endDW_bin2gray_inst U

(.inst_b(bin ),.g_inst(gray )

);

endmodule

makefile文件:

all: listfile com sim verdi cleanlistfile:find -name "*.v" > filelist.fcom:vcs -full64 -cpp g++-4.8 -cc gcc-4.8 -LDFLAGS -Wl,--no-as-needed -sverilog -debug_access -timescale=1ns/10ps \-f filelist.f -l com.log -kdb -lca -y ${SYNOPSYS}/dw/sim_ver +libext+.v +incdir+${SYNOPSYS}/dw/sim_ver+sim:./simv -l sim.logverdi:verdi -f filelist.f -ssf *.fsdb -nologo &clean:rm -rf csrc *.log *.key *simv* *.vpd *DVE*rm -rf verdiLog *.fsdb *.bak *.conf *.rc *.f可以看到,在仿真该IP的时候,不仅加入了-y ${SYNOPSYS}/dw/sim_ver +libext+.v编译选项,还加入了+incdir+${SYNOPSYS}/dw/sim_ver+选项。这里,+incdir+dir1+dir2+…用于vcs从指定的目录当中查找源文件中所包含的include文件。

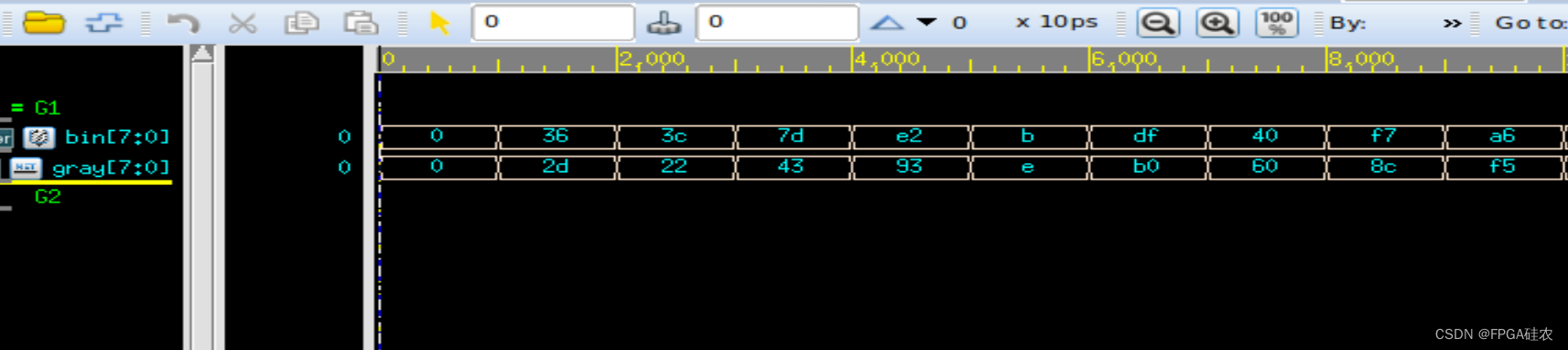

仿真结果如下:

相关文章:

【数字IC设计】VCS仿真DesignWare IP

DesignWare介绍 DesignWare是SoC/ASIC设计者最钟爱的设计IP库和验证IP库。它包括一个独立于工艺的、经验证的、可综合的虚拟微架构的元件集合,包括逻辑、算术、存储和专用元件系列,超过140个模块。DesignWare和 Design Compiler的结合可以极大地改进综合…...

【*1900 图论+枚举思想】CF1328 E

Problem - E - Codeforces 题意: 思路: 注意到题目的性质:满足条件的路径个数是极少的,因为每个点离路径的距离<1 先考虑一条链,那么直接就选最深那个点作为端点即可 为什么,因为我们需要遍历所有点…...

10.5-通信管理模块)

AutoSAR系列讲解(实践篇)10.5-通信管理模块

目录 一、ComM 1、内部唤醒 2、外部唤醒 二、CanSM 三、状态关联 之前讲解了BswM和EcuM,详细讲解了BswM的配置,而大部分的配置都在BswM中做了,EcuM的配置就很简单了,基本上勾一勾就ok了。下面我们 来讲解模式管理还可能用到的通信模块 一、ComM ComM就像一个通信的总…...

)

2023.7.30(epoll实现并发服务器)

服务器 #include <arpa/inet.h> #include <netinet/in.h> #include <netinet/ip.h> #include <stdio.h> #include <stdlib.h> #include <string.h> #include <sys/epoll.h> #include <sys/socket.h> #include <sys/types.…...

)

小研究 - 基于解析树的 Java Web 灰盒模糊测试(一)

由于 Java Web 应用业务场景复杂, 且对输入数据的结构有效性要求较高, 现有的测试方法和工具在测试Java Web 时存在测试用例的有效率较低的问题. 为了解决上述问题, 本文提出了基于解析树的 Java Web 应用灰盒模糊测试方法. 首先为 Java Web 应用程序的输入数据包进行语法建模创…...

SpringBoot接手JSP项目--【JSB项目实战】

SpringBoot系列文章目录 SpringBoot知识范围-学习步骤【JSB系列之000】 文章目录 SpringBoot系列文章目录[TOC](文章目录) SpringBoot技术很多很多工作之初,面临JSP的老项目我要怎么办环境及工具:项目里可能要用到的技术JSPjstl其它的必要知识 上代码WE…...

Python模块psycopg2连接postgresql

目录 1. 基础语法 2. 基础用法 3. 多条SQL 4. 事务SQL 1. 基础语法 语法 psycopg2.connect(dsn #指定连接参数。可以使用参数形式或 DSN 形式指定。host #指定连接数据库的主机名。dbname #指定数据库名。user #指定连接数据库使用的用户名。…...

Kotlin基础(八):泛型

前言 本文主要讲解kotlin泛型,主要包括泛型基础,类型变异,类型投射,星号投射,泛型函数,泛型约束,泛型在Android中的使用。 Kotlin文章列表 Kotlin文章列表: 点击此处跳转查看 目录 1.1 泛型基…...

环境变量path配置及其作用)

Java学习笔记——(10)环境变量path配置及其作用

环境变量的作用为了在 Dos 的任务目录,可以去使用 javac 和 java开发工具命令 先配置 JAVA_HOME 指向 jdk 安装的主目录(避免开发中出现问题) 编辑 path 环境变量(开发环境),增加 %JAVA_HOME%\bin 编辑 path 环境变量(运行环境…...

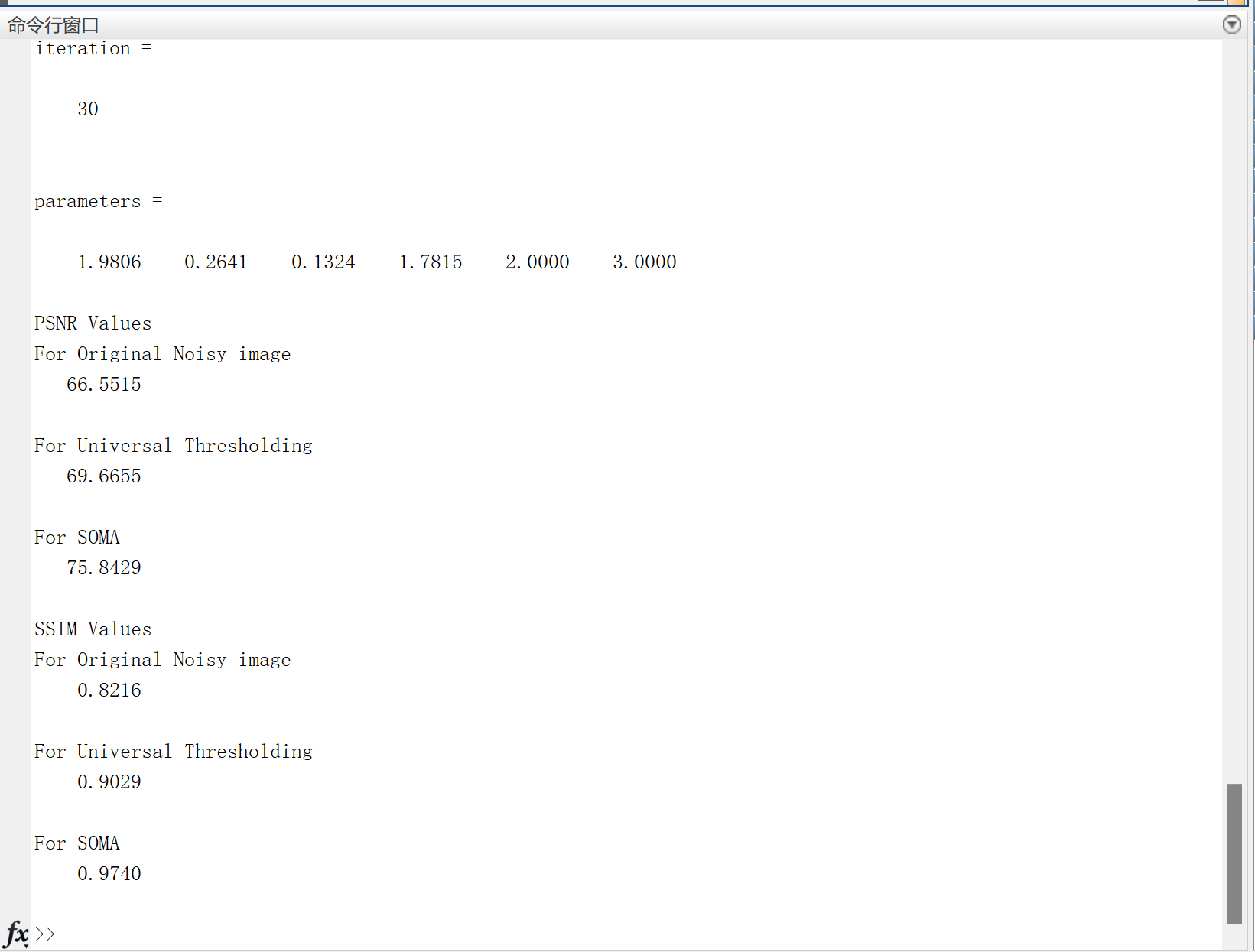

【图像去噪】基于进化算法——自组织迁移算法(SOMA)的图像去噪研究(Matlab代码实现)

💥💥💞💞欢迎来到本博客❤️❤️💥💥 🏆博主优势:🌞🌞🌞博客内容尽量做到思维缜密,逻辑清晰,为了方便读者。 ⛳️座右铭&a…...

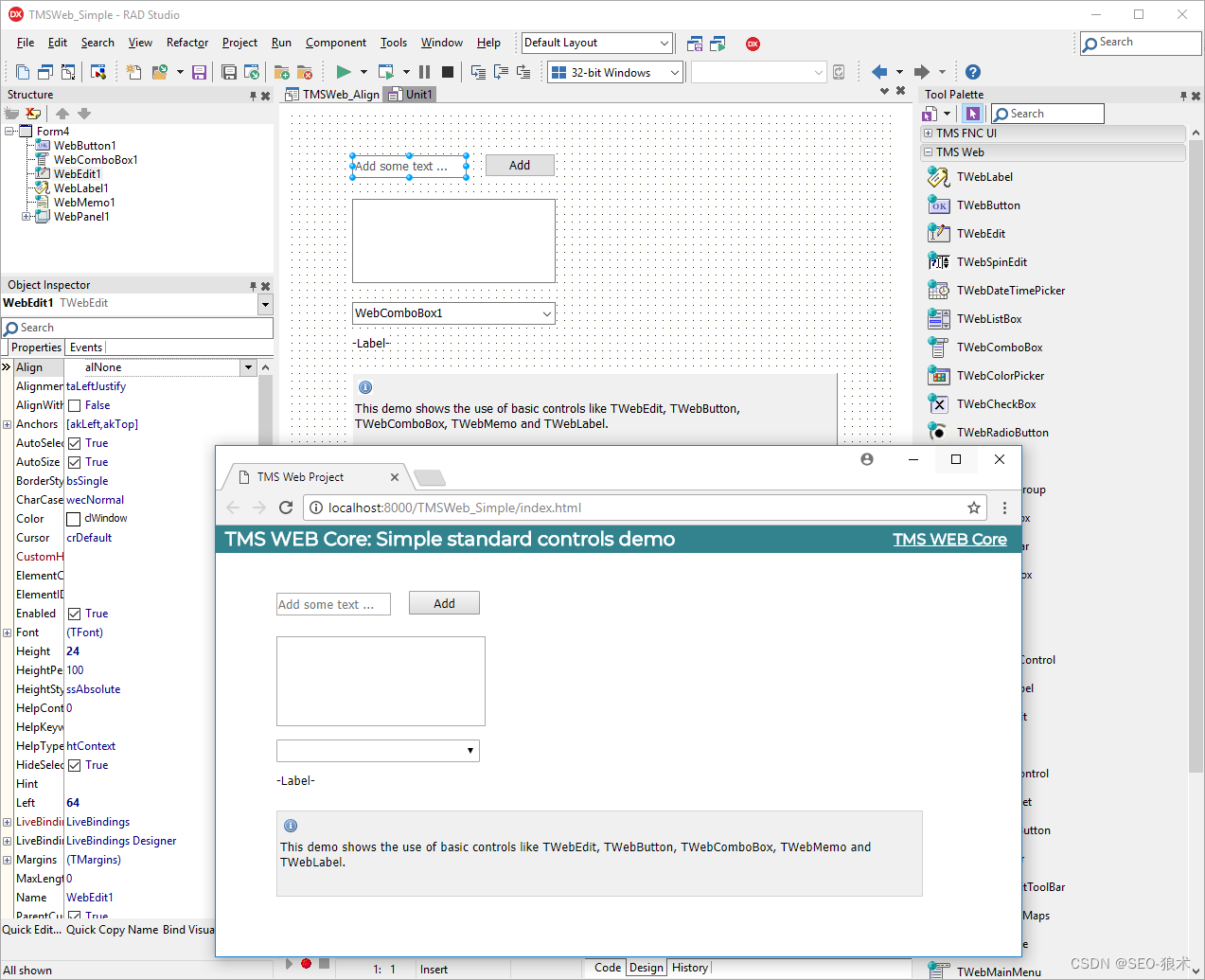

TMS WEB Core Crack,TMS软件Delphi组件RADical Web

TMS WEB Core Crack,TMS软件Delphi组件RADical Web 使用我们的现代web应用程序框架,可以节省宝贵的时间并创造丰富的用户体验。我们所有的工具都由经验丰富的开发人员组成的专门团队提供支持。您可以信赖卓越的服务、活跃的社区和我们不断的创新。TMS Software是您的…...

PHP使用Redis实战实录4:单例模式和面向过程操作redis的语法

PHP使用Redis实战实录系列 PHP使用Redis实战实录1:宝塔环境搭建、6379端口配置、Redis服务启动失败解决方案PHP使用Redis实战实录2:Redis扩展方法和PHP连接Redis的多种方案PHP使用Redis实战实录3:数据类型比较、大小限制和性能扩展PHP使用Re…...

解决:移动端H5的<video>初始化拿不到总时长

移动端 在<video>的初始化后,会调用如下事件。 canplay"canplay" 解决方案:<video>添加自动播放属性: autoplay"autoplay" 然后这个方法里,用js在0.01秒后主动关闭播放,接着在0.…...

百度云上传身份证获取身份信息封装

1.目录结构 -script_discerm ------------包 -discerm.py --------------主要逻辑 -__init__.py -id_care---------------文件夹 存放图片 2.安装模块 pip install urllib31.23 pip install requests pip install base64 3.各文件内容 2.1 discerm.py import jsonimpo…...

vscode 上cmake 版本过低

问题: 装了vscode中的camke插件后,报错如下: CMake 3.9 or higher is required. You are running version 3.3.2。 解决办法: 卸载掉插件的cmake。 到官网下载合适的版本,设置系统变量 然后重新下载camke tools&…...

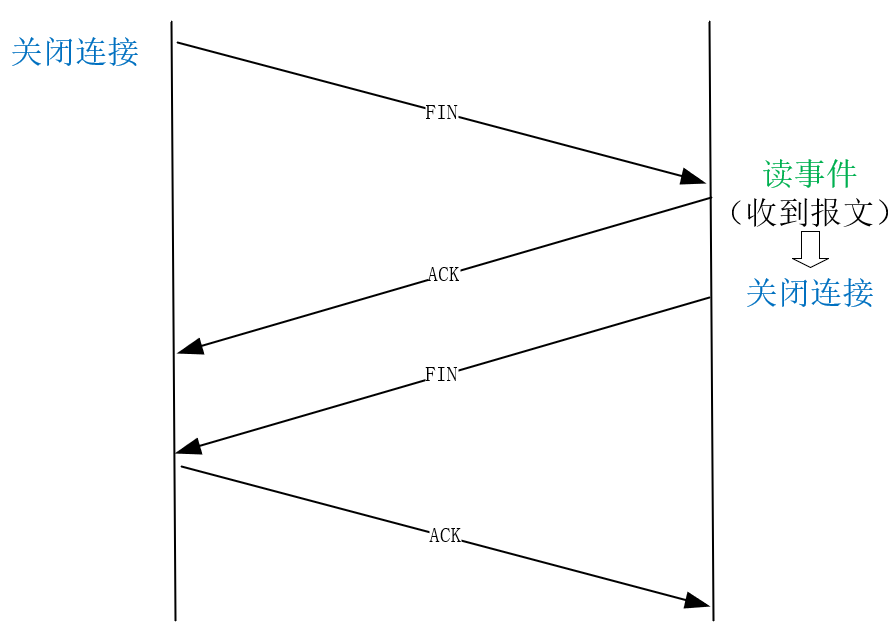

OS-08-事件驱动:C10M是如何实现的?

08-事件驱动:C10M是如何实现的? 你好,我是陶辉。 上一讲介绍了广播与组播这种一对多通讯方式,从这一讲开始,我们回到主流的一对一通讯方式。 早些年我们谈到高并发,总是会提到C10K,这是指服务…...

mysql 主从同步排查和处理 Slave_IO、Slave_SQL

目录 查看主从是否同步 详解Slave_IO、Slave_SQL 判断主从完全同步 各个 Log_File 和 Log_Pos的关系 修复命令 查看主从是否同步 show slave status; Slave_IO_Running、Slave_SQL_Running,这两个值是Yes表示正常,No是异常 使用竖排显示…...

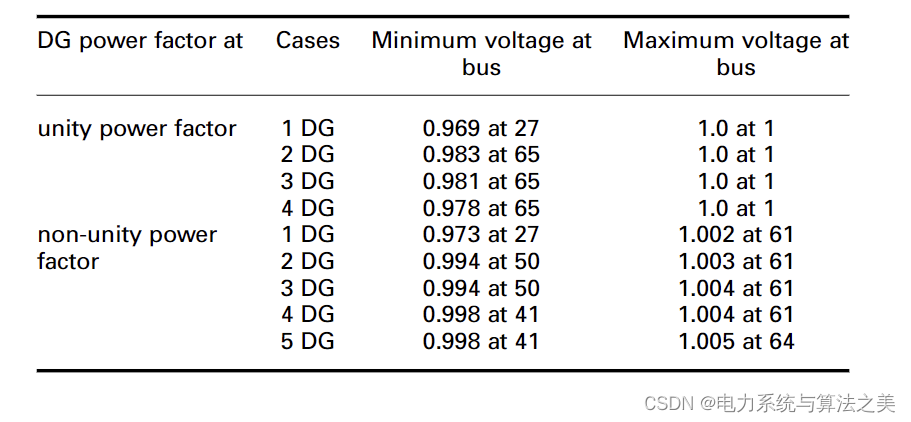

基于解析法和遗传算法相结合的配电网多台分布式电源降损配置(Matlab实现)

目录 1 概述 2 数学模型 2.1 问题表述 2.2 DG的最佳位置和容量(解析法) 2.3 使用 GA 进行最佳功率因数确定和 DG 分配 3 仿真结果与讨论 3.1 33 节点测试配电系统的仿真 3.2 69 节点测试配电系统仿真 4 结论 1 概述 为了使系统网损达到最低值&a…...

07mysql查询语句之子查询

#1.查询和Zlotkey相同部门的员工姓名和工资 SELECT last_name,salary FROM employees WHERE department_id IN ( SELECT department_id FROM employees WHERE last_name Zlotkey ); #2.查询工资比公司平均工资高的员工的员工号࿰…...

)

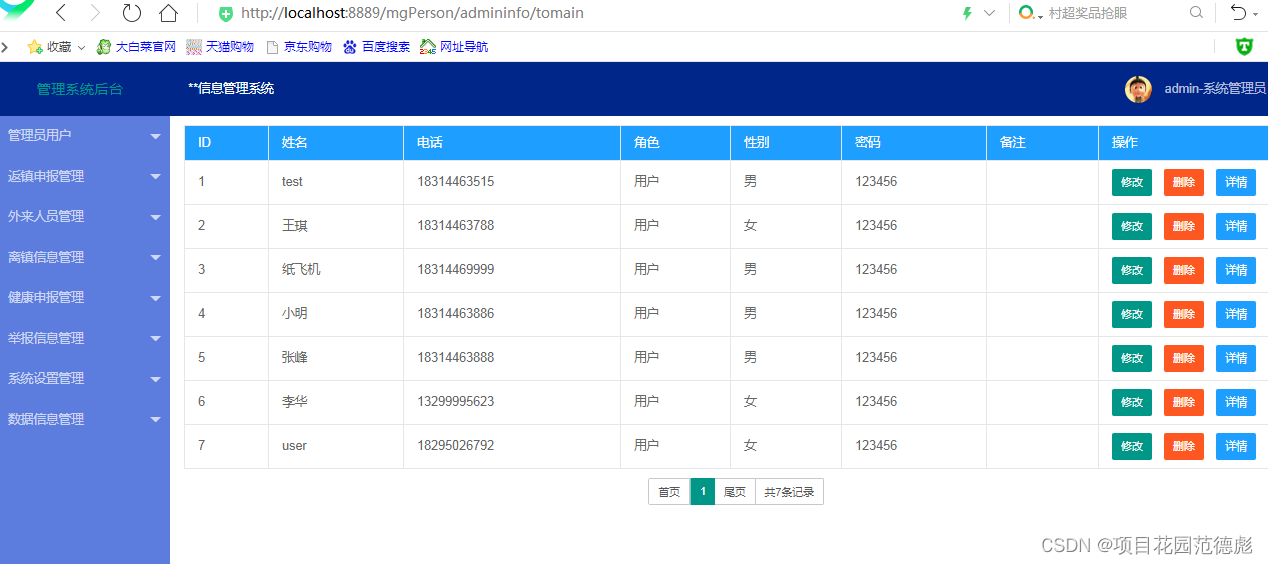

笙默考试管理系统-MyExamTest(22)

笙默考试管理系统-MyExamTest(22) 目录 一、 笙默考试管理系统-MyExamTest 二、 笙默考试管理系统-MyExamTest 三、 笙默考试管理系统-MyExamTest 四、 笙默考试管理系统-MyExamTest 五、 笙默考试管理系统-MyExamTest 笙默考试管理系统-MyExa…...

三星 Infinite AI 葡萄酒冰箱:智能厨房新尝试能否突围?

AI 加持,葡萄酒管理新体验周一,三星推出了 Infinite AI 葡萄酒冰箱,目前仅在韩国有售。这款冰箱采用了“AI 葡萄酒管理器”,借助安装在顶部的“AI 视觉”摄像头,能检测用户放入或取出的酒瓶及位置,还能分析…...

实战构建企业技能评估系统:基于快马平台实现skill-vetter全流程解决方案

实战构建企业技能评估系统:基于快马平台实现skill-vetter全流程解决方案 最近在帮公司搭建内部技能认证系统时,发现传统线下考试方式存在效率低、数据难沉淀的问题。于是尝试用InsCode(快马)平台开发了一套skill-vetter系统,整个过程比想象中…...

探索GetQzonehistory:永久保存QQ空间记忆的数字时光机

探索GetQzonehistory:永久保存QQ空间记忆的数字时光机 【免费下载链接】GetQzonehistory 获取QQ空间发布的历史说说 项目地址: https://gitcode.com/GitHub_Trending/ge/GetQzonehistory 在数字时代,我们的记忆分散在各个社交平台,而Q…...

Qwen2.5-Coder-1.5B应用案例:自动生成Bash脚本处理日志文件

Qwen2.5-Coder-1.5B应用案例:自动生成Bash脚本处理日志文件 1. 日志处理场景与痛点分析 1.1 运维工程师的日常挑战 在服务器运维工作中,日志分析是最常见也最耗时的任务之一。想象一下这样的场景: 你需要检查10台服务器上50个不同的服务日…...

OpenSees数值模拟从入门到进阶:理论、代码与实践

OpenSees数值模拟从入门到进阶:理论、代码与实践 摘要 OpenSees(Open System for Earthquake Engineering Simulation)作为开源的地震工程模拟系统,凭借其强大的非线性分析能力和开放的架构,已成为结构地震响应分析领域的重要工具。本文系统介绍OpenSees数值模拟的基本原…...

告别手速焦虑:大麦抢票神器让你轻松锁定心仪演出

告别手速焦虑:大麦抢票神器让你轻松锁定心仪演出 【免费下载链接】ticket-purchase 大麦自动抢票,支持人员、城市、日期场次、价格选择 项目地址: https://gitcode.com/GitHub_Trending/ti/ticket-purchase 还在为抢不到演唱会门票而烦恼吗&#…...

Phi-4-mini-reasoning效果展示:含单位换算、科学计数法的复合型数学题求解

Phi-4-mini-reasoning效果展示:含单位换算、科学计数法的复合型数学题求解 1. 模型能力概览 Phi-4-mini-reasoning是一款专注于推理任务的文本生成模型,特别擅长处理需要多步逻辑推导的问题。与通用聊天模型不同,它更专注于"问题输入→…...

)

从理论到面包板:手把手搭建Series-Shunt反馈放大器(含阻抗匹配避坑指南)

从理论到面包板:手把手搭建Series-Shunt反馈放大器(含阻抗匹配避坑指南) 在电子工程实践中,反馈放大器设计是模拟电路领域的核心技能之一。Series-Shunt结构因其出色的电压放大特性和相对简单的实现方式,成为初学者入门…...

Delphi网络编程实战:UDP通信与多线程网络优化详解

前两篇文章分别讲解了Delphi中基于Indy组件的TCP点对点通信、HTTP/HTTPS接口交互,覆盖了可靠连接、Web对接两大常用场景。本篇将深入讲解UDP通信,同时补充多线程网络编程、数据传输防护、常见故障排查等进阶内容,补齐Delphi网络开发的核心模块…...

TEA算法逆向实战:从特征识别到脚本魔改的CTF通关指南

1. TEA算法特征快速识别指南 第一次在CTF比赛中遇到TEA算法时,我盯着反编译代码看了半小时都没反应过来。直到后来总结出几个关键特征,现在遇到这类题目基本能在30秒内锁定目标。最明显的标志就是那个魔性的delta常量0x9E3779B9(或者它的补码…...