从零开始 verilog 以太网交换机(三)MAC发送控制器的设计与实现

从零开始 verilog 以太网交换机(三)MAC发送控制器的设计与实现

🔈声明:

😃博主主页:王_嘻嘻的CSDN主页

🧨 从零开始 verilog 以太网交换机系列专栏:点击这里

🔑未经作者允许,禁止转载,侵权必删

🚩关注本专题的朋友们可以收获一个经典交换机设计的全流程,包括设计与验证(FPGA);以太网MAC的基础知识。新手朋友们还将获得一个具有竞争力的项目经历,后续整个工程和代码下载链接也都会放在csdn和公众号内

本章将继续进行MAC发送端控制器的设计与实现,交换机完整的架构可以参考:从零开始 verilog 以太网交换机(一)架构分析。

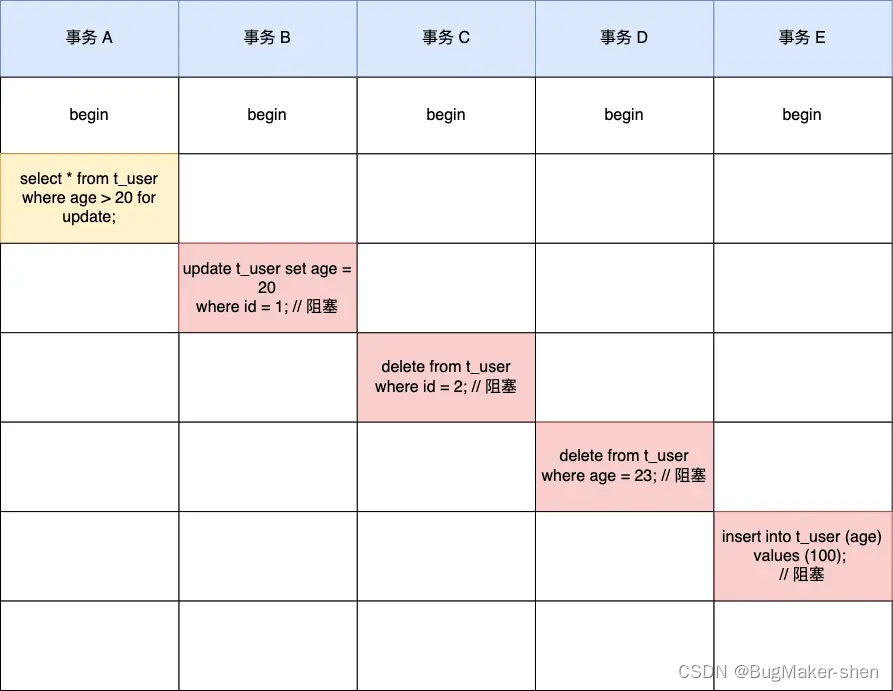

1、MAC发送控制器功能

MAC发送控制器的功能和接收控制器对称,负责以太网的MAC -> PHY的数据交换,将数据帧转换为MII接口形式的数据流,并根据长度进行补零,计算CRC校验等。

其功能包括以下5点:

- 根据以太网规范,先发送前导码,再发送帧起始符(关于前导符和帧起始符的基础知识在第二章中有介绍:MAC接收控制器的设计与实现);

- 之后将Payload(有效荷载)从数据缓冲区读出,并发送;

- 若数据过短,需要填充数据‘0’,使MAC帧长度符合要求;

- 将同步计算的CRC-32校验值发送;

- 当MAC全部发送结束后,需要按照以太网规范插入帧间等待时间,本工程中为24个cycle(时钟周期);

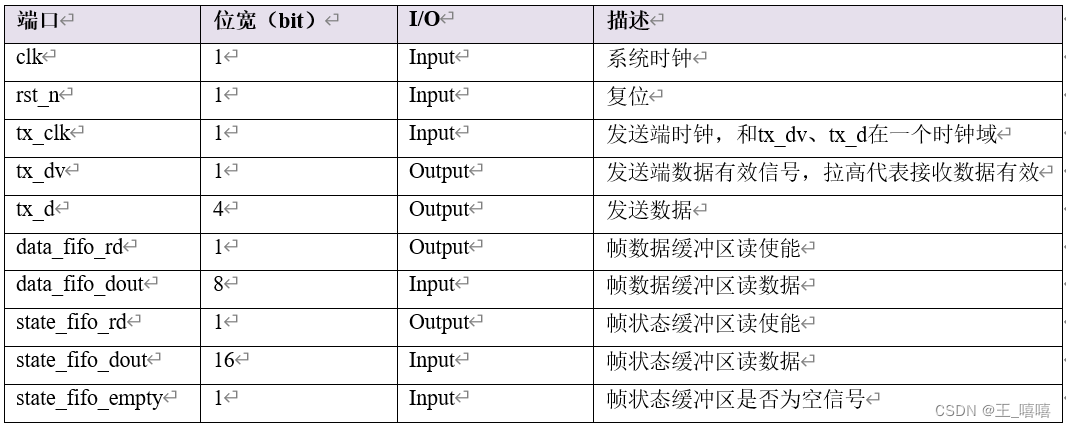

2、MAC发送控制器接口

与接收控制器正好相反,MAC发送控制器一端连接数据缓冲区和状态缓冲区,另一端连接标准MII接口,具体接口如下。

需要注意的是,系统时钟clk和MII发送端时钟tx_clk不同,tx_dv和tx_d需要在tx_clk下控制。

3、MAC发送控制器实现细节

发送控制器需要根据数据帧生成CRC-32校验值,通常CRC的多项式公式可以直接通过生成器来生成。(CRC生成器将放在本号的资源栏中,有需要的可以下载,或者关注博主的公众号,也有下载链接)

AFIFO的格式和结构都与接受控制器的相同,不了解的同学可以回看上一章内容:从零开始 verilog 以太网交换机(一)架构分析。

3.1、功能细节分析

- 检查state_fifo是否为空,若非空,则从state_fifo中取出一个数据,得到需要发送的MAC帧长度信息;

- 发送前导码’0101’(本工程内重复6次)和帧起始符4‘b1011;

- 将data_fifo数据取出发送到MII接口,并同步进行CRC-32的计算,当长度过小时进行填充处理;

- Payload发送完毕后,将CRC-32的计算值一并发送;

- MAC发送结束后,等待帧间隔时间后,继续发送下一帧;

3.3、MAC发送器核心电路设计

由于MAC发送控制器需要制造前导码,在帧尾填充数据,将交换机内部的8-bits数据转换成MII接口的4-bits数据,且系统时钟sys_clk和MII时钟tx_clk异步,所以在该模块中设置了一级用AFIFO实现的中间队列,既便于控制数据通路,又能处理异步时钟域。

所以发送控制器的总体架构如下:

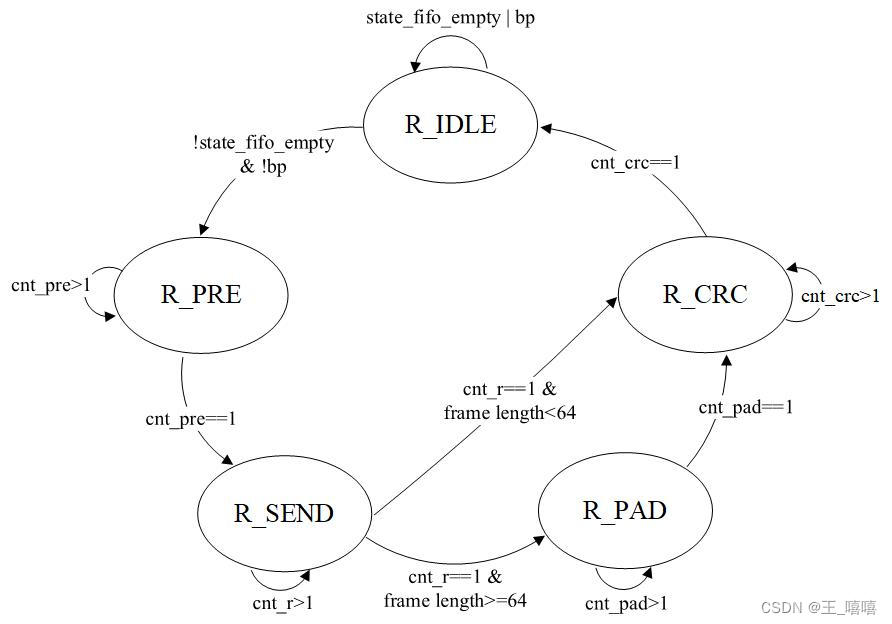

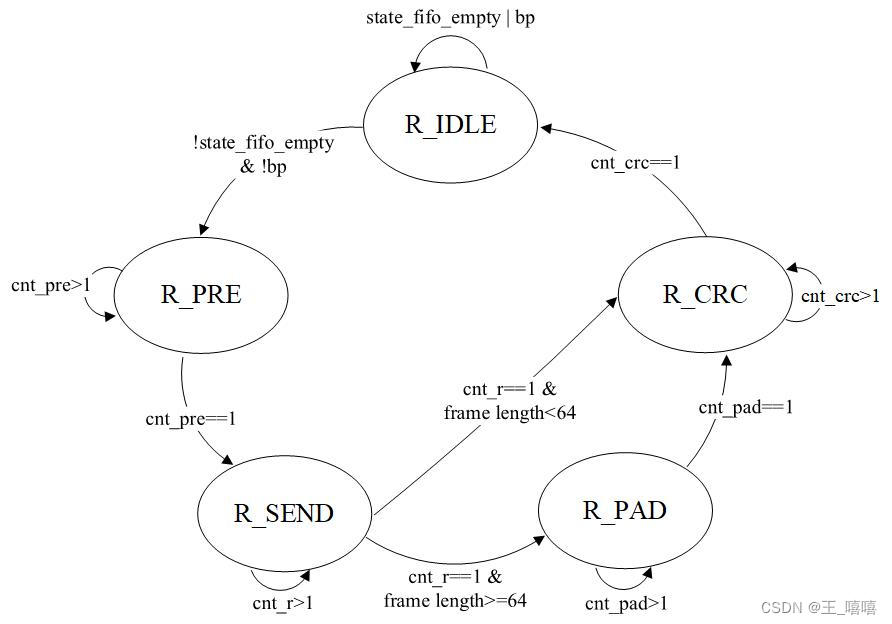

前级队列控制状态机负责接收交换机处理完的数据帧,并写入对应的中间队列internal_data_fifo和internal_state_fifo,在设计中前级状态机分为5个状态,R_IDLE、R_PRE、R_SEND、R_PAD和R_CRC,后四个状态分别负责向internal_data fifo存储前导码、Payload、填充‘0’和CRC校验值。

根据每个状态需要的字节数cnt_r控制状态的跳转,每当前级state fifo非空时,发起一次接收数据帧的处理,把封装好的完整帧存储在internal data fifo中,并在最后一拍更新internal state fifo内容。

而当internal data fifo不足以存放一个最大帧时(此最大帧需要包括前导码和CRC校验的字节数),前级队列状态机会反压输入,停止接收任何数据。

后级队列控制器负责将接收到的完整数据帧连续不断的发送到MII接口,同样也是通过状态机的形式控制internal fifo的输出逻辑。

后级队列控制相对容易,当internal state fifo非空时,取出实际长度数据,并按长度读取data fifo,每拍发送一个4-bits data到MII接口,发送完一个完整帧后,停止一段时间后继续开始检测下一数据帧是否准备完成。

3.4、MAC发送器代码

控制器的设计并不复杂,Verilog代码将放在下面,Testbench就不展示了,有需要的可以等专题结束后在资源中下载,或者去我的公众号获得链接。

module mac_t(

//system interface

input clk,

input rst_n,

//MII interface

input tx_clk,

output reg tx_dv,

output [3:0] tx_d,

//mac-r - interface mux

output reg data_fifo_rd,

input [7:0] data_fifo_dout,

output reg state_fifo_rd,

input [15:0] state_fifo_dout,

input state_fifo_empty);parameter BCNT_MAX = 1518;

parameter BCNT_MIN = 64;

parameter PRE_CNT = 7; //前导码数量

parameter CRC_CNT = 4; //4 byte crc code

parameter FRAME_WAIT_CNT = 24;

//前级接收数据帧的状态机

localparam R_IDLE = 5'b00001;

localparam R_PRE = 5'b00010;

localparam R_SEND = 5'b00100;

localparam R_PAD = 5'b01000;

localparam R_CRC = 5'b10000;//缓存向MII发送数据帧的状态机

localparam T_IDLE = 3'b001;

localparam T_SEND = 3'b010;

localparam T_WAIT = 3'b100;reg [4:0] cur_sta_r;

reg [4:0] next_sta_r;reg [10:0] cnt_r; //内部计数器 记录还有多少byte需要发送 最大2k//internal data fifo变量

reg [7:0] in_data_fifo_din;

reg in_data_fifo_wr;

reg in_data_fifo_rd;

wire [7:0] in_data_fifo_dout;

wire [11:0] in_data_fifo_wr_cnt;//internal state fifo变量

reg [15:0] in_state_fifo_din;

reg in_state_fifo_wr;

wire in_state_fifo_rd;

wire [15:0] in_state_fifo_dout;

wire in_state_fifo_full;

wire in_state_fifo_empty;wire bp; //反压信号,当internal fifo空间不够一个最大帧时,反压上级,拒绝接收一切数据//crc 变量

reg crc_init;

wire crc_cal;

wire crc_vld;

wire [7:0] crc_dout;

wire [7:0] crc_din;assign bp = (in_data_fifo_wr_cnt[11:0] > 4096-BCNT_MAX-PRE_CNT-1) | in_state_fifo_full;assign crc_din[7:0] = in_data_fifo_din[7:0];//后级状态机变量

reg [2:0] cur_sta_t;

reg [2:0] next_sta_t;reg [11:0] cnt_t; //以半字节为单位

reg in_state_fifo_empty_dly;//============================前级状态机=========================

always @(posedge clk or negedge rst_n)beginif(!rst_n)cur_sta_r[4:0] <= R_IDLE;elsecur_sta_r[4:0] <= next_sta_r[4:0];

endalways @(*)begincase(cur_sta_r[4:0])R_IDLE: next_sta_r[4:0] = (!bp & !state_fifo_empty) ? R_PRE : R_IDLE; //IDLE态时 只有internal fifo空间足够 且 前级已有处理完的数据帧才能进入下一状态R_PRE: next_sta_r[4:0] = (cnt_r[10:0]==11'b1) ? R_SEND : R_PRE; //发送完所有前导码和起始符后 进入下一状态R_SEND: next_sta_r[4:0] = (cnt_r[10:0]==11'b1) ? ( state_fifo_dout[10:0]< BCNT_MIN-CRC_CNT ) ? R_PAD : R_CRC : R_SEND; //发送完所有数据帧 进入下一状态 cnt每一状态都会更新R_PAD: next_sta_r[4:0] = (cnt_r[10:0]==11'b1) ? R_CRC : R_PAD; //完成所有填充 进入下一状态R_CRC: next_sta_r[4:0] = (cnt_r[10:0]==11'b1) ? R_IDLE: R_CRC; //CRC校验需要4 cycle 结束后,将校验值填入 返回IDLE态default: next_sta_r[4:0] = R_IDLE; endcase

end//cnt采样

always @(posedge clk or negedge rst_n)beginif(!rst_n)cnt_r[10:0] <= 11'b0;else begincase(cur_sta_r[4:0])R_IDLE: cnt_r[10:0] <= PRE_CNT ;R_PRE: cnt_r[10:0] <= cnt_r[10:0] > 11'b1 ? cnt_r[10:0] - 11'b1 : state_fifo_dout[10:0];R_SEND: cnt_r[10:0] <= cnt_r[10:0] > 11'b1 ? cnt_r[10:0] - 11'b1 : (state_fifo_dout[10:0] < (BCNT_MIN-CRC_CNT)) ? BCNT_MIN-CRC_CNT-state_fifo_dout[10:0] : CRC_CNT;R_PAD: cnt_r[10:0] <= cnt_r[10:0] > 11'b1 ? cnt_r[10:0] - 11'b1 : CRC_CNT;R_CRC: cnt_r[10:0] <= cnt_r[10:0] - 11'b1;default: cnt_r[10:0] <= 11'b0;endcaseend

end//==============crc var 控制================

always @(posedge clk or negedge rst_n)beginif(!rst_n)crc_init <= 1'b0;else if(cur_sta_r[4:0]==R_IDLE && next_sta_r[4:0]==R_PRE)crc_init <= 1'b1;elsecrc_init <= 1'b0;

endassign crc_cal = cur_sta_r[4:0]==R_SEND | cur_sta_r[4:0]==R_PAD;

assign crc_vld = cur_sta_r[4:0]==R_SEND | cur_sta_r[4:0]==R_PAD | cur_sta_r[4:0]==R_CRC;//=========================================

//out data fifo控制

always @(posedge clk or negedge rst_n)beginif(!rst_n)data_fifo_rd <= 1'b0;else if(cur_sta_r[4:0]==R_PRE && cnt_r[10:0]==11'b1)data_fifo_rd <= 1'b1;else if(cur_sta_r[4:0]==R_SEND && cnt_r[10:0]==11'b1)data_fifo_rd <= 1'b0;

end//out state fifo控制

always @(posedge clk or negedge rst_n)beginif(!rst_n)state_fifo_rd <= 1'b0;else if(cur_sta_r[4:0]==R_CRC && cnt_r[10:0]==11'b1)state_fifo_rd <= 1'b1;elsestate_fifo_rd <= 1'b0;

end//internal data fifo控制

always @(posedge clk or negedge rst_n)beginif(!rst_n)in_data_fifo_wr <= 1'b0;else if(cur_sta_r[4:0]==R_IDLE)in_data_fifo_wr <= 1'b0;else if(next_sta_r[4:0]==R_PRE)in_data_fifo_wr <= 1'b1;

endalways @(posedge clk or negedge rst_n)begin //TODOif(!rst_n)in_data_fifo_din[7:0] <= 8'h0;else if(cur_sta_r[4:0]==R_IDLE)in_data_fifo_din[7:0] <= 8'h55;else if(cur_sta_r[4:0]==R_PRE && cnt_r[10:0]==11'd1)in_data_fifo_din[7:0] <= 8'hd5;else if(cur_sta_r[4:0]==R_SEND)in_data_fifo_din[7:0] <= data_fifo_dout[7:0];else if(cur_sta_r[4:0]==R_PAD)in_data_fifo_din[7:0] <= 8'h0;else if(cur_sta_r[4:0]==R_CRC)in_data_fifo_din[7:0] <= crc_dout[7:0];

end//internal state fifo控制

always @(posedge clk or negedge rst_n)beginif(!rst_n)in_state_fifo_wr <= 1'b0;else if(cur_sta_r[4:0]==R_CRC && cnt_r[10:0]==11'b1)in_state_fifo_wr <= 1'b1;elsein_state_fifo_wr <= 1'b0;

endalways @(posedge clk or negedge rst_n)beginif(!rst_n)in_state_fifo_din[15:0] <= 16'b0;else if(cur_sta_r[4:0]==R_CRC && cnt_r[10:0]==11'b1)in_state_fifo_din[15:0] <= state_fifo_dout[15:0];elsein_state_fifo_din[15:0] <= 16'b0;

end//==========================================================================//=================================后级状态机===============================

always @(posedge tx_clk or negedge rst_n)beginif(!rst_n)cur_sta_t[2:0] <= T_IDLE;elsecur_sta_t[2:0] <= next_sta_t[2:0];

endalways @(posedge tx_clk or negedge rst_n)begin //打一拍 为了in state fifo read over, fsm enter next stateif(!rst_n)in_state_fifo_empty_dly <= 1'b1;elsein_state_fifo_empty_dly <= in_state_fifo_empty;

endalways @(*)begincase(cur_sta_t[2:0])T_IDLE: next_sta_t[2:0] = !in_state_fifo_empty_dly ? T_SEND : T_IDLE;T_SEND: next_sta_t[2:0] = cnt_t[11:0]==12'b1 ? T_WAIT : T_SEND;T_WAIT: next_sta_t[2:0] = cnt_t[11:0]==12'b1 ? T_IDLE : T_WAIT;default:next_sta_t[2:0] = T_IDLE;endcase

end//发送状态时 cnt采样

always @(posedge tx_clk or negedge rst_n)beginif(!rst_n)cnt_t[11:0] <= 12'b0;else begincase(cur_sta_t[2:0])T_IDLE: cnt_t[11:0] <= !in_state_fifo_empty_dly ? (in_state_fifo_dout[10:0]+PRE_CNT+CRC_CNT)<<1'b1 : 12'b0;T_SEND: cnt_t[11:0] <= cnt_t[11:0]==12'b1 ? FRAME_WAIT_CNT : cnt_t[11:0] - 12'b1;T_WAIT: cnt_t[11:0] <= cnt_t[11:0] - 12'b1;default: cnt_t[11:0] <= 12'b0;endcaseend

end//internal state fifo 控制assign in_state_fifo_rd = cur_sta_t[2:0]==T_IDLE & !in_state_fifo_empty;//internal data fifo 控制

always @(posedge tx_clk or negedge rst_n)begin //fifo dout需要提前读取后,dout上才有数据,并不是数据先在总线上if(!rst_n)in_data_fifo_rd <= 1'b0;else if( (cur_sta_t[2:0]==T_IDLE & !in_state_fifo_empty) | (cur_sta_t[2:0]==T_SEND & cnt_t[0]) )in_data_fifo_rd <= 1'b1;elsein_data_fifo_rd <= 1'b0;

end//MII接口控制

always @(posedge tx_clk or negedge rst_n)beginif(!rst_n)tx_dv <= 1'b0;else if(cur_sta_t[2:0]==T_SEND)tx_dv <= 1'b1;elsetx_dv <= 1'b0;

endassign tx_d[3:0] = cnt_t[0] ? in_data_fifo_dout[3:0] : in_data_fifo_dout[7:4];data_fifo x_internal_data_fifo(.rst(~rst_n),.wr_clk(clk),.rd_clk(tx_clk),.din(in_data_fifo_din[7:0]),.wr_en(in_data_fifo_wr),.rd_en(in_data_fifo_rd),.dout(in_data_fifo_dout[7:0]),.full(),.empty(),.rd_data_count(),.wr_data_count(in_data_fifo_wr_cnt[11:0]));state_fifo x_internal_state_fifo(.rst(~rst_n),.wr_clk(clk),.rd_clk(tx_clk),.din(in_state_fifo_din[15:0]),.wr_en(in_state_fifo_wr),.rd_en(in_state_fifo_rd),.dout(in_state_fifo_dout[15:0]),.full(in_state_fifo_full),.empty(in_state_fifo_empty)); crc32 x_crc32(.clk(clk),.rst_n(rst_n),.data(crc_din[7:0]),.init(crc_init),.cal(crc_cal),.vld(crc_vld),.crc_reg(),.crc(crc_dout[7:0])); endmodule

搜索关注我的微信公众号【IC墨鱼仔】,获取我的更多IC干货分享!

相关文章:

从零开始 verilog 以太网交换机(三)MAC发送控制器的设计与实现

从零开始 verilog 以太网交换机(三)MAC发送控制器的设计与实现 🔈声明: 😃博主主页:王_嘻嘻的CSDN主页 🧨 从零开始 verilog 以太网交换机系列专栏:点击这里 🔑未经作者允…...

使用vector<char>作为输入缓冲区

一、引言 当我们编写代码:实现网络接收、读取文件内容等功能时,我们往往要在内存中开辟一个输入缓冲区(又名:input buffer/读缓冲区)来存贮接收到的数据。在C里面我们可以用如下方法开辟输入缓冲区。 ①使用C语言中的数组&#x…...

自己在网站搭建用到的一些网站

背景 以后可能很少做网站类的项目了,所以做个简单总结,把自己的一些经历和一些小工具做个记录 域名和主机 https://www.godaddy.com/zh-sg, 我之前的基本都是国际会议型的网站,所以就在gadaddy上买了主机和域名。目标群体在国内可以考虑腾…...

XLSReadWriteII5 Color 颜色l的调用和使用

XLSReadWriteII5 Color 颜色l的调用和使用 一、色彩三原色 自然界,颜色是由红、绿、蓝三色组成,人眼的可见的颜色,可以通过红、绿、蓝三色按照不同的比例合成产生。 任意一种颜色由这三种原色按照一定的比例混合出来。 二、Windows系…...

RT-Thread SP使用教程

RT-Thread SPI 使用教程 实验环境使用的是正点原子的潘多拉开发板。 SPI从机设备使用的是BMP280温湿度大气压传感器。 使用RT-Thread Studio搭建基础功能。 1. 创建工程 使用RT-Thread Studio IDE创建芯片级的工程。创建完成后,可以直接编译下载进行测试。 2.…...

LeetCode 2363. 合并相似的物品

给你两个二维整数数组 items1 和 items2 ,表示两个物品集合。每个数组 items 有以下特质: items[i] [valuei, weighti] 其中 valuei 表示第 i 件物品的 价值 ,weighti 表示第 i 件物品的 重量 。 items 中每件物品的价值都是 唯一的 。 请你…...

numpy 中常用的数据保存、fmt多个参数

在经常性读取大量的数值文件时(比如深度学习训练数据),可以考虑现将数据存储为Numpy格式,然后直接使用Numpy去读取,速度相比为转化前快很多 一、保存为二进制文件(.npy/.npz) (1)numpy.save(file, arr, allow_pickleTrue, fix_importsTrue) file:文件名…...

从0到1一步一步玩转openEuler--19 openEuler 管理服务-特性说明

文章目录19 管理服务-特性说明19.1 更快的启动速度19.2 提供按需启动能力19.3 采用cgroup特性跟踪和管理进程的生命周期19.4 启动挂载点和自动挂载的管理19.5 实现事务性依赖关系管理19.6 与SysV初始化脚本兼容19.7 能够对系统进行快照和恢复19 管理服务-特性说明 19.1 更快的…...

完整思路Python代码)

23美赛E题:光污染(ICM)完整思路Python代码

问题E(综合评价与仿真题):光污染(ICM) 背景 光污染用于描述过度或不良使用人造光。我们称之为光污染的一些现象包括光侵入、过度照明和光杂波。在大城市,太阳落山后,这些现象最容易在天空中看到;然而,它们也可能发生在更偏远的地区。 光污染会改变我们对夜空的看法,…...

快速排序的描述以及两种实现方案

一、快速排序描述 每一轮排序选择一个基准点(pivot)进行分区 1.1. 让小于基准点的元素的进入一个分区,大于基准点的元素的进入另一个分区 1.2. 当分区完成时,基准点元素的位置就是其最终位置在子分区内重复以上过程,直…...

算力引领 数“聚”韶关——第二届中国韶关大数据创新创业大赛圆满收官

为进一步促进数字经济领域创新创业发展,推动国家数据中心集群建设,构建大数据领域资源专业平台,促进大湾区大数据科技成果和创新创业人才转化落地,为韶关大数据领域创新型产业集群的打造、大数据科技成果和创新创业人才的转化落地…...

MySQL 记录锁+间隙锁可以防止删除操作而导致的幻读吗?

文章目录什么是幻读?实验验证加锁分析总结什么是幻读? 首先来看看 MySQL 文档是怎么定义幻读(Phantom Read)的: The so-called phantom problem occurs within a transaction when the same query produces different sets of r…...

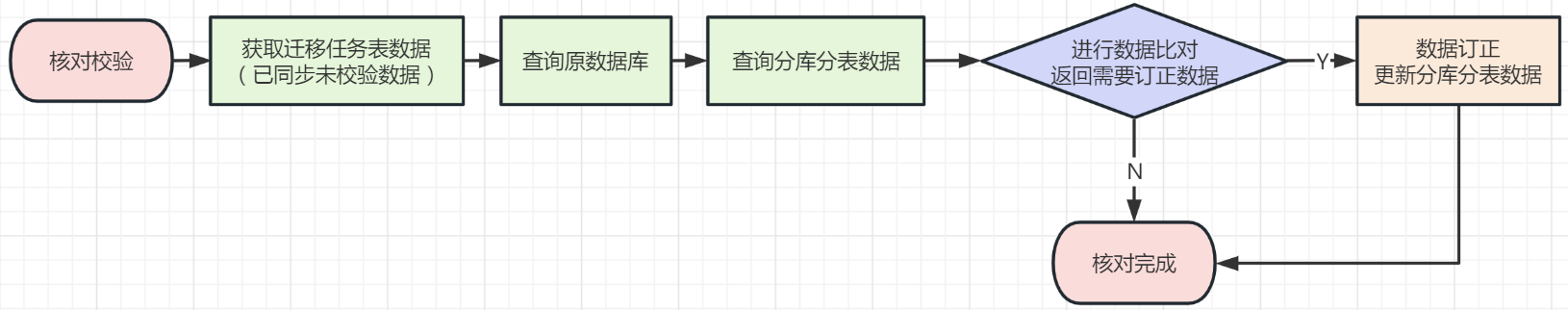

【分库分表】企业级分库分表实战方案与详解(MySQL专栏启动)

📫作者简介:小明java问道之路,2022年度博客之星全国TOP3,专注于后端、中间件、计算机底层、架构设计演进与稳定性建设优化,文章内容兼具广度、深度、大厂技术方案,对待技术喜欢推理加验证,就职于…...

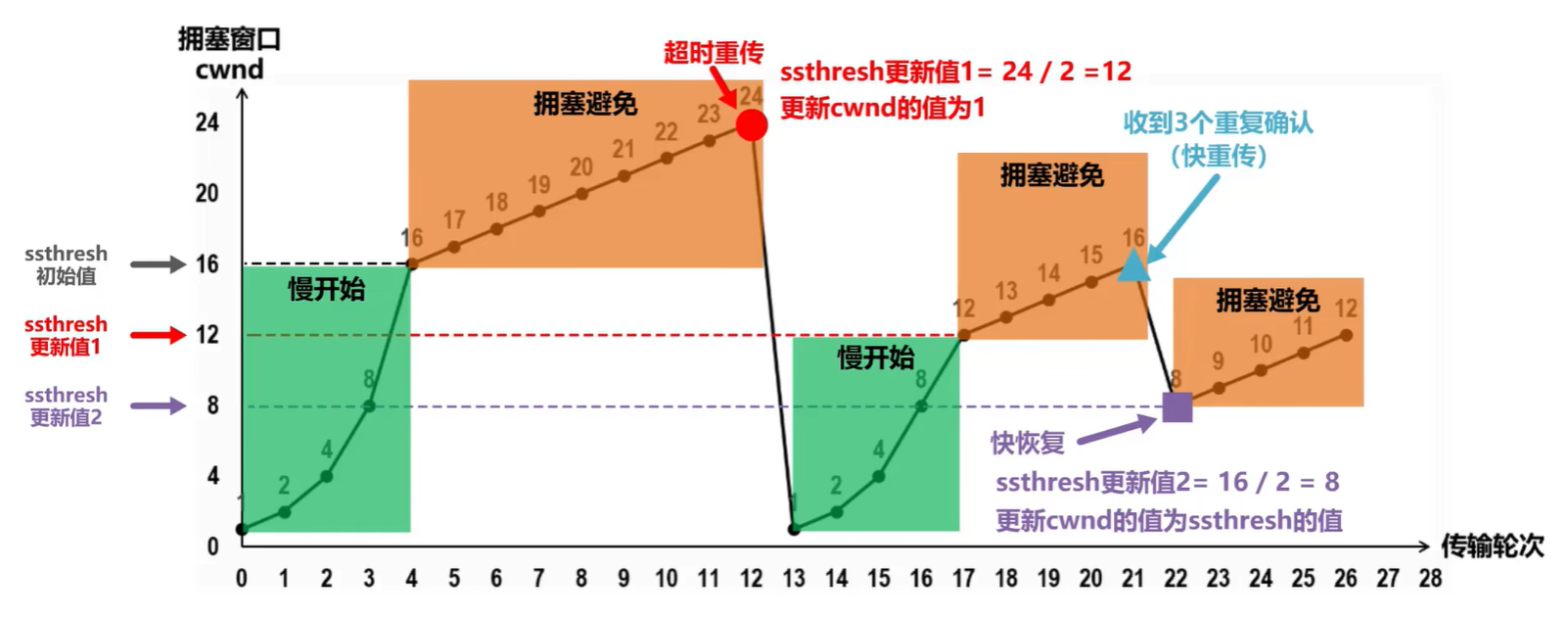

(考研湖科大教书匠计算机网络)第五章传输层-第五节:TCP拥塞控制

获取pdf:密码7281专栏目录首页:【专栏必读】考研湖科大教书匠计算机网络笔记导航 文章目录一:拥塞控制概述二:拥塞控制四大算法(1)慢开始和拥塞避免A:慢启动(slow start)…...

13.使用自动创建线程池的风险,要自己创建为好

自动创建线程池就是直接调用 Executors去new默认的那几个线程池,但是会出现一定的风险,线程池里面会用到队列,也会跟线程池自身有关,所以要从队列和线程池两个方面去解析。 1.了解线程池的队列 线程池的内部结构主要由四部分组成…...

【项目设计】—— 负载均衡式在线OJ平台

目录 一、项目的相关背景 二、所用技术栈和开发环境 三、项目的宏观结构 四、compile_server模块设计 1. 编译服务(compiler模块) 2. 运行服务(runner模块) 3. 编译并运行服务(compile_run模块) 4…...

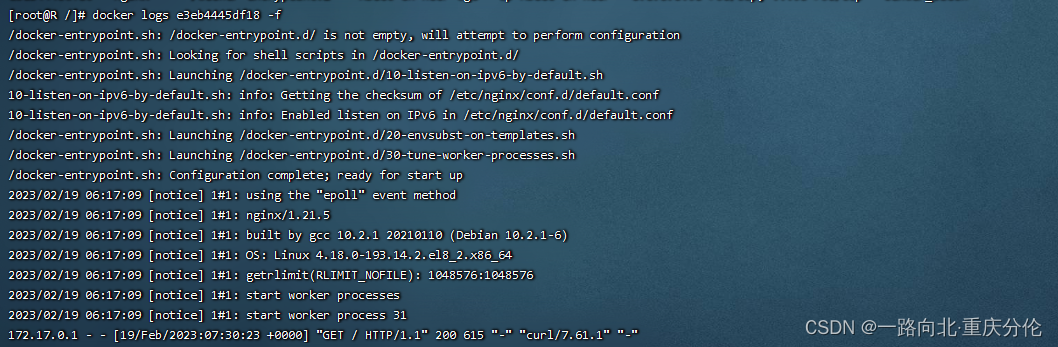

Docker学习笔记

1:docker安装步骤Linux 2:docker安装步骤Windows 3:docker官方文档 4:docker官方远程仓库 docker常用命令 1: docker images----查看docker中安装的镜像 2: docker pull nginx------在docker中安装Nginx镜…...

【爬虫理论实战】详解常见头部反爬技巧与验证方式 | 有 Python 代码实现

以下是常见头部反爬技巧与验证方式的大纲: User-Agent 字段的伪装方式,Referer 字段的伪装方式,Cookie 字段的伪装方式。 文章目录1. ⛳️ 头部反爬技巧1.1. User-Agent 字段&User-Agent 的作用1.2. 常见 User-Agent 的特征1.3. User-Age…...

基于SpringBoot+Vue的鲜花商场管理系统

【辰兮要努力】:hello你好我是辰兮,很高兴你能来阅读,昵称是希望自己能不断精进,向着优秀程序员前行! 博客来源于项目以及编程中遇到的问题总结,偶尔会有读书分享,我会陆续更新Java前端、后台、…...

)

华为OD机试 - 静态扫描最优成本(JS)

静态扫描最优成本 题目 静态扫描快速识别源代码的缺陷,静态扫描的结果以扫描报告作为输出: 文件扫描的成本和文件大小相关,如果文件大小为 N ,则扫描成本为 N 个金币扫描报告的缓存成本和文件大小无关,每缓存一个报告需要 M 个金币扫描报告缓存后,后继再碰到该文件则不…...

Stardew Valley Mod开发:使用OpenClaw主题框架快速构建原生风格UI

1. 项目概述:一个为Stardew Valley Mod开发者量身打造的主题框架如果你是一位《星露谷物语》(Stardew Valley)的模组(Mod)开发者,或者正打算踏入这个充满创造力的社区,那么你很可能已经体会过&a…...

Linux重定向与管道:从文件描述符到高效命令行工作流

1. 项目概述:为什么重定向是命令行的效率倍增器?如果你在Linux命令行里混过一段时间,肯定遇到过这样的场景:想看看一个命令的输出,结果屏幕刷地一下滚过去几百行,关键信息一闪而过;或者想把一个…...

)

【工具分享】9款漏扫工具来了!(内附学习笔记)

【工具分享】9款漏扫工具来了!(内附学习笔记) 以下所有这些工具都是捆绑在一起的Linux发行版,如Kali Linux或BackBox,所以我会建议您安装一个合适的Linux黑客系统,尤其是因为这些黑客工具可以(自…...

模块四-数据转换与操作——28. 分组变换与过滤

28. 分组变换与过滤 1. 概述 除了聚合(agg)之外,groupby 还支持**变换(transform)和过滤(filter)**操作。transform 用于在组内进行元素级运算,filter 用于根据组属性筛选组。 impor…...

如何使用ChatGPT for Google:让搜索结果与AI回答完美协作的终极指南

如何使用ChatGPT for Google:让搜索结果与AI回答完美协作的终极指南 【免费下载链接】chatgpt-google-extension This project is deprecated. Check my new project ChatHub: 项目地址: https://gitcode.com/gh_mirrors/ch/chatgpt-google-extension ChatGP…...

)

基于SSM框架的传统服饰文化平台体验(10034)

有需要的同学,源代码和配套文档领取,加文章最下方的名片哦 一、项目演示 项目演示视频 二、资料介绍 完整源代码(前后端源代码SQL脚本)配套文档(LWPPT开题报告/任务书)远程调试控屏包运行一键启动项目&…...

)

别再乱用`define了!SV宏定义实战避坑指南(从`ifdef到字符串拼接)

别再乱用define了!SV宏定义实战避坑指南(从ifdef到字符串拼接) 在SystemVerilog开发中,宏定义(define)是提高代码复用性和灵活性的利器,但同时也是隐藏最深的"代码地雷"之一。许多开发…...

)

保姆级教程:用斐讯N1盒子刷Armbian 5.77,打造你的专属Debian服务器(附解决负载过高问题)

斐讯N1盒子改造指南:从电视盒子到高性能家庭服务器的蜕变 在智能家居和个性化网络需求日益增长的今天,拥有一台24小时运行的家庭服务器成为许多技术爱好者的刚需。而斐讯N1盒子凭借其出色的硬件配置和极低的功耗,成为了DIY玩家眼中的"宝…...

终极游戏素材资源库:明日方舟开源项目深度解析与实战指南

终极游戏素材资源库:明日方舟开源项目深度解析与实战指南 【免费下载链接】ArknightsGameResource 明日方舟客户端素材 项目地址: https://gitcode.com/gh_mirrors/ar/ArknightsGameResource 在游戏开发与创作领域,获取高质量、结构化的游戏素材资…...

从PI到PR:静止坐标系下永磁同步电机电流控制的新范式

1. 永磁同步电机控制的痛点与变革 每次调试永磁同步电机(PMSM)时,最让人头疼的就是参数漂移问题。记得去年做伺服系统项目,电机运行半小时后电流波形就开始畸变——电感值因温升变化了15%,导致PI控制器输出的d轴电流出…...