FPGA纯Verilog实现任意尺寸图像缩放,串口指令控制切换,贴近真实项目,提供工程源码和技术支持

目录

- 1、前言

- 2、目前主流的FPGA图像缩放方案

- 3、本方案的优越性

- 4、详细设计方案

- 5、vivado工程详解

- 6、上板调试验证并演示

- 7、福利:工程源码获取

1、前言

代码使用纯verilog实现,没有任何ip,可在Xilinx、Intel、国产FPGA间任意移植;

图像缩放的实现方式很多,最简单的莫过于Xilinx的HLS方式实现,用opencv的库,以c++语言几行代码即可完成,但大多使用了IP,导致在其他FPGA器件上移植变得困难。

本文详细描述了纯verilog实现设计方案,工程代码编译通过后上板调试验证,文章末尾有演示视频,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

关于HLS实现图像缩,放请参考我之前写的文章HLS实现图像缩放点击查看:HLS图像缩放

关于纯verilog实现图像缩放,请参考我之前写的文章纯verilog实现图像缩放点击查看:verilog图像缩放

本设计基于我之前写的文章纯verilog实现图像缩放开发;

2、目前主流的FPGA图像缩放方案

目前市面上主流的FPGA图像缩放方案如下:

1:Xilinx的HLS方案,该方案简单,易于实现,但只能用于Xilinx自家的FPGA;关于HLS实现图像缩放请,参考我之前写的文章HLS实现图像缩放点击查看:HLS图像缩放

2:非纯Verilog方案,大部分代码使用Verilog实现,但中间的fifo或ram等使用了IP,导致移植性变差,难以在Xilinx、Altera和国产FPGA之间自由移植;

3:纯Verilog方案,也就是本方案,一个字:牛逼!!!

3、本方案的优越性

一个字:牛逼,表现如下:

1:纯Verilog代码实现,学习性和阅读性达到天花板;

2:移植性达到天花板,Xilinx、Altera和国产FPGA之间自由移植;

3:算法达到天花板,融合了邻近插值和双线性插值两种算法;

4:实用性达到天花板,采用串口协议帧控制切换,不同于市面上验证性和实验性的工程,本设计直接面向实用工程,贴近真实项目,由串口控制缩放分辨率,做类似项目的兄弟可直接拿去用,一个月工资直接拿到手。。。

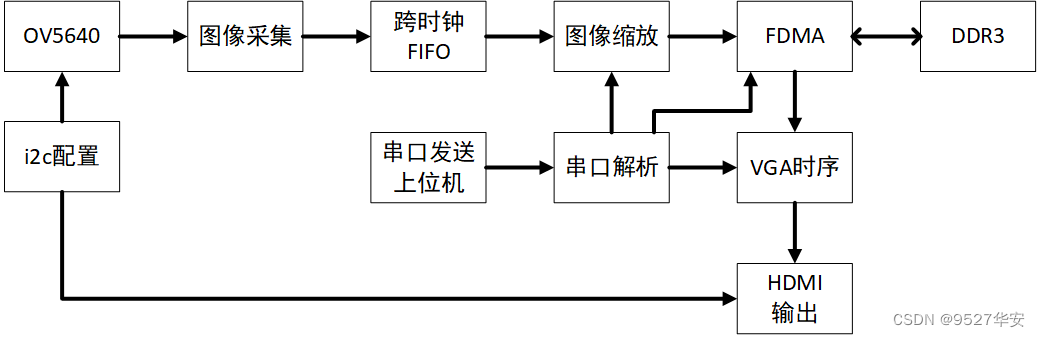

4、详细设计方案

图中使用到了HDMI输出,HDMI输出由silicon9134芯片驱动,关于这部分请参考我之前写的文章点击查看:silicon9134驱动HDMI输出

图中使用到了FDMA做图像缓存,关于这部分请参考我之前写的文章点击查看:FDMA图像缓存

关于纯verilog实现图像缩放,请参考我之前写的文章纯verilog实现图像缩放点击查看:verilog图像缩放

那篇文章详细描述了纯Verilog实现任意尺寸图像缩放的方案,本设计也是基于那个工程修改了,增加了适用于真实项目的串口控制功能,这里只讲新增部分的设计方案;

关于串口协议帧部分,请参考我前面写的文章串口协议帧

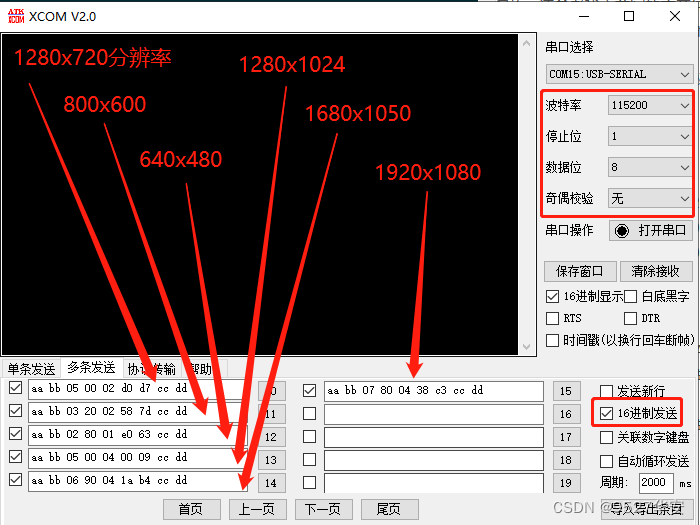

串口协议帧控制缩放分辨率协议如下:

有效数据的高两个字节决定输出分辨率的宽;

有效数据的低两个字节决定输出分辨率的高;

比如:

有效数据0x05,0x00,0x02,0xd0表示输出1280x720的视频;

有效数据0x03,0x20,0x02,0x58表示输出800x600的视频;

有效数据0x07,0x80,0x04,0x38表示输出1920x1080的视频;

具体操作如下:

上电后默认输出原图分辨率为1280x720;

串口发送指令控制缩放模块逻辑如下:

串口指令分辨率参数同时传递给图像缩放模块、FDMA和VGA时序模块;

如果串口指令分辨率小于原图,则控制图像缩放模块做缩小操作;将缩小后的分辨率给FDMA将制定分辨率的图片写入DDR3缓存后输出,同时VGA时序模块只输出制定大小的有效图像,即缩小后的分辨率图像;

如果串口指令分辨率大于原图,则控制图像缩放模块做放大操作;将缩小后的分辨率给FDMA将制定分辨率的图片写入DDR3缓存后输出,同时VGA时序模块只输出制定大小的有效图像,即放大后的分辨率图像;

下面给出串口指令发送举例:

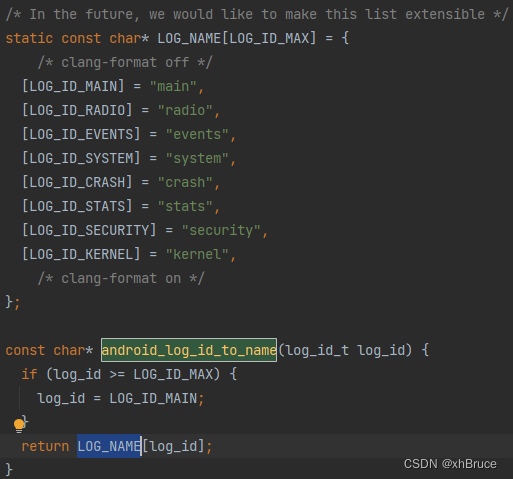

串口切换部分代码如下:

always @(*) beginif(~pll_resetn) beginw_ddr_clk=cmos_pclk;disp_h='d1280;disp_v='d720; endelse if(r_rx_data==32'h050002d0) begin //1280x720w_ddr_clk=cmos_pclk;disp_h='d1280;disp_v='d720; endelse if(r_rx_data==32'h03200258) begin //800x600w_ddr_clk=cmos_pclk;disp_h='d800;disp_v='d600; endelse if(r_rx_data==32'h028001e0) begin //640x480w_ddr_clk=cmos_pclk;disp_h='d640;disp_v='d480; endelse if(r_rx_data==32'h05000400) begin //1280x1024w_ddr_clk=clk_hdmi;disp_h='d1280;disp_v='d1024; endelse if(r_rx_data==32'h0690041a) begin //1680x1050w_ddr_clk=clk_hdmi;disp_h='d1680;disp_v='d1050; end else if(r_rx_data==32'h07800438) begin //1920x1080w_ddr_clk=clk_hdmi;disp_h='d1920;disp_v='d1080; endelse begin //1280x720w_ddr_clk=cmos_pclk;disp_h='d1280;disp_v='d720; end

end

这里设置了5种不同的分辨率,有缩小也有放大,可以根据自身项目修改参数,自由配置;

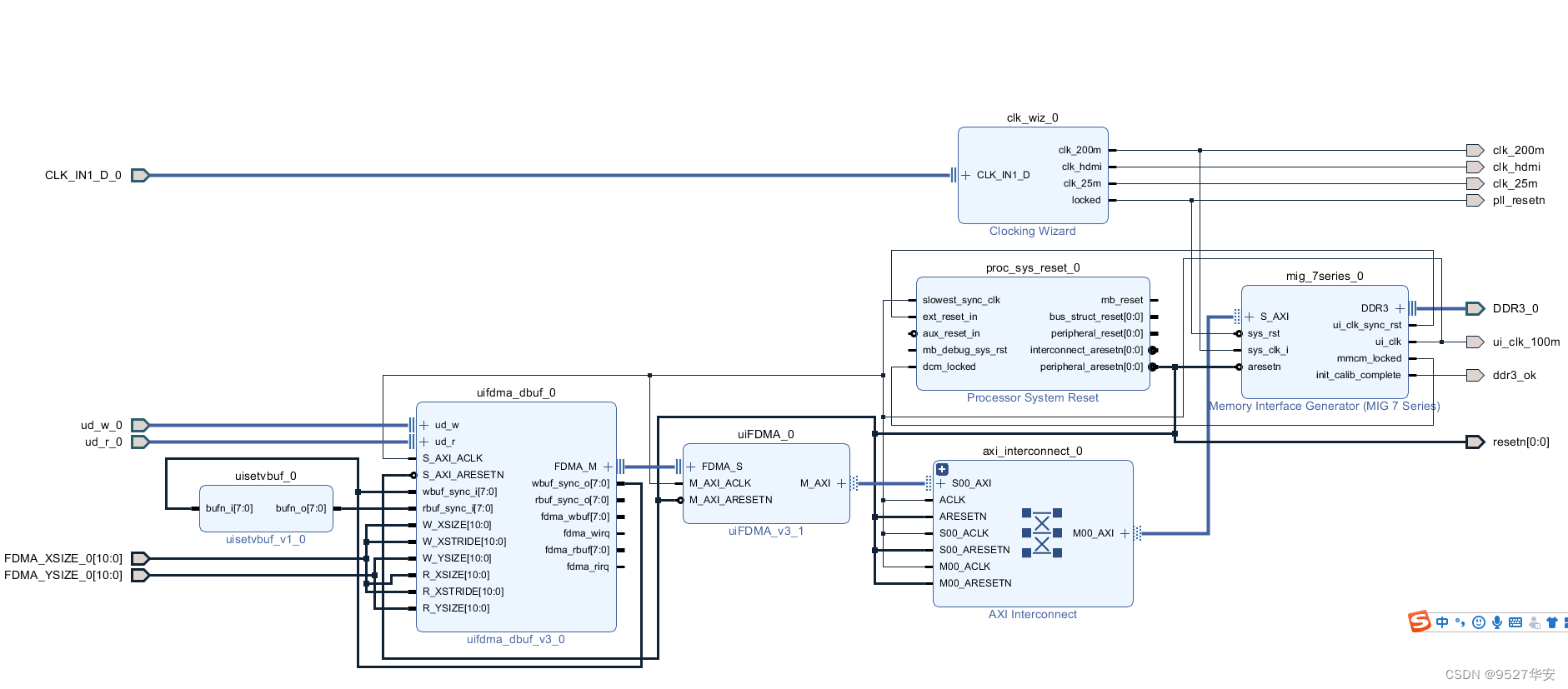

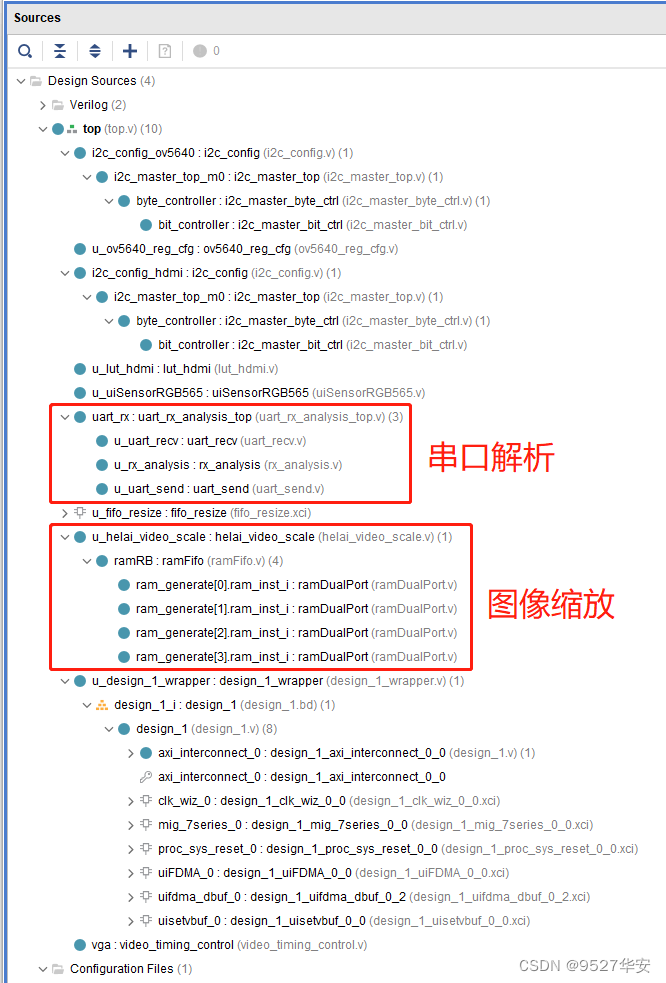

5、vivado工程详解

开发板:Xilinx Artix7开发板;

开发环境:Vivado2019.1;

输入:OV5640摄像头,原始分辨率1280x720p;

输出:HDMI,1080P分辨率下的输出分辨率有效区域显示;

工程BD如下:

工程代码架构如下:

6、上板调试验证并演示

静态展示如下:

演示视频如下:

FPGA纯Verilog实现任意尺寸图像缩放,串口指令控制

7、福利:工程源码获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

相关文章:

FPGA纯Verilog实现任意尺寸图像缩放,串口指令控制切换,贴近真实项目,提供工程源码和技术支持

目录1、前言2、目前主流的FPGA图像缩放方案3、本方案的优越性4、详细设计方案5、vivado工程详解6、上板调试验证并演示7、福利:工程源码获取1、前言 代码使用纯verilog实现,没有任何ip,可在Xilinx、Intel、国产FPGA间任意移植; 图…...

| 代码+思路+重要知识点)

华为OD机试题 - 最长合法表达式(JavaScript)| 代码+思路+重要知识点

最近更新的博客 华为OD机试题 - 字符串加密(JavaScript) 华为OD机试题 - 字母消消乐(JavaScript) 华为OD机试题 - 字母计数(JavaScript) 华为OD机试题 - 整数分解(JavaScript) 华为OD机试题 - 单词反转(JavaScript) 使用说明 参加华为od机试,一定要注意不要完全背…...

L1-005 考试座位号

L1-005 考试座位号 每个 PAT 考生在参加考试时都会被分配两个座位号,一个是试机座位,一个是考试座位。正常情况下,考生在入场时先得到试机座位号码,入座进入试机状态后,系统会显示该考生的考试座位号码,考试…...

Obsidian + remotely save + 坚果云:实现电脑端和手机端的同步

写在前面:近年来某象笔记广告有增无减,不堪其扰,便转投其它笔记,Obsidian、OneNote、Notion、flomo都略有使用,本人更偏好obsidian操作简单,然其官方同步资费甚高,囊中羞涩,所幸可通…...

对比学习MoCo损失函数infoNCE理解(附代码)

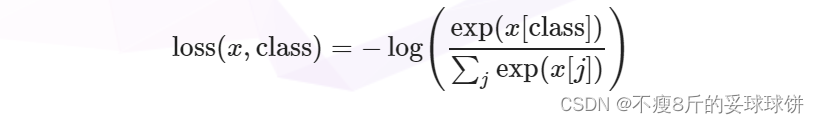

MoCo loss计算采用的损失函数是InfoNCE: 下面是MoCo的伪代码,MoCo这个loss的实现就是基于cross entropy loss。 将k作为q的正样本,因为k与q是来自同一张图像的不同视图;将queue作为q的负样本,因为queue中含有大量…...

logd守护进程

logd守护进程1、adb logcat命令2、logd守护进程启动2.1 logd文件目录2.2 main方法启动3、LogBuffer缓存大小3.1 缓存大小优先级设置3.2 缓存大小相关代码位置android12-release1、adb logcat命令 命令功能adb bugreport > bugreport.txtbugreport 日志adb shell dmesg >…...

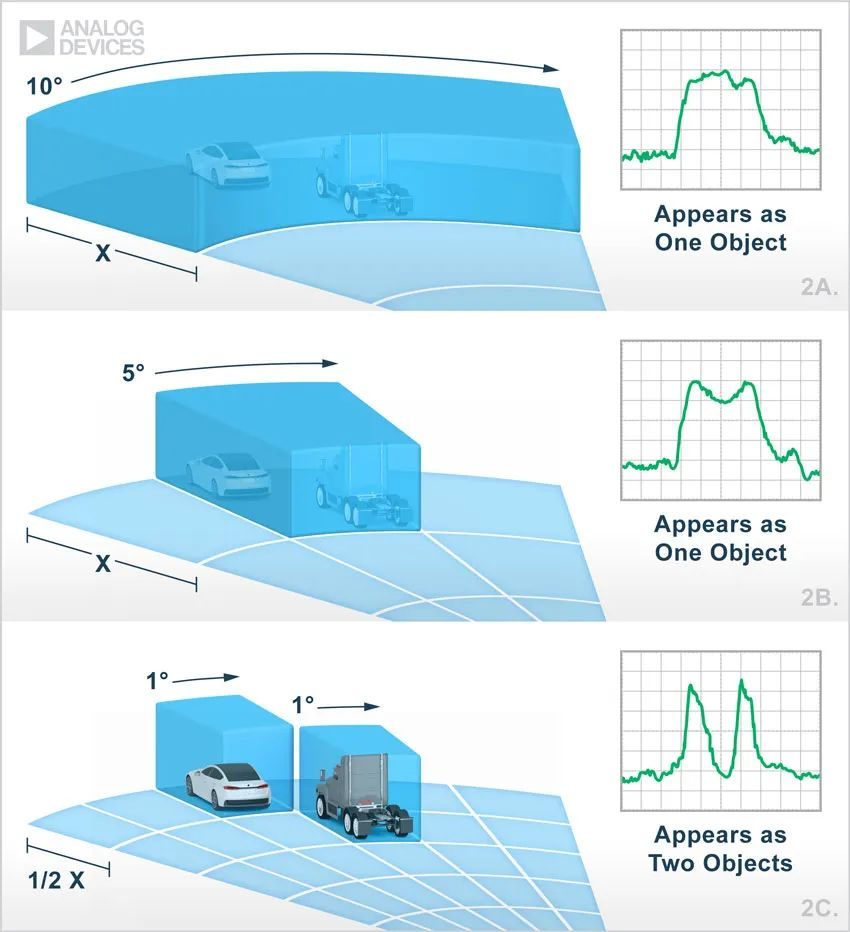

【汽车雷达通往自动驾驶的关键技术】

本文编辑:调皮哥的小助理 现代汽车雷达装置比手机还小,能探测前方、后方或侧方的盲点位置是否存在障碍物,但这还不百分之百实现全自动驾驶的。传统的汽车雷达分辨率都不高,只能“看到”一团东西,可以检测到汽车周围存在…...

2023实习面经

实习面经 秋招笔试面试全记录 字节-电商 字节实习一面: 二分类的损失函数是什么,怎么算?多分类的损失函数怎么算?如果文本分类的标签有多个,比如一个文本同时属于多个label那怎么办?如果文本分类里面的…...

linux shell 入门学习笔记2shell脚本

什么是shell脚本 当命令或者程序语句写在文件中,我们执行文件,读取其中的代码,这个程序就称之为shell脚本。 有了shell脚本肯定是要有对应的解释器了,常见的shell脚本解释器有sh、python、perl、tcl、php、ruby等。一般这种使用文…...

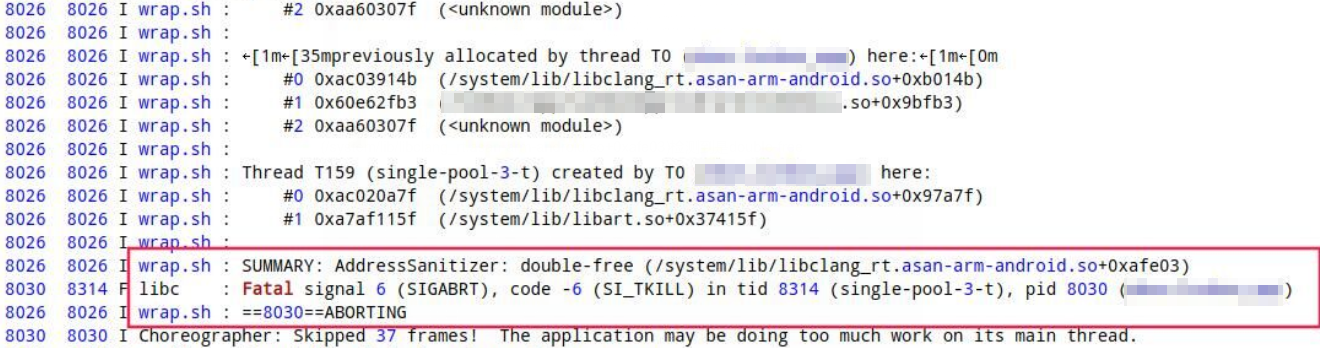

Android稳定性系列-01-使用 Address Sanitizer检测原生代码中的内存错误

前言想必大家曾经被各种Native Crash折磨过,本地测试没啥问题,一到线上或者自动化测试就出现各种SIGSEGV、SIGABRT、SIGILL、SIGBUS、SIGFPE异常,而且堆栈还是崩溃到libc.so这种,看起来跟我们的代码没啥关系,关键还不好…...

HyperOpt-quniform 范围问题

在使用 quniform 的时候,可能会出现超出指定范围的值,例如对于 GBDT 设置参数空间为 learning_rate:hp.quniform(learning_rate,0.05,2.05,0.2),但是仍然会报错 ValueError: learning_rate must be greater than 0 but was 0.0,但…...

Pycharm搭建一个Django项目

File->new project 点击create, 等待一下即可 查看安装 Django 版本: 在 Pycharm 底部选择 Terminal 然后在里面输入:python -m django --version 启动项目: 在 Terminal 里面输入: python manage.py runserver 查看文件目…...

浅析前端工程化中的一部曲——模块化

在日益复杂和多元的 Web 业务背景下,前端工程化经常会被提及。工程化的目的是高性能、稳定性、可用性、可维护性、高效协同,只要是以这几个角度为目标所做的操作,都可成为工程化的一部分。工程化是软件工程中的一种思想,当下的工程…...

新版bing(集成ChatGPT)申请通过后在谷歌浏览器(Chrome)上的使用方法

大家好,我是herosunly。985院校硕士毕业,现担任算法研究员一职,热衷于机器学习算法研究与应用。曾获得阿里云天池比赛第一名,科大讯飞比赛第三名,CCF比赛第四名。拥有多项发明专利。对机器学习和深度学习拥有自己独到的见解。曾经辅导过若干个非计算机专业的学生进入到算法…...

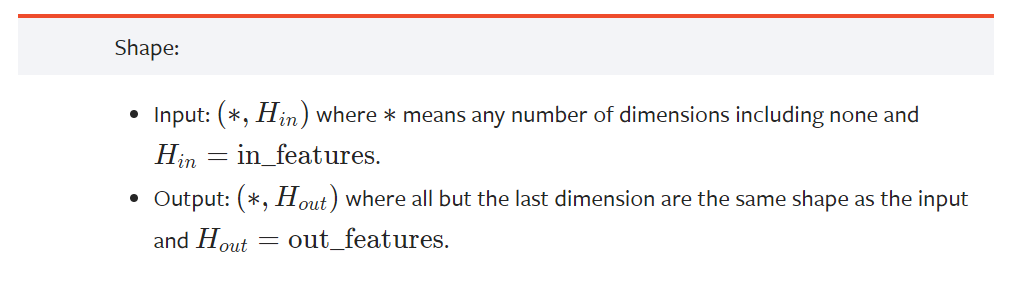

Time-distributed 的理解

前言 今天看到论文中用到 Time-distributed CNN,第一次见到 Time-distributed,不理解是什么含义,看到代码实现也很懵。不管什么网络结构,外面都能套一个TimeDistributed。看了几个博客,还是不明白,问了问C…...

matlab 计算矩阵的Moore-Penrose 伪逆

目录 一、Moore-Penrose 伪逆1、主要函数2、输入输出参数二、代码示例使用伪逆求解线性方程组一、Moore-Penrose 伪逆 Moore-Penrose 伪逆是一种矩阵,可在不存在逆矩阵的情况下作为逆矩阵的部分替代。此矩阵常被用于求解没有唯一解或有许多解的线性方程组。 对于任何矩阵…...

简历制作方面的经验与建议

专栏推荐:2023 数字IC设计秋招复盘——数十家公司笔试题、面试实录 专栏首页:2023 数字IC设计秋招复盘——数十家公司笔试题、面试实录 专栏内容: 笔试复盘篇 2023秋招过程中整理的笔试题,来源包括我自己求职笔试以及整理其他同学的笔试。包含华为、中兴、联发科、AMD、大…...

C语言--static、const、volatile关键字

Static static修饰局部变量改变了变量的生命周期,让静态局部变量出了作用域依然存在,到程序结束,生命周期才结束。 static 修饰局部变量 改变局部变量的生命周期,本质上是改变了局部变量的存储位置,让局部变量不再是…...

Rust学习入门--【18】Rust结构体

系列文章目录 Rust 语言是一种高效、可靠的通用高级语言,效率可以媲美 C / C 。本系列文件记录博主自学Rust的过程。欢迎大家一同学习。 Rust学习入门–【1】引言 Rust学习入门–【2】Rust 开发环境配置 Rust学习入门–【3】Cargo介绍 Rust学习入门–【4】Rust 输…...

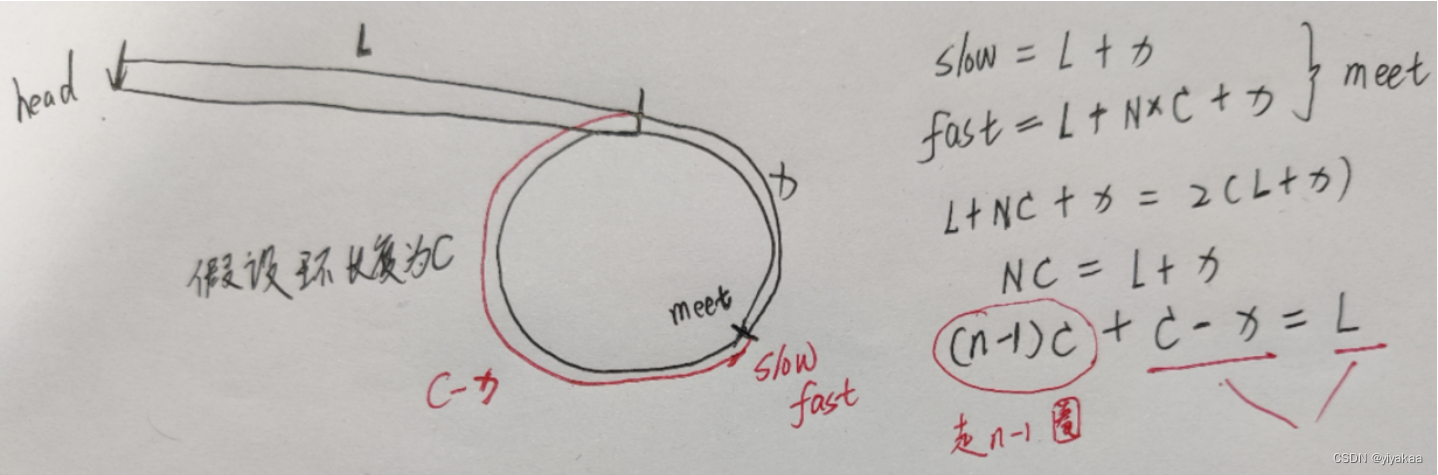

LeetCode142 环形链表Ⅱ

题目: 给定一个链表的头节点 head ,返回链表开始入环的第一个节点。 如果链表无环,则返回 null。 如果链表中有某个节点,可以通过连续跟踪 next 指针再次到达,则链表中存在环。 为了表示给定链表中的环,评…...

OpenClaw技能扩展实战:用Qwen3.5-9B构建图片分析工作流

OpenClaw技能扩展实战:用Qwen3.5-9B构建图片分析工作流 1. 为什么需要图片分析工作流 作为一个经常需要处理大量图片的内容创作者,我长期被三个问题困扰:相册混乱难以查找、社交媒体配文耗时、截图信息整理低效。直到发现OpenClaw支持通过S…...

OpenTSDB数据模型设计终极指南:掌握时间序列数据的最佳实践和常见模式

OpenTSDB数据模型设计终极指南:掌握时间序列数据的最佳实践和常见模式 【免费下载链接】opentsdb A scalable, distributed Time Series Database. 项目地址: https://gitcode.com/gh_mirrors/op/opentsdb OpenTSDB作为一款可扩展的分布式时间序列数据库&…...

万物识别-中文镜像多场景落地:已接入12家中小制造企业视觉质检系统

万物识别-中文镜像多场景落地:已接入12家中小制造企业视觉质检系统 1. 万物识别技术概述 万物识别技术正在改变传统制造业的质检方式。这项技术基于先进的深度学习算法,能够自动识别图像中的物体并给出准确标签。对于中小制造企业来说,这意…...

Davinci NvM Block与Fee Block关联配置详解

1. Davinci配置工具中的NvM与Fee Block基础概念 第一次接触Davinci配置工具时,很多人会对NvM Block和Fee Block的关系感到困惑。简单来说,NvM(Non-volatile Memory)Block是我们配置的非易失性存储单元,而Fee࿰…...

如何快速上手AssetStudio:Unity游戏资源提取的终极指南

如何快速上手AssetStudio:Unity游戏资源提取的终极指南 【免费下载链接】AssetStudio AssetStudio - Based on the archived Perfares AssetStudio, I continue Perfares work to keep AssetStudio up-to-date, with support for new Unity versions and additional…...

实测GLM-4v-9b:单卡24G显存,高清图片识别与问答实战体验

实测GLM-4v-9b:单卡24G显存,高清图片识别与问答实战体验 1. 模型概述与核心优势 GLM-4v-9b是智谱AI于2024年开源的多模态视觉-语言模型,基于90亿参数的GLM-4-9B语言模型架构,通过端到端训练整合了视觉编码器。该模型在11201120高…...

从‘拉风箱’到‘指哪打哪’:VCM音圈马达如何重塑了我们的手机拍照体验?

从‘拉风箱’到‘指哪打哪’:VCM音圈马达如何重塑了我们的手机拍照体验? 还记得十年前用手机拍运动场景的崩溃体验吗?按下快门后镜头反复伸缩发出"咔咔"声,像老式风箱般迟钝,等对焦完成时孩子早已跑出画面。…...

Unity | HDRP高清渲染管线实战:优化Lightmapping性能的10个关键技巧

1. 理解HDRP中的Lightmapping核心机制 在HDRP高清渲染管线中,光照烘焙(Lightmapping)是将复杂光照计算转化为纹理贴图的关键技术。与实时渲染不同,烘焙过程会预先计算场景中静态物体的间接光照、阴影和环境光遮蔽效果,…...

别再死记硬背背包问题公式了!用‘小偷逛博物馆’的故事带你手写递归C++代码

当小偷逛博物馆遇上背包问题:用故事解锁递归思维 推开厚重的博物馆大门,昏暗的灯光下陈列着五件稀世珍宝。作为一名"专业"小偷,你只有一个承重20公斤的背包,每件藏品都有独特的重量和价值。如何在有限负重下最大化收益&…...

OpenClaw视频处理流水线:千问3.5-9B自动剪辑与字幕生成

OpenClaw视频处理流水线:千问3.5-9B自动剪辑与字幕生成 1. 从手动剪辑到AI流水线的转变 去年夏天,当我需要为一期技术教程视频添加字幕时,整整花了三个小时反复校对时间轴。这种低效的重复劳动让我开始思考:能否用AI实现视频处理…...