HDLBits-Verilog学习记录 | Verilog Language-Vectors

文章目录

- 11.vectors | vector0

- 12.vectors in more detail | vector1

- 13.Vector part select | Vector2

- 14.Bitwise operators | Vectorgates

- 15.Four-input gates | Gates4

- 16.Vector concatenation operator | Vector3

- 17.Vector reversal 1 | Vectorr

- 18. Replication operator | Vector4

- 19.More replication | Vector5

11.vectors | vector0

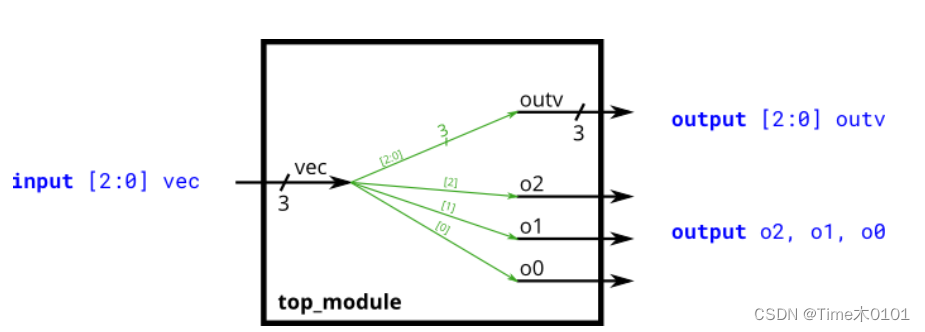

practice:Build a circuit that has one 3-bit input, then outputs the same vector, and also splits it into three separate 1-bit outputs. Connect output o0 to the input vector’s position 0, o1 to position 1, etc.

In a diagram, a tick mark with a number next to it indicates the width of the vector (or “bus”), rather than drawing a separate line for each bit in the vector.

module top_module ( input wire [2:0] vec,output wire [2:0] outv,output wire o2,output wire o1,output wire o0 ); // Module body starts after module declarationassign o0 = vec[0];assign o1 = vec[1];assign o2 = vec[2];assign outv = vec;

endmodule其实可以发现,只要有C语或者其他计算机语言的基础的话,刷vetilog题不算很难上手,写代码的时候还真并不确定语法正不正确,单凭借着对c语言的理解,试着运行,还成功了。

12.vectors in more detail | vector1

practice:Build a combinational circuit that splits an input half-word (16 bits, [15:0] ) into lower [7:0] and upper [15:8] bytes.

`default_nettype none // Disable implicit nets. Reduces some types of bugs.

module top_module( input wire [15:0] in,output wire [7:0] out_hi,output wire [7:0] out_lo );assign out_hi[7:0] = in[15:8];assign out_lo[7:0] = in[7:0];

endmodule

13.Vector part select | Vector2

practice;A 32-bit vector can be viewed as containing 4 bytes (bits [31:24], [23:16], etc.). Build a circuit that will reverse the byte ordering of the 4-byte word.

AaaaaaaaBbbbbbbbCcccccccDddddddd => DdddddddCcccccccBbbbbbbbAaaaaaaa

module top_module( input [31:0] in,output [31:0] out );//// assign out[31:24] = ...;assign out[31:24] = in[7:0];assign out[23:16] = in[15:8];assign out[15:8] = in[23:16];assign out[7:0] = in[31:24];

endmodule

14.Bitwise operators | Vectorgates

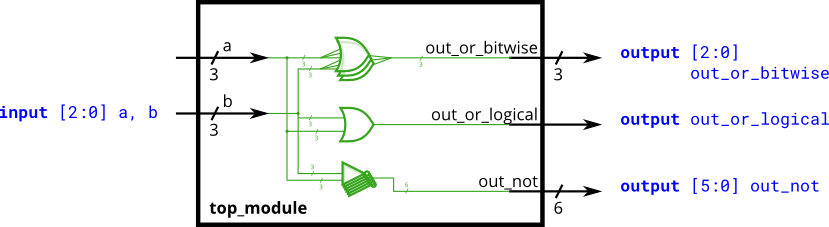

Build a circuit that has two 3-bit inputs that computes the bitwise-OR of the two vectors, the logical-OR of the two vectors, and the inverse (NOT) of both vectors. Place the inverse of b in the upper half of out_not (i.e., bits [5:3]), and the inverse of a in the lower half.

module top_module(input [2:0] a,input [2:0] b,output [2:0] out_or_bitwise,output out_or_logical,output [5:0] out_not

);assign out_or_bitwise = a | b;assign out_or_logical = a || b;assign out_not[5:3] = ~b;assign out_not[2:0] = ~a;endmodule

15.Four-input gates | Gates4

practice:

Build a combinational circuit with four inputs, in[3:0].

There are 3 outputs:

out_and: output of a 4-input AND gate.

out_or: output of a 4-input OR gate.

out_xor: output of a 4-input XOR gate.

module top_module(input [3:0] in,output out_and,output out_or,output out_xor

);assign out_and = in[3] & in[2] & in[1] & in[0];assign out_or = in[3] | in[2] | in[1] | in[0];assign out_xor = in[3] ^ in[2] ^ in[1] ^ in[0];endmodule

注:其中代码可以简化为

assign out_and = & in;

assign out_or = | in;

assign out_xor = ^ in;

16.Vector concatenation operator | Vector3

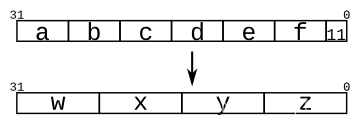

practice:

Given several input vectors, concatenate them together then split them up into several output vectors. There are six 5-bit input vectors: a, b, c, d, e, and f, for a total of 30 bits of input. There are four 8-bit output vectors: w, x, y, and z, for 32 bits of output. The output should be a concatenation of the input vectors followed by two 1 bits:

module top_module (input [4:0] a, b, c, d, e, f,output [7:0] w, x, y, z );assign {w,x,y,z} = {a,b,c,d,e,f,2'b11};

endmodule

17.Vector reversal 1 | Vectorr

practice:Given an 8-bit input vector [7:0], reverse its bit ordering.

module top_module(input [7:0] in,output [7:0] out

);assign out = {in[0],in[1],in[2],in[3],in[4],in[5],in[6],in[7]};endmodule

18. Replication operator | Vector4

practice:Build a circuit that sign-extends an 8-bit number to 32 bits. This requires a concatenation of 24 copies of the sign bit (i.e., replicate bit[7] 24 times) followed by the 8-bit number itself.

module top_module (input [7:0] in,output [31:0] out );assign out = {{24{in[7]}},in};endmodule

注:1这里要非常注意大括号的使用,倍数和后面要成为一个整体,一开始少加一个括号,找了半天错误,后来看错误有提示,才知道。

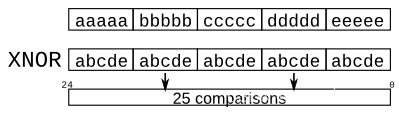

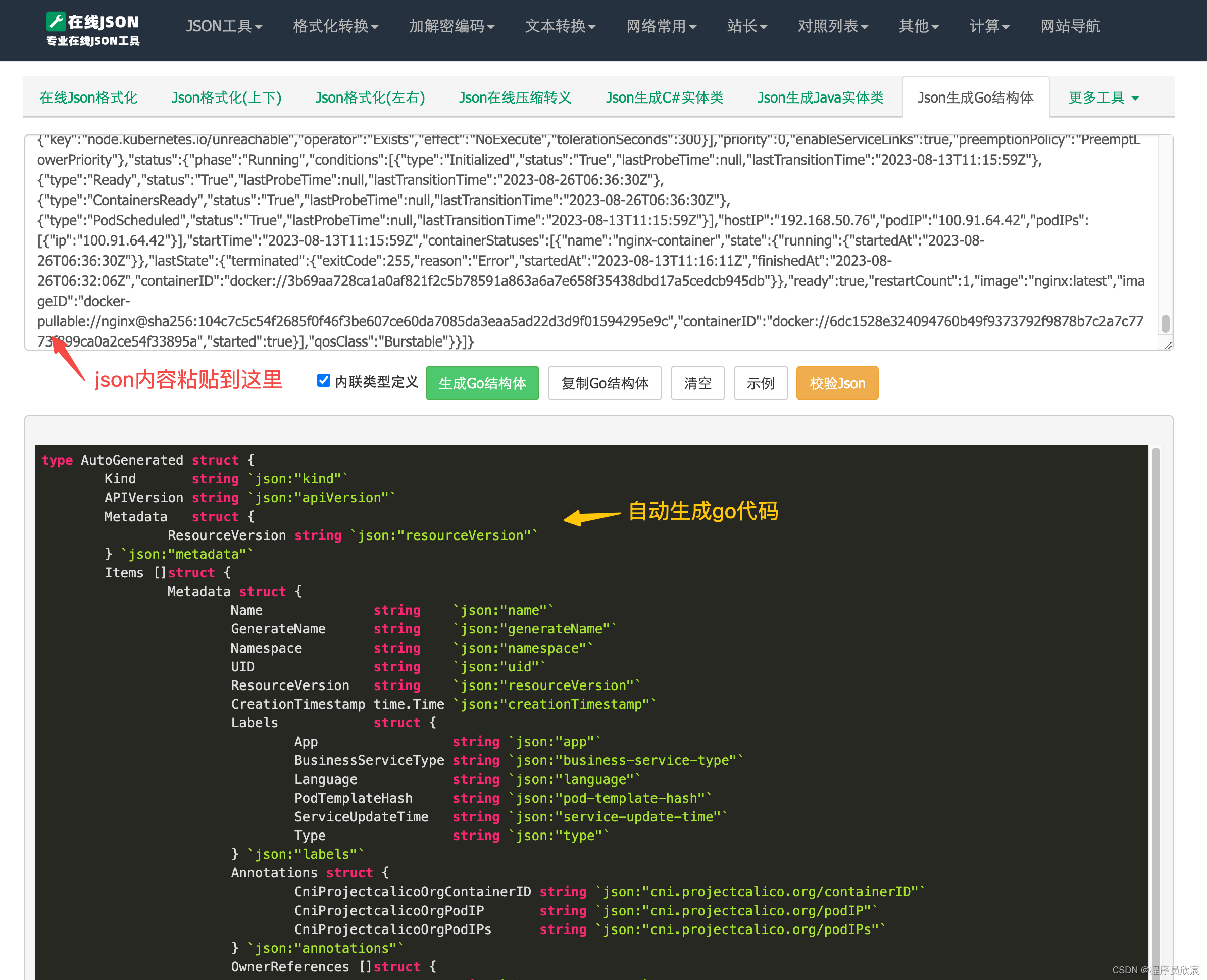

19.More replication | Vector5

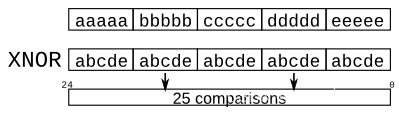

practice:

As the diagram shows, this can be done more easily using the replication and concatenation operators.

The top vector is a concatenation of 5 repeats of each input

The bottom vector is 5 repeats of a concatenation of the 5 inputs

module top_module (input a, b, c, d, e,output [24:0] out );assign out = ~{{5{a}},{5{b}},{5{c}},{5{d}},{5{e}}} ^ {5{a,b,c,d,e}};endmodule

注:1、同样需要大括号

相关文章:

HDLBits-Verilog学习记录 | Verilog Language-Vectors

文章目录 11.vectors | vector012.vectors in more detail | vector113.Vector part select | Vector214.Bitwise operators | Vectorgates15.Four-input gates | Gates416.Vector concatenation operator | Vector317.Vector reversal 1 | Vectorr18. Replication operator | …...

彻底搞懂 PHP 运算符 ?: 和 ??

文章目录 快速掌握?: 短三元运算符?? NULL 合并运算符 附上官方文档查阅方式 快速掌握 ?: 短三元运算符 ?: 称之为短三元运算符,它是我们熟悉的三元运算符(也叫做条件运算符)的一种特殊写法,也就是省略了三元运算符中间的部…...

贝叶斯人工智能大脑与 ChatGPT

文章目录 一、前言二、主要内容 🍉 CSDN 叶庭云:https://yetingyun.blog.csdn.net/ 一、前言 论文地址:https://arxiv.org/abs/2308.14732 这篇论文旨在研究 Chat Generative Pre-trained Transformer(ChatGPT)在贝叶斯…...

适应高速率网络设备的-2.5G/5G/10G网络变压器/网络滤波器介绍

Hqst盈盛(华强盛)电子导读:在高速发展的互联网/物联网时代,为满足高网速的网络数据传输需求,网络设备在制造中也要选用合适的网络变压器/滤波器产品,有哪些可供选择的高速率网络变压器产品也是广大采购人员…...

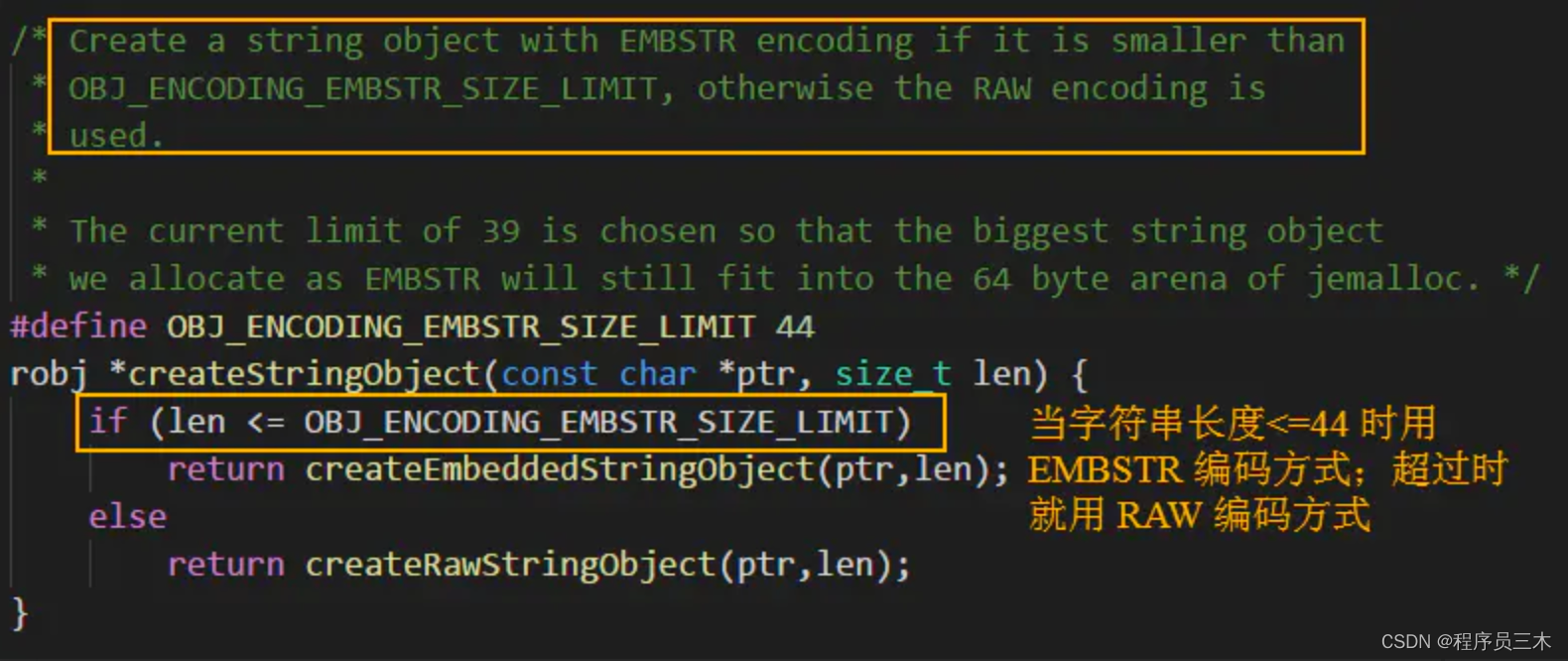

「Redis」1. 数据类型的底层实现

前言:在这篇博文中,我们将简单总结在面试中怎么回答Redis数据类型的底层实现。 因为面试时间就那么点,言简意赅的描述自己会的知识显得尤为重要‼️ 文章目录 0.1. String 的底层实现原理0.2. 列表的底层实现原理0.3. 字典的底层实现原理0.4.…...

Win11共享文件,能发现主机但无法访问,提示找不到网络路径

加密长度选择如下: 参考以下链接: Redirectinghttps://answers.microsoft.com/zh-hans/windows/forum/all/win11%E8%AE%BE%E7%BD%AE%E6%96%87%E4%BB%B6%E5%A4%B9/554343a9-d963-449a-aa59-ce1e6f7c8982?tabAllReplies#tabs...

ROS中使用Navigation报错信息

在ROS中使用遇到了几个Navigation报错信息,在这里进行下记录: [ WARN] [1688134727.429227824]: The origin for the sensor at (7.35, 13.12) is out of map bounds. So, the costmap cannot raytrace for it. 解决办法: [ WARN] [16881…...

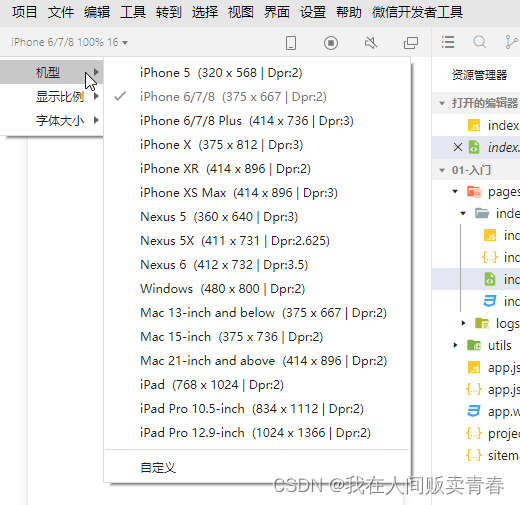

three.js(六):自适应设备分辨率

自适应设备分辨率 当今大多数的PC端和移动端显示器都是HD-DPI显示器。HD-DPI 是High Definition-Dots Per Inch 的简称,意思是高分辨率显示器。不同设备的显示器的分辨率是不一样的。 以上图中的iPhone6/7/8 为例:375*667 代表的手机的屏幕的物理尺寸&a…...

Kubernetes对象深入学习之五:TypeMeta无效之谜

欢迎访问我的GitHub 这里分类和汇总了欣宸的全部原创(含配套源码):https://github.com/zq2599/blog_demos 本篇概览 本文是《Kubernetes对象深入学习之五》系列的第五篇,从前文的分析也能看出,代表对象类型的schema.ObjectKind,于…...

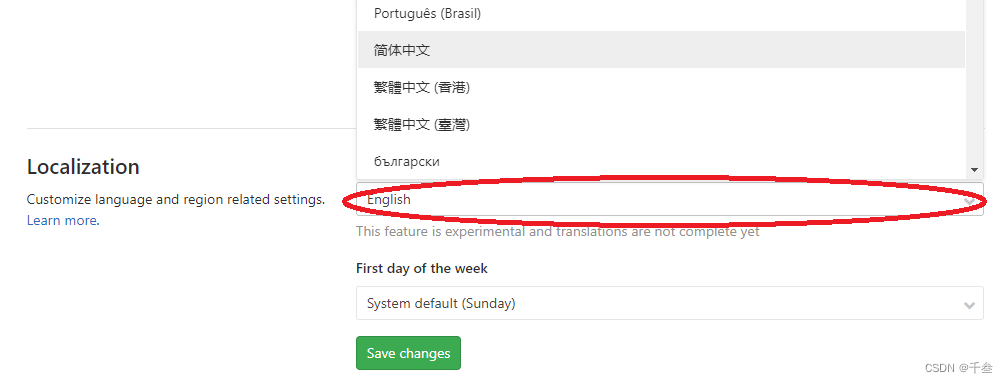

Gitlab设置中文

1. 打开设置 2.选择首选项Preferences 3. 下滑选择本地化选项Localization,设置简体中文,然后保存更改save changes。刷新网页即可。...

【微服务部署】05-安全:强制HTTPS

文章目录 安全 : 强制HTTPS的两种方式1. Ingress配置重定向2. 应用程序配置3. Ingress配置4. 应用程序配置代码总结 安全 : 强制HTTPS的两种方式 互联网发展中,安全是非常重要的,由其是现在HTTPS非常普及的情况下,应用程序在公网上一般都会被…...

Config:服务端连接Git配置

创建子模块 Pom文件 <?xml version"1.0" encoding"UTF-8"?> <project xmlns"http://maven.apache.org/POM/4.0.0"xmlns:xsi"http://www.w3.org/2001/XMLSchema-instance"xsi:schemaLocation"http://maven.apache.org…...

c++学习 之 类和对象 public , protected ,private

前言 在C中,访问控制修饰符(Access Control Modifiers)用于控制类的成员(成员变量和成员函数)的访问权限。这些修饰符分为三种:public、protected和private。它们定义了成员可以在何处访问,具体…...

ECharts图表动态修改series显示隐藏

文章目录 1、前言2、思路3、实现 1、前言 最近做的大数据平台,里面很多部分用到了ECharts,其中有个功能,要求将图表分组,根据用户选择的组,来确定ECharts要显示那些线条和柱子,也就是动态的显示option.seri…...

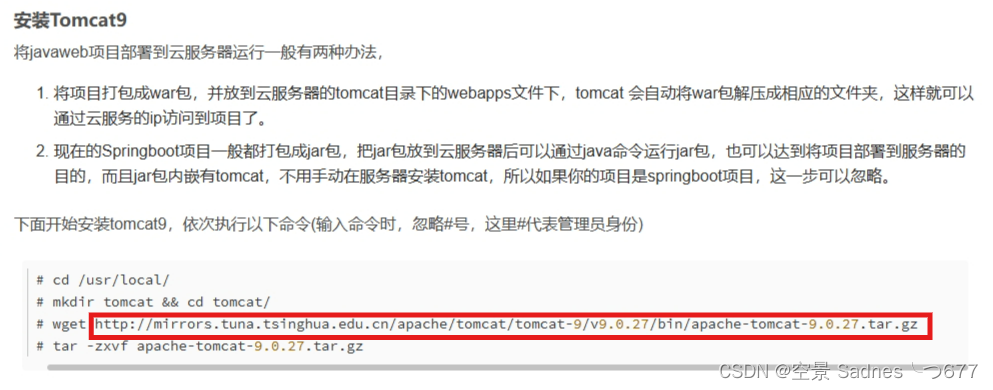

云服务器(Centos7系统)配置JAVA+mysql+tomcat 环境

文章主要内容来源云服务器(Centos7系统)部署javaweb项目(二)配置JAVAmysqltomcat 环境_man_zuo的博客-CSDN博客 模仿途中遇到的问题 连接无效 有时连接无法下载,可能是过期了,将其更换为官网给的下载连接即…...

)

【计算机视觉 | 目标检测】目标检测常用数据集及其介绍(四)

文章目录 一、JTA (Joint Track Auto)二、AVD (Active Vision Dataset)三、ExDark (Exclusively Dark Image Dataset)四、InteriorNet五、ScanRefer Dataset六、FlickrLogos-32七、SIXray八、Clear Weather (DENSE)九、DVQA (Data Visualizations via Question Answering)十、M…...

Dockerfile制作镜像与搭建LAMP环境

一.编写Dockerfile制作Web应用系统nginx镜像,生成镜像nginx:v1.1,并推送其到私有仓库。具体要求如下: (1)基于centos基础镜像; (2)指定作者信息; (3ÿ…...

Linux系统中查看端口的方法

一、使用netstat命令 netstat命令是一种非常实用的命令,可以用来显示网络连接、路由表、网络接口和网络统计信息等。它还可以用来显示系统中正在监听的端口。要查看端口,只需在终端中输入以下命令: netstat -tuln 这个命令的意思是列出所有…...

java mysql传入string数组返回string数组的简单写法

一、前言 最近有个需求,需要一个传入string数组返回string数组的sql逻辑。 懒得封装成javabean了,于是就写了一个简单的样例,总结下。 二、代码 1.mapper.java,可以这样写: public interface MyMapper {String[] …...

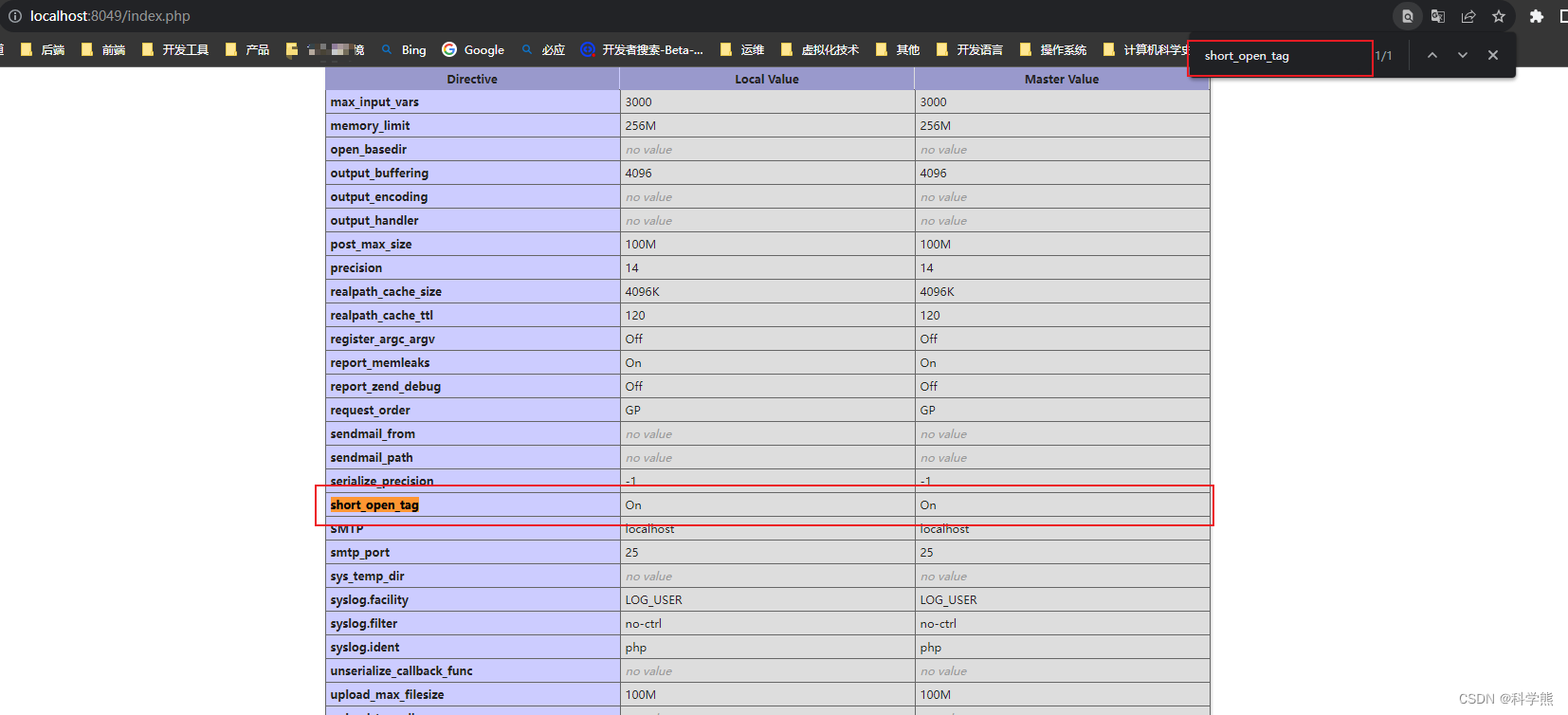

【PHP】PHP基本语法

1、PHP标记 当解析一个文件时,PHP 会寻找起始和结束标记,也就是 <?php 和 ?>,告诉 PHP 开始和停止解析二者之间的代码。此种解析方式使得 PHP 可以被嵌入到各种不同的文档中去,而任何起始和结束标记之外的部分都会被 PHP…...

IntelliJ IDEA 2023.3 集成 Maven 3.8.3 保姆级避坑指南:从环境变量到项目构建全流程

IntelliJ IDEA 2023.3 与 Maven 3.8.3 深度集成实战:从零构建企业级Java项目 作为一名长期使用IntelliJ IDEA进行Java开发的工程师,我深刻体会到Maven与IDE无缝集成的重要性。每次新版本发布,那些看似简单的配置背后往往隐藏着令人头疼的兼容…...

华硕笔记本G-Helper显示管理全攻略:从色彩异常到专业校准的5步解决方案

华硕笔记本G-Helper显示管理全攻略:从色彩异常到专业校准的5步解决方案 【免费下载链接】g-helper Lightweight Armoury Crate alternative for Asus laptops with nearly the same functionality. Works with ROG Zephyrus, Flow, TUF, Strix, Scar, ProArt, Vivob…...

5个步骤在Windows Hyper-V上完美运行macOS虚拟机

5个步骤在Windows Hyper-V上完美运行macOS虚拟机 【免费下载链接】OSX-Hyper-V OpenCore configuration for running macOS on Windows Hyper-V. 项目地址: https://gitcode.com/gh_mirrors/os/OSX-Hyper-V 你是否想在Windows电脑上体验macOS的流畅操作?OSX-…...

Beam Search超参数调优指南:从原理到实践,如何为你的NLP任务选择最佳beam width?

Beam Search超参数调优实战:如何在生成质量与推理效率间找到平衡点 当GPT-3生成那段令人惊艳的诗歌时,背后其实经历了几百次候选序列的评估与筛选——这正是beam search算法的魔力所在。作为自然语言生成任务中最核心的解码策略之一,beam wid…...

)

从原理图到Ping通:我的STM32F407 RMII以太网调试笔记(含LAN8720硬件差异处理)

从原理图到Ping通:我的STM32F407 RMII以太网调试笔记(含LAN8720硬件差异处理) 第一次点亮STM32F407的以太网接口时,那种成就感至今难忘。但在此之前,我经历了整整两周的煎熬——原理图反复检查、PCB打样两次、软件调试…...

终极指南:如何为ZXing创建企业级自定义解码器解决业务条码难题

终极指南:如何为ZXing创建企业级自定义解码器解决业务条码难题 【免费下载链接】zxing ZXing ("Zebra Crossing") barcode scanning library for Java, Android 项目地址: https://gitcode.com/gh_mirrors/zx/zxing 你是否曾遇到过标准扫码库无法解…...

3个关键技巧:用ProperTree告别Plist编辑的繁琐与混乱

3个关键技巧:用ProperTree告别Plist编辑的繁琐与混乱 【免费下载链接】ProperTree Cross platform GUI plist editor written in python. 项目地址: https://gitcode.com/gh_mirrors/pr/ProperTree 你是否曾经面对macOS配置文件时感到手足无措?那…...

)

别再只盯着P0XXX了!一文搞懂UDS诊断中DTC的三个字节到底在说什么(附实战解析)

解码UDS诊断中的DTC三字节:从十六进制到故障真相 当诊断仪屏幕上跳出"0x43E711"这样的神秘代码时,多数工程师的第一反应是翻查故障码手册。但真正的高手会像破译密码一样,直接拆解这三个字节背后的工程语言。本文将带您深入DTC的二…...

小新 Pad Pro 2022 投屏新姿势|ZUI14 小组件一键镜像,效率直接拉满

很多联想小新平板用户都知道系统自带投屏功能,但很少有人留意到ZUI14 里藏着一个超便捷的小组件投屏入口,不用翻设置、不用等搜索,桌面点一下就能快速投屏,特别适合日常办公、学习、演示等高频场景。今天分享来自联想官方知识库的…...

国产芯片独角兽IPO热潮来袭,百度昆仑芯与阿里平头哥角逐RISC-V弯道超车机遇

国产芯片好消息不断,长鑫科技与长江存储启动IPO,百度昆仑芯、阿里平头哥也有相关动作。互联网大厂钟情自研AI芯片,昆仑芯与平头哥发展路径不同,RISC-V或是弯道超车关键。国产芯片独角兽登场被誉为“存储双雄”的长鑫科技与长江存储…...