ZYNQ通过AXI DMA实现PL发送连续大量数据到PS DDR

硬件:ZYNQ7100

软件:Vivado 2017.4、Xilinx SDK 2017.4

ZYNQ PL 和 PS 的通信方式有 AXI GPIO、BRAM、DDR等。对于数据量较少、地址不连续、长度规则的情况,BROM 比较适用。而对于传输速度要求高、数据量大、地址连续的情况,比如 ADC,可以通过 AXI DMA 来完成。

1、硬件设计

1.1 ZYNQ7 Processing System IP核

选中 M AXI GP0 和 S AXI HP0

选中 PL 到 PS 的中断端口

选中 PL 到 PS 的中断端口

其他按开发板要求配置。

其他按开发板要求配置。

1.2 AXI Direct Memory Access IP核

AXI Direct Memory Access IP核配置如下图所示。由于只需要 PL 向 PS 的 DDR写数据,所以只使能了写通道。

1.3 AXI4-Stream Data FIFO IP核

AXI4-Stream Data FIFO IP核用于缓存数据,它的接口按照 AXI4-Stream 协议通信,它的配置如下图所示。

1.4 连续数据生成模块

编写一个生成连续数据的模块,它在接收到一个触发信号上升沿后,按 AXI4-Stream 协议输出连续数据。

module dma_frame_gen #(parameter TRANS_NUM = 32'd1550336 //1514*1024)(input resetn,input clk,input trans_start,// axi-streamoutput [31:0] m_axis_tdata,output [3:0] m_axis_tkeep,output m_axis_tlast,output m_axis_tvalid,input m_axis_tready);assign m_axis_tkeep = 4'b1111;

reg trans_start_0, trans_start_1;

wire pos_trans_start;

assign pos_trans_start = trans_start_0 & (~trans_start_1);

always @(posedge clk or negedge resetn) beginif(~resetn) begintrans_start_0 <= 1'd0;trans_start_1 <= 1'd0;endelse begintrans_start_0 <= trans_start;trans_start_1 <= trans_start_0;end

end

localparam IDLE = 2'b00;

localparam TRANS = 2'b01;

localparam DONE = 2'b10;

reg [1:0] state;

reg [31:0] trans_cnt;

reg [31:0] r_tdata;

reg r_tvalid, r_tlast;

always @(posedge clk or negedge resetn) beginif(!resetn) beginstate <= IDLE;r_tdata <= 32'd0;r_tvalid <= 1'b0;endelse beginr_tdata <= 32'd0;r_tvalid <= 1'b0;case(state)IDLE: beginif(pos_trans_start && m_axis_tready) beginstate <= TRANS;endelse beginstate <= IDLE;endendTRANS: beginif(trans_cnt < TRANS_NUM) beginstate <= TRANS;r_tvalid <= 1'b1;r_tdata <= trans_cnt;endelse beginstate <= DONE;endendDONE: beginstate <= IDLE;enddefault: beginstate <= IDLE;endendcaseend

end

always @(posedge clk or negedge resetn) beginif(!resetn) beginr_tlast <= 1'b0;endelse beginif(state == TRANS && trans_cnt == TRANS_NUM-1) beginr_tlast <= 1'b1;endelse beginr_tlast <= 1'b0;endend

end

always @(posedge clk or negedge resetn) beginif(!resetn) begintrans_cnt <= 0;endelse beginif(state == TRANS) begintrans_cnt <= trans_cnt + 1;endelse begintrans_cnt <= 32'd0;endend

end

assign m_axis_tdata = r_tdata;

assign m_axis_tlast = r_tlast;

assign m_axis_tvalid = r_tvalid;

endmodule

把此模块添加到 block design 里,软件能自动识别 AXI4-Stream 端口。

1.5 block design整体设计

block design整体设计如下图所示,主要的数据通路用橙色线表示。dma_frame_gen 的 m_axis 端口连接 AXI4-Stream Data FIFO 的 S_AXIS 端口,AXI4-Stream Data FIFO 的 M_AXIS 端口连接 AXI DMA Memory Access 的 S_AXIS_S2MM 端口,AXI DMA Memory Access 的 M_AXI_S2MM 端口连接 AXI SmartConnect 的 S00_AXI 端口,AXI SmartConnect 的 M00_AXI 端口连接 ZYNQ7 Processing System 的 S_AXI_HP0 端口。

2、软件设计

2.1 AXI DMA 初始化和 DMA 中断函数

void axi_dma_init()

{XAxiDma_Config *axi_dma_cfg_ptr;axi_dma_cfg_ptr = XAxiDma_LookupConfig(XPAR_AXIDMA_0_DEVICE_ID);XAxiDma_CfgInitialize(&axi_dma_0_inst, axi_dma_cfg_ptr);// interruptXScuGic_SetPriorityTriggerType(&scugic_inst, XPAR_FABRIC_AXIDMA_0_VEC_ID, 0xA0, 0x3);XScuGic_Connect(&scugic_inst, XPAR_FABRIC_AXIDMA_0_VEC_ID, (Xil_InterruptHandler) axi_dma_rx_intr_handler, &axi_dma_0_inst);XScuGic_Enable(&scugic_inst, XPAR_FABRIC_AXIDMA_0_VEC_ID);XAxiDma_IntrEnable(&axi_dma_0_inst, XAXIDMA_IRQ_ALL_MASK, XAXIDMA_DEVICE_TO_DMA);

}

void axi_dma_rx_intr_handler(void *CallBackRef)

{int timeout;u32 irq_status;XAxiDma *axidma_inst = (XAxiDma *)CallBackRef;irq_status = XAxiDma_IntrGetIrq(axidma_inst, XAXIDMA_DEVICE_TO_DMA);XAxiDma_IntrAckIrq(axidma_inst, irq_status, XAXIDMA_DEVICE_TO_DMA);if ((irq_status & XAXIDMA_IRQ_ERROR_MASK)){

// error = 1;XAxiDma_Reset(axidma_inst);timeout = 10000;while(timeout){if (XAxiDma_ResetIsDone(axidma_inst)) break;timeout--;}return;}if ((irq_status & XAXIDMA_IRQ_IOC_MASK)){dma_rx_done = 1;}

}

2.2 初始化中断

void interrupt_init()

{XScuGic_Config *intc_cfg_ptr;intc_cfg_ptr = XScuGic_LookupConfig(XPAR_SCUGIC_SINGLE_DEVICE_ID);XScuGic_CfgInitialize(&scugic_inst, intc_cfg_ptr, intc_cfg_ptr->CpuBaseAddress);Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_INT, (Xil_ExceptionHandler)XScuGic_InterruptHandler, &scugic_inst);Xil_ExceptionEnable();

}

2.3 初始化 AXI GPIO

void axi_gpio_init()

{XGpio_Initialize(&axi_gpio_0_inst, XPAR_GPIO_0_DEVICE_ID);XGpio_SetDataDirection(&axi_gpio_0_inst, 1, 0x01);

}

2.4 main 函数

在 main 函数中先执行中断、AXI GPIO 和 AXI DMA 的初始化函数,然后 AXI GPIO 输出一个信号上升沿触发 dma_frame_gen 模块输出连续数据,XAxiDma_SimpleTransfer 函数触发一次 DMA 传输,Xil_DCacheFlushRange 函数刷新 Data Cache。DMA 传输完成后触发 DMA 中断,如果 DMA 传输成功,dma_rx_done 在 DMA 中断中置 1。

int main()

{int status;FIL fil;volatile int rec_data[BUF_SIZE] = {0};interrupt_init();axi_gpio_init();axi_dma_init();XGpio_DiscreteWrite(&axi_gpio_0_inst, 1, 0x01);XAxiDma_SimpleTransfer(&axi_dma_0_inst, (UINTPTR) rec_data, BUF_SIZE*sizeof(int), XAXIDMA_DEVICE_TO_DMA);XGpio_DiscreteClear(&axi_gpio_0_inst, 1, 0x01);Xil_DCacheFlushRange((UINTPTR) rec_data, BUF_SIZE*sizeof(int)); //刷新Data Cachewhile(!dma_rx_done);return 0;

}

3、上板验证

用 Debug 模式运行程序,在 main 函数的 return 0; 行放断点,当程序运行到断点处时,看 rec_data 中存的是从 0 到 BUF_SIZE-1 的连续数值,实验成功。

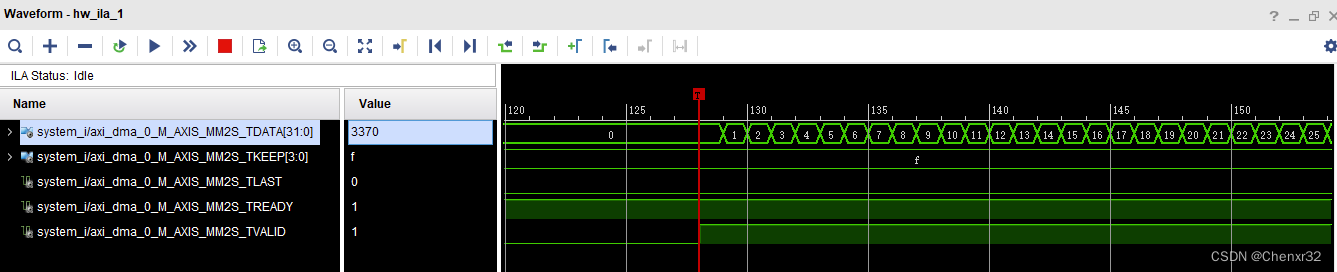

dma_frame_gen 的 m_axis 端口输出波形如下图所示。

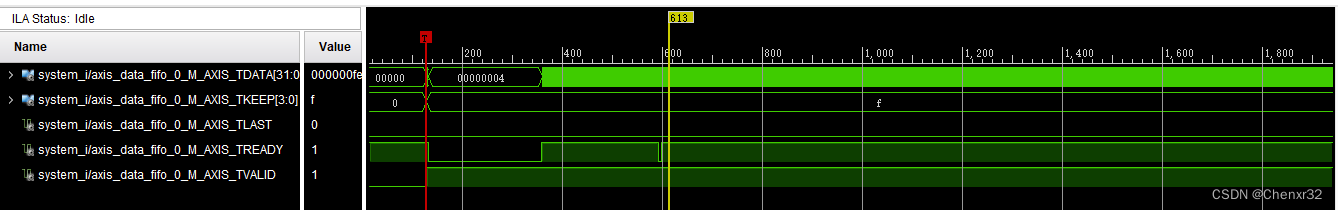

AXI4-Stream Data FIFO 的 M_AXIS 端口输出波形如下图所示。

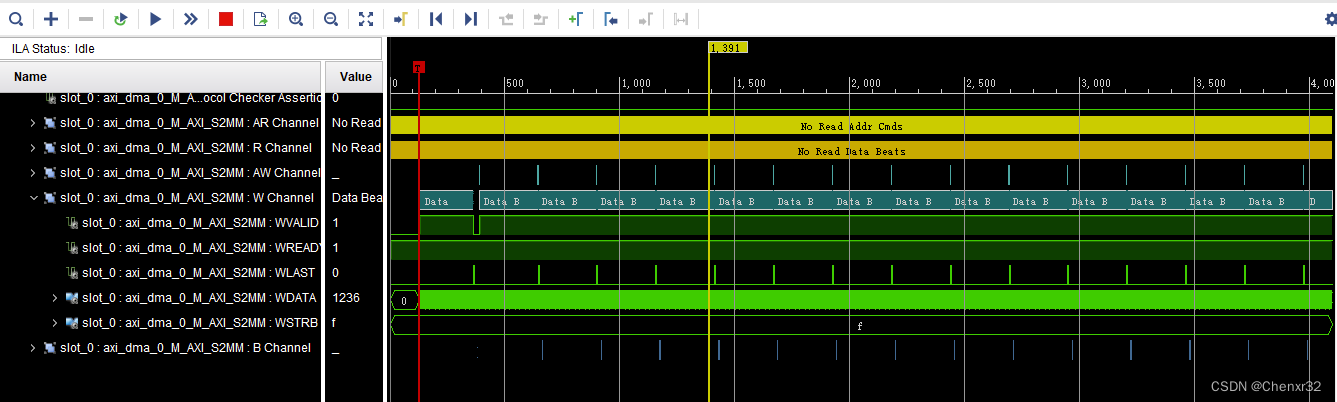

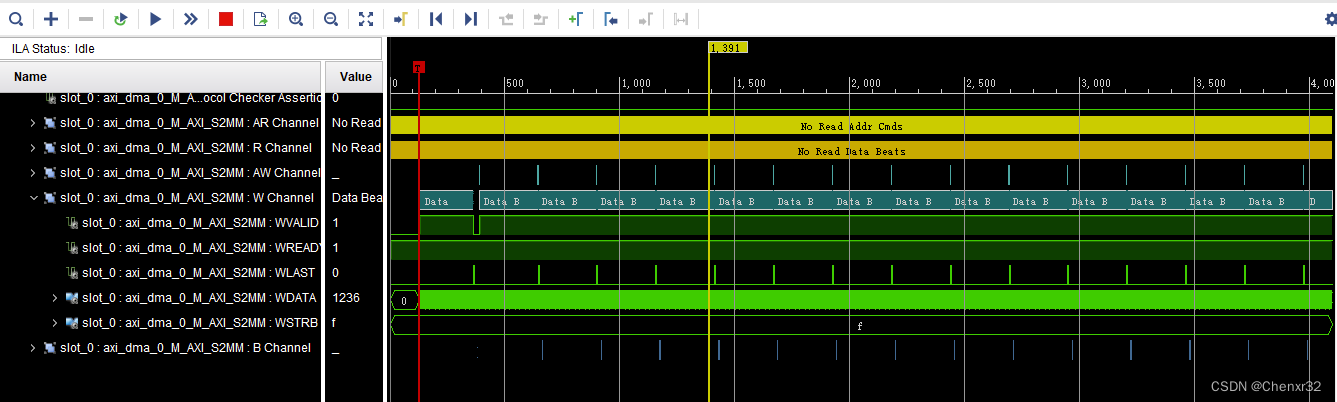

AXI DMA Memory Access 的 M_AXI_S2MM 端口的写通道波形如下图所示。

相关文章:

ZYNQ通过AXI DMA实现PL发送连续大量数据到PS DDR

硬件:ZYNQ7100 软件:Vivado 2017.4、Xilinx SDK 2017.4 ZYNQ PL 和 PS 的通信方式有 AXI GPIO、BRAM、DDR等。对于数据量较少、地址不连续、长度规则的情况,BROM 比较适用。而对于传输速度要求高、数据量大、地址连续的情况,比…...

用于强化学习的置换不变神经网络

一、介绍 如果强化学习代理提供的输入在训练中未明确定义,则通常表现不佳。一种新方法使 RL 代理能够正常运行,即使受到损坏、不完整或混乱的输入的影响也是如此。 “大脑能够使用来自皮肤的信息,就好像它来自眼睛一样。我们不是用眼睛看&…...

【华为OD题库-008】座位调整-Java

题目 疫情期间课堂的座位进行了特殊的调整,不能出现两个同学紧挨着,必须隔至少一个空位。给你一个整数数组desk表示当前座位的占座情况,由若干0和1组成,其中0表示没有占位,1表示占位。在不改变原有座位秩序情况下&…...

4 Paimon数据湖之Hive Catalog的使用

更多Paimon数据湖内容请关注:https://edu.51cto.com/course/35051.html Paimon提供了两种类型的Catalog:Filesystem Catalog和Hive Catalog。 Filesystem Catalog:会把元数据信息存储到文件系统里面。Hive Catalog:则会把元数据…...

Verilog刷题[hdlbits] :Bcdadd100

题目:Bcdadd100 You are provided with a BCD one-digit adder named bcd_fadd that adds two BCD digits and carry-in, and produces a sum and carry-out. 为您提供了一个名为bcd_fadd的BCD一位数加法器,它将两个BCD数字相加并带入,并生…...

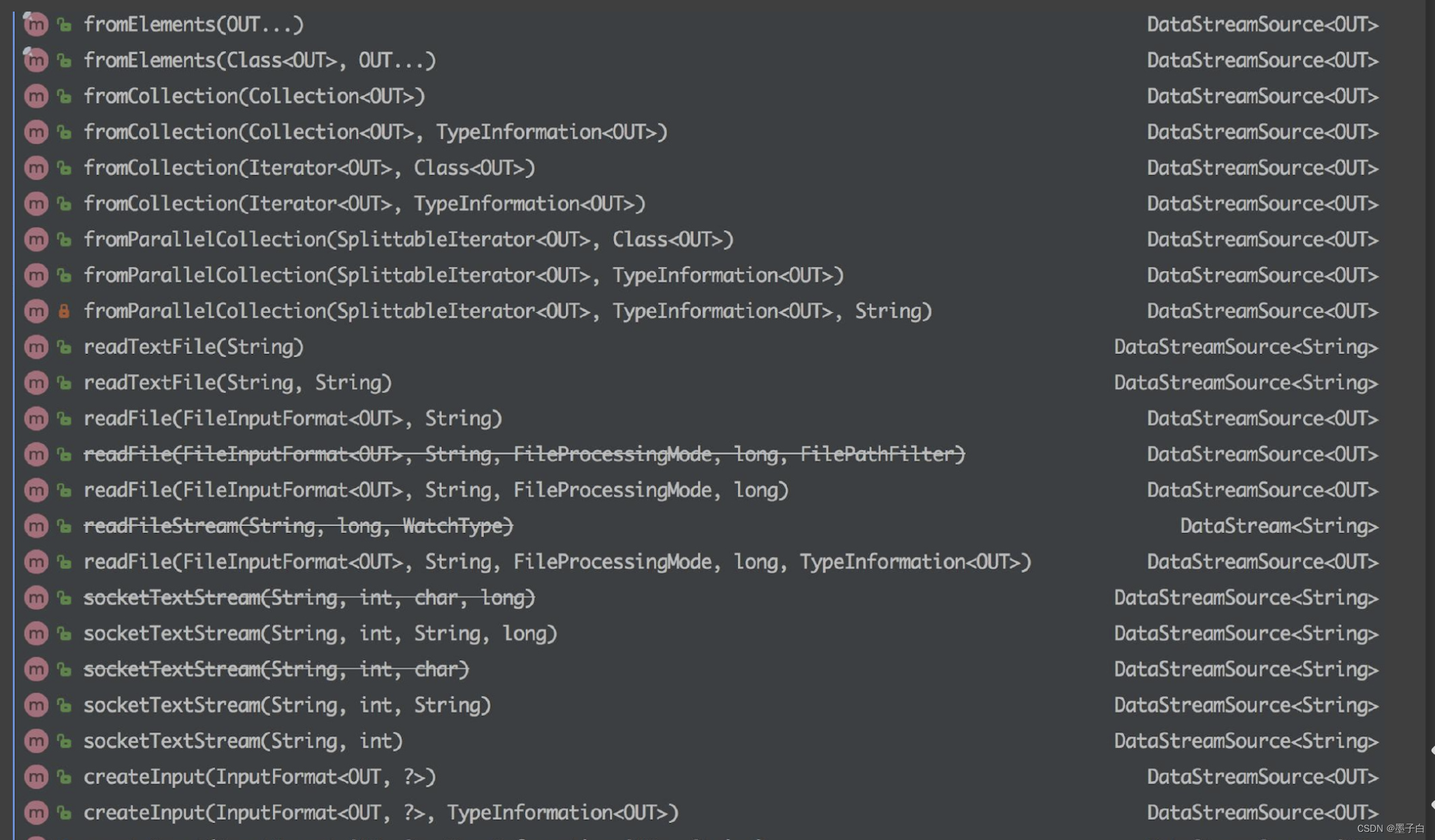

Flink—— Data Source 介绍

Data Source 简介 Flink 做为一款流式计算框架,它可用来做批处理,即处理静态的数据集、历史的数据集;也可以用来做流处理,即实时的处理些实时数据流,实时的产生数据流结果,只要数据源源不断的过来ÿ…...

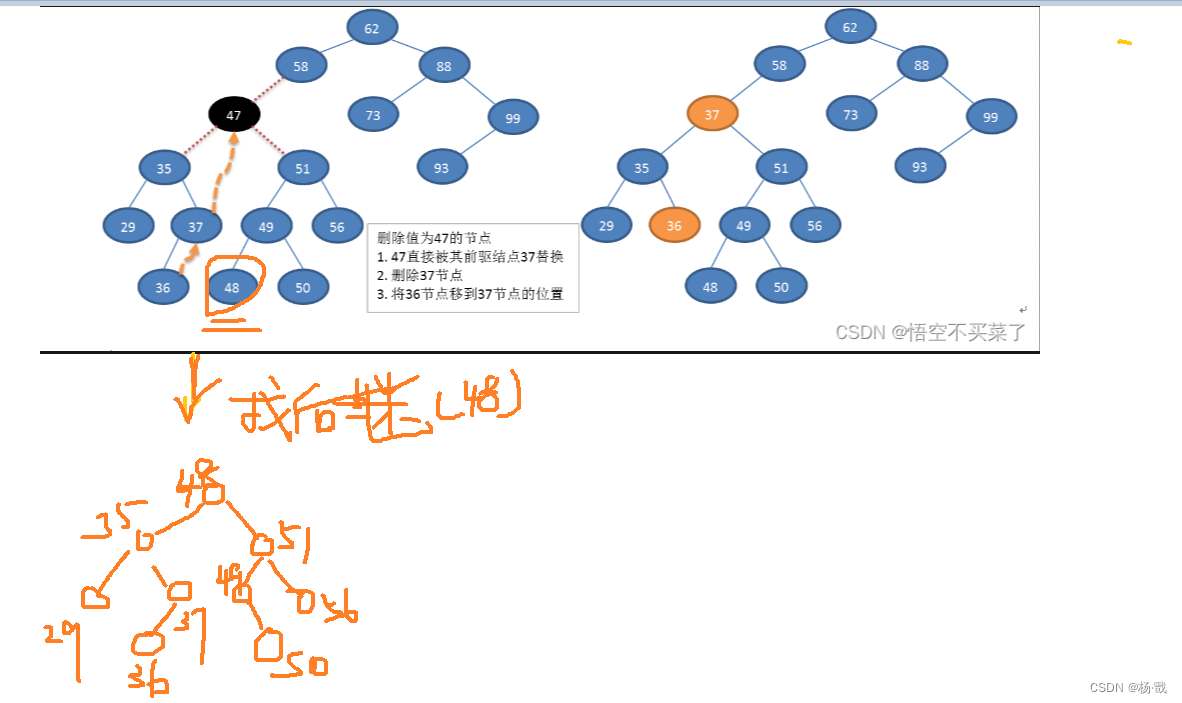

树之二叉排序树(二叉搜索树)

什么是排序树 说一下普通二叉树可不是左小右大的 插入的新节点是以叶子形式进行插入的 二叉排序树的中序遍历结果是一个升序的序列 下面是两个典型的二叉排序树 二叉排序树的操作 构造树的过程即是对无序序列进行排序的过程。 存储结构 通常采用二叉链表作为存储结构 不能 …...

管易云与电商平台的无代码集成:实现API连接与用户运营

管易云简介及其与电商平台的合作 金蝶管易云是金蝶集团旗下以电商为核心业务的子公司,是国内最早的电商ERP服务商之一,总部在上海,与淘宝、天猫、 京东、拼多多、抖音等300多家主流电商平台建立合作关系,同时管易云是互联网平台首…...

)

ElementUI的el-upload上传组件与表单一起提交遇到的各种问题以及解决办法(超详细,每个步骤都有详细解读)

背景: 使用ruoyi-vue进行2次开发,需要实现表单与文件上传一起提交,并且文件上传有4个,且文件校验很复杂,因此ruoyi-vue集成的上传组件FileUpload调试几天后发现真不太适用,最终选择element UI原生组件el-upload(FileUpload也是基于el-upload实现的),要实现表单与文件同…...

python flask_restful “message“: “Failed to decode JSON object: None“

1、问题表现 "message": "Failed to decode JSON object: None"2、出现的原因 Werkzeug 版本过高 3、解决方案 pip install Werkzeug2.0解决效果 可以正常显示json数据了 {"message": {"rate": "参数错误"} }...

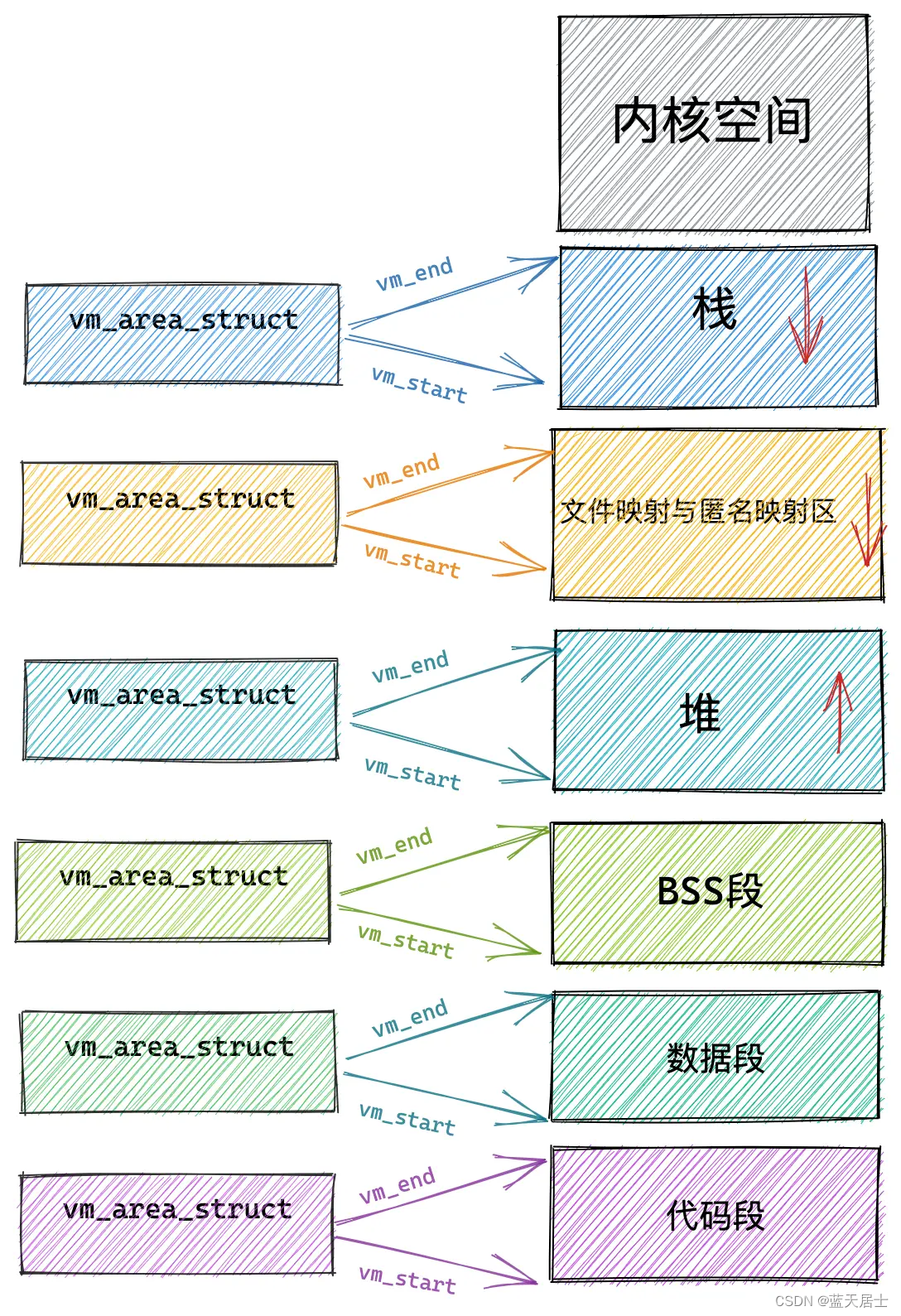

Linux内核有什么之内存管理子系统有什么第六回 —— 小内存分配(4)

接前一篇文章:Linux内核有什么之内存管理子系统有什么第五回 —— 小内存分配(3) 本文内容参考: linux进程虚拟地址空间 《趣谈Linux操作系统 核心原理篇:第四部分 内存管理—— 刘超》 特此致谢! 二、小…...

)

【OpenHarmony内核】Harmony内核之线程操作函数(二)

文章目录 前言一、获取线程优先级二、转交控制运行权三、挂起线程3.1 线程的挂起是什么意思?3.2 函数介绍四、恢复线程五、分离指定的线程5.1 分离线程是什么意思5.2 函数介绍六、等待线程终止运行七、终止当前线程的运行八、终止指定线程的运行九、获取活跃线程数总结前言 O…...

二十五、W5100S/W5500+RP2040树莓派Pico<Modebus TCP Server示例>

文章目录 1 前言2 简介2 .1 什么是Modbus TCP?2.2 Modbus TCP指令介绍2.3 请求数据过程2.4 Modbus TCP协议优点2.5 Modbus TCP应用场景 3 WIZnet以太网芯片4 Modbus TCP示例概述以及使用4.1 流程图4.2 准备工作核心4.3 连接方式4.4 主要代码概述4.5 结果演示 5 注意…...

Android画个圆点状态灯

1、创建一个 XML 文件在 res/drawable 目录下(默认为黑色) <?xml version"1.0" encoding"utf-8"?> <shape xmlns:android"http://schemas.android.com/apk/res/android"android:shape"oval"><…...

高性能网络编程 - 解读3种线程模型

文章目录 Pre线程模型1:传统阻塞 I/O 服务模型线程模型2:Reactor 模式Reactor 模式的基本设计思想Reactor 模式中的关键组成3种典型实现单 Reactor 单线程单 Reactor 多线程主从 Reactor 多线程 小结 线程模型3:Proactor 模型 Pre 高性能网络…...

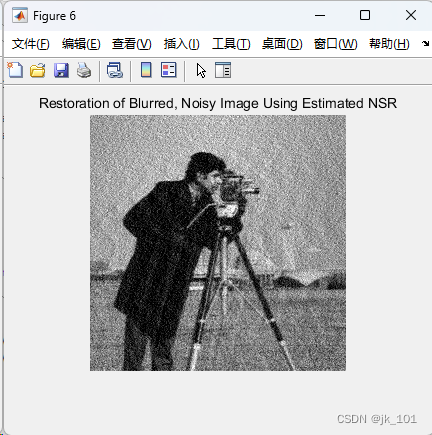

MATLAB中deconvwnr函数用法

目录 语法 说明 示例 使用 Wiener 滤波对图像进行去模糊处理 deconvwnr函数的功能是使用 Wiener 滤波对图像进行去模糊处理。 语法 J deconvwnr(I,psf,nsr) J deconvwnr(I,psf,ncorr,icorr) J deconvwnr(I,psf) 说明 J deconvwnr(I,psf,nsr) 使用 Wiener 滤波算法对…...

赛宁网安入选国家工业信息安全漏洞库(CICSVD)2023年度技术组成员单

近日,由国家工业信息安全发展研究中心、工业信息安全产业发展联盟主办的“2023工业信息安全大会”在北京成功举行。 会上,国家工业信息安全发展研究中心对为国家工业信息安全漏洞库(CICSVD)提供技术支持的单位授牌表彰。北京赛宁…...

Git系列之Git集成开发工具及git扩展使用

🎉🎉欢迎来到我的CSDN主页!🎉🎉 🏅我是君易--鑨,一个在CSDN分享笔记的博主。📚📚 🌟推荐给大家我的博客专栏《Git实战开发》。🎯🎯 &a…...

selenium headless 无头模式慢

selenium设置headlessTrue发现非常慢,headlessFalse要快很多。 最后测试发现升级到selenium最新版本,selenium4.15.2。设置--headlessnew,解决了,速度正常了。 新版selenium有了两种headless模式,参见:He…...

快速修复因相机断电导致视频文件打不开的问题

3-5 本文主要解决因相机突然断电导致拍摄的视频文件打不开的问题。 在日常工作中,有时候需要使用相机拍摄视频,比如现在有不少短视频拍摄的需求,如果因电池突然断电的原因,导致拍出来的视频播放不了,这时候就容易出大…...

)

Win10家庭版升级专业版后,5分钟搞定VMware与Device Guard的兼容问题(附完整代码)

Win10专业版环境下VMware与Device Guard冲突的深度解决方案 当Windows 10家庭版用户升级到专业版后,往往会遇到一个棘手问题:VMware等虚拟机软件与系统内置的Device Guard和Credential Guard安全功能产生冲突。这种兼容性问题不仅影响虚拟机的正常使用&a…...

)

别再写跨线程异常了!WPF中Application.Current.Dispatcher的3种实战用法(附CheckAccess避坑)

WPF多线程UI更新实战:Dispatcher的深度应用与避坑指南 在WPF开发中,跨线程操作UI元素是个永恒的话题。每当看到"调用线程无法访问此对象"的异常提示,开发者们都会会心一笑——这几乎是每个WPF程序员成长路上的必经之痛。本文将带你…...

RK3588项目实战:手把手教你集成RTL8188EU驱动并优化WiFi连接稳定性

RK3588项目实战:手把手教你集成RTL8188EU驱动并优化WiFi连接稳定性 在智能硬件开发中,稳定可靠的无线网络连接往往是产品体验的关键。RK3588作为一款高性能处理器,搭配经济高效的RTL8188EUS USB WiFi模块,成为许多嵌入式设备的理想…...

Matchering 的未来发展:音频AI技术的前景与挑战

Matchering 的未来发展:音频AI技术的前景与挑战 【免费下载链接】matchering 🎚️ Open Source Audio Matching and Mastering 项目地址: https://gitcode.com/gh_mirrors/ma/matchering Matchering 作为一款开源音频匹配与母带处理工具ÿ…...

如何用 dispatchEvent 在 window 全局触发自定义的消息通知

直接在window上用dispatchEvent触发自定义消息通知,核心是创建带数据的CustomEvent并派发到全局作用域;通过new CustomEvent(type,{detail:data})创建事件,window.dispatchEvent()派发,可统一封装为window.emit()函数,…...

【王炸组合】Hermes Agent 官方 UI 发布:本地白嫖 Google Gemma 4,零成本打造最强微信 AI 助手

前言如果说 2025 年是 AI 大模型的爆发年,那么 2026 年 4 月就是“个人 AI 智能体”的普及元年。随着 Gemma 4(Google 4月2日刚刚发布,31B 性能直逼 GPT-4o)的开源,以及 Hermes Agent 终于告别了繁琐的命令行、发布了正…...

省钱攻略:在AutoDL上用网盘离线安装PyTorch和Transformers,避开pip超时

AutoDL云平台深度学习环境搭建:网盘离线安装PyTorch全攻略 在按小时计费的云GPU平台上,每一分钟都在消耗真金白银。最近帮团队优化AutoDL环境搭建流程时发现,90%的实例启动时间浪费在pip安装环节——网络波动导致重复下载、依赖冲突引发环境崩…...

TorchTitan分布式训练终极审计指南:资源使用与能效深度分析

TorchTitan分布式训练终极审计指南:资源使用与能效深度分析 【免费下载链接】torchtitan A PyTorch native platform for training generative AI models 项目地址: https://gitcode.com/GitHub_Trending/to/torchtitan TorchTitan作为PyTorch原生的生成式AI…...

Flutter Easy Refresh多平台适配:Web、Android、iOS统一体验终极指南

Flutter Easy Refresh多平台适配:Web、Android、iOS统一体验终极指南 【免费下载链接】flutter_easy_refresh A flutter widget that provides pull-down refresh and pull-up load. 项目地址: https://gitcode.com/gh_mirrors/fl/flutter_easy_refresh Flut…...

别再只盯着协议了!手把手教你用示波器实测MIPI D-PHY的HS/LP模式切换波形

示波器实战:深度解析MIPI D-PHY模式切换的波形捕获技巧 当你在调试一块搭载MIPI接口的摄像头模组时,是否遇到过图像传输不稳定、画面闪烁甚至完全无信号的问题?这些现象往往与D-PHY在高速模式(HS)和低功耗模式(LP)之间的切换时序异常有关。本…...