FPGA采集AD7606全网最细讲解 提供串行和并行2套工程源码和技术支持

目录

- 1、前言

- 2、AD7606数据手册解读

- 输入信号采集范围

- 输出模式选择

- 过采样率设置

- 3、AD7606串行输出采集

- 4、AD7606并行输出采集

- 5、vivado仿真

- 6、上板调试验证

- 7、福利:工程代码的获取

1、前言

AD7606是一款非常受欢迎的AD芯片,因为他支持8通道同时采集数据,采样深度16位,已经很不错了,虽然采样率只有200 kSPS,但对电压等低速数据源的采集而言已经完全足够了,该芯片在电压检测等项目中有着广泛应用。

本文详细描述了设计方案,工程代码编译通过后上板调试验证,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做项目开发,可应用于AD数据采集领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

2、AD7606数据手册解读

AD7606英文原版数据手册只有37页,但真正看懂的兄弟却很少,下面解读一下这个手册:

DAQ7606 是 16 位 8 通道同步采样模数数据采集系统(DAS)。

AD7606 内置模拟输入箝位保护、二阶抗混叠滤波器、跟踪保持放大器、16 位电荷再分配逐次逼近型 ADC、灵活的数字滤波器、2.5V 基准电压源、基准电压缓冲以及高速串行和并行接口。AD7606 采用 5V 单电源供电,可以处理±10V 和±5V 真双极性输入信号,同时所有通道均能以高达 200 kSPS 的吞吐速率采样。输入箝位保护电路可以耐受最高达±16.5V 的电压。无论以何种采样频率工作,AD7606 的模拟输入阻抗均为 1 MΩ。它采用单电源工作方式,具有片内滤波和高输入阻抗,因此无需驱动运算放大器和外部双极性电源。AD7606 抗混叠滤波器的 3 dB 截止频率为 22 kHz;当采样速率为 200 ksps 时,它具有 40 dB 抗混叠抑制特性。灵活的数字滤波器采用引脚驱动,可以改善信噪比(SNR),并降低 3 dB 带宽。

写了这么多你看懂了吗?

我猜你应该是云里雾里,下面举例说人话,让你听得懂:

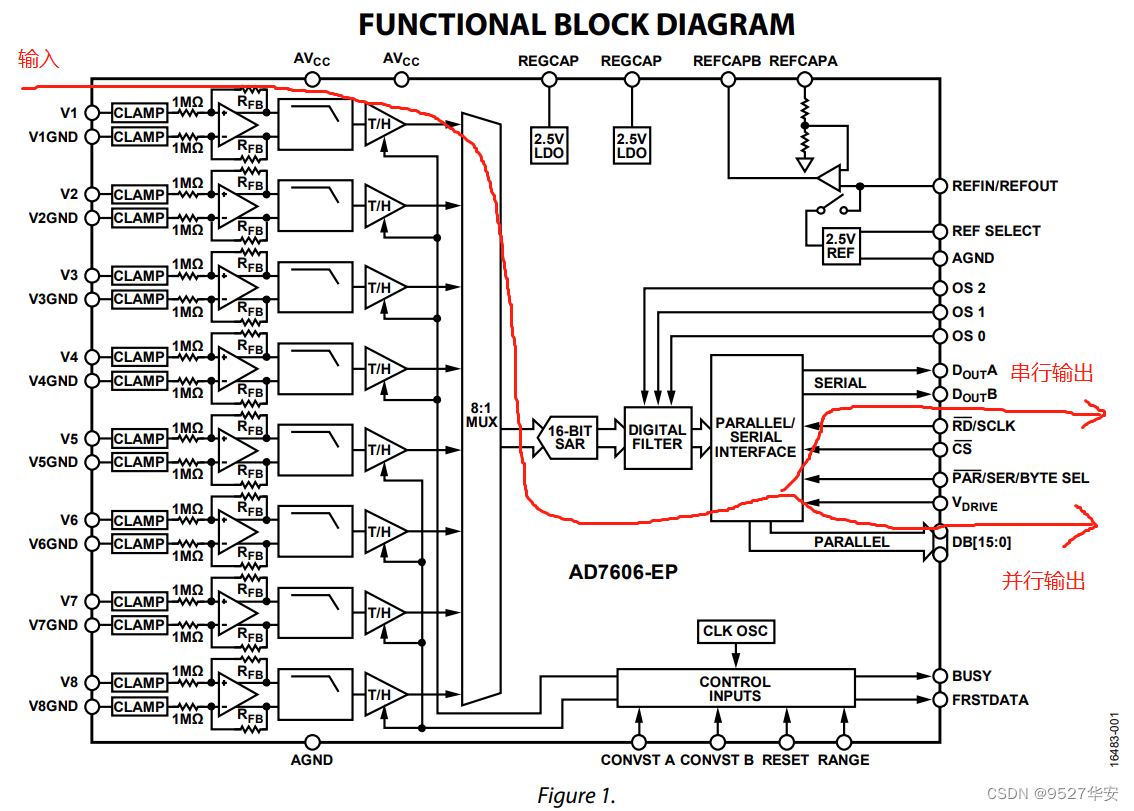

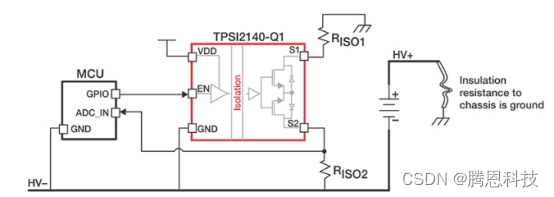

AD7606芯片框图如下:

红线即是信号输出输出的数据通路;

输入信号采集范围

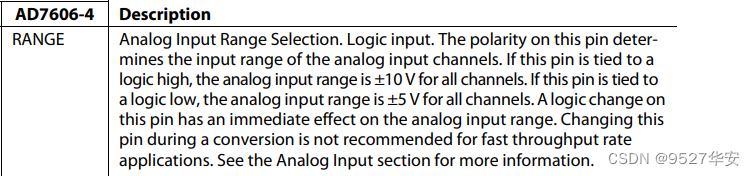

AD7606可以处理±10V 和±5V 真双极性输入信号,即输入信号可以是±10V 和±5V,由RANGE引脚上下拉决定;

下拉处理±5V 信号;

上拉处理±10V 信号;

一旦选择了输入信号范围,就别乱给信号源了,否则烧板子了。。。

原文如下:

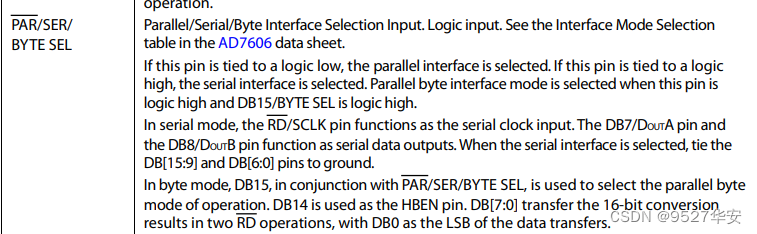

输出模式选择

红线以通道1为例:

输入数据位单端模拟数据,进过复杂的转换后可输出串行数字信号或者并行数据信号;

如果你的板子设计引脚资源有限,则选择串行输出;串行输出的优点是节约IO,缺点是采集时序复杂些;

如果你的板子设计引脚足够多,则选择并行输出,并行输出数据线占用16个IO口,并行输出的优点是采集时序简单,缺点是费IO;可自行选择;

输出模式选择通过PAR/SER/BYTE SEL引脚的上下拉决定;

上拉选择串行输出;

下拉选择并行输出;

具体的时序细节放在后面的章节;

原文如下:

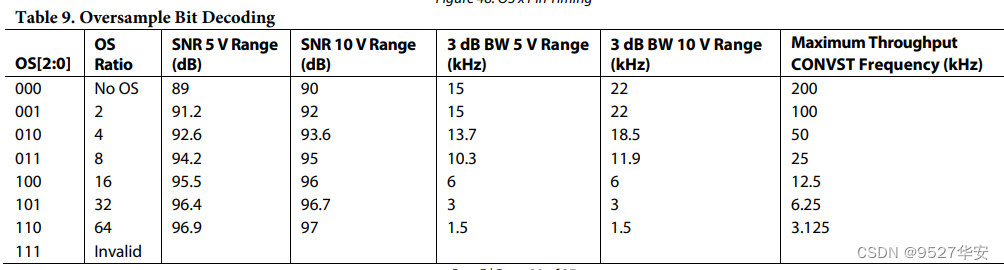

过采样率设置

过采样率设置由OS的三个引脚上下拉决定,可以固定用电阻上下拉,这种模式就定死了,除非飞线,也可以用FPGA引脚给高低电平配置,具体配置模式如下图:

作为FPGA开发者,需要知道这些就行了,具体的时序细节放在后面的章节;

3、AD7606串行输出采集

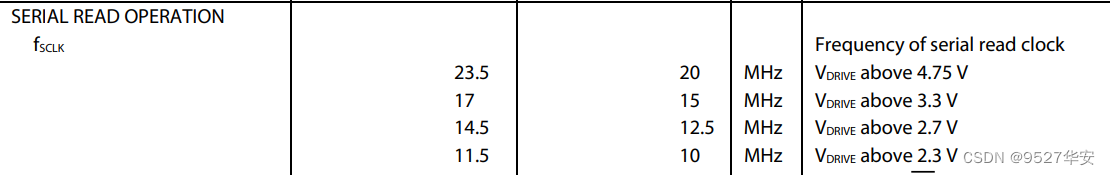

AD7606串行采集时钟的范围要求如下:

这里我们选择16.666MHz时钟,不高也不低;

系统参考时钟选择100M,那个1个时钟周期就是1000÷100=10ns;

采集时钟是16.666M,那个1个时钟周期就是1000÷16.666=60ns;

记住这两个时钟周期,很重要;

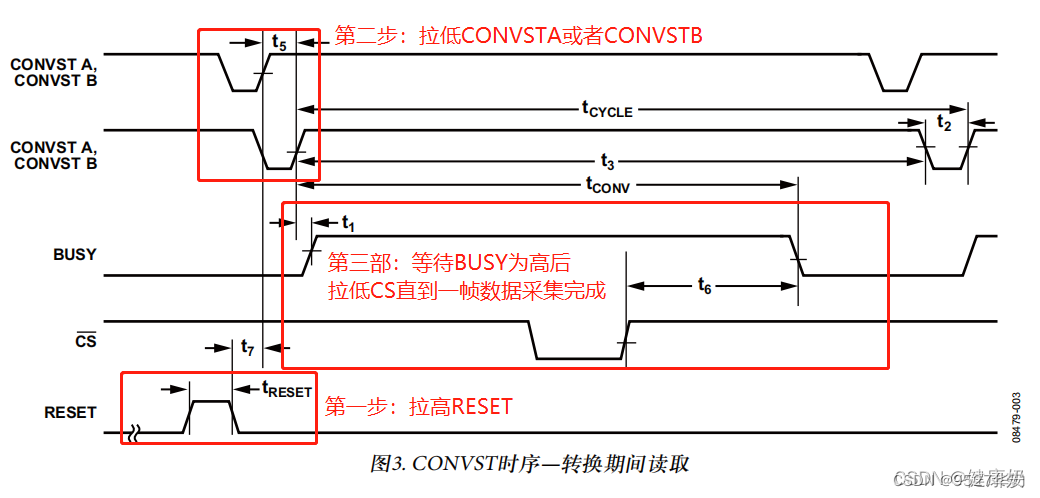

串行输出流程时序图如下:

这张图采用边转换边读取的方式,还有转换完成后再读取的方式,既然可以边转换边读取,为何还要等转换完成后再读取呢?所以我们直接用这种方式。

并行采集使用的则是转换完成后再读取的方式。

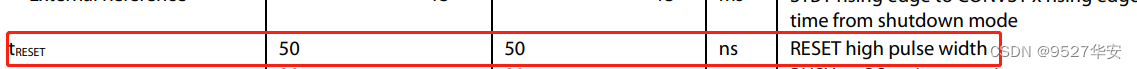

第一步:拉高RESET引脚至少至少50ns,数据手册规定如下:

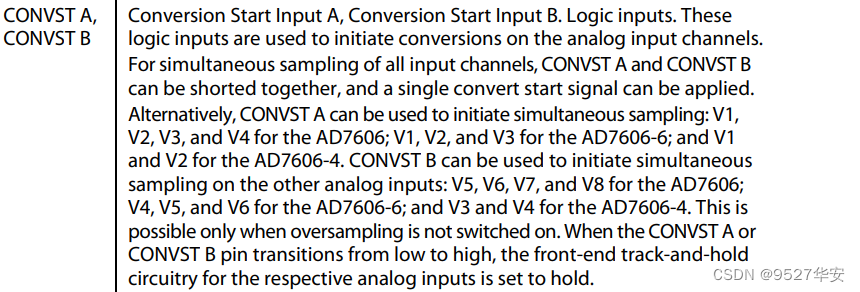

第二步:拉低CONVSTA或者CONVSTB持续最多0.5ms(500ns),注意这里是最多,所以在代码里只需一个参考时钟周期足以,比如你用的100M,一个参考时钟周期就是10ns,当然,CONVSTA和CONVSTB也可同时拉低,这样就是8个通道同时采集,时间由数据手册得知,如下:

CONVSTA开启V1-V4通道的转换;

CONVSTB开启V5-V8通道的转换;

原文如下:

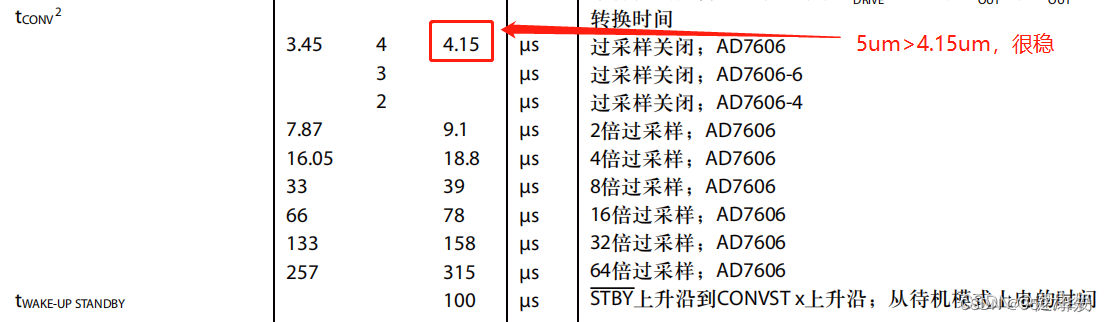

第三步:等待BUSY为高后,拉低CS,这个BUSY是AD7606输出给用户的,表征AD转换正在进行,他有一个最大时间,我们一定要满足他的最大时间,不然人家还没转换完你就结束采集了,岂不唧唧了;那么,CS在什么时刻拉低呢?既然前面我们已经选择了边转换边读取的方式,所以在BUSY拉高的期间CS拉低,数据手册最大推荐4.15us,代码里直接设置5ms,由数据手册得知,如下:

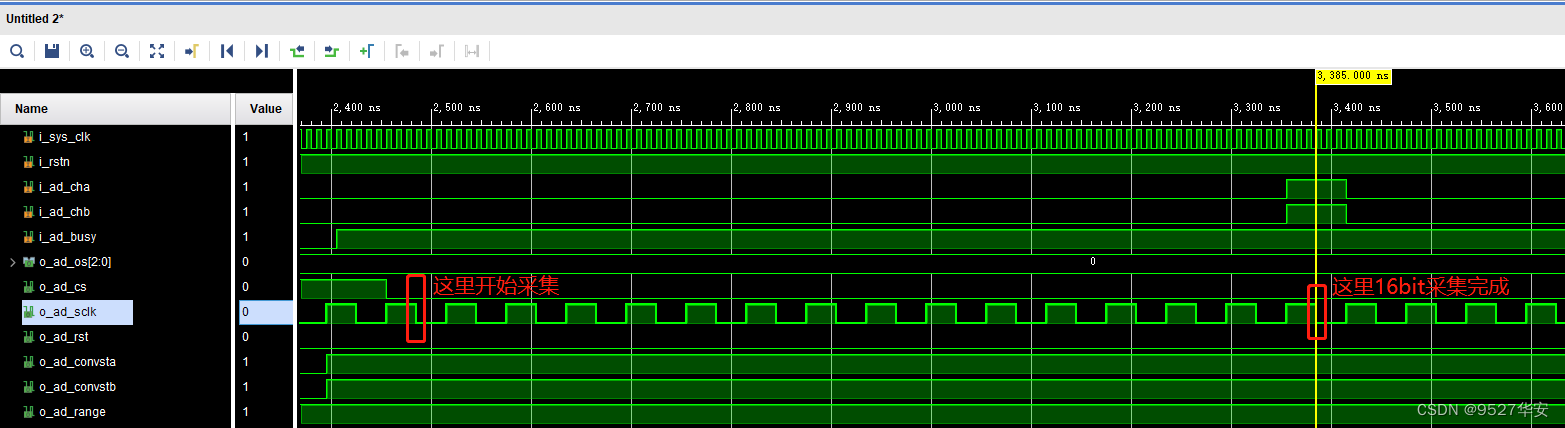

流程看完了,来看具体的采集时序:

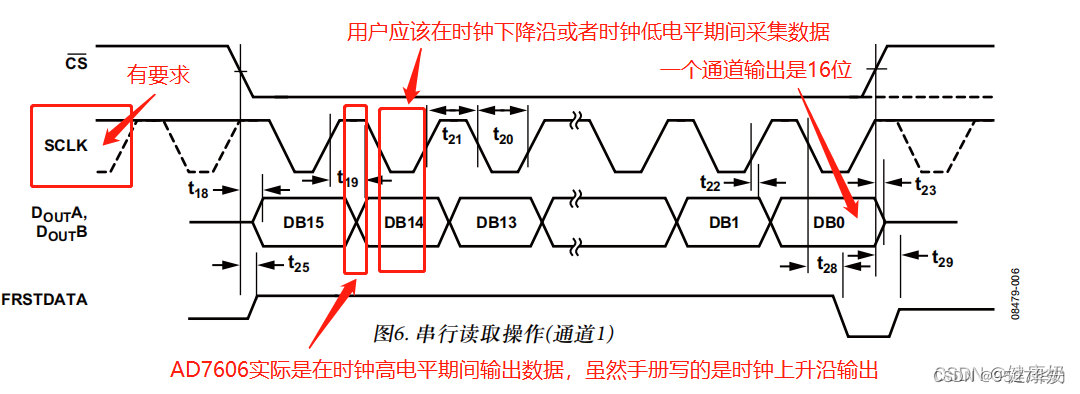

采集时序如下:

首先用户拉低CS,并给出SCLK到AD7606,AD7606在CS为低期间,在SCLK的上升沿输出数据(但根据时序图,我感觉是SCLK高电平期间输出的),一个通道一次转换后输出16位采样数据;

既然AD7606是在SCLK上升沿输出,那么FPGA就应该在SCLK下降沿采集(或者低电平采集);

AD7606有8个模拟输入通道,串行输出模式下只有两个数字输出通道,每个输入通道输出16位采样数据;

DOUTA对应CH1、CH2、CH3、CH4四个输出通道;

DOUTB对应CH5、CH6、CH7、CH8四个输出通道;

因为每个输入通道输出16位采样数据,需要16个SCLK周期,所以4个输入通道输出16位采样数据,需要64个SCLK周期;那个我们需要一个计数器,计数到64时输出64位的采集数据,呢么采集到的每个通道数据对应如下:

wire [15:0] ad_ch1 = ad_out_a[63:48];

wire [15:0] ad_ch2 = ad_out_a[47:32];

wire [15:0] ad_ch3 = ad_out_a[31:16];

wire [15:0] ad_ch4 = ad_out_a[15: 0];

wire [15:0] ad_ch5 = ad_out_b[63:48];

wire [15:0] ad_ch6 = ad_out_b[47:32];

wire [15:0] ad_ch7 = ad_out_b[31:16];

wire [15:0] ad_ch8 = ad_out_b[15: 0];

转换状态机部分源码如下:

always @(posedge i_sys_clk) beginif(o_ad_rst||!i_rstn) beginad_convst <= 1'b1; AD_S <= 2'd0; endelse begincase(AD_S) 2'd0: beginif(p_ad_sclk) begin //开启8通道转换 ad_convst <= 1'b0;AD_S <= 2'd1;endend 2'd1: beginif(p_ad_sclk)begin //转换时间最大500ns,这里60ns即可ad_convst <= 1'b1; AD_S <= 2'd2;endend 2'd2: beginif(p_ad_sclk&&i_ad_busy) AD_S <= 2'd3; //BUSY拉高,进入采集数据状态 end2'd3: beginif(cycle_end) AD_S <= 2'd0; //转换结束,重新采集 enddefault: ;endcase end

end

串行采集代码顶层接口代码如下:

module helai_ad7606_ser#(parameter SYS_CLK = 100_000_000, //系统时钟parameter SPI_CLK = 16_666_666 //AD采集时钟

)

(input i_sys_clk , //系统时钟 input i_rstn , //系统复位,低有效input i_ad_cha , //AD7606串行输出通道Ainput i_ad_chb , //AD7606串行输出通道B input i_ad_busy , //输入BUSYoutput [2:0] o_ad_os , //输出采样率配置output o_ad_cs , //输出片选output reg o_ad_sclk , //输出采样时钟output o_ad_rst , //输出复位output o_ad_convsta, //输出开启V1-V4通道采集output o_ad_convstb, //输出开启V5-V8通道采集output o_ad_range , //输入信号范围配置output [15:0] o_ad_ch1 , //输出通道1output [15:0] o_ad_ch2 , //输出通道2output [15:0] o_ad_ch3 , //输出通道3output [15:0] o_ad_ch4 , //输出通道4output [15:0] o_ad_ch5 , //输出通道5output [15:0] o_ad_ch6 , //输出通道6output [15:0] o_ad_ch7 , //输出通道7output [15:0] o_ad_ch8 , //输出通道8output o_ad_rxdone //输出数据有效信号,高有效);

4、AD7606并行输出采集

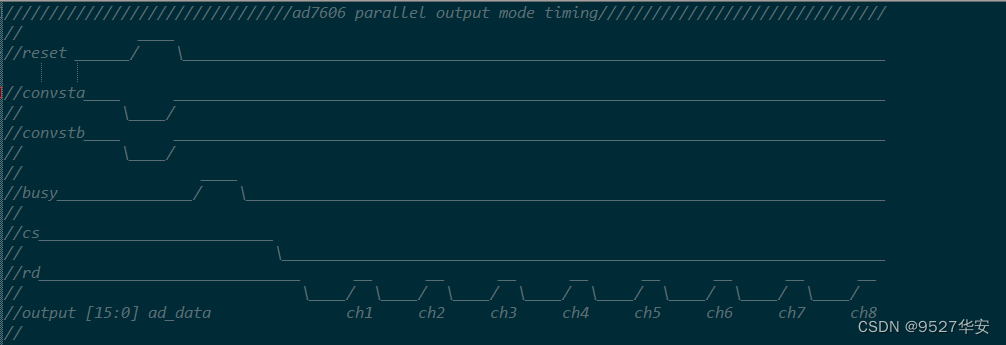

并行采集时序,由于官方画的图太繁琐,我直接重画了一个图来表示,如下:

第一步:拉高RESET引脚至少至少50ns,和串行采集一样;

第二步:拉低CONVSTA或者CONVSTB持续最多0.5ms(500ns),和串行采集一样;

第三步:等待转换完成再读取数据,即采用转换完成后再读取的方式;

第四步:拉低CS片选信号;

第五步:拉低RD信号,在RD和CS同时为低时即可依次读取V1-V8通道的数据;

相应的时间问题也是重要的,具体查看手册;

并行采集代码顶层接口代码如下:

module helai_ad7606_par(input clk , //系统时钟,100M input rst_n , //系统复位,低有效input [15:0] ad_data , //输入并行数据input ad_busy , //输入BUSYinput first_data , //未用到此信号output [2:0] ad_os , //输出采样率配置output reg ad_cs , //输出片选output reg ad_rd , //输出读数据output reg ad_reset , //输出复位output reg ad_convstab , //输出开启V1-V8通道采集output ad_data_valid, //输出数据有效信号,高有效output reg [15:0] ad_ch1 , //输出通道1output reg [15:0] ad_ch2 , //输出通道2output reg [15:0] ad_ch3 , //输出通道3output reg [15:0] ad_ch4 , //输出通道4output reg [15:0] ad_ch5 , //输出通道5output reg [15:0] ad_ch6 , //输出通道6output reg [15:0] ad_ch7 , //输出通道7output reg [15:0] ad_ch8 //输出通道8

);

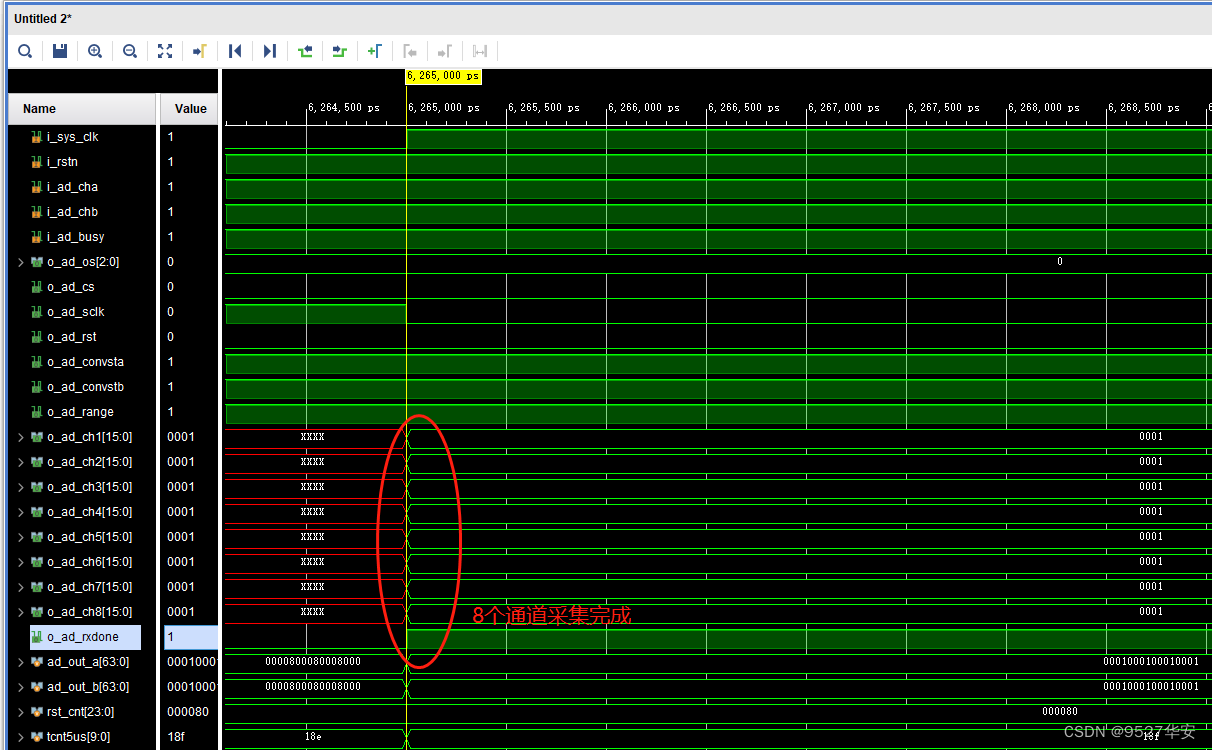

5、vivado仿真

仅提供了串行采集的仿真,文件如下;

vivado仿真如下:

6、上板调试验证

请参考我之前写的基于zynq7100使用AD7606进行电压监测的文章点击查看:AD7606工程

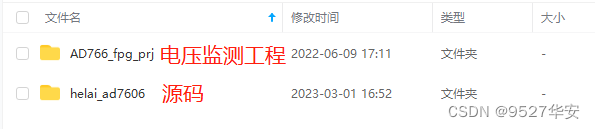

7、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

相关文章:

FPGA采集AD7606全网最细讲解 提供串行和并行2套工程源码和技术支持

目录1、前言2、AD7606数据手册解读输入信号采集范围输出模式选择过采样率设置3、AD7606串行输出采集4、AD7606并行输出采集5、vivado仿真6、上板调试验证7、福利:工程代码的获取1、前言 AD7606是一款非常受欢迎的AD芯片,因为他支持8通道同时采集数据&am…...

CSS介绍

文章目录一. CSS介绍二. CSS的引入方式三. CSS选择器一. CSS介绍 定义: 层叠样式表作用: 美化界面: 设置标签文字大小,颜色,字体加粗等样式控制页面布局: 设置浮动,定位等样式 基本语法: 选择器{样式规则 } 样式规则: 属性名1: 属性值1 属性名2: 属性值2 属性名3: 属性值3 ..…...

Auto-encoder 系列

Auto-Encoder (AE)Auto-encoder概念自编码器要做的事:将高维的信息通过encoder压缩到一个低维的code内,然后再使用decoder对其进行重建。“自”不是自动,而是自己训练[1]。PCA要做的事其实与AE一样,只是没有神经网络。对于一个输入…...

【蓝桥杯入门不入土】变幻莫测的链表

文章目录一:链表的类型单链表双链表循环链表二:链表的存储方式三:链表的定义删除节点添加节点四:实战练习1.设计链表2. 移除链表元素最后说一句一:链表的类型 单链表 什么是链表,链表是一种通过指针串联在…...

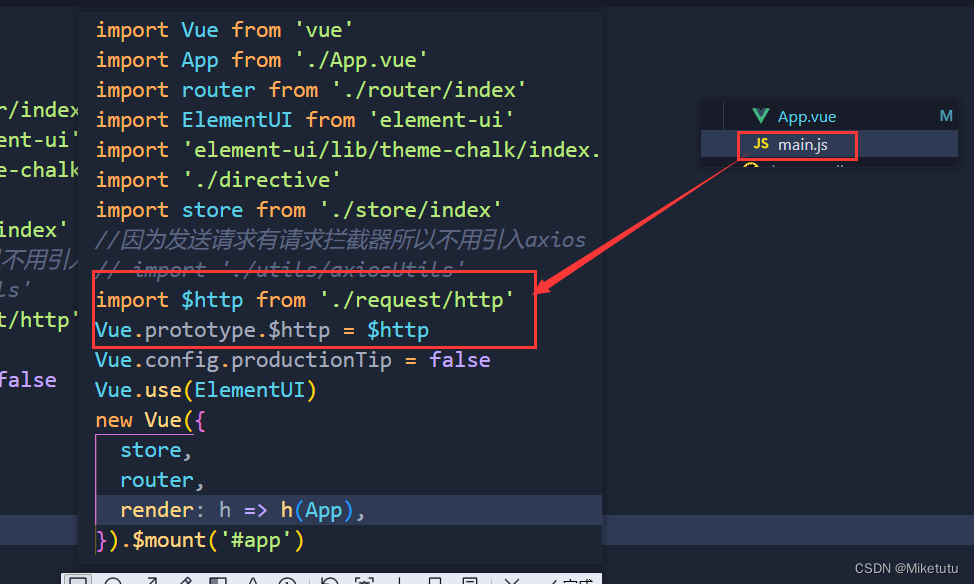

axios的二次封装

方式一:将axios单独分装到某个配置文件中import axios from axios; const axiosApi axios.create({baseURL:http://127.0.0.1:3000,timeout:3000 }) export default axiosApi在组件中使用:import $http from axios配置文件的地址 $http.get(/student/test).then(re…...

)

GET与POST区别(最详细)

相同点:本质上都是TCP连接。 不同点:由于HTTP规定和服务器/浏览器限制,在应用过程中区别如下: 1.get产生一个TCP数据包,post 产生两个TCP数据包 get请求,浏览器会把http header和data一起发送,…...

精选博客系列|将基于决策树的Ensemble方法用于边缘计算

在即将到来的边缘计算时代,越来越需要边缘设备执行本地快速训练和分类的能力。事实上,无论是手机上的健康应用程序、冰箱上的传感器还是扫地机器人上的摄像头,由于许多原因,例如需要快速响应时间、增强安全性、数据隐私࿰…...

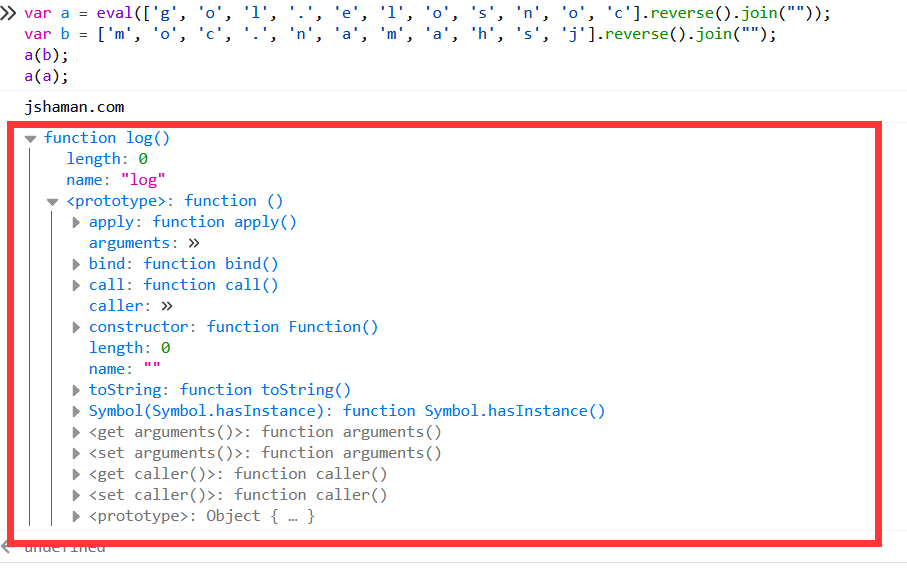

JS混淆加密:Eval的未公开用法

JavaScript奇技淫巧:Eval的未公开用法 作者:http://JShaman.com w2sft,转载请保留此信息很多人都知道,Eval是用来执行JS代码的,可以执行运算、可以输出结果。 但它还有一种未公开的用途,想必很少有人用过。…...

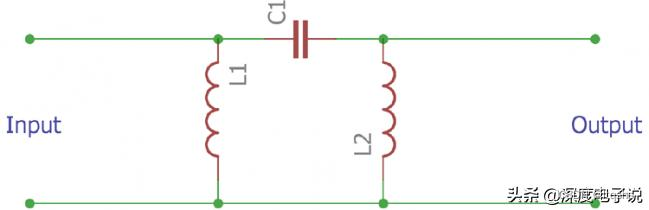

π型滤波器 计算_π型滤波电路

滤波器在功率和音频电子中常用于滤除不必要的频率。而电路设计中,基于不同应用有着许多不同种类的滤波器,但它们的基本理念都是一致的,那就是移除不必要的信号。所有滤波器都可以被分为两类,有源滤波器和无源滤波器。有源滤波器用…...

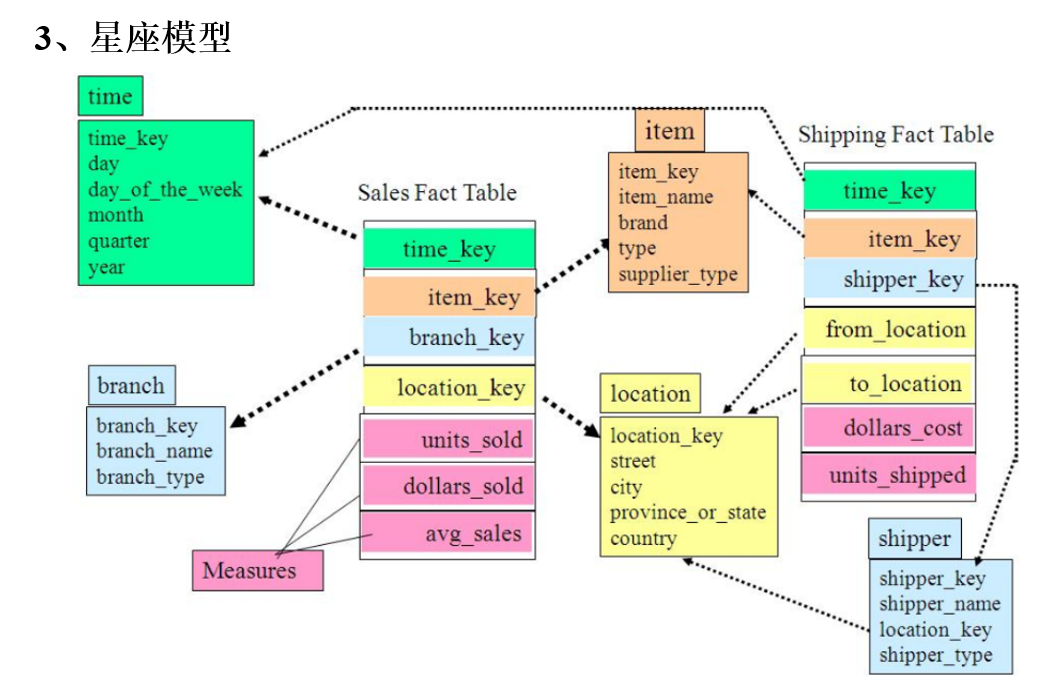

大数据常见术语

大数据常见术语一览 主要内容包含以下(收藏,转发给你身边的朋友) 雪花模型、星型模型和星座模型 事实表 维度表 上钻与下钻 维度退化 数据湖 UV与PV 画像 ETL 机器学习 大数据杀熟 SKU与SPU 即席查询 数据湖 数据中台 ODS,DWD&…...

带你了解“函数递归”

目录 1. 什么是递归? 2. 函数递归的必要条件 2.1 接收一个整型值(无符号),按照顺序打印它的每一位。 代码如下: 2.2 编写一个函数,不用临时变量求字符串长度 代码如下: 2.3 递归与迭代 …...

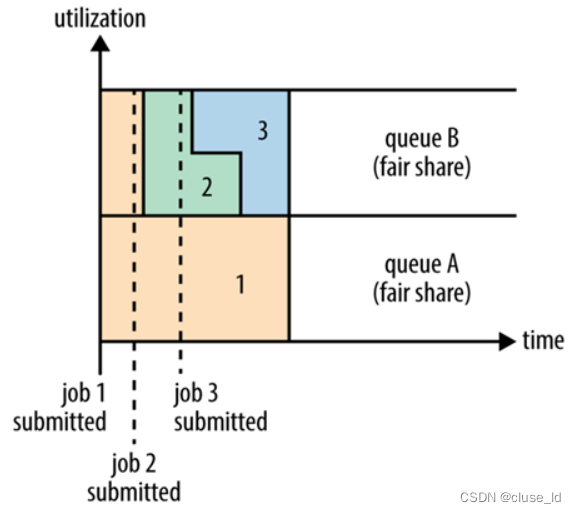

网络资源面经2

文章目录Kafka 原理,数据怎么平分到消费者生产者分区消费者分区Flume HDFS Sink 小文件处理Flink 与 Spark Streaming 的差异,具体效果Spark 背压机制具体实现原理Yarn 调度策略Spark Streaming消费方式及区别Zookeeper 怎么避免脑裂,什么是脑…...

4年经验来面试20K的测试岗,一问三不知,我还真不如去招应届生。

公司前段缺人,也面了不少测试,结果竟然没有一个合适的。一开始瞄准的就是中级的水准,也没指望来大牛,提供的薪资在10-20k,面试的人很多,但平均水平很让人失望。看简历很多都是4年工作经验,但面试…...

K8S搭建NACOS集群踩坑问题

一、NACOS容器启动成功无法访问现象描述:通过K8S的statefulset启动,通过NodePort暴露不能在外网访问,只能在MASTER主节点访问。yaml配置:apiVersion: apps/v1 kind: StatefulSet metadata:name: nacos-${parameters.nameSpace}-dm…...

怎么避免计算机SCI论文的重复率过高? - 易智编译EaseEditing

论文成稿前 在撰写阶段就避免重复:在撰写阶段就避免文章中的重复内容,可以减少后期修改的工作量。 在写作前,可以制定良好的计划和大纲,规划好文章的结构和内容,从而减少重复内容。 加强对相关文献的阅读 为了避免自己…...

uni-app路由拦截

新建一个auth.js /** * description 权限存储函数 */ const authorizationKey Authorization export function getAuthorization() { return uni.getStorageSync(authorizationKey) } export function setAuthorization(authorization) { return uni.setStorageSync(aut…...

如何使用固态继电器实现更高可靠性的隔离和更小的解决方案尺寸

自晶体管发明之前,继电器就已被用作开关。从低压信号安全控制高压系统的能力,如隔离电阻监控,对于许多汽车系统的开发是必要的。虽然机电继电器和接触器的技术多年来有所改进,但设计人员要实现其终身可靠性和快速开关速度以及低噪…...

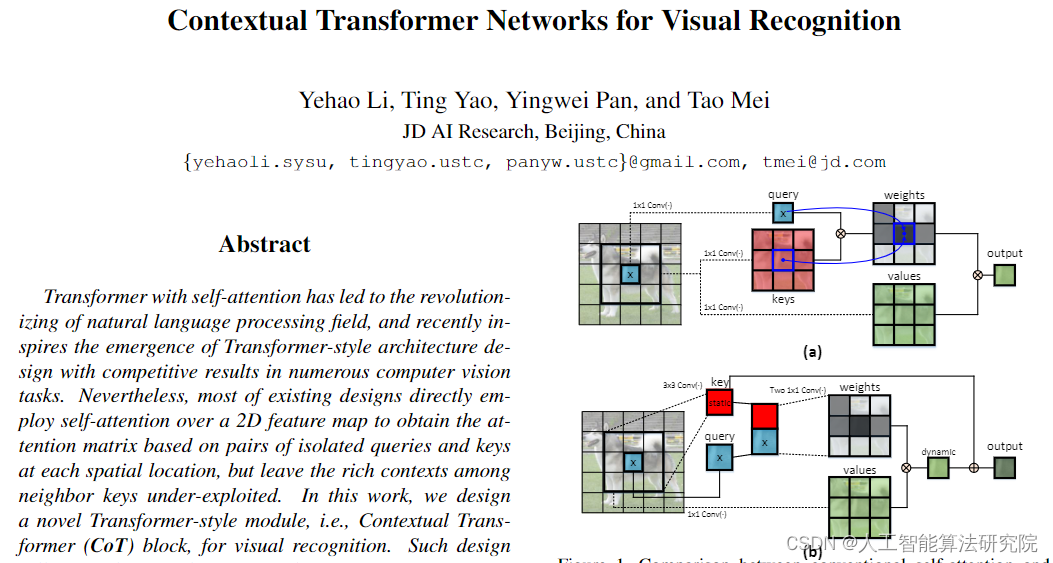

【YOLOv8/YOLOv7/YOLOv5系列算法改进NO.56】引入Contextual Transformer模块(sci期刊创新点之一)

文章目录前言一、解决问题二、基本原理三、添加方法四、总结前言 作为当前先进的深度学习目标检测算法YOLOv8,已经集合了大量的trick,但是还是有提高和改进的空间,针对具体应用场景下的检测难点,可以不同的改进方法。此后的系列…...

深圳大学计软《面向对象的程序设计》实验3 指针2

A. 月份查询(指针数组) 题目描述 已知每个月份的英文单词如下,要求创建一个指针数组,数组中的每个指针指向一个月份的英文字符串,要求根据输入的月份数字输出相应的英文单词 1月 January 2月 February 3月 March …...

【基于机器学习的推荐系统项目实战-2】项目介绍与技术选型

本节目录一、项目介绍1.1 采用的数据源1.2 Concrec架构技术选型1.3 Sprak介绍1.4 Flink1.5 TensorFlow一、项目介绍 1.1 采用的数据源 Kaggle Anime Recommendations Dataset。 其中的动漫数据源自myanimelist.net。 1.2 Concrec架构技术选型 数据预处理模块:汇总…...

)

uniapp 对接腾讯云IM群组成员管理(增删改查)

UniApp 实战:腾讯云IM群组成员管理(增删改查) 一、前言 在社交类App开发中,群组成员管理是核心功能之一。本文将基于UniApp框架,结合腾讯云IM SDK,详细讲解如何实现群组成员的增删改查全流程。 权限校验…...

Rust 异步编程

Rust 异步编程 引言 Rust 是一种系统编程语言,以其高性能、安全性以及零成本抽象而著称。在多核处理器成为主流的今天,异步编程成为了一种提高应用性能、优化资源利用的有效手段。本文将深入探讨 Rust 异步编程的核心概念、常用库以及最佳实践。 异步编程基础 什么是异步…...

大模型多显卡多服务器并行计算方法与实践指南

一、分布式训练概述 大规模语言模型的训练通常需要分布式计算技术,以解决单机资源不足的问题。分布式训练主要分为两种模式: 数据并行:将数据分片到不同设备,每个设备拥有完整的模型副本 模型并行:将模型分割到不同设备,每个设备处理部分模型计算 现代大模型训练通常结合…...

JS手写代码篇----使用Promise封装AJAX请求

15、使用Promise封装AJAX请求 promise就有reject和resolve了,就不必写成功和失败的回调函数了 const BASEURL ./手写ajax/test.jsonfunction promiseAjax() {return new Promise((resolve, reject) > {const xhr new XMLHttpRequest();xhr.open("get&quo…...

BLEU评分:机器翻译质量评估的黄金标准

BLEU评分:机器翻译质量评估的黄金标准 1. 引言 在自然语言处理(NLP)领域,衡量一个机器翻译模型的性能至关重要。BLEU (Bilingual Evaluation Understudy) 作为一种自动化评估指标,自2002年由IBM的Kishore Papineni等人提出以来,…...

深入浅出Diffusion模型:从原理到实践的全方位教程

I. 引言:生成式AI的黎明 – Diffusion模型是什么? 近年来,生成式人工智能(Generative AI)领域取得了爆炸性的进展,模型能够根据简单的文本提示创作出逼真的图像、连贯的文本,乃至更多令人惊叹的…...

【无标题】湖北理元理律师事务所:债务优化中的生活保障与法律平衡之道

文/法律实务观察组 在债务重组领域,专业机构的核心价值不仅在于减轻债务数字,更在于帮助债务人在履行义务的同时维持基本生活尊严。湖北理元理律师事务所的服务实践表明,合法债务优化需同步实现三重平衡: 法律刚性(债…...

【QT控件】显示类控件

目录 一、Label 二、LCD Number 三、ProgressBar 四、Calendar Widget QT专栏:QT_uyeonashi的博客-CSDN博客 一、Label QLabel 可以用来显示文本和图片. 核心属性如下 代码示例: 显示不同格式的文本 1) 在界面上创建三个 QLabel 尺寸放大一些. objectName 分别…...

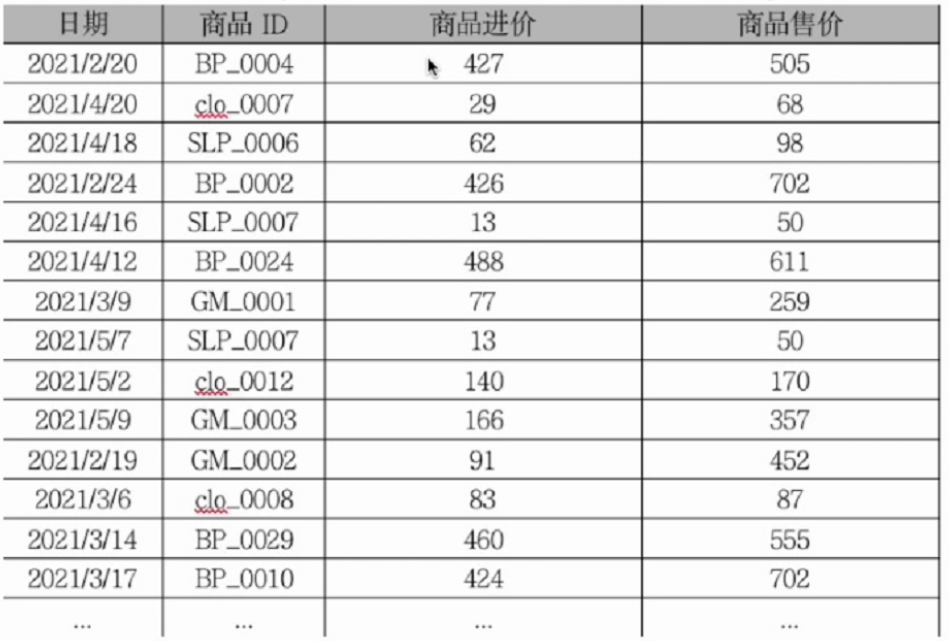

智警杯备赛--excel模块

数据透视与图表制作 创建步骤 创建 1.在Excel的插入或者数据标签页下找到数据透视表的按钮 2.将数据放进“请选择单元格区域“中,点击确定 这是最终结果,但是由于环境启不了,这里用的是自己的excel,真实的环境中的excel根据实训…...

【笔记】结合 Conda任意创建和配置不同 Python 版本的双轨隔离的 Poetry 虚拟环境

如何结合 Conda 任意创建和配置不同 Python 版本的双轨隔离的Poetry 虚拟环境? 在 Python 开发中,为不同项目配置独立且适配的虚拟环境至关重要。结合 Conda 和 Poetry 工具,能高效创建不同 Python 版本的 Poetry 虚拟环境,接下来…...