vivado FIR Filters

Vivado合成直接从RTL中推导出乘加级联来组成FIR滤波器。这种滤波器有几种可能的实现方式;一个例子是收缩滤波器在7系列DSP48E1 Slice用户指南(UG479)中进行了描述,并在8抽头偶数中显示对称收缩FIR(Verilog)。从编码示例下载编码示例文件。

相关文章:

vivado FIR Filters

Vivado合成直接从RTL中推导出乘加级联来组成FIR滤波器。这种滤波器有几种可能的实现方式;一个例子是收缩滤波器在7系列DSP48E1 Slice用户指南(UG479)中进行了描述,并在8抽头偶数中显示对称收缩FIR(Verilog)…...

c# Contains方法-检查集合中是否包含指定的元素

Contains 是 .NET 集合框架中许多集合类(如 List、Array、HashSet 等)提供的一种方法,用于检查集合中是否包含指定的元素。对于 List<int> 类型,Contains 方法会遍历列表中的所有元素,并判断传入的方法参数是否存…...

【开源】在线办公系统 JAVA+Vue.js+SpringBoot+MySQL

目录 1 功能模块1.1 员工管理模块1.2 邮件管理模块1.3 人事档案模块1.4 公告管理模块 2 系统展示3 核心代码3.1 查询用户3.2 导入用户3.3 新增公告 4 免责声明 本文项目编号: T 001 。 \color{red}{本文项目编号:T001。} 本文项目编号:T001。…...

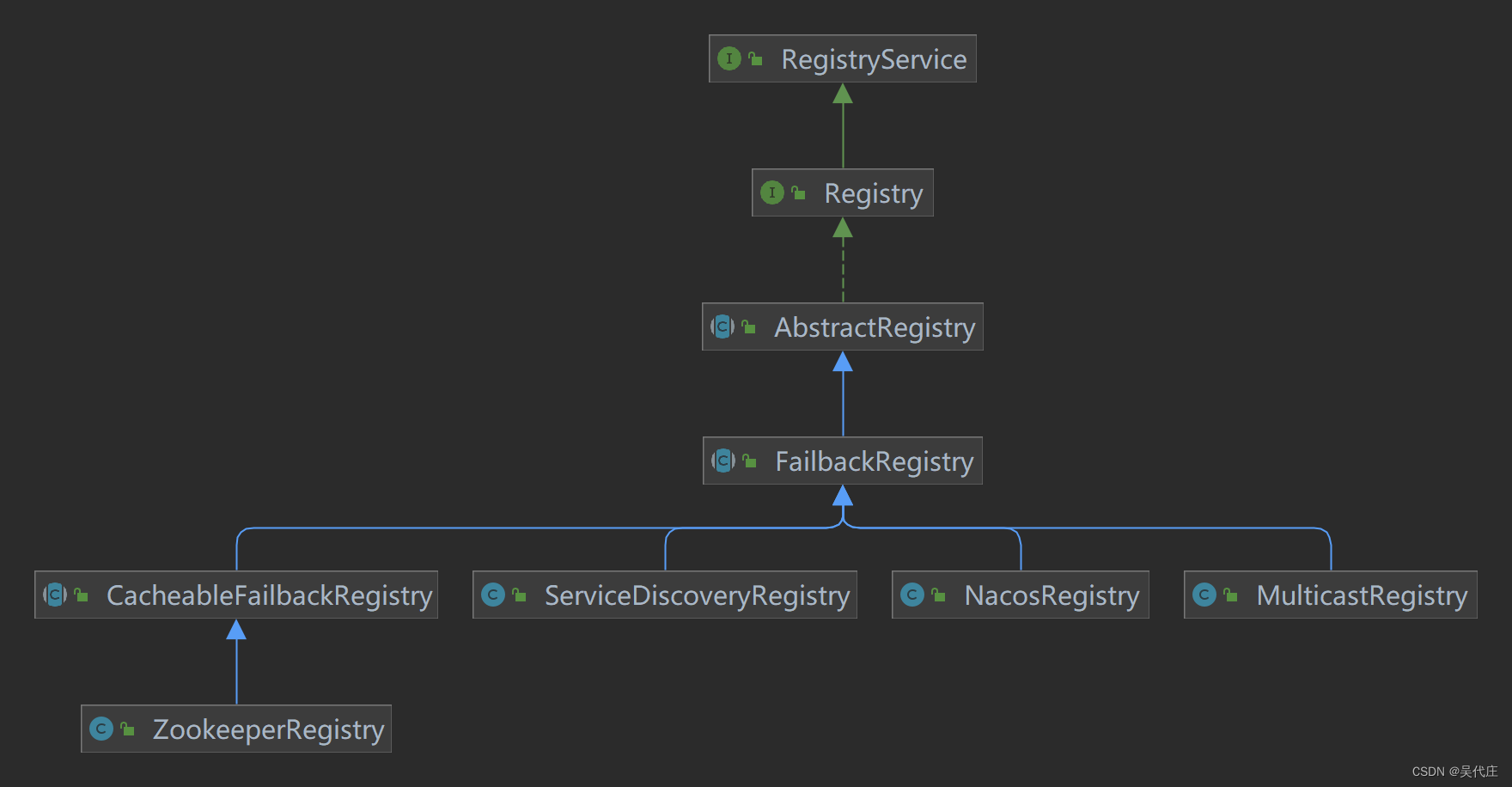

dubbo源码中设计模式——注册中心中工厂模式的应用

工厂模式的介绍 工厂模式提供了一种创建对象的方式,而无需指定要创建的具体类。 工厂模式属于创建型模式,它在创建对象时提供了一种封装机制,将实际创建对象的代码与使用代码分离。 应用场景:定义一个创建对象的接口࿰…...

T-Dongle-S3开发笔记——移植LVGL

添加lvgl组件 idf.py add-dependency lvgl/lvgl>8.* 新建终端执行命令后出现了新的文件: 清除再编译后才会出现lvgl库 优化为本地组件 以上方式修改了组件文件内容重新编译后文件又会变回去。 所以我们要把lvgl变成本地组件 1、要把 idf_component.yml 文…...

SOPHON算能科技新版SDK环境配置以及C++ demo使用过程

目录 1 SDK大包下载 2 获取SDK中的库文件和头文件 2.1 注意事项 2.2 交叉编译环境搭建 2.2.1 首先安装工具链 2.2.2 解压sophon-img包里的libsophon_soc__aarch64.tar.gz,将lib和include的所有内容拷贝到soc-sdk文件夹 2.2.3 解压sophon-mw包里的sophon-mw-s…...

Linux-SSH被攻击-解决方案

文章目录 一、检查攻击来源二、防范措施三、Fail2banfirewallcmd-ipset安装Fail2ban:安装firewalld:配置Fail2ban:配置firewalld以使用fail2ban:测试配置: SSH端口暴露在公网上很可能被黑客扫描,并尝试登入…...

)

第1章 计算机系统概述(2)

1.4操作系统结构 随着操作系统功能的不断增多和代码规模的不断变大,合理的操作系统结构,对于降低操作系统复杂度,提升操作系统安全与可靠性来说变得尤为重要。 分层法: 优点: 1.便于系统调试和验证,简化系统的设计和实现 2.易于扩充和维护 缺点: 1.合理定义各层较难(依赖关系比…...

【Java中23种设计模式-单例模式--饿汉式】

加油,新时代打工人! 简单粗暴,直接上代码。 23种设计模式定义介绍 Java中23种设计模式-单例模式 Java中23种设计模式-单例模式2–懒汉式线程不安全 Java中23种设计模式-单例模式2–懒汉式2线程安全 package mode;/*** author wenhao* dat…...

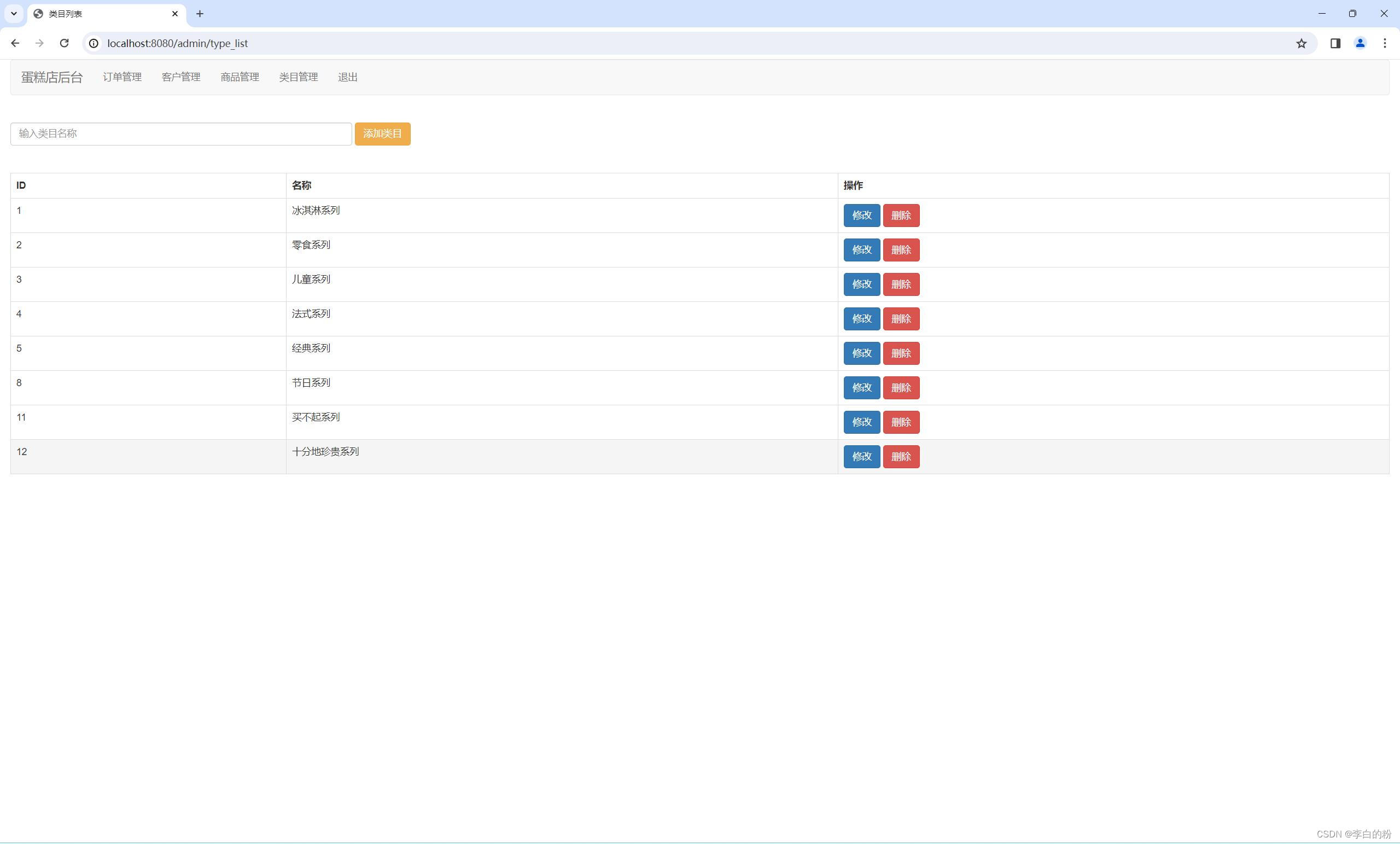

基于JavaWeb实现的在线蛋糕商城

一、系统架构 前端:jsp | bootstrap | js | css 后端:servlet | mybatis 环境:jdk1.7 | mysql | maven | tomcat 二、代码及数据库 三、功能介绍 01. web页-首页 02. web页-商品分类 03. web页-热销 04. web页-新品 05. w…...

【Pytorch】各种维度变换函数总结

维度变换千万不要混着用,尤其是交换维度的transpose和更改观察视角的view或者reshape!混用了以后虽然不会报错,但是数据是乱的, 建议用einops中的rearrange,符合人的直观,不容易出错。 一个例子: >>…...

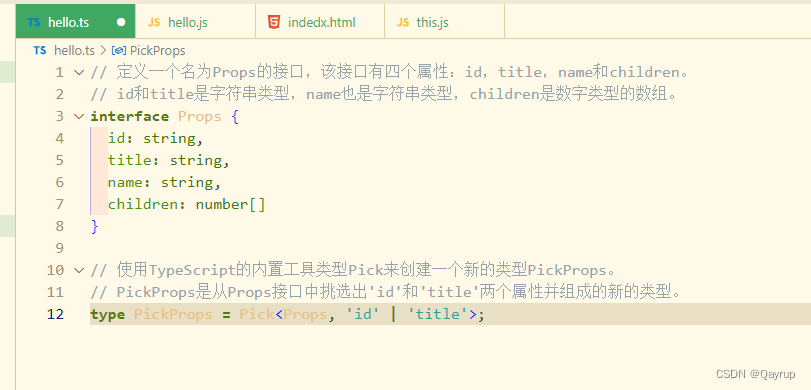

typescript 泛型详解

typescript 泛型 泛型是可以在保证类型安全前提下,让函数等与多种类型一起工作,从而实现复用,常用于: 函数、接口、class中。 需求:创建一个id 函数,传入什么数据就返回该数据本身(也就是说,参数和返回值类型相同)。 …...

【Ubuntu内核】解决Ubuntu 20.04更新内核后无法联网的问题

最近在使用Ubuntu 20.04时,在更新内核后无法进行WiFi联网。我的电脑上装载的是AX211型号的无线网卡,之前安装了相应的驱动,并且一直正常使用。但不小心更新到了Linux 5.15.0-94-generic后,突然发现无法连接网络了。 于是首先怀疑…...

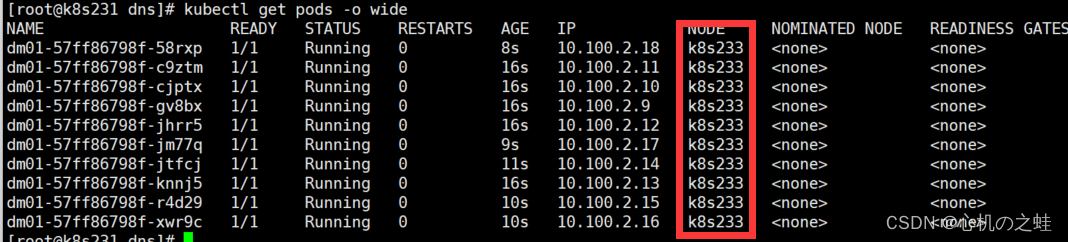

20-k8s中pod的调度-nodeSelector节点选择器

一、概念 我们先创建一个普通的deploy资源,设置为10个副本 [rootk8s231 dns]# cat deploy.yaml apiVersion: apps/v1 kind: Deployment metadata: name: dm01 spec: replicas: 10 selector: matchLabels: k8s: k8s template: metadata: …...

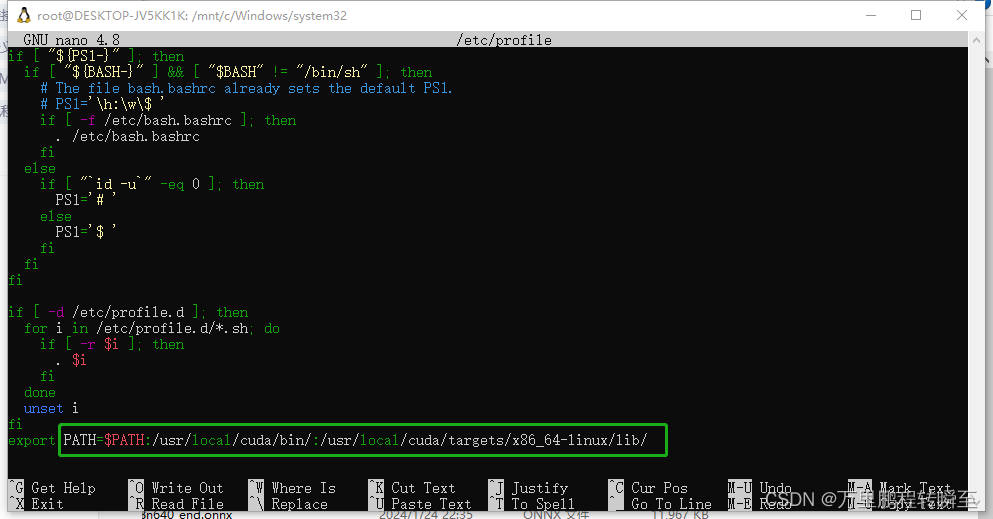

win10下wsl2使用记录(系统迁移到D盘、配置国内源、安装conda环境、配置pip源、安装pytorch-gpu环境、安装paddle-gpu环境)

wsl2 安装好后环境测试效果如下,支持命令nvidia-smi,不支持命令nvcc,usr/local目录下没有cuda文件夹。 系统迁移到非C盘 wsl安装的系统默认在c盘,为节省c盘空间进行迁移。 1、输出wsl -l 查看要迁移的系统名称 2、执行导出命…...

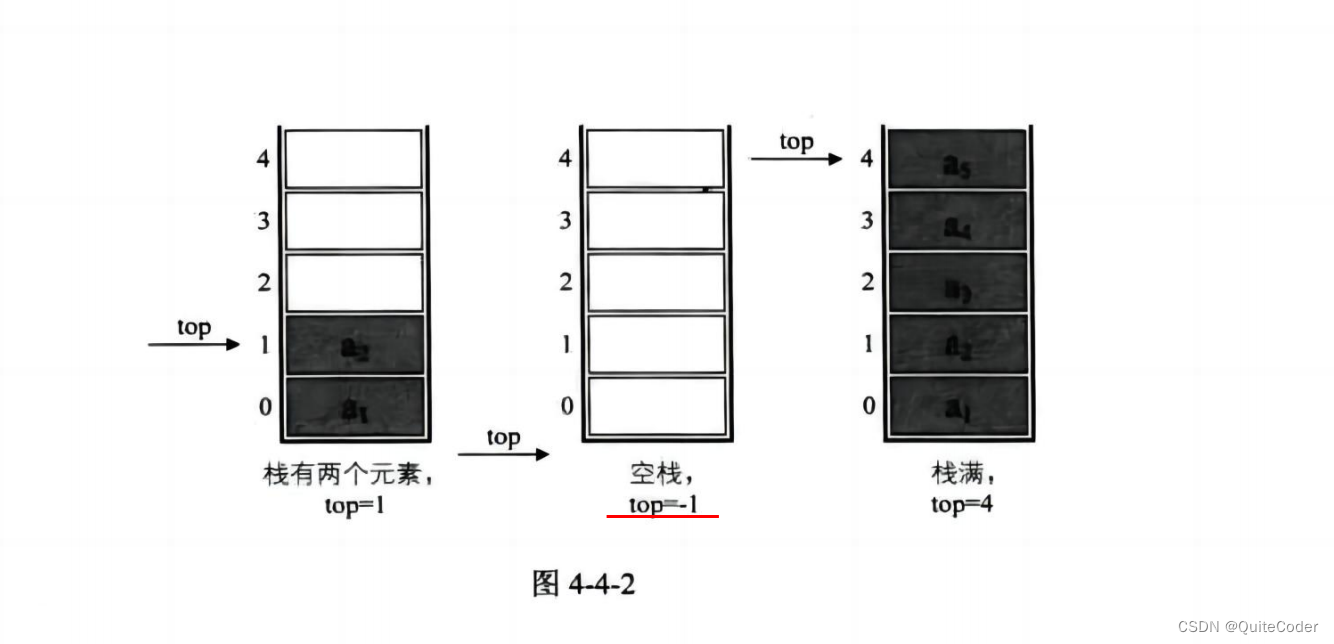

数据结构与算法:栈

朋友们大家好啊,在链表的讲解过后,我们本节内容来介绍一个特殊的线性表:栈,在讲解后也会以例题来加深对本节内容的理解 栈 栈的介绍栈进出栈的变化形式 栈的顺序存储结构的有关操作栈的结构定义与初始化压栈操作出栈操作获取栈顶元…...

Newtonsoft.Json设置忽略某些字段

using Newtonsoft.Json; using Newtonsoft.Json.Serialization; using System; using System.Collections.Generic; using System.Linq; using System.Text; using System.Threading.Tasks;namespace TestProject1 {/// <summary>/// 输出json时,设置忽略哪些…...

【c++每天一题】跳跃游戏

题目 给你一个非负整数数组 nums ,你最初位于数组的 第一个下标 。数组中的每个元素代表你在该位置可以跳跃的最大长度。 判断你是否能够到达最后一个下标,如果可以,返回 true ;否则,返回 false 。 示例 1࿱…...

【C# 中抓取包含多个屏幕内容的整个桌面】

要在 C# 中抓取包含多个屏幕内容的整个桌面,可以使用 .NET Framework 或者其他第三方库来实现。一种常见的方法是使用 System.Windows.Forms 和 System.Drawing 命名空间中的类来实现屏幕截图。以下是一个示例代码,演示如何抓取包含多个屏幕内容的整个桌…...

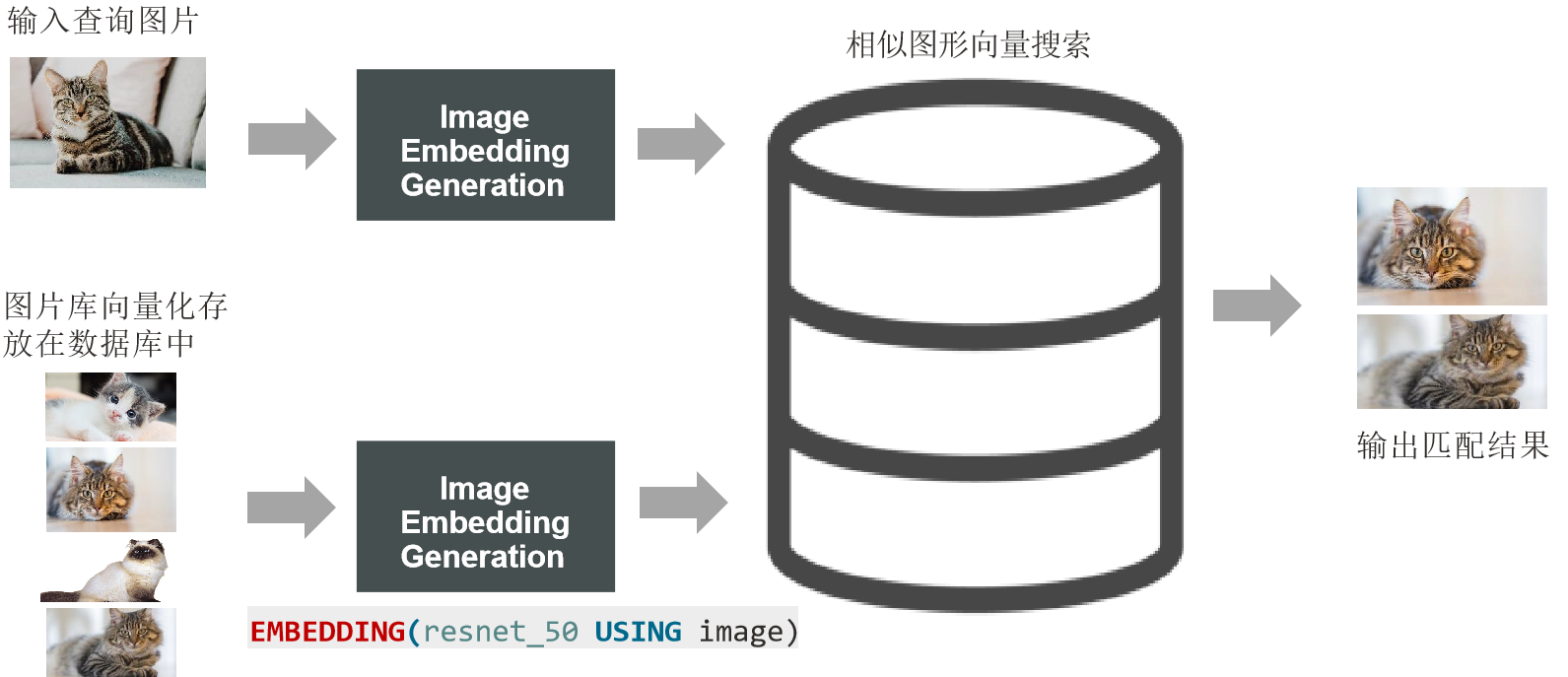

数据库管理-第152期 Oracle Vector DB AI-04(20240220)

数据库管理152期 2024-02-20 数据库管理-第152期 Oracle Vector DB & AI-04(20240220)1 常用的向量检索方法聚类图搜索哈希量化 2 Oracle Vector DB中的索引索引(默认) 索引(高级)3 EMBEDDINGSSQL EMBE…...

数据结构——带懒标记的线段树

一、什么是线段树?线段树是一种二叉树数据结构,用于高效地处理区间查询和区间更新操作。核心思想:将数组分成若干个区间(线段),每个节点代表一个区间,通过合并子节点的信息来得到父节点的信息。…...

你的仿真传感器数据准吗?Gazebo中激光雷达与深度相机的噪声模型配置与Rviz可视化调参实战

高保真机器人仿真:Gazebo传感器噪声模型与Rviz可视化调参全指南 在机器人算法开发中,仿真环境的真实性直接决定了算法测试的有效性。许多SLAM和导航算法在仿真环境中表现优异,一旦部署到真实机器人上却出现各种问题,这往往源于仿真…...

C++lambda表达式深入解析

Clambda表达式深入解析lambda表达式是C11引入的匿名函数特性,它提供了一种简洁的方式来定义内联函数对象,特别适合用于STL算法和回调函数。lambda表达式的基本语法包括捕获列表、参数列表、返回类型和函数体。#include #include #include #includevoid b…...

Go语言DDD实战:领域驱动设计

Go语言DDD实战:领域驱动设计 1. DDD分层 type UserService struct {repo UserRepository }func (s *UserService) CreateUser(cmd *CreateUserCommand) error {// 领域逻辑 }2. 总结 DDD通过统一语言和限界上下文实现复杂业务系统的有效建模。...

ARM NEON中的VMLAL/VMLSL指令详解与优化实践

1. ARM SIMD指令集概述在嵌入式系统和移动计算领域,ARM架构凭借其出色的能效比占据了主导地位。随着多媒体处理、机器学习等计算密集型任务的普及,单指令多数据流(SIMD)技术成为提升处理器性能的关键手段。ARM的Advanced SIMD扩展(通常称为NEON技术)提供…...

超详细全解:从诞生背景到工作原理)

【Linux驱动开发】第11天:设备树(Device Tree)超详细全解:从诞生背景到工作原理

一、设备树的诞生背景:传统驱动的致命痛点 在设备树出现之前(Linux 3.0之前),Linux内核采用硬编码的方式描述所有硬件信息。这意味着: 每一个开发板的寄存器地址、中断号、GPIO号,都直接写死在驱动代码里换…...

6.解决 99% 刷机故障|GPT 分区修复 + SEP 兼容检测 + 全分区备份,工程师实战手册

摘要 本文面向具备基础Linux命令行操作能力的维修工程师与高级发烧友,系统阐述主流品牌手机刷机与维修的底层逻辑与标准化操作流程。内容覆盖高通、联发科、苹果A系列三大芯片平台的刷机协议差异,提供完整的刷机工具链搭建脚本、分区备份恢复脚本、以及底层驱动级故障诊断代…...

TensorFlow数据增强Pipeline:从固定顺序到条件驱动的工业级重构

1. 为什么“写死顺序”的增强 pipeline 在真实项目中总是卡壳?你有没有遇到过这种场景:模型在验证集上指标涨得不错,一到线上推理就崩得稀里哗啦?或者训练时 loss 曲线看着很稳,但模型对稍微偏移一点的拍摄角度、光照变…...

内部举报、纪检谈话等敏感场景,企业沟通工具需要具备哪些安全能力

一家组织处理内部举报时,沟通链路往往比事件本身更敏感。 举报人担心身份暴露,被举报部门担心信息扩散,纪检或内控人员需要核实事实,法务和审计又可能随后介入。一次谈话纪要、一张截图、一份附件、一个会议链接,都可能…...

UPGEN Lighting HDRP:HDRP光照优化与自动化配置方案

1. 这不是又一个“开箱即用”的灯光插件,而是HDRP光照工程的系统性减负方案我第一次在项目里把UPGEN Lighting HDRP拖进Assets文件夹时,并没指望它能解决什么大问题——毕竟Unity官方HDRP模板里自带的Light Explorer、Light Probe Group、Reflection Pro…...