Zynq学习笔记--AXI4-Stream到视频输出IP是如何工作的?

目录

1. 简介

2. 原理详解

2.1 示例工程

2.2 AXI4-Stream to Video Out

3. Master/Slave Timing Mode

3.1 Slave Timing Mode

3.2 Master Timing Mode

4. 总结

1. 简介

本文主要介绍了 AXI4-Stream 到视频输出 的内容。其中,示例工程展示了一个具体的设计,包括时钟、复位信号、视频数据以及一些参数设置。该示例工程使用 AXI4-Lite 接口配置视频输出的参数,例如图像的高度、宽度和背景图案。此外,文本还详细解释了 AXI4-Stream 到视频输出 IP 的组成部分,包括数据部分、时序信号部分和同步部分。同步器的工作原理涵盖了初始对齐阶段和时序模式,以实现数据和时序信号的同步。

2. 原理详解

2.1 示例工程

`timescale 1ns / 1psimport axi_vip_pkg::*;

import design_1_axi_vip_0_0_pkg::*;module tb_AXI4S_to_Vid_Out();bit aclk = 0, aresetn = 0;

xil_axi_resp_t resp;

bit vid_hblank, vid_vblank, vid_hsync, vid_vsync ;

bit [23:0] vid_data;

integer counter_width = 0, counter_height = 0;

integer final_width = 0, final_height = 0;parameter integer tpg_base_address = 12'h000;parameter integer TPG_CONTROL_REG = tpg_base_address;parameter integer TPG_ACTIVE_H_REG = tpg_base_address + 8'h10;parameter integer TPG_ACTIVE_W_REG = tpg_base_address + 8'h18;parameter integer TPG_BG_PATTERN_REG = tpg_base_address + 8'h20;

integer height=480, width=640;always #12.5ns aclk = ~aclk; // 40MHzdesign_1_wrapper UUT(.aclk_40MHz (aclk),.aresetn_0 (aresetn),.vid_data (vid_data),.vid_hblank (vid_hblank),.vid_hsync (vid_hsync),.vid_vblank (vid_vblank),.vid_vsync (vid_vsync));initial begin#50ns aresetn = 1;

enddesign_1_axi_vip_0_0_mst_t master_agent;initial begin master_agent = new("master vip agent",UUT.design_1_i.axi_vip_0.inst.IF);master_agent.start_master();wait (aresetn == 1'b1);#200nsmaster_agent.AXI4LITE_WRITE_BURST(TPG_ACTIVE_H_REG, 0, height, resp);master_agent.AXI4LITE_WRITE_BURST(TPG_ACTIVE_W_REG, 0, width, resp);master_agent.AXI4LITE_WRITE_BURST(TPG_BG_PATTERN_REG, 0, 9, resp);#200nsmaster_agent.AXI4LITE_WRITE_BURST(TPG_CONTROL_REG, 0, 8'h81, resp);

end

endmodule

注意:

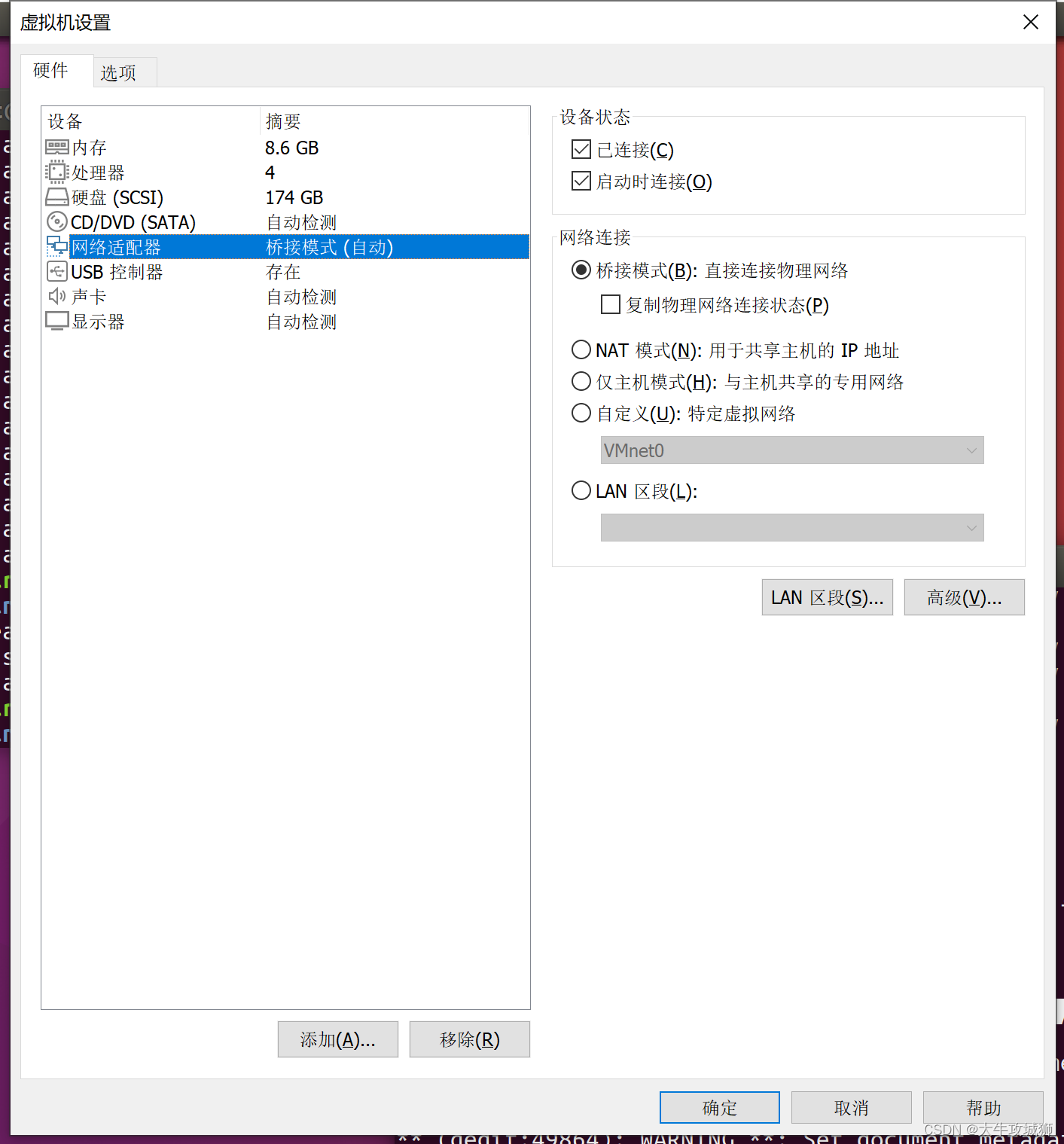

- 如果 Clock Mode 选用独立时钟,则启用fifo的跨时钟域功能。

- fifo深度如何设定?答:在根据fifo_flag调试;

- fid仅用于隔行扫描,很少用到;

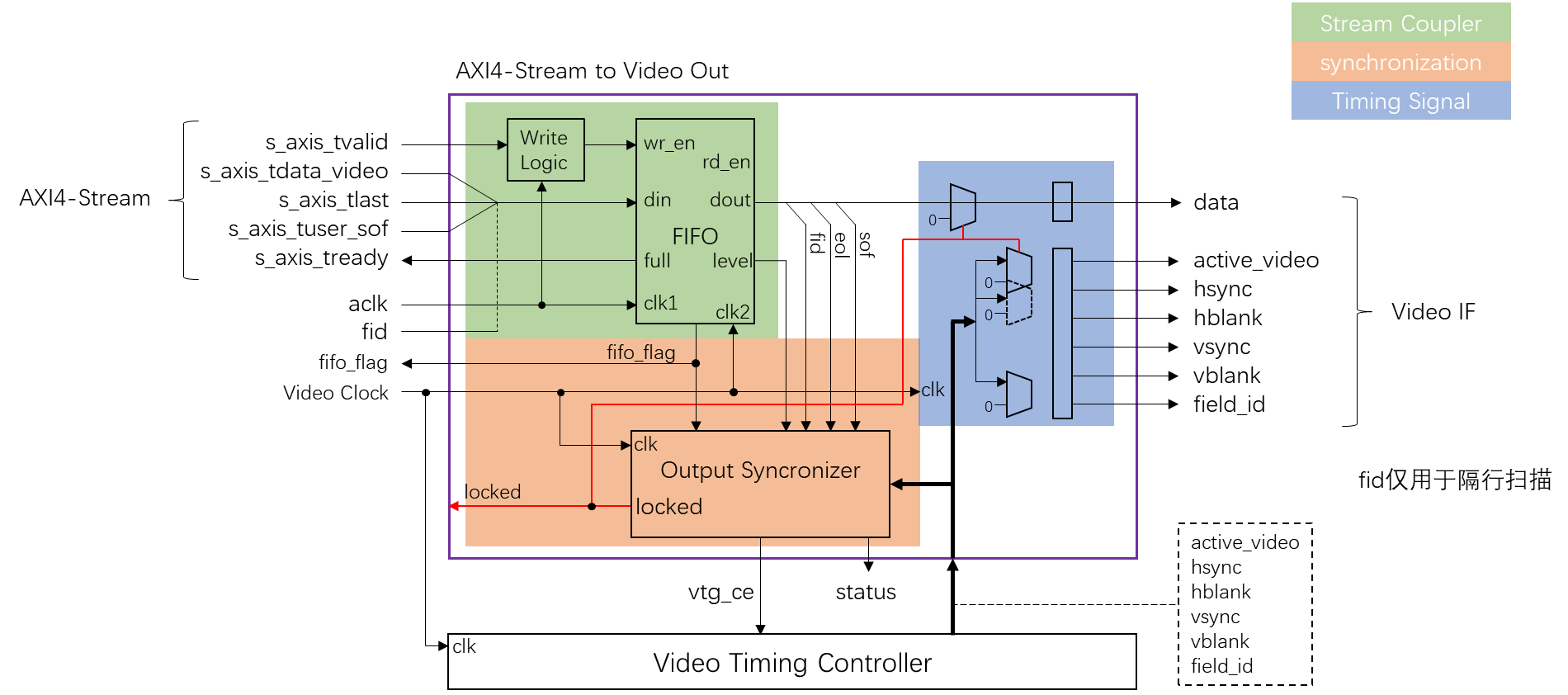

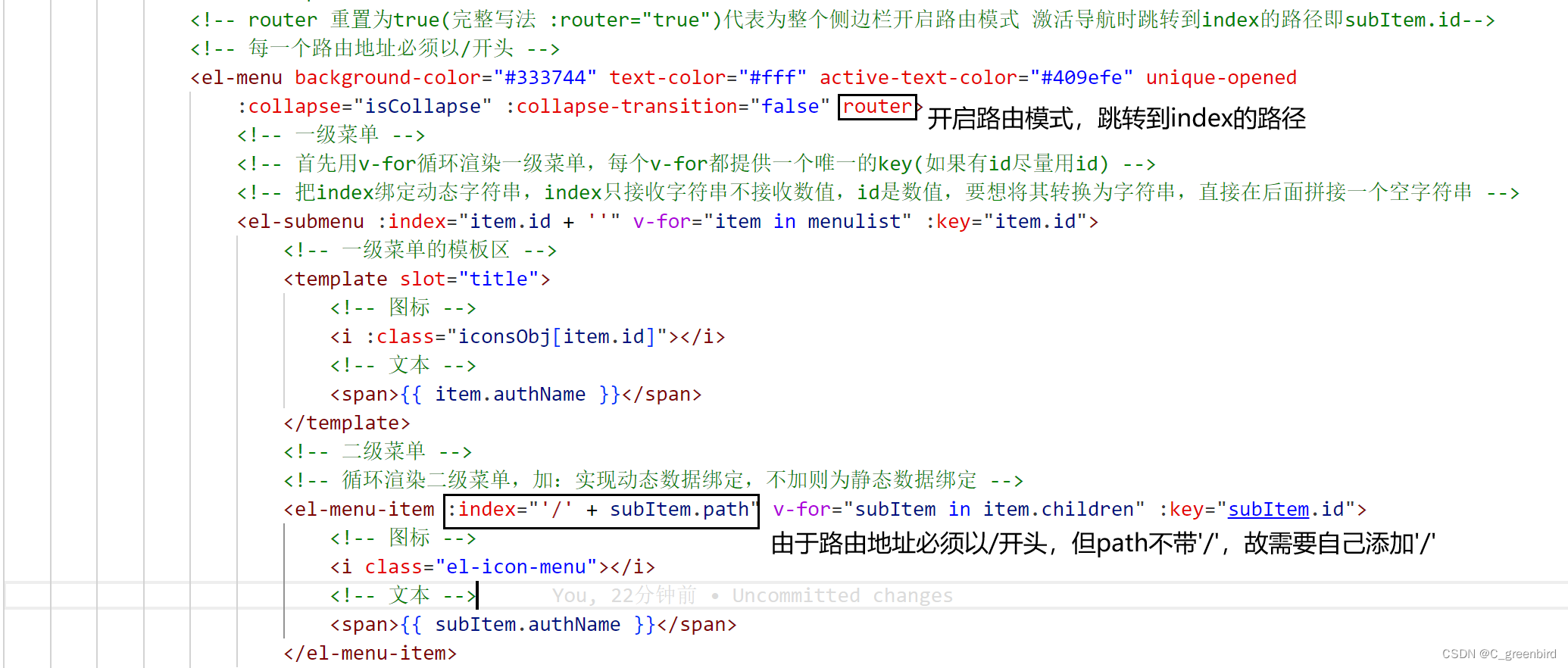

2.2 AXI4-Stream to Video Out

其中:

fifo_flag: overflow, underflow

status:

status[1] – Course Align, Wait for VTG SOF

status[3] – Fine Align, VTG EOL Leading

status[8] – Fine Align Locked

…

AXI4-Stream到视频输出IP的组成部分:

- 数据部分(红色):数据首先通过FIFO,然后进行格式化,以遵循Xilinx视频IP的AXI4-Stream编码(UG934中定义)。

- 时序信号部分(绿色):时序信号直接从VTC(视频时序控制器)传递给AXI4-Stream到视频输出IP,无需修改。

- 同步部分(橙色):输出同步器从AXI4-Stream接收帧边界信息信号(帧开始和行结束),以及来自VTC的时序信号,以实现数据和时序信号的同步。

同步器的工作原理:

- 初始对齐阶段:AXI4-Stream到视频输出首先进入粗对齐阶段,然后进入精细对齐阶段,最终锁定。具体的对齐细节可以在PG044中找到。

- 时序模式:根据Master或Slave模式,同步器控制VTC或内部FIFO,以实现同步。详细的时序模式说明在PG044的第3章中有。

- 输出同步器块从AXI4-Stream接收帧边界信息信号(tuser, or sof and eol)以及从VTC IP接收的时序信号作为输入,以同步数据和时序信号。根据时序模式(Master 或 Slave),它将控制VTC(使用vtg_ce)或内部FIFO以实现同步。

3. Master/Slave Timing Mode

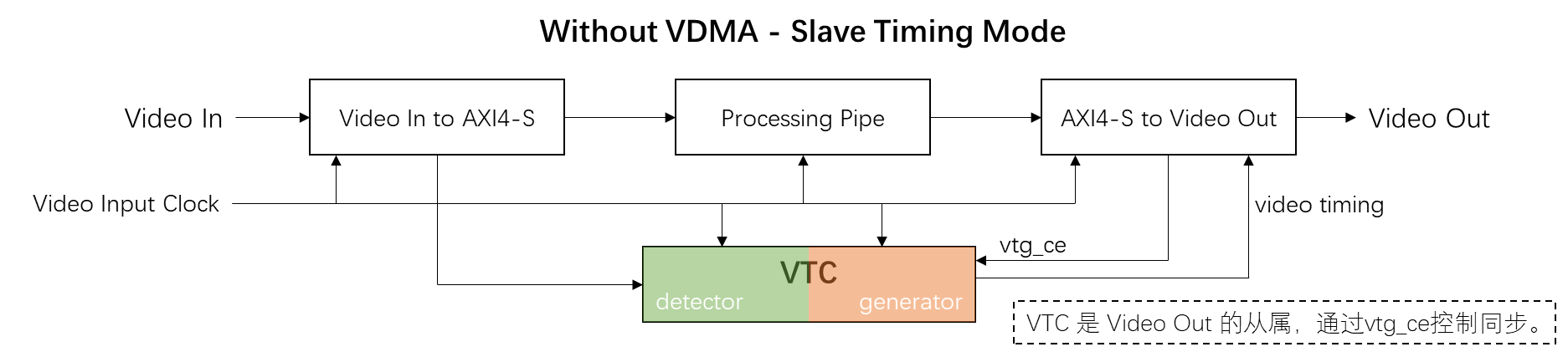

3.1 Slave Timing Mode

Slave Timing Mode,是指 VTC 是 Video Out 的从属,通过vtg_ce控制同步。

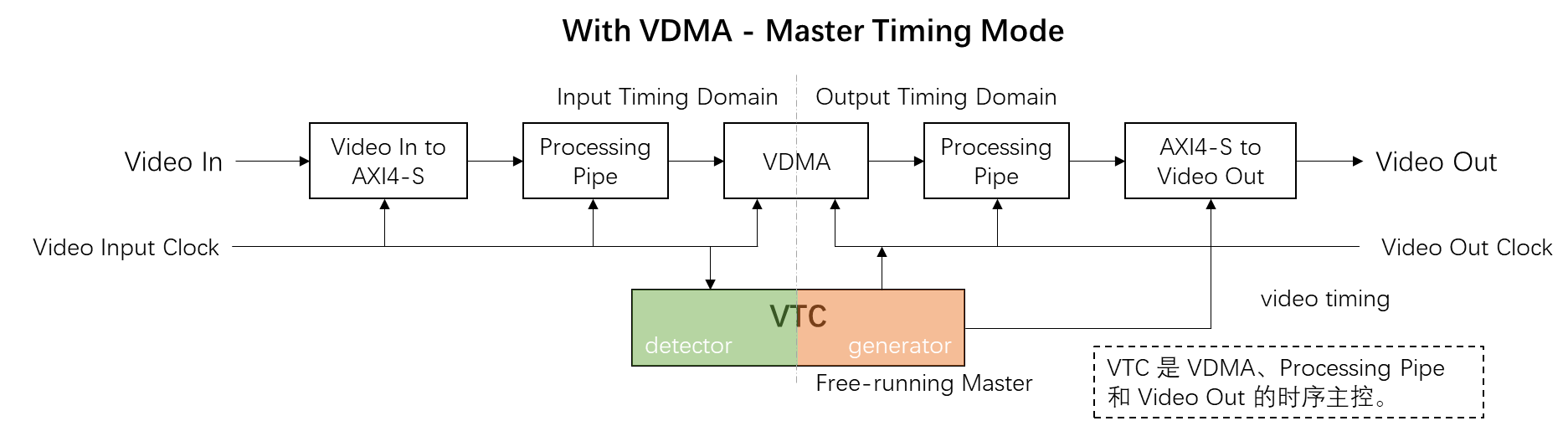

3.2 Master Timing Mode

Master Timing Mode,是指 VTC 是 VDMA、Processing Pipe 和 Video Out 的时序主控。

4. 总结

本文介绍了 AXI4-Stream 到视频输出的工作原理和示例工程。通过该工程,详细展示了如何使用 AXI4-Lite 接口配置视频输出参数,包括图像高度、宽度和背景图案等。AXI4-Stream 到视频输出 IP 包含数据部分、时序信号部分和同步部分,确保数据与时序信号的同步。同步器通过初始对齐和时序模式来实现这一目标,支持独立时钟模式下的跨时钟域功能。最后,解释了 Master 和 Slave 时序模式,分别由 VTC 控制同步信号和作为时序主控。总的来说,本文为实现视频输出提供了全面的技术指导和详细的操作示例。

相关文章:

Zynq学习笔记--AXI4-Stream到视频输出IP是如何工作的?

目录 1. 简介 2. 原理详解 2.1 示例工程 2.2 AXI4-Stream to Video Out 3. Master/Slave Timing Mode 3.1 Slave Timing Mode 3.2 Master Timing Mode 4. 总结 1. 简介 本文主要介绍了 AXI4-Stream 到视频输出 的内容。其中,示例工程展示了一个具体的设计&…...

2016-2023 年美国农业部作物序列边界

简介 2016-2023 年美国农业部作物序列边界 作物序列边界(CSB)是与美国农业部经济研究局合作开发的,它提供了美国毗连地区的田间边界、作物种植面积和作物轮作的估计数据。该数据集利用卫星图像和其他公共数据,并且是开放源码的,使用户能够对美国种植的商品进行面积和统计…...

数字人源码部署怎么做?如何高效搭建好用的数字人系统?

作为人工智能时代的风口项目,AI数字人自出现之日起便引发了大量的关注。不少创业者都有了搭建数字人系统的想法,但却苦于没有强大的专业背景和雄厚资金支撑,只能在局外徘徊,而这恰恰为数字人源码公司推出的数字人源码部署服务的火…...

解决虚拟机Ubuntu IP总是掉的问题

问题 嵌入式开发过程中,需要使用NFS/TFTP等等,虚拟机Ubuntu就需要和板卡进行网络连接,但是我发现虚拟机Ubuntu的IP地址经常动不动就掉线,本文记录解决该问题的一些思路。 其实这个问题很简单,我早该想到,…...

[13] CUDA_Opencv联合编译过程

CUDA_Opencv联合编译过程 详细编译过程可见我之前的文章:Win10下OpencvCUDA联合编译详细教程(版本455、460、470,亲测可用!!!)本文给出Windows\linux下的opencvcuda的编译总结,摘自 <基于GP…...

uni-app canvas创建画布

canvasTmp: function(arr2, store_name, successFn, errFun) {let that this;const ctx uni.createCanvasContext(myCanvas);ctx.clearRect(0, 0, 0, 0);/*** 只能获取合法域名下的图片信息,本地调试无法获取* */uni.getImageInfo({ src: arr2[0],success: function(res) {…...

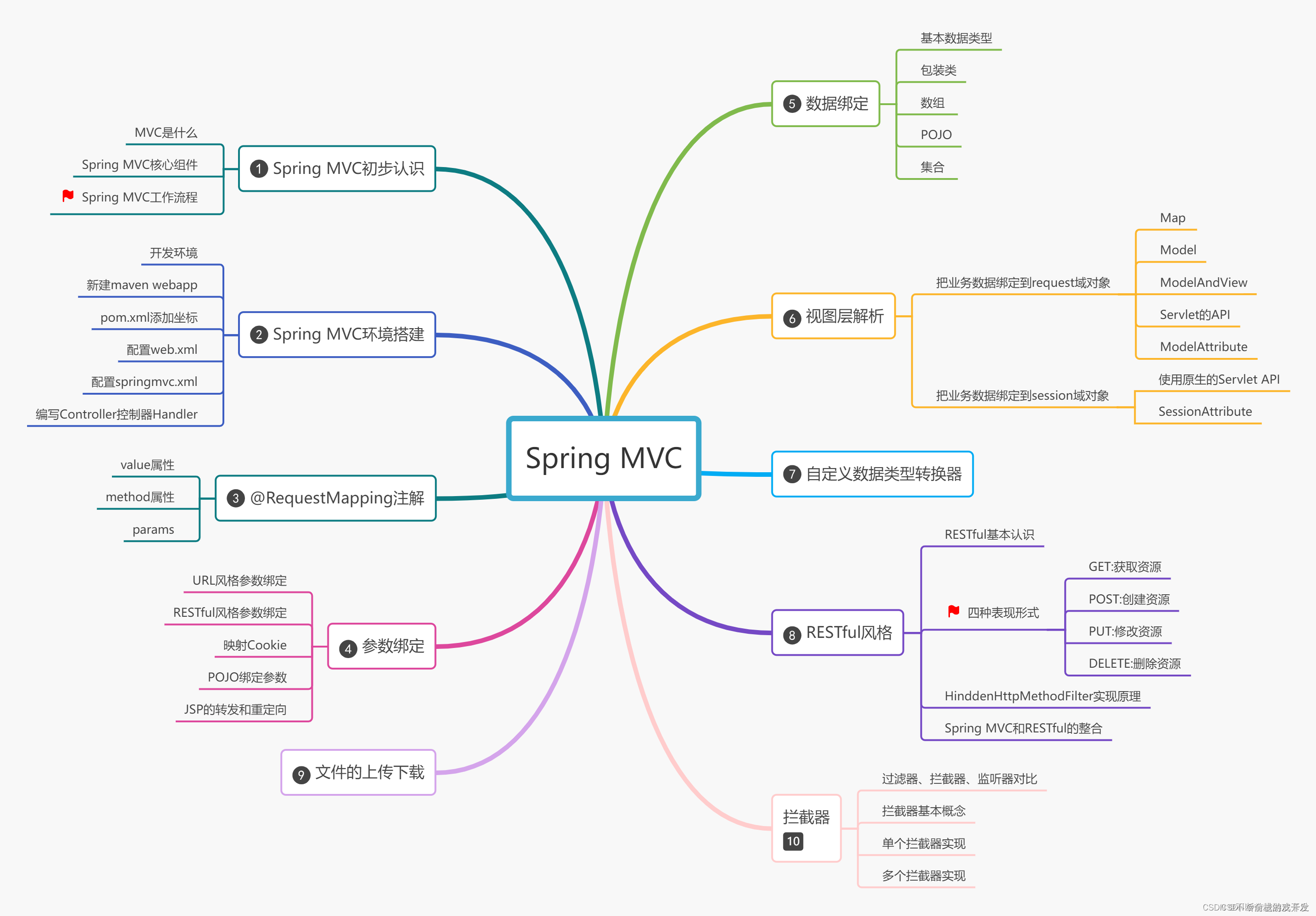

Spring MVC详解(上)

一、Spring MVC初步认识 1.1介绍 Spring MVC是Spring Framework提供的Web组件,全称是Spring Web MVC,是目前主流的实现MVC设计模式的框架,提供前端路由映射、视图解析等功能 Java Web开发者必须要掌握的技术框架 1.2MVC是什么 MVC是一种软件架构思想…...

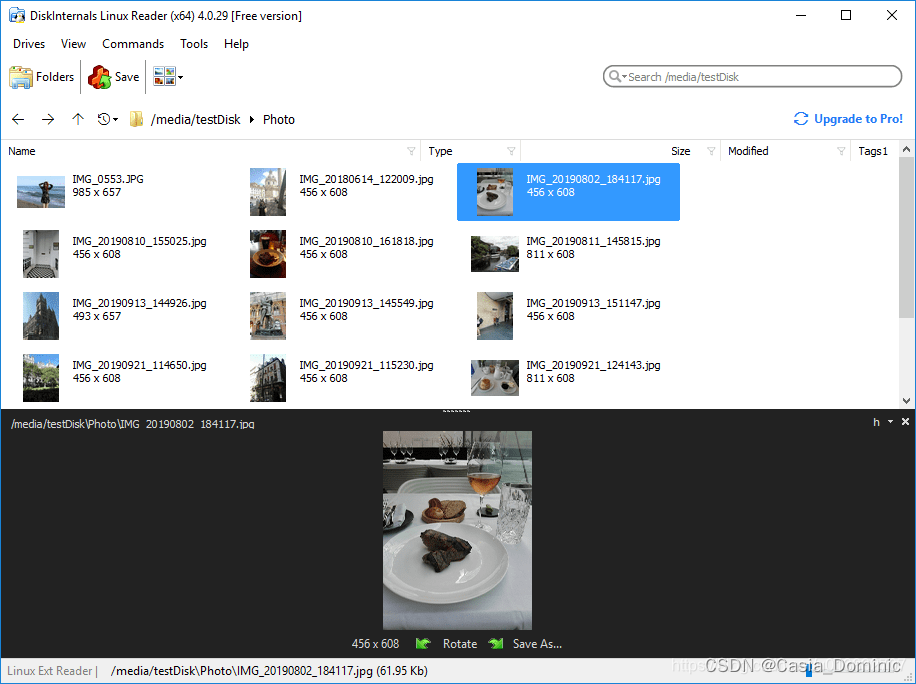

【Linux硬盘读取】Windows下读取Linux系统的文件解决方案:Linux Reader4.5 By DiskInternals

前言 相信做机器视觉相关的很多人都会安装 Windows 和 Linux 双系统。在 Linux 下,我们可以很方便的访问Windows的磁盘,反过来却不行。但是这又是必须的。通过亲身体验,向大家推荐这么一个工具,可以让 Windows 方便的访问 Ext 2/3…...

操作系统—页表(实验)

文章目录 页表1.实验目标2.实验过程记录(1).增加打印页表函数(2).独立内核页表(3).简化软件模拟地址翻译 3.实验问题及相应解答问题1问题2问题3问题4 实验小结 页表 1.实验目标 了解xv6内核当中页表的实现原理,修改页表,使内核更方便地进行用户虚拟地址…...

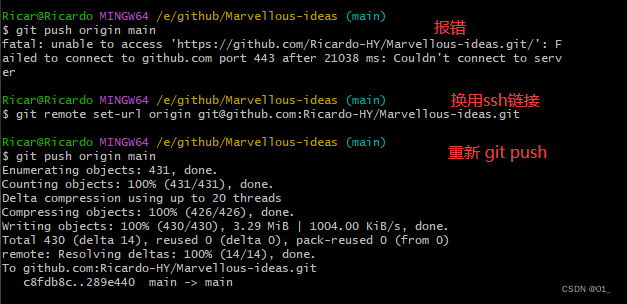

github 本地仓库上传及报错处理

一.本地文件上传 这里为上传部分,关于gitbash安装配置,读者可自行搜索,由于已经安装完成,未进行截图保存,这里便不做赘述。 1.登录git账号并创建一个仓库 点击仓库打开后会看到这个仓库的网址链接(这个链…...

)

【ZZULIOJ】1104: 求因子和(函数专题)

题目描述 输入正整数n(2<n<1000),计算并输出n的所有正因子(包括1,不包括自身)之和。要求程序定义一个FacSum ()函数和一个main()函数,FacSum ()函数计算并返回n的所有正因子之和,其余功能在main()函…...

轨迹优化 | 图解欧氏距离场与梯度场算法(附ROS C++/Python实现)

目录 0 专栏介绍1 什么是距离场?2 欧氏距离场计算原理3 双线性插值与欧式梯度场4 仿真实现4.1 ROS C实现4.2 Python实现 0 专栏介绍 🔥课程设计、毕业设计、创新竞赛、学术研究必备!本专栏涉及更高阶的运动规划算法实战:曲线生成…...

【二维差分】2132. 用邮票贴满网格图

本文涉及知识点 二维差分 LeetCode2132. 用邮票贴满网格图 给你一个 m x n 的二进制矩阵 grid ,每个格子要么为 0 (空)要么为 1 (被占据)。 给你邮票的尺寸为 stampHeight x stampWidth 。我们想将邮票贴进二进制矩…...

【前端项目笔记】2 主页布局

主页布局 element-ui提供的组件名称就是它的类名 ☆☆ CSS选择器: (1)基本选择器 类型选择器 p/span/div…… 类选择器 (.classname) ID选择器 (#idname) 通配选择器 ( * ) (2)属性选择器 选择具有特定属性或属性值的…...

t265 jetpack 6 px4 ros2

Ubuntu22.04 realsenseSDK2和ROS2Wrapper安装方法,包含T265版本踩坑问题_ros2 realsense-CSDN博客 210 git clone https://github.com/IntelRealSense/librealsense.git 212 git branch 215 git tag 218 git checkout v2.51.1 219 git branch 265 git clone https://…...

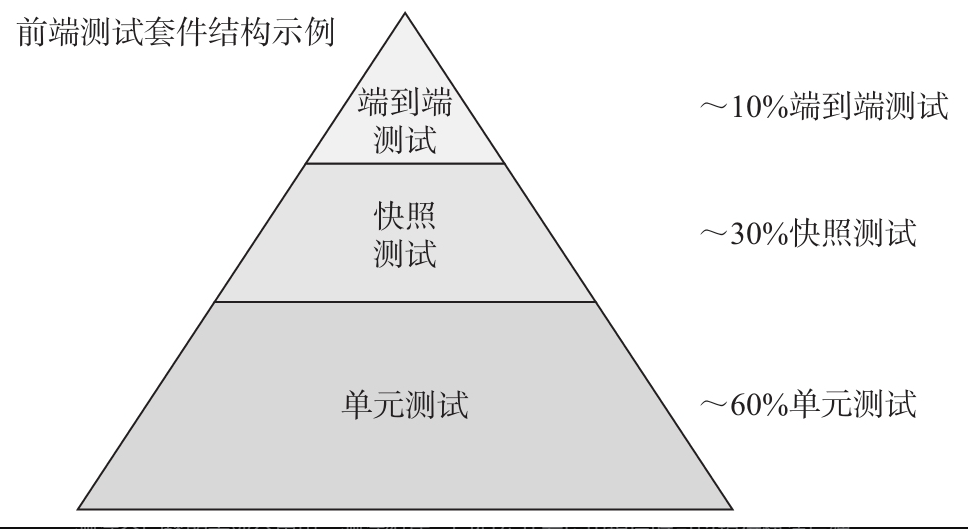

vue 应用测试(一) --- 介绍

vue 应用测试(一) ---介绍 前端测试简介组件测试Jest 测试框架简介其他测试框架 第一个测试避免误报如何组织测试代码 组件挂载Vue2 组件挂载的方式Vue3 的挂载方式vue-test-utils挂载选项 如何调试测试用例参考小结 前端测试简介 软件测试:…...

Perl 语言入门学习

一、介绍 Perl 是一种高级的、动态的、解释型的通用编程语言,由Larry Wall于1987年开发。它是一种非常灵活和强大的语言,广泛用于文本处理、系统管理、网络编程、图形编程等领域。 Perl 语言的设计理念是“用一种简单的语法,去解决复杂的编…...

HarmongOS打包[保姆级]

创建应用 首先进入 华为开发者联盟-HarmonyOS开发者官网 然后进行登录。 登录成功后,鼠标悬停在在登录右上角那个位置后再点击管理中心,进入下面这个界面。 再点击:应用服务–>应用发布–>新建–>完善信息 构建和生成私钥和证书请求…...

SpringBoot怎么实现自定义接口全局异常捕获?详细教程

自定义异常 package com.single.bean;import org.springframework.core.NestedRuntimeException;public class FDWException extends NestedRuntimeException {private static final long serialVersionUID = 6046035491210083235L;public FDWException(String msg) {super(msg…...

Ms08067安全实验室成功实施多家业务系统渗透测试项目

点击星标,即时接收最新推文 近日,Ms08067安全实验室针对多家公司重要系统实施渗透测试项目。公司网络信息系统的业务应用和存储的重要信息资产均较多,存在网络系统结构的复杂性和庞杂等特点,使得公司网络信息系统面临一定风险。项…...

混合人工智能架构可以将神经形态系统转变为可靠的发现机器。

基于ON-OFF神经元的高阶伊辛机架构。图片来源:Nature Communications (2026)。DOI:10.1038/s41467-026-71937-4来源:https://techxplore.com/news/2026-05-hybrid-ai-architecture-neuromorphic-reliable.html主导世界的AI机器可以分为三大类…...

汽车后市场品牌营销路径:以奇正沐古和康明斯为例

在汽车后市场,很多品牌真正的难题并非没有技术、没有产品、没有资源,而是这些优势到了终端之后,无法变成司机、经销商和维修点愿意相信、愿意推荐、愿意购买的理由。康明斯发动机润滑油就是个典型例子,康明斯作为全球柴油发动机技…...

重塑游戏社交:Nucleus Co-Op如何用一台电脑创造四人同屏体验

重塑游戏社交:Nucleus Co-Op如何用一台电脑创造四人同屏体验 【免费下载链接】nucleuscoop Starts multiple instances of a game for split-screen multiplayer gaming! 项目地址: https://gitcode.com/gh_mirrors/nu/nucleuscoop 问题:本地多人…...

技术奇点之后,人类程序员的历史角色

当人工智能越过技术奇点,代码生成、测试用例设计乃至系统运维都将发生质变。本文从软件测试从业者的视角出发,系统探讨人类程序员在奇点之后可能扮演的六种核心角色:系统守护者、需求翻译官、质量伦理法官、人机交互设计师、持续学习组织者与…...

南京彩钢瓦屋面防水供应商

在南京,彩钢瓦屋面广泛应用于各类建筑,然而其防水问题一直是困扰众多业主的难题。选择一家靠谱的彩钢瓦屋面防水供应商至关重要。今天就为大家详细介绍雨中行修缮工程有限公司,同时也对比其他一些大厂,看看雨中行修缮为何能在市场…...

数据分析实习面试准备全攻略:专业知识+项目深挖+行为面试,职卓科技的面试辅导体系

摘要数据分析实习面试通常包含三大模块:专业知识考察(SQL、Python、统计学基础)、项目深挖(业务理解、技术选择、问题解决)、行为面试(团队协作、学习能力、职业规划)。很多学员在面试中表现不佳…...

3分钟掌握Krita AI抠图:点一下就能完成的智能选区革命

3分钟掌握Krita AI抠图:点一下就能完成的智能选区革命 【免费下载链接】krita-vision-tools Krita plugin which adds selection tools to mask objects with a single click, or by drawing a bounding box. 项目地址: https://gitcode.com/gh_mirrors/kr/krita-…...

从零到精通:AI大模型学习路线图,手把手带你入门!

本文提供了一条从基础到高级的AI大模型学习路线图,涵盖数学与编程基础、机器学习入门、深度学习实践、大模型探索以及进阶应用等方面。文章推荐了丰富的学习资源,包括经典书籍、在线课程、实践项目和开源平台,旨在帮助新手小白系统学习AI大模…...

如何突破窗口限制:3分钟掌握WindowResizer强制调整技巧

如何突破窗口限制:3分钟掌握WindowResizer强制调整技巧 【免费下载链接】WindowResizer 一个可以强制调整应用程序窗口大小的工具 项目地址: https://gitcode.com/gh_mirrors/wi/WindowResizer 还在为那些无法拖拽大小的应用程序窗口而烦恼吗?Win…...

为Odoo ERP构建安全的AI数据访问层:基于权限治理的语义查询实践

1. 项目概述:为Odoo ERP构建一个受治理的AI数据访问层如果你正在使用Odoo管理企业业务,同时又希望让AI助手(比如Claude、Cursor)能够安全地查询销售数据、分析库存状况,而不是让它们直接面对你的生产数据库写SQL&#…...