系统架构设计师——计算机体系结构

分值占比3-4分

计算机硬件组成

计算机硬件组成主要包括主机、存储器和输入/输出设备。

-

主机:主机是计算机的核心部分,包括运算器、控制器、主存等组件。运算器负责执行算术和逻辑运算;控制器负责协调和控制计算机的各个部件;主存(内存)用于存储正在运行的程序和数据。

-

存储器:存储器分为主存和辅存两种类型。主存(内存)是计算机中临时存储数据的地方,通常比辅存速度快,但容量较小。辅存(如硬盘、固态硬盘等)用于长期存储数据,容量较大,但速度较慢。

-

输入/输出设备:输入设备(如键盘、鼠标、触摸屏等)用于向计算机输入数据;输出设备(如显示器、打印机、音响等)用于显示或播放计算机处理后的结果。

主机的组成

主机的组成主要包括CPU(中央处理器)、主存储器和控制器等部分。以下是这些部件的具体功能和作用:

-

CPU(中央处理器):

- 算术逻辑单元(ALU):负责处理所有的算术运算(如加减乘除)和逻辑运算(如AND、OR、NOT)。

- 控制单元(CU):解释程序指令,控制数据流向,并管理其它电脑硬件资源。

- 寄存器:暂时存储数据和指令,包括:

- 指令寄存器(IR):存储当前正在执行的指令。

- 地址寄存器(AR):存储将要访问的内存地址。

- 数据寄存器(DR):暂时存储数据。

- 状态条件寄存器(PSW):存储处理器的状态信息。

- 程序计数器(PC):存储下一条要执行的指令的地址。

- 存储器缓冲寄存器(MBR):在数据传输时作为主存和CPU之间的缓冲。

-

主存储器:

- 存储体:主存储器的主要部分,用于存放程序和数据。

- 存储器地址寄存器(MAR):存储体中用于存放要访问的内存单元的地址。

- 存储器数据寄存器(MDR):存储体中用于暂存要写入内存或从内存读取的数据。

-

控制器:

- 指令译码器(ID):对指令寄存器中的指令进行译码,确定需要执行的操作。

- 提加寄存器(IR):与指令寄存器配合使用,提供指令的临时存储。

- 控制逻辑单元:生成控制信号,用于控制数据在各个寄存器和处理器之间的传输。

- 时序部件:产生时钟信号,同步各部件的操作。

以上是计算机主机内部的主要组成部分及其功能。每个部件都扮演着特定的角色,共同完成计算机的各项操作和数据处理任务。

指令系统

指令系统是计算机硬件的语言系统,它包含了机器所具有的全部指令的集合。反映了计算机所拥有的基本功能。

指令系统作为计算机的基本命令集,体现了计算机处理任务的基本方法。在设计计算机架构时,确定哪些操作由硬件直接实现,哪些由软件间接实现是关键。这直接影响到计算机的性能和灵活性。指令系统的设计和选择可以从以下几个角度进行探讨:

- 操作码字段(OP):

- 操作码字段是指令的一部分,用来指定操作的性质及功能。

- 每条指令都通过操作码来区分其具体执行的操作类型,如加、减、乘、除等。

- 操作码的设计要简洁明了,易于理解和使用,以减少错误并提高编程效率。

- 地址码字段(Addr):

- 地址码字段用于指出操作数的存放位置或直接给出操作数。

- 通过地址码,CPU可以定位到所需的数据或指令存储的具体位置。

- 地址码的设计需要考虑到存储器的容量与机器的字长,确保指令能够有效访问所需数据。

- 指令的功能与操作:

- 指令系统包括数据处理、数据传送、程序控制等多种类型的指令。

- 每种指令都有其特定的功能,如数据处理指令用于执行算术运算和逻辑运算。

- 程序控制指令则用于改变程序执行的顺序,如条件转移和转子程序指令。

- 指令的格式与类型:

- 指令格式通常包含操作码字段和地址码字段,根据操作数数量的不同,可以分为三地址、二地址、单地址等格式。

- 选择合适的指令格式可以优化存储空间的使用和提高指令执行的效率。

- 指令还可以根据功能分为算术运算型、逻辑运算型、数据传送型等。

- 指令系统的发展历程:

- 从早期的简单指令系统到现在的复杂指令系统,计算机的功能和性能有了显著提升。

- 现代计算机通过引入更多面向高级语言的复杂指令,缩小了机器指令与高级语言之间的语义差距。

- 随着技术的发展,指令系统也在不断地调整和优化,以适应新的技术挑战和应用需求。

总的来说,指令系统不仅仅是计算机硬件的核心部分,它也是计算机功能实现的基础。操作码字段和地址码字段的设计决定了指令的种类和功能,从而影响计算机的处理能力和适用范围。随着计算机技术的发展,指令系统也在不断演进,以提供更强大、更灵活的计算能力。

复杂指令系统

复杂指令系统(CISC)是一种计算机指令集架构,其基本思想是通过进一步增强原有指令的功能,用更为复杂的新指令取代原先由软件子程序完成的功能,实现软件功能的硬化,导致机器的指令系统越来越庞大、复杂。

复杂指令系统(CISC)在设计上具有独特的特点和优势,但也存在一些缺点。下面的内容将详细分析其特点:

- 指令数量众多:

- CISC指令系统拥有大量的指令,通常有100~50条。这些指令涵盖各种功能,包括数据传输、算术运算、逻辑运算等。

- 由于指令数量众多,编程者可以方便地找到特定操作对应的指令,这在某种程度上简化了程序设计。

- 指令使用频率相差悬殊:

- 最常使用的是一些比较简单的指令,仅占指令总数的20%,但在程序中出现的频率却占80%。而部分复杂指令却很少使用。

- 这种使用频率的悬殊导致许多复杂指令在实际程序中并不实用,增加了硬件的复杂度却没有带来相应的性能提升。

- 功能强大的指令集:

- CISC指令集包含丰富的指令,每条指令可以完成多个操作,这使得处理特殊任务时效率较高。

- 例如,一条单一的指令可能包含存储、加载、计算等多种操作,减少了需要执行的指令数量,提高了程序运行效率。

- 灵活的存储器操作:

- CISC架构允许指令直接操作存储器,存储器操作指令多且灵活,这使得数据传递和处理更加直接。

- 这种灵活性对编写复杂程序和科学计算非常有利,汇编语言程序设计相对简单。

- 微程序控制器:

- 在CISC架构中,通常会采用微程序控制器来实现复杂指令。微程序控制器包含微代码,用于解释和执行指令。

- 通过微代码实现指令可以增加处理器的灵活性,但同时也增加了处理器设计的复杂度和执行时间。

- 向后兼容性好:

- CISC架构由于历史悠久,具有良好的向后兼容性。新的处理器能够运行旧的软件和应用程序。

- 这种向后兼容性使得CISC架构在企业级应用和桌面计算领域得到了广泛应用,如x86体系结构。

精简指令系统

精简指令系统(RISC)是一种计算机指令集架构,其基本思想是通过减少指令总数和简化指令功能降低硬件设计的复杂度,使指令能单周期执行,并通过优化编译提高指令的执行速度,采用硬布线控制逻辑优化编译程序。

精简指令系统(RISC)在设计上具有显著的特点和优势,这些特点使它与复杂指令系统(CISC)有明显区别。下面的内容将详细解析其特点:

- 指令数量少:

- RISC指令系统优先选取使用频率最高的一些简单指令和一些常用指令,避免使用复杂指令。

- 由于指令数量较少,硬件设计相对简单,从而降低了设计成本和功耗。

- 寻址方式少:

- RISC指令的寻址方式较少,这简化了指令解码过程,提高了指令执行效率。

- 这种简化同时也减少了编译器的负担,使得编译过程更加高效。

- 指令长度固定:

- RISC指令长度固定,指令格式种类少,这有利于流水线的高效执行。

- 固定长度的指令简化了硬件设计,使得每条指令都能在一个机器周期内完成。

- 硬布线逻辑控制为主:

- 为了提高操作的执行速度,RISC通常采用硬布线逻辑(组合逻辑)来构建控制器。

- 与微程序控制相比,硬布线逻辑控制能够更快地完成指令执行,从而提高整体性能。

- 单周期指令执行:

- RISC采用流水线技术,大部分指令都能在一个机器周期内完成。

- 这种设计使得处理器可以高效地处理指令,提升了运算速度和系统吞吐率。

- 优化的编译器:

- RISC的精简指令集使编译工作简单化。因为指令长度固定、格式少、寻址方式少,编译时不必在具有相似功能的许多指令中进行选择。

- 优化编译器可以生成高效率执行的机器代码,进一步提升程序运行效率。

- CPU中的通用寄存器数量多:

- RISC架构的CPU中通常包含多个通用寄存器,一般在32个以上,多的甚至上千个。

- 大量的寄存器减少了对存储器的依赖,从而加快了数据处理速度和指令执行效率。

指令流水

要计算流水线周期和100条指令全部执行完毕所需的时间,我们首先需要了解流水线周期的计算方法。流水线周期是指执行时间最长的一个阶段,它决定了流水线的频率。对于给定的例子,我们可以按照以下步骤进行计算:

-

确定流水线周期:

- 取指时间为2ns,分析时间为2ns,执行时间为1ns。

- 流水线周期取这些阶段中最长的时间为周期长度,因此流水线周期为2ns(取指和分析的时间)。

-

计算100条指令全部执行完毕所需的时间:

- 公式为: ( t 1 + t 2 + … + t k ) + ( n − 1 ) ∗ Δ t (t_1 + t_2 + \ldots + t_k) + (n - 1) * \Delta t (t1+t2+…+tk)+(n−1)∗Δt,其中 t 1 , t 2 , … , t k t_1, t_2, \ldots, t_k t1,t2,…,tk是各个阶段的时间, n n n是指令数, Δ t \Delta t Δt是流水线周期。

- 将给定的值代入公式: ( 2 + 2 + 1 ) + ( 100 − 1 ) ∗ 2 = 5 + 99 ∗ 2 = 5 + 198 = 203 (2 + 2 + 1) + (100 - 1) * 2 = 5 + 99 * 2 = 5 + 198 = 203 (2+2+1)+(100−1)∗2=5+99∗2=5+198=203ns。

因此,流水线周期是2ns,100条指令全部执行完毕需要的总时间是203ns。

流水线的吞吐率(TP)和最大吞吐率(TP_max)是衡量流水线性能的重要指标。吞吐率是指单位时间内流水线处理的结果数,对于指令执行而言,就是单位时间内完成的指令数。下面是关于流水线吞吐率和最大吞吐率的详细解析:

流水线吞吐率(TP)

吞吐率定义为单位时间内流水线处理的结果数。在流水线中,这通常是指在稳定状态下,流水线每个周期完成的任务数。公式为:

T P = n T TP = \frac{n}{T} TP=Tn

其中,$ n $ 是任务数(或指令数),$ T $ 是完成所有任务所需的总时间。

最大吞吐率(TP_max)

最大吞吐率是在理想情况下,流水线每个周期都能输出一个结果时的吞吐率。在这种情况下,吞吐率等于流水线的周期时间的倒数,即:

T P m a x = 1 Δ t TP_{max} = \frac{1}{\Delta t} TPmax=Δt1

其中,$ \Delta t $ 是流水线的周期时间。

流水线执行时间

流水线执行时间是指从第一条指令开始执行到最后一条指令完成的总时间。对于一个分为$ k 个阶段的流水线,执行 个阶段的流水线,执行 个阶段的流水线,执行 n 条指令的总时间 条指令的总时间 条指令的总时间 T $可以表示为:

T = ( k + ( n − 1 ) ) × Δ t T = (k + (n - 1)) \times \Delta t T=(k+(n−1))×Δt

流水线加速比(S)

流水线加速比是指使用流水线执行时间与不使用流水线执行时间的比值。公式为:

S = T n o n − p i p e l i n e d T p i p e l i n e d S = \frac{T_{non-pipelined}}{T_{pipelined}} S=TpipelinedTnon−pipelined

其中,$ T_{non-pipelined} $ 是不使用流水线时执行$ n 条指令所需的时间, 条指令所需的时间, 条指令所需的时间, T_{pipelined} $ 是使用流水线执行$ n $条指令所需的时间。

存储系统

存储器的层次

存储器的层次结构是一个由多级存储设备组成的系统,其顶层是寄存器,然后依次是Cache、主存和磁盘。

寄存器位于CPU内部,它的访问速度最快,能在单个CPU周期内完成,容量有限,仅能存储少量数据,但价格相对较高。Cache使用静态随机存取存储器,位于CPU和主存之间,用于暂存频繁访问的指令和数据。它比寄存器慢,但速度仍远快于主存,其价格也较高。

主存通常使用动态随机存取存储器,容量较大,价格适中,但速度慢于Cache。磁盘包括固态硬盘和机械硬盘,它们有极大的容量和最低的成本,但访问速度最慢。

从用户角度出发,存储器的三个主要指标是容量、速度和每位价格。越靠近CPU的存储器容量越小、速度越快、价格越高;反之,远离CPU的存储器则容量大、速度慢、价格便宜。这种层次结构不仅解决了存储器的速度、容量和成本之间的矛盾,还通过局部性原理优化了存储访问效率。

主存储器

主存用来存放计算机运行期间所需要的程序和数据,CPU可直接随机地 进行读/写。

在计算机系统中,CPU与主存之间的数据交换是通过总线进行的,具体涉及到数据总线、地址总线和控制总线。以下是这一过程的详细描述:

数据总线(DR)

- 功能:数据总线用于在CPU和主存之间传输数据。

- 特点:它的宽度决定了每次可以传输数据的位数,直接影响数据传输的速度和效率。

地址总线(AR)

- 功能:地址总线用于从CPU向主存传递地址信息。

- 特点:地址总线的宽度决定了CPU可以直接寻址的内存范围。例如,32位宽的地址总线可以寻址到4GB的内存空间。

控制总线

- 功能:控制总线携带的是控制信号,如读/写控制信号。

- 特点:控制总线确保数据传输的正确性和有序性,它传达了CPU对外围设备的操作命令,如读取或写入数据的指令。

读/写操作过程

-

读操作:

- CPU通过地址总线发送所要读取数据的内存地址。

- 控制总线发出读信号。

- 数据通过数据总线从主存传输到CPU。

-

写操作:

- CPU通过地址总线发送将要写入数据的内存地址。

- 控制总线发出写信号。

- 数据通过数据总线从CPU传输到主存。

典型真题

题目

内存按字节编址,地址从A4000H到CBFFFH,共有()个字节。若用存储容量为32KX8bit的存储芯片构成该内存,至少需要()片。

A、80K

B、96K

C、160K

D、192K

A、2

B、5

C、8

D、10

解题思路

-

计算地址范围:

- 首先,将十六进制地址转换为十进制地址。

- 计算两个地址之间的差值,得到总的字节数。

-

计算所需芯片数量:

- 每个存储芯片的容量为32K字节,即32768字节(因为1K = 1024字节)。

- 使用总字节数除以单片芯片的字节数,得到所需的芯片数量。

- 如果结果不是整数,向上取整得到实际需要的芯片数量。

具体步骤

-

地址转换和计算:

- A4000H = $ 10 \times 65536 + 4 \times 4096 + 0 \times 256 = 655360 + 16384 = 671744 $

- CBFFFH = $ 12 \times 65536 + 11 \times 4096 + 15 \times 256 + 15 = 786432 + 45056 + 3840 + 15 = 835343 $

- $ 835343 - 671744 = 163599 $ 字节

-

计算芯片数量:

- 每片芯片容量:32768 字节

- 所需芯片数:$ \lceil \frac{163599}{32768} \rceil = 5 $

结论

- 从地址A4000H到CBFFFH共有163599个字节。

- 若用存储容量为32KX8bit的存储芯片构成该内存,至少需要5片。

- 正确答案是 B、5。

磁盘阵列

磁盘阵列(RAID)是一个由多个磁盘驱动器组成的存储系统,旨在提供更高的性能、更大的存储容量和更好的数据可靠性。下面是关于RAID的详细解析:

RAID的级别

RAID共有8个不同的级别,每个级别都提供了不同的性能和冗余特性。这些级别包括:

- RAID 0 - 无冗余分条:提供数据分条技术,但不提供冗余,因此没有容错能力。

- RAID 1 - 镜像:数据被镜像到两个或多个磁盘上,提供数据冗余,但磁盘利用率较低。

- RAID 2 - 位级条带化加汉明码:使用汉明码进行错误校正,适用于高性能计算环境。

- RAID 3 - 带奇偶校验的并行访问:所有数据磁盘共享一个奇偶校验磁盘,适用于大文件的顺序访问。

- RAID 4 - 带专用奇偶校验的磁盘镜像:与RAID 3类似,但奇偶校验信息存储在专用磁盘上。

- RAID 5 - 带分散奇偶校验的分条:类似于RAID 0,但增加了分散的奇偶校验信息,提高了读取速度和可靠性。

- RAID 6 - 双奇偶校验:提供双重奇偶校验,即使两个磁盘同时失效也能保持数据完整性。

- RAID 7 - 带网络支持的磁盘阵列:使用高速缓存和网络连接,适用于大型数据中心。

RAID的主要技术

- 分块技术:将数据分成小块,分布在多个磁盘上,可以提高数据传输速率和并行处理能力。

- 交叉技术:交叉技术是指将数据以交叉的方式存储在多个磁盘上,可以改善I/O性能,减少磁盘访问时间。

- 重聚技术:在数据从多个磁盘读取后,重聚技术负责将数据重新组合成用户所需的格式,确保数据的完整性和可用性。

RAID的优势

- 提高读写速度:通过并行访问多个磁盘,RAID可以显著提高数据的读写速度。

- 增加存储容量:RAID系统通过组合多个磁盘的存储空间,提供了更大的存储容量。

- 提供冗余保护:除了RAID 0,其他RAID级别都提供了不同程度的数据冗余保护,以防数据丢失。

- 提高可靠性:通过冗余和错误校正技术,RAID系统提高了数据的可靠性和系统的容错能力。

校验码

循环冗余校验码

循环冗余校验(CRC)是一种通过特定的生成多项式来检测或验证数据传输或存储过程中的错误的技术。下面是关于CRC的详细解析:

CRC的基本原理

CRC基于除法算法,使用一个称为生成多项式的特定多项式来生成校验码。生成多项式的最高位为1,且通常比要计算的数据位长。CRC的处理过程如下:

- 准备数据:将要传输或存储的数据表示为一个二进制数。

- 选择生成多项式:选择一个适当的生成多项式,该多项式的位数决定了校验位的长度。

- 编码过程:将数据与生成多项式进行模2除法,得到的余数即为CRC校验码。

- 附加校验码:将校验码附加到数据的末尾,形成完整的CRC编码数据。

CRC的数学表达

假设有一个数据位序列 $ D(x) $ 和一个生成多项式 $ G(x) $,其中 $ G(x) $ 的次数为 $ r $(即校验位的长度)。CRC编码的过程可以表示为:

CRC编码 = D ( x ) ⋅ x r m o d G ( x ) \text{CRC编码} = D(x) \cdot x^r \mod G(x) CRC编码=D(x)⋅xrmodG(x)

这里的 $ \mod G(x) $ 表示模2除法操作。

CRC的特点

- 错误检测能力:CRC能够检测出大部分常见的错误,如单比特错误、双比特错误等。

- 无法纠正错误:CRC仅用于错误检测,不能纠正错误。

- 低误判率:CRC具有极低的误判率,这意味着很少会将错误数据误认为是正确数据。

- 灵活性:通过选择不同的生成多项式,可以在检测能力和系统开销之间做出权衡。

CRC的应用

- 数据通信:在数据传输中,CRC用于确保数据的正确性,特别是在无线通信和网络协议中。

- 磁介质存储:在硬盘驱动器和固态硬盘中,CRC用于检测存储数据的错误。

- 文件系统:许多文件系统使用CRC来检测文件数据的完整性。

结论

循环冗余校验(CRC)是一种强大且广泛应用于数据通信和存储领域的错误检测技术。它利用生成多项式对数据进行编码,产生校验码,从而在数据传输或存储过程中提供错误检测功能。尽管CRC无法纠正错误,但其高可靠性和低误判率使其成为保护数据完整性的重要工具。

考试真题

好的,下面是整理后的题目和解题思路:

题目

采用CRC进行差错校验,生成多项式为 $ G(X) = X^4 + X + 1 $,信息码字为10111,则计算出的CRC校验码是( )。

A. 0000

B. 0100

C. 0010

D. 1100

解题步骤

-

化解多项式:生成多项式 $ G(X) = X^4 + X + 1 $ 对应的二进制数为10011。

-

信息码加0:在信息码字10111后面添加4个0,变为101110000。这些额外的位用于存放计算出的CRC校验码。

-

模二除运算:使用生成多项式10011对101110000进行模二除法运算。模二除法类似于常规的除法,但使用的是异或操作而不是减法,并且不进位。

迭代过程:

得到余数:

最终的余数是最后5位,这5位即为CRC校验码。

总线

总线是计算机硬件系统中的重要组成部分,它负责在各个组件之间传输数据和控制信号。根据不同的标准,总线可以分为多种类型,每种类型的总线都有其特定的设计目的和应用场景。下面是对您提到的各种总线的简要概述:

内部总线与外部总线

- 内部总线:连接CPU内部的各个部件,如寄存器、算术逻辑单元等。

- 外部总线:连接CPU与计算机系统中的其他主要组件,如内存、输入输出设备等。

按功能分类

- 地址总线:传输地址信息,指定数据的来源或目的地。

- 数据总线:传输实际的数据。

- 控制总线:传输控制信号,用于管理数据总线和地址总线的操作。

按数据线的多少分类

- 并行总线:具有多条双向数据线,能够同时传输多位数据,提高了数据传输速率,适用于近距离连接,如计算机内部的连接。

- 串行总线:只有一条或两条单向数据线,数据传输速率相对较低,但适合长距离连接,常用于计算机之间或计算机与其他系统间的通信。

应用示例

- 系统总线:如PCI, PCIe,主要用于计算机内部各部件的连接,属于并行总线。

- 通信总线:如USB, RS-232,主要用于计算机与外部设备的连接,可以是串行也可以是并行。

- 串行总线:如I²C, SPI,主要用于嵌入式系统和外围设备的通信,适合长距离连接。

特点与适用场景

- 并行总线:由于有多条数据线,可以同时传输多个数据位,因此传输速度快,适合内部高速数据传输。

- 串行总线:数据传输速度相对较慢,但由于只需要少量的线缆,成本较低,易于维护,适合远距离通信。

相关文章:

系统架构设计师——计算机体系结构

分值占比3-4分 计算机硬件组成 计算机硬件组成主要包括主机、存储器和输入/输出设备。 主机:主机是计算机的核心部分,包括运算器、控制器、主存等组件。运算器负责执行算术和逻辑运算;控制器负责协调和控制计算机的各个部件;主存…...

3D鸡哥又上开源项目!单图即可生成,在线可玩

大家好,今天和大家分享几篇最新的工作 1、Unique3D Unique3D从单视图图像高效生成高质量3D网格,具有SOTA水平的保真度和强大的通用性。 如下图所示 Unique3D 在 30 秒内从单视图野生图像生成高保真且多样化的纹理网格。 例如属于一张鸡哥的打球写真照 等…...

设计模式实现思路介绍

设计模式是在软件工程中用于解决特定问题的典型解决方案。它们是在多年的软件开发实践中总结出来的,并且因其重用性、通用性和高效性而被广泛接受。设计模式通常被分为三种主要类型:创建型、结构型和行为型。 创建型设计模式 创建型设计模式专注于如何创…...

Node.js学习教程

Node.js学习教程可以从基础到高级,逐步深入理解和掌握这一强大的JavaScript运行环境。以下是一个详细的Node.js学习教程概述,帮助初学者和进阶者更好地学习Node.js。 一、Node.js基础入门 1. 了解Node.js 定义:Node.js是一个基于Chrome V8…...

项目页面优化,我们该怎么做呢?

避免页面卡顿 怎么衡量页面卡顿的情况呢? 失帧和帧率FPS 60Hz就是帧率fps,即一秒钟60帧,换句话说,一秒钟的动画是由60幅静态图片连在一起形成的。 卡了,失帧了,或者掉帧了,一秒钟没有60个画面&…...

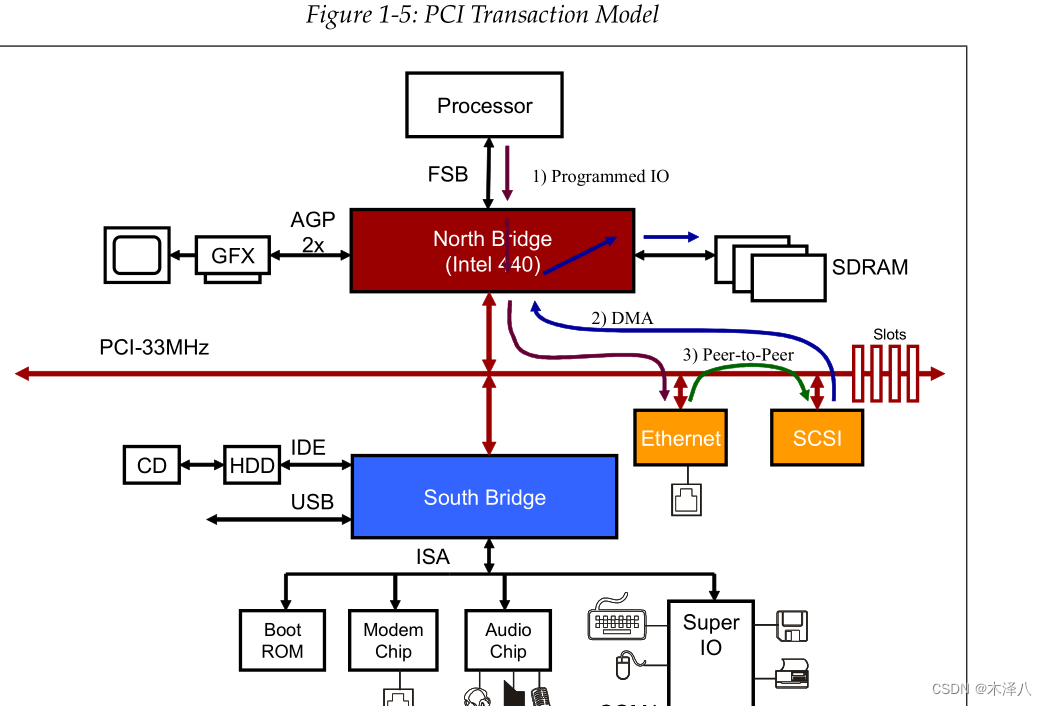

【PCIe】P2P DMA

PCIe P2P (peer-to-peer communication)是PCIe的一种特性,它使两个PCIe设备之间可以直接传输数据,而不需要使用主机RAM作为临时存储。如下图3的走向 比如EP1要发送和数据给EP2,操作流程如下: 1. 打开EP1的dma控制器;--client侧 …...

Linux shell编程学习笔记62: top命令 linux下的任务管理器

0 前言 top命令是Unix 和 Linux下常用的性能分析工具,提供了一个动态的、交互式的实时视图,显示系统的整体性能信息,以及正在运行的进程的相关信息,包括各个进程的资源占用状况,类似于Windows的任务管理器。 1 top命令…...

如何在Java中实现高性能的网络通信

如何在Java中实现高性能的网络通信 大家好,我是免费搭建查券返利机器人省钱赚佣金就用微赚淘客系统3.0的小编,也是冬天不穿秋裤,天冷也要风度的程序猿! 1. 引言 在当今互联网时代,高性能的网络通信是构建大规模分布…...

政务单位网站SSL证书选择策略

在数字化快速发展的今天,政务单位网站作为政府与公众沟通的重要桥梁,其安全性和可信度显得尤为重要。SSL证书作为保障网站安全的重要手段,其选择对于政务单位网站来说至关重要。本文将探讨政务单位网站在选择SSL证书时应该考虑的因素…...

零基础入门 Ai 数据挖掘竞赛-速通 Baseline-1

#AI夏令营 #Datawhale #夏令营 本项目为Datawhale 2024 年 AI 夏令营赛事,零基础入门 AI 数据挖掘竞赛-速通学习手册配套的代码项目。 项目链接:https://aistudio.baidu.com/bd-cpu-02/user/2961857/8113198/home#codelab 任务目标 根据给的test&…...

(Python))

第二十六章 生成器(generator)(Python)

文章目录 前言一、生成器函数 前言 在 Python 中,使用了 yield 的函数被称为生成器(generator) yield 是一个关键字,用于定义生成器函数,生成器函数是一种特殊的函数,可以在迭代过程中逐步产生值ÿ…...

Vue通过Key管理状态

Vue通过Key管理状态 Vue 默认按照“就地更新”的策略来更新,通过 v-for 渲染的元素列表。当数据项的顺序改变时,Vue 不会随之移动 DOM 元素的顺序,而是就地更新每个元素,确保它们在原本指定的索引位置上渲染。为了给 Vue 一个提示…...

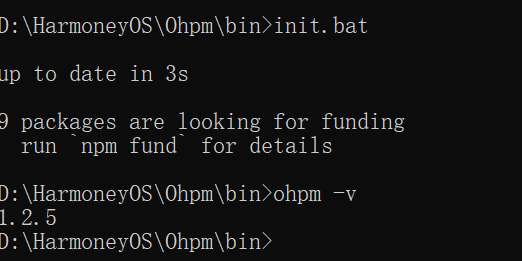

鸿蒙 HarmonyOs 网络请求 快速入门

官方文档: ArkUI简介-ArkUI(方舟UI框架)-应用框架 | 华为开发者联盟 (huawei.com) 一、通过原有的http组件进行网络请求(方式一) 1.1 HttpRequestOptions的操作 名称类型描述methodRequestMethod请求方式ÿ…...

Kubernetes云原生存储解决方案openebs部署实践-4.0.1版本(helm部署)

Kubernetes云原生存储解决方案openebs部署实践-4.0.1版本(helm部署) 简介 OpenEBS 是一种开源云原生存储解决方案。OpenEBS 可以将 Kubernetes 工作节点可用的任何存储转化为本地或复制的 Kubernetes 持久卷。OpenEBS 帮助应用和平台团队轻松地部署需要…...

如何使用Pip生成requirements.txt文件:全面指南与实践示例

如何使用Pip生成requirements.txt文件:全面指南与实践示例 Python的包管理工具Pip是Python开发中不可或缺的一部分。它不仅可以帮助我们安装和管理Python包,还可以通过生成requirements.txt文件来记录项目所需的所有依赖。本文将详细介绍如何使用Pip生成…...

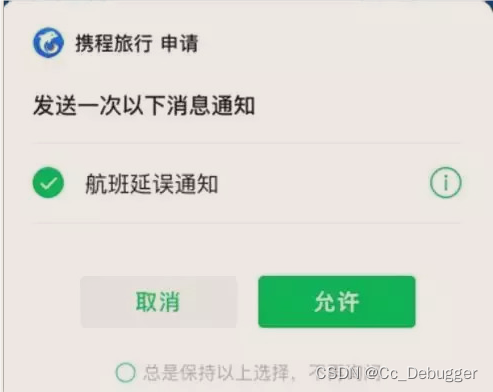

微信小程序消息通知(一次订阅)

在微信公众平台配置通知模版 通过wx.login获取code发送给后端 let that this // 登陆codewx.login({success: function (res) {if (res.code) {// 发送code到后端换取openid和session_keythat.setData({openCode: res.code})console.log(that.data.openCode, openCode);// 调…...

电传动无杆飞机牵引车交付用户

自2019年起,我们计划做电传动控制,先后做了电传动水泥搅拌罐车罐体控制(国内首创),初步理解了电机控制的特点。 20-21年接着做了10t飞机牵引车控制,还是电液控制联合的,把越野叉车的行驶控制方…...

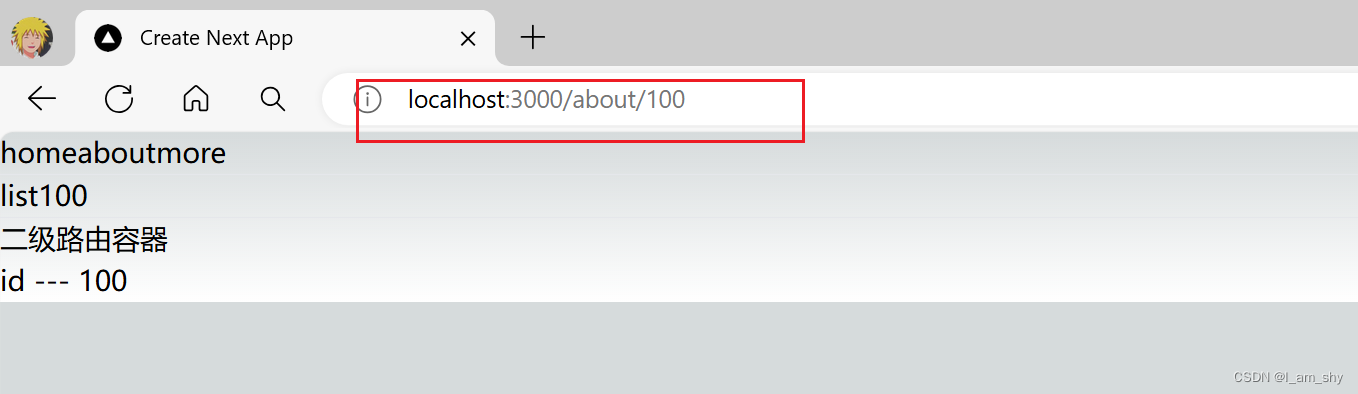

react框架,使用vite和nextjs构建react项目

react框架 React 是一个用于构建用户界面(UI)的 JavaScript 库,它的本质作用是使用js动态的构建html页面,react的设计初衷就是为了更方便快捷的构建页面,官方并没有规定如何进行路由和数据获取,要构建一个完整的react项目,我们需要…...

Games101学习笔记 Lecture16 Ray Tracing 4 (Monte Carlo Path Tracing)

Lecture16 Ray Tracing 4 (Monte Carlo Path Tracing 一、蒙特卡洛积分 Monte Carlo Integration二、路径追踪 Path tracing1.Whitted-Style Ray Tracings Problems2.只考虑直接光照时3.考虑全局光照①考虑物体的反射光②俄罗斯轮盘赌 RR (得到正确shade函数&#x…...

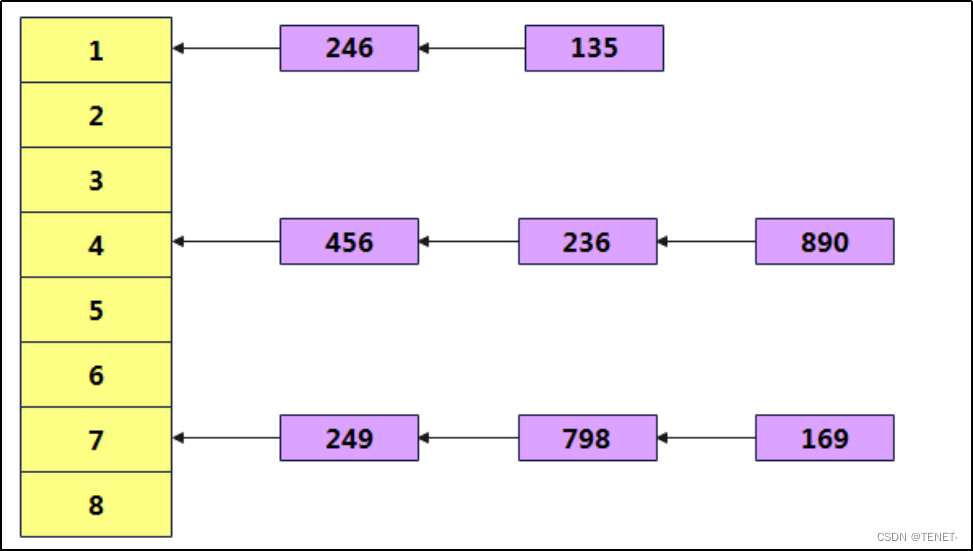

数据结构概念

文章目录 1. 概念 2. 数据结构和算法的关系 3. 内存 4. 数据的逻辑结构 5. 数据的存储结构 1. 顺序存储结构 2. 链式存储结构 3. 索引存储结构 4. 散列存储结构 6. 数据的运算 1. 概念 定义1(宏观): 数据结构是为了高效访问数据而…...

高效音频录制实战:如何为你的Web应用选择最佳编码方案

高效音频录制实战:如何为你的Web应用选择最佳编码方案 【免费下载链接】Recorder html5 js 录音 mp3 wav ogg webm amr g711a g711u 格式,支持pc和Android、iOS部分浏览器、Hybrid App(提供Android iOS App源码)、微信,…...

SMUDebugTool:深度掌控AMD Ryzen系统的硬件调试利器

SMUDebugTool:深度掌控AMD Ryzen系统的硬件调试利器 【免费下载链接】SMUDebugTool A dedicated tool to help write/read various parameters of Ryzen-based systems, such as manual overclock, SMU, PCI, CPUID, MSR and Power Table. 项目地址: https://gitc…...

【技术选型指南】Avalonia、MAUI、Uno Platform、Flutter、Electron、Qt与Tauri:从场景到决策的深度剖析

1. 跨平台框架选型的核心考量因素 当你准备启动一个新项目或重构现有技术栈时,面对琳琅满目的跨平台框架,选择困难症很容易发作。我经历过多次这样的技术决策过程,发现关键在于先明确项目的核心需求。就像装修房子前要先确定是想要北欧简约风…...

如何快速掌握深度学习调参技巧:tuning_playbook_zh_cn完全解析

如何快速掌握深度学习调参技巧:tuning_playbook_zh_cn完全解析 【免费下载链接】tuning_playbook_zh_cn 一本系统地教你将深度学习模型的性能最大化的战术手册。 项目地址: https://gitcode.com/gh_mirrors/tu/tuning_playbook_zh_cn tuning_playbook_zh_cn是…...

菊水PBZ40可编程电源RS232C通信协议实战指南

1. 认识菊水PBZ40可编程电源 如果你正在实验室里捣鼓自动化测试系统,大概率会遇到需要精确控制电源输出的场景。菊水PBZ40就是这样一款专业选手,它不仅能提供稳定的直流输出,还能模拟各种交流波形信号。我第一次接触这台设备时,就…...

OpCore Simplify:自动化OpenCore EFI配置的革命性工具

OpCore Simplify:自动化OpenCore EFI配置的革命性工具 【免费下载链接】OpCore-Simplify A tool designed to simplify the creation of OpenCore EFI 项目地址: https://gitcode.com/GitHub_Trending/op/OpCore-Simplify OpCore Simplify是一款专为Hackinto…...

)

PX4串口通讯避坑指南:从波特率设置到数据收发全流程解析(以Serial4/5为例)

PX4串口通讯实战指南:从硬件配置到数据交互的深度解析 在无人机和机器人开发领域,PX4作为一款开源的飞控系统,其串口通讯功能是实现传感器数据采集、地面站通信以及外设控制的核心技术。然而,许多开发者在实际项目中常会遇到数据丢…...

基于Koopman算子的四旋翼无人机MPC控制开发:一种创新的数据驱动方法

318-一种基于Koopman算子的模型预测控制MPC控制四旋翼无人机开发 简介: 一种基于Koopman算子和扩展动态模式分解(EDMD)的四旋翼无人机学习和控制的新型数据驱动方法。 基于欧拉角(表示方向)等传统方法构建EDMD的观测器已知涉及奇异性。 为了解决这个问题,…...

多角色语音合成解决方案:Chatterbox技术实现与应用指南

多角色语音合成解决方案:Chatterbox技术实现与应用指南 【免费下载链接】chatterbox Open source TTS model 项目地址: https://gitcode.com/GitHub_Trending/chatterbox7/chatterbox 在数字化内容创作与智能交互领域,语音合成技术正经历从单一语…...

低成本搭建DNF外网服务器:腾讯云轻量应用服务器实战教程

腾讯云轻量应用服务器搭建DNF外网版全攻略 最近几年,怀旧游戏私服搭建在技术爱好者圈子里越来越流行。作为一款经典的横版格斗网游,DNF(地下城与勇士)的私服搭建需求尤其旺盛。本文将详细介绍如何利用腾讯云轻量应用服务器&#x…...