使用fifo IP核,给fifo写数据,当检测到ALMOST_EMPTY时,为什么不能立即赋值

这涉及到FIFO(先入先出缓冲器)的内部工作机制和时序考虑。让我详细解释为什么在检测到ALMOST_EMPTY信号时不能立即向FIFO写入数据。

-

ALMOST_EMPTY信号的特性:

- ALMOST_EMPTY是一个预警信号,表示FIFO中的数据量已经接近空。

- 这个信号的目的是提前通知系统,让系统有时间准备新的数据写入。

- ALMOST_EMPTY阈值通常可以在IP核配置时设置。

-

时序考虑:

- FIFO内部状态更新和信号传播需要时间。

- ALMOST_EMPTY信号可能需要一个或多个时钟周期才能反映FIFO的最新状态。

-

写入操作的延迟:

- 写入操作本身也需要时间来完成。

- 从准备数据到实际写入FIFO可能需要一个或多个时钟周期。

-

避免竞争条件:

- 立即响应可能导致竞争条件,特别是在高速系统中。

- 需要确保写入操作不会与其他可能的读取操作冲突。

-

FIFO内部逻辑:

- FIFO可能正在处理其他操作,如内部指针更新。

- 立即写入可能会干扰这些内部操作。

-

稳定性和可靠性:

- 为了确保系统的稳定性,通常需要给予FIFO一定的反应时间。

- 这有助于避免边界条件和潜在的数据完整性问题。

正确的做法:

-

使用状态机:

- 实现一个简单的状态机来管理FIFO写入操作。

- 当检测到ALMOST_EMPTY时,转换到准备写入状态。

-

引入延迟:

- 在检测到ALMOST_EMPTY后,等待一个或多个时钟周期再开始写入操作。

-

使用标志:

- 设置一个标志来指示需要写入数据,而不是立即执行写入。

-

同步设计:

- 确保所有的操作都与系统时钟同步。

示例代码:

以下是一个简单的Verilog代码示例,展示了如何正确处理ALMOST_EMPTY信号:

module fifo_controller (input wire clk,input wire rst,input wire fifo_almost_empty,output reg [7:0] data_to_fifo,output reg write_enable

);reg [1:0] state;

localparam IDLE = 2'b00, PREPARE_WRITE = 2'b01, WRITING = 2'b10;always @(posedge clk or posedge rst) beginif (rst) beginstate <= IDLE;write_enable <= 1'b0;data_to_fifo <= 8'd0;end else begincase (state)IDLE: beginif (fifo_almost_empty) beginstate <= PREPARE_WRITE;write_enable <= 1'b0;endendPREPARE_WRITE: begin// 准备数据,但还不写入data_to_fifo <= 8'hAA; // 示例数据state <= WRITING;endWRITING: beginwrite_enable <= 1'b1;state <= IDLE;endendcaseend

endendmodule

在这个例子中:

- 当检测到ALMOST_EMPTY时,状态机首先进入PREPARE_WRITE状态。

- 在下一个时钟周期,它准备数据但还不执行写入。

- 再下一个时钟周期,它才实际执行写入操作。

这种方法可以确保:

- 有足够的时间来准备数据。

- FIFO有时间更新其内部状态。

- 避免了潜在的时序问题。

不能在检测到ALMOST_EMPTY时立即写入数据,主要是出于时序和可靠性的考虑。通过引入适当的延迟和使用状态机,可以确保FIFO操作的稳定性和可靠性。这种方法在实际系统设计中非常重要,特别是在处理高速数据流或关键应用时。

详细地解释避免竞争条件这一点:

竞争条件(Race Condition):

竞争条件是指系统的行为依赖于多个事件的相对时序,而这些事件的实际发生顺序是不可预测的。在FIFO操作中,这通常涉及到读取和写入操作的时序。

-

FIFO中的竞争条件:

a. 读写冲突:

- 当FIFO几乎为空时,可能同时发生读取和写入操作。

- 如果写入操作不正确处理,可能导致读取无效数据。

b. 状态更新延迟:

- FIFO的内部状态(如空/满标志)可能需要一些时间来更新。

- 立即响应可能基于过时的状态信息。

c. 指针更新:

- FIFO使用读写指针来跟踪数据位置。

- 快速连续的操作可能导致指针更新不一致。

-

高速系统中的特殊考虑:

a. 信号传播延迟:

- 在高速系统中,信号传播时间变得更加重要。

- ALMOST_EMPTY信号可能需要多个时钟周期才能反映当前状态。

b. 时钟域crossing:

- 如果FIFO跨越不同的时钟域,同步问题变得更加复杂。

- 需要额外的时间来确保信号正确同步。

c. 亚稳态:

- 高速系统更容易受到亚稳态的影响。

- 立即响应增加了捕获亚稳态信号的风险。

-

写入操作与读取操作的冲突:

a. 边界条件:

- 当FIFO几乎为空时,读取操作可能正在进行。

- 立即写入可能干扰正在进行的读取操作。

b. 数据完整性:

- 如果写入操作不当,可能导致部分写入或数据损坏。

- 读取操作可能获取到不完整或无效的数据。

c. 标志更新:

- 读取操作可能正在更新FIFO的空标志。

- 立即写入可能导致标志状态不一致。

-

避免竞争条件的策略:

a. 使用同步设计:

- 确保所有操作都与系统时钟同步。

- 使用适当的时序约束来保证信号的稳定性。

b. 实现状态机:

- 使用状态机来控制读写操作的顺序。

- 在状态转换中引入必要的延迟。

c. 双端口FIFO设计:

- 使用真正的双端口FIFO架构,分离读写操作。

- 这可以减少读写冲突的可能性。

d. 使用握手机制:

- 实现请求-确认协议来控制数据传输。

- 这确保了操作的完成被正确确认。

e. 缓冲区:

- 在FIFO接口处添加额外的缓冲寄存器。

- 这可以帮助隔离和同步读写操作。

示例代码:

以下是一个更复杂的Verilog代码示例,展示了如何通过状态机和握手机制来避免竞争条件:

module fifo_controller (input wire clk,input wire rst,input wire fifo_almost_empty,input wire read_in_progress,output reg [7:0] data_to_fifo,output reg write_req,input wire write_ack,output reg read_block

);reg [2:0] state;

localparam IDLE = 3'b000, PREPARE_WRITE = 3'b001, REQUEST_WRITE = 3'b010, WAIT_ACK = 3'b011, WRITING = 3'b100;always @(posedge clk or posedge rst) beginif (rst) beginstate <= IDLE;write_req <= 1'b0;data_to_fifo <= 8'd0;read_block <= 1'b0;end else begincase (state)IDLE: beginif (fifo_almost_empty && !read_in_progress) beginstate <= PREPARE_WRITE;read_block <= 1'b1; // 阻止新的读取操作endendPREPARE_WRITE: begindata_to_fifo <= 8'hAA; // 准备数据state <= REQUEST_WRITE;endREQUEST_WRITE: beginwrite_req <= 1'b1; // 请求写入state <= WAIT_ACK;endWAIT_ACK: beginif (write_ack) beginwrite_req <= 1'b0;state <= WRITING;endendWRITING: beginread_block <= 1'b0; // 允许读取操作state <= IDLE;endendcaseend

endendmodule

在这个例子中:

- 使用了一个更复杂的状态机来控制写入过程。

- 引入了read_in_progress信号来检查是否有正在进行的读取操作。

- 使用write_req和write_ack实现了一个简单的握手机制。

- 添加了read_block信号来暂时阻止新的读取操作,直到写入完成。

这种设计可以有效地避免读写操作之间的竞争条件,确保FIFO操作的可靠性和数据完整性。

避免竞争条件是FIFO设计中的一个关键考虑因素,特别是在高速系统中。通过仔细的时序设计、使用状态机和握手机制,以及适当的缓冲和同步技术,可以大大减少竞争条件的风险,提高系统的可靠性和性能。

详细解释FIFO内部逻辑和立即写入可能带来的干扰问题。

这是FIFO设计中的一个重要方面,涉及到FIFO的内部工作机制。

-

FIFO内部结构:

a. 存储单元:

- FIFO通常由一系列存储单元(如寄存器或RAM)组成。

- 这些单元按顺序排列,形成一个循环缓冲区。

b. 读写指针:

- 读指针(read pointer): 指向下一个要读取的数据位置。

- 写指针(write pointer): 指向下一个可写入数据的位置。

- 这些指针通常是二进制计数器。

c. 状态逻辑:

- 跟踪FIFO的填充状态(如空、满、几乎空、几乎满)。

- 生成相应的标志信号(如EMPTY, FULL, ALMOST_EMPTY, ALMOST_FULL)。

-

FIFO内部操作:

a. 指针更新:

- 每次读操作,读指针递增。

- 每次写操作,写指针递增。

- 这些更新通常在时钟边沿发生。

b. 环绕逻辑:

- 当指针到达FIFO末尾时,需要环绕到开始位置。

- 这涉及复杂的逻辑,特别是在确定FIFO满/空状态时。

c. 状态计算:

- 基于读写指针的位置计算FIFO的当前状态。

- 这可能包括复杂的比较逻辑,尤其是对于"几乎空"和"几乎满"状态。

d. 标志生成:

- 根据计算出的状态生成各种标志信号。

- 这些信号可能需要经过同步处理,特别是在跨时钟域设计中。

-

立即写入可能造成的干扰:

a. 指针更新冲突:

- 如果在指针正在更新时立即写入,可能导致指针值不一致。

- 例如,写指针可能还没有完全更新,就开始新的写入操作。

b. 状态计算错误:

- 立即写入可能发生在FIFO状态正在计算的过程中。

- 这可能导致瞬时的状态不一致,如错误地判断FIFO已满或已空。

c. 标志生成延迟:

- 新的写入可能改变FIFO状态,但相应的标志信号可能还未更新。

- 这可能导致系统基于过时的状态信息做出错误决策。

d. 数据完整性问题:

- 在某些实现中,数据写入可能需要多个时钟周期完成。

- 立即写入可能中断正在进行的写入过程,导致数据不完整。

e. 同步问题:

- 在跨时钟域设计中,立即写入可能干扰正在进行的同步过程。

- 这可能导致亚稳态或数据采样错误。

-

示例场景:

假设一个FIFO正在进行以下操作序列:

-

当前FIFO几乎为空,ALMOST_EMPTY标志刚被置位。

-

内部逻辑正在更新读写指针和计算新的状态。

-

在这个过程中,如果立即执行写入操作:

- 写指针可能在更新过程中被改变,导致指针不一致。

- ALMOST_EMPTY标志可能还未来得及清除,导致错误的状态判断。

- 新的写入可能干扰正在进行的状态计算,导致瞬时的状态错误。

-

代码示例:

以下是一个简化的FIFO内部逻辑示例,展示了可能的问题:

module simple_fifo (input wire clk,input wire rst,input wire write_en,input wire read_en,input wire [7:0] data_in,output reg [7:0] data_out,output reg almost_empty,output reg almost_full

);reg [3:0] write_ptr, read_ptr;

reg [4:0] count; // 额外的位用于满/空检测

reg [7:0] memory [0:15]; // 16深度的FIFOalways @(posedge clk or posedge rst) beginif (rst) beginwrite_ptr <= 4'd0;read_ptr <= 4'd0;count <= 5'd0;almost_empty <= 1'b1;almost_full <= 1'b0;end else begin// 更新指针和计数if (write_en && !almost_full) beginmemory[write_ptr] <= data_in;write_ptr <= write_ptr + 1;count <= count + 1;endif (read_en && !almost_empty) begindata_out <= memory[read_ptr];read_ptr <= read_ptr + 1;count <= count - 1;end// 更新状态标志almost_empty <= (count <= 5'd2);almost_full <= (count >= 5'd14);end

endendmodule

在这个例子中,如果在almost_empty刚被置位,而count和指针还在更新过程中时立即执行写入,可能会导致瞬时的状态不一致。正确的做法是等待至少一个时钟周期,确保所有内部更新都已完成。

-

解决方案:

a. 引入延迟:

- 在检测到ALMOST_EMPTY后,等待至少一个时钟周期再执行写入。

- 这给予FIFO足够的时间完成内部更新。

b. 使用双缓冲:

- 实现输入和输出缓冲区,隔离外部接口和FIFO核心逻辑。

- 这可以减少直接干扰FIFO内部操作的风险。

c. 状态机控制:

- 使用状态机来管理写入操作,确保写入发生在适当的时机。

d. 异步FIFO设计:

- 在读写时钟域不同的情况下,使用异步FIFO设计可以更好地处理时序问题。

总结:

FIFO的内部逻辑涉及复杂的指针管理、状态计算和标志生成。立即写入可能干扰这些操作,导致数据不一致或错误的状态判断。通过理解FIFO的内部工作机制,并采用适当的设计策略(如引入延迟、使用状态机等),可以有效避免这些问题,确保FIFO操作的可靠性和稳定性。

相关文章:

使用fifo IP核,给fifo写数据,当检测到ALMOST_EMPTY时,为什么不能立即赋值

这涉及到FIFO(先入先出缓冲器)的内部工作机制和时序考虑。让我详细解释为什么在检测到ALMOST_EMPTY信号时不能立即向FIFO写入数据。 ALMOST_EMPTY信号的特性: ALMOST_EMPTY是一个预警信号,表示FIFO中的数据量已经接近空。这个信号…...

【Python123题库】#汽车迷 #编写函数输出自除数 #身份证号基本信息

禁止转载,原文:https://blog.csdn.net/qq_45801887/article/details/140080109 参考教程:B站视频讲解——https://space.bilibili.com/3546616042621301 有帮助麻烦点个赞 ~ ~ Python123题库 汽车迷编写函数输出自除数身份证号基本信息 汽车…...

普通人怎么利用GPT赚钱之SEO优化内容

如何利用GPT撰写SEO优化内容:全面指南 在当今的数字化世界,搜索引擎优化(SEO)是提升网站流量和曝光率的关键。高质量的SEO优化内容不仅可以提高搜索引擎排名,还能吸引更多潜在客户。GPT(生成预训练变换器)作为一种先进的人工智能工具,可以大大提升SEO内容创作的效率和…...

LeetCode热题100刷题8:54. 螺旋矩阵、73. 矩阵置零、48. 旋转图像

54. 螺旋矩阵 class Solution { public:vector<int> spiralOrder(vector<vector<int>>& matrix) {vector<int> vec;if(matrix.empty())return vec;int left0;int right matrix[0].size()-1;int up0;int down matrix.size()-1;while(true) {for(i…...

景联文科技打造高质量图文推理问答数据集,赋能大语言模型提升推理能力

大语言模型在处理推理任务时,不同于人类能够反思错误并修正思维路径,当它遇到自身知识盲区时,缺乏自我校正机制,往往导致输出结果不仅无法改善,反而可能变得更不准确。 需要依赖外部的知识库和推理能力来克服其在理解和…...

用网络编程完成windows和linux跨平台之间的通信(服务器)

服务器代码逻辑: 服务器功能 创建 Socket: 服务器首先创建一个 Socket 对象,用于进行网络通信。通常使用 socket() 函数创建。 绑定(Bind): 服务器将 Socket 绑定到一个特定的 IP 地址和端口号上。这是通过…...

力扣3148.矩阵中的最大得分

力扣3148.矩阵中的最大得分 类似二维前缀和 枚举右下角 求(i,j) - (0,0)的子矩阵的最小值每次与当前点作差 求答案 class Solution {public:int maxScore(vector<vector<int>>& grid) {int res INT_MIN;int m grid.size(),n grid[0].size();vector<ve…...

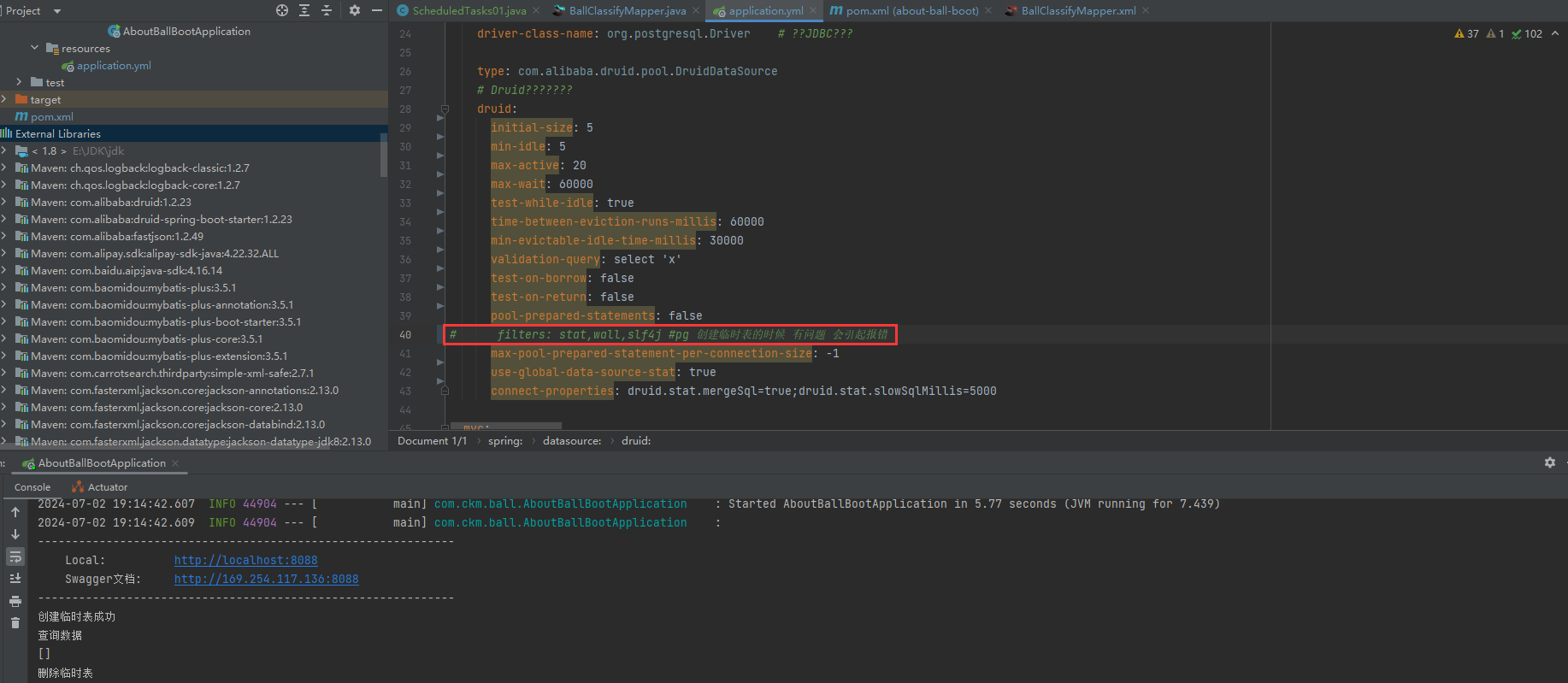

解决数据库PGSQL,在Mybatis中创建临时表报错TODO IDENTIFIER,连接池用的Druid。更换最新版本Druid仍然报错解决

Druid版本1.1.9报错Caused by: java.sql.SQLException: sql injection violation, syntax error: TODO IDENTIFIER : CREATE TEMPORARY TABLE temp_ball_classify (id int8 NOT NULL,create_time TIMESTAMP,create_by VARCHAR,classify_name VARCHAR) 代码如下: 测…...

【WPF】桌面程序开发之xaml页面基础布局方式详解

使用Visual Studio开发工具,我们可以编写在Windows系统上运行的桌面应用程序。其中,WPF(Windows Presentation Foundation)项目是一种常见的选择。然而,对于初学者来说,WPF项目中xaml页面的布局设计可能是一…...

第十五章 Nest Pipe(内置及自定义)

NestJS的Pipe是一个用于数据转换和验证的特殊装饰器。Pipe可以应用于控制器(Controller)的处理方法(Handler)和中间件(Middleware),用于处理传入的数据。它可以用来转换和验证数据,确…...

:使用Processing创建动态图形:诡异八爪鱼)

实战篇(八):使用Processing创建动态图形:诡异八爪鱼

使用Processing创建动态图形:诡异八爪鱼 引言 在这个教程中,我们将深入探讨如何使用Processing编程语言创建一个动态的图形效果。我们将通过一个具体的例子,展示如何绘制一个跟随鼠标移动的“鱿鱼”图形,并使其颜色和形状动态变化。这个项目不仅适合初学者学习Processing…...

大模型成为软件和数据工程师

前言 想象一下这样一个世界:人工智能伙伴负责编码工作,让软件和数据工程师释放他们的创造天赋来应对未来的技术挑战! 想象一下:你是一名软件工程师,埋头于堆积如山的代码中,淹没在无数的错误中࿰…...

【鸿蒙学习笔记】页面布局

官方文档:布局概述 常见页面结构图 布局元素的组成 线性布局(Row、Column) 了解思路即可,更多样例去看官方文档 Entry Component struct PracExample {build() {Column() {Column({ space: 20 }) {Text(space: 20).fontSize(15)…...

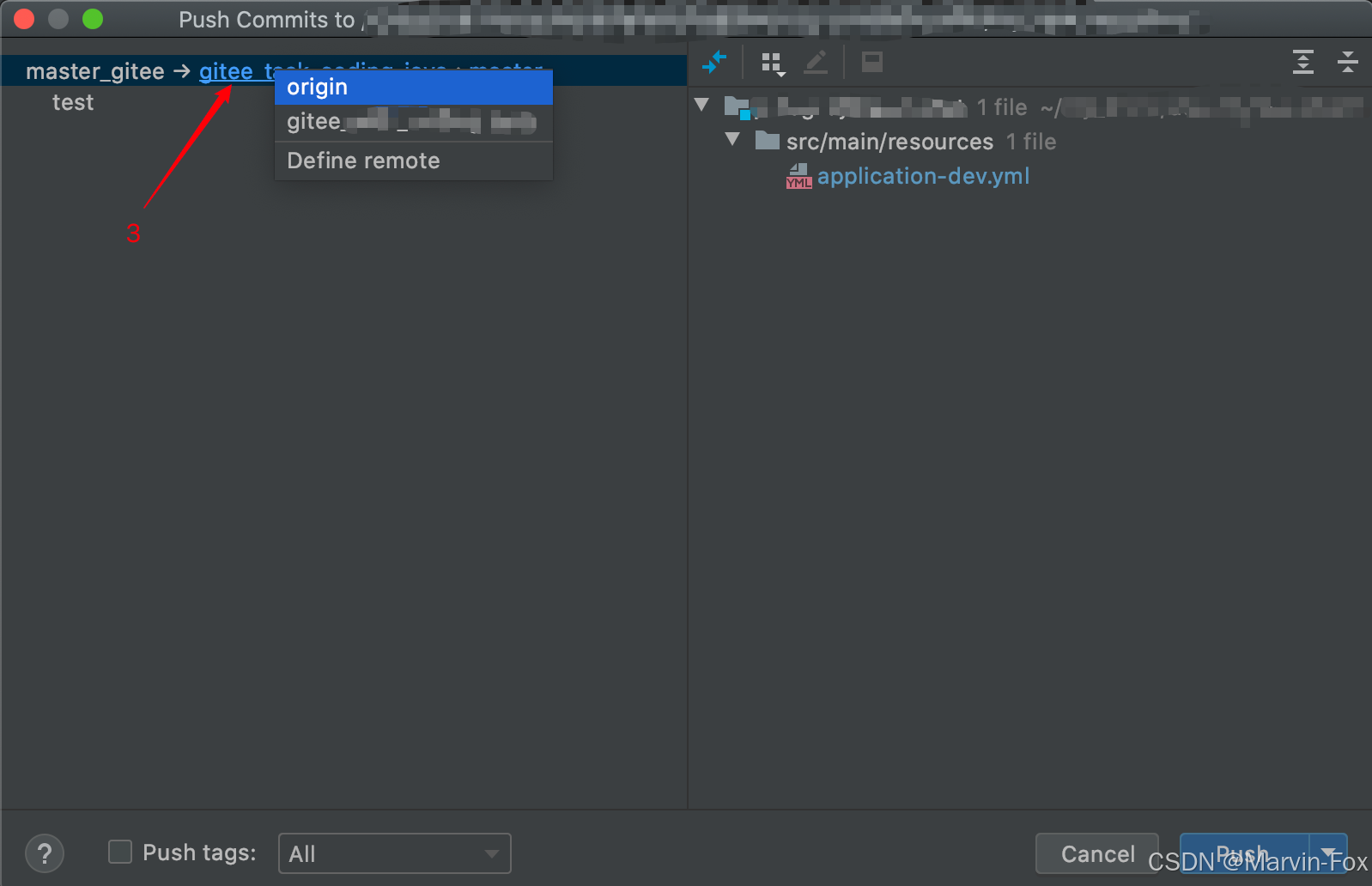

GIT 使用相关技巧记录

目录 1、commit 用户信息变更 全局用户信息(没有特殊配置的情况下默认直接用全局信息) 特定仓库用户信息(只针对于当前项目) 方法一:修改config文件 方法二:命令方式 2、idea同一代码推向多个远端仓库…...

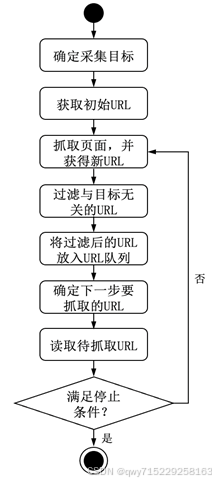

1-认识网络爬虫

1.什么是网络爬虫 网络爬虫(Web Crawler)又称网络蜘蛛、网络机器人,它是一种按照一定规则,自动浏览万维网的程序或脚本。通俗地讲,网络爬虫就是一个模拟真人浏览万维网行为的程序,这个程序可以代替真人…...

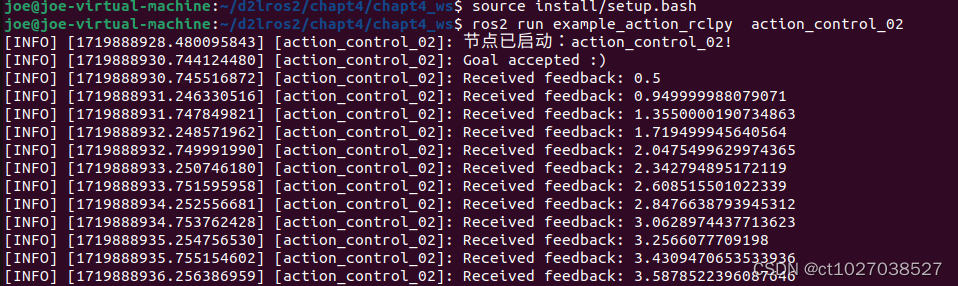

ROS2使用Python开发动作通信

1.创建接口节点 cd chapt4_ws/ ros2 pkg create robot_control_interfaces --build-type ament_cmake --destination-directory src --maintainer-name "joe" --maintainer-email "1027038527qq.com" mkdir -p src/robot_control_interfaces/action touch…...

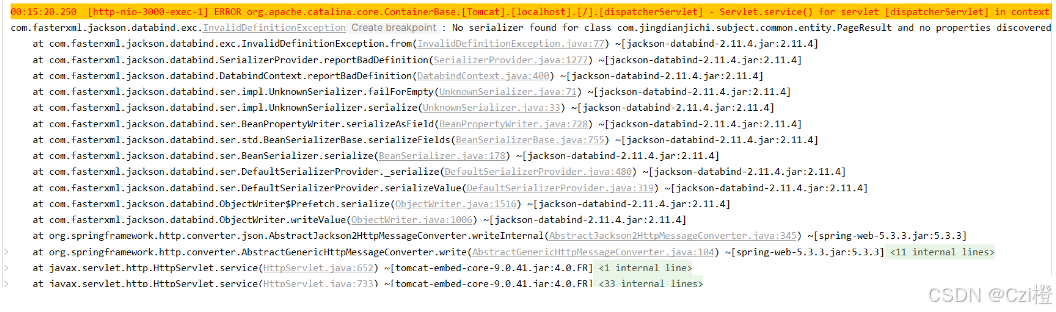

Bug记录:【com.fasterxml.jackson.databind.exc.InvalidDefinitionException】

bug记录 序列化错误 异常com.fasterxml.jackson.databind.exc.InvalidDefinitionException: 完整错误(主要是FAIL_ON_EMPTY_BEANS) 00:15:20.250 [http-nio-3000-exec-1] ERROR org.apache.catalina.core.ContainerBase.[Tomcat].[localhost].[/].[dispatcherServlet] - S…...

Mongodb索引的删除

学习mongodb,体会mongodb的每一个使用细节,欢迎阅读威赞的文章。这是威赞发布的第87篇mongodb技术文章,欢迎浏览本专栏威赞发布的其他文章。如果您认为我的文章对您有帮助或者解决您的问题,欢迎在文章下面点个赞,或者关…...

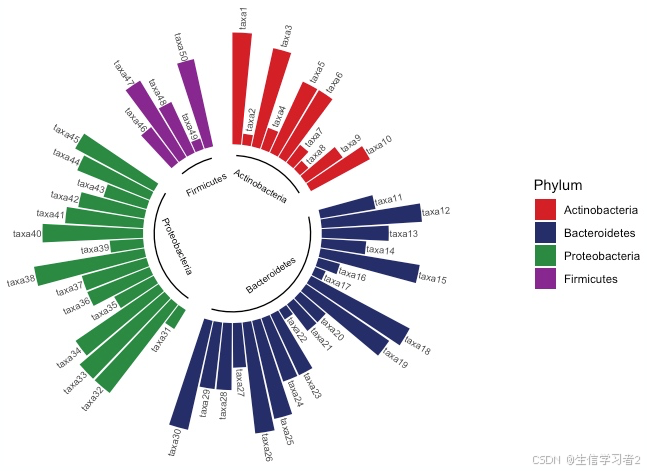

科研绘图系列:R语言径向柱状图(Radial Bar Chart)

介绍 径向柱状图(Radial Bar Chart),又称为雷达图或蜘蛛网图(Spider Chart),是一种在极坐标系中绘制的柱状图。这种图表的特点是将数据点沿着一个或多个从中心向外延伸的轴来展示,这些轴通常围绕着一个中心点均匀分布。 特点: 极坐标系统:数据点不是在直角坐标系中展…...

鸿蒙开发管理:【@ohos.account.distributedAccount (分布式帐号管理)】

分布式帐号管理 本模块提供管理分布式帐号的一些基础功能,主要包括查询和更新帐号登录状态。 说明: 本模块首批接口从API version 7开始支持。后续版本的新增接口,采用上角标单独标记接口的起始版本。开发前请熟悉鸿蒙开发指导文档ÿ…...

Mapbox GL JS 新手必看:GeoJSON 数据坐标填错,地图显示全乱套?

Mapbox GL JS 开发避坑指南:GeoJSON 坐标系问题全解析 刚接触 Mapbox GL JS 的开发者经常会遇到一个令人抓狂的问题:明明按照文档写了代码,GeoJSON 数据也加载成功了,但地图上的点线面全都显示在错误的位置,有的甚至跑…...

Hermes性能优化:如何提高邮件生成速度和降低资源消耗

Hermes性能优化:如何提高邮件生成速度和降低资源消耗 【免费下载链接】hermes Golang package that generates clean, responsive HTML e-mails for sending transactional mail 项目地址: https://gitcode.com/gh_mirrors/he/hermes Hermes是一个Golang包&a…...

告别Lottie和SVGA:用Unity给Android应用做高性能动态引导动画的实战踩坑记录

告别Lottie和SVGA:用Unity给Android应用做高性能动态引导动画的实战踩坑记录 在移动应用开发中,动态引导动画一直是提升用户体验的关键元素。从早期的帧动画到后来的Lottie、SVGA等方案,开发者们不断寻求更高效、更灵活的动画实现方式。然而&…...

Cursor Pro免费激活终极指南:3步永久解锁AI编程神器

Cursor Pro免费激活终极指南:3步永久解锁AI编程神器 【免费下载链接】cursor-free-vip [Support 0.45](Multi Language 多语言)自动注册 Cursor Ai ,自动重置机器ID , 免费升级使用Pro 功能: Youve reached your trial…...

无人机新手必看:Remote ID和ADS-B到底选哪个?从原理到实战全解析

无人机新手必看:Remote ID和ADS-B到底选哪个?从原理到实战全解析 刚入手的无人机在阳光下闪着金属光泽,充电时发出的细微电流声让人心跳加速——直到你发现说明书最后一页印着"需遵守Remote ID或ADS-B监管要求"。这两个陌生术语瞬…...

)

28GHz毫米波滤波器设计实战:用SynMatrix快速搞定SIW带通滤波器(附完整参数)

28GHz毫米波滤波器设计实战:SynMatrix工具链的高效应用指南 在毫米波频段,滤波器设计一直是射频工程师面临的重大挑战之一。尤其是当工作频率上升到28GHz甚至更高时,传统设计方法往往陷入反复迭代的泥潭,耗费大量时间在仿真优化与…...

)

告别while循环轮询!用STM32 HAL库定时器中断实现按键扫描(附状态机源码)

STM32高效按键处理实战:定时器中断与状态机的完美结合 在嵌入式开发中,按键处理看似简单却暗藏玄机。传统while循环轮询方式不仅占用CPU资源,还容易导致代码结构混乱。本文将带你用STM32 HAL库的定时器中断和状态机,实现一套高效、…...

OFA图像描述效果展示:COCO风格caption生成——简洁、准确、自然

OFA图像描述效果展示:COCO风格caption生成——简洁、准确、自然 1. 项目概述 今天要给大家展示一个特别实用的AI工具——基于OFA模型的图像描述生成系统。这个工具能够自动为任何图片生成简洁、准确、自然的英文描述,就像给图片配上了专业的文字说明。…...

炸锅!Claude Code 完整源码意外泄露,51 万行核心代码直接开源!

突发!Claude Code 意外开源 51 万行源码全网曝光 2026 年 3 月 31 日,AI 圈迎来重磅事件 ——Anthropic 旗下 Claude Code 因 npm 配置失误,通过 source map 文件意外泄露全部源码,超 1900 个文件、51.2 万行 TypeScript 代码公开…...

Godot PCK文件高效解包全攻略:从资源提取到实战应用

Godot PCK文件高效解包全攻略:从资源提取到实战应用 【免费下载链接】godot-unpacker godot .pck unpacker 项目地址: https://gitcode.com/gh_mirrors/go/godot-unpacker 作为游戏开发者或爱好者,你是否曾遇到过想要分析或复用Godot引擎打包的游…...