计算机组成原理|第四章(笔记)

目录

- 第四章 存储器

- 4.1 概述

- 4.1.1 存储器分类

- 4.1.2 存储器的层次结构

- 4.2 主存储器

- 4.2.1 概述

- 4.2.2 半导体存储芯片简介

- 4.2.3 随机存取存储器(RAM)

- 4.2.4 只读存储器(ROM)

- 4.2.5 存储器与CPU的连接

- 4.2.6 存储器的校验

- 4.2.7 提高访存速度的措施

- 4.3 高速缓冲存储器(Cache)

- 4.3.1 概述

- 4.3.2 Cache --- 主存地址映象

- 4.3.3 替换算法

- 4.4 辅助存储器

- 4.4.1 概述

- 4.4.2 磁记录原理和记录方式

- 4.4.3 硬磁盘存储器

- 4.4.4 软磁盘存储器

- 4.4.5 光盘存储器

- 4.4.6 循环冗余校验码(CRC码)

- 4.4.7 光盘存储器

上篇:第三章:系统总线

第四章 存储器

4.1 概述

存储器是计算机系统中的记忆设备,用来存放程序和数据。是计算机系统中最重要的组件之一,执行程序时所需要的指令、数据都来自于存储器,程序的执行结果也保存在存储器当中,另外,各种文档、音频资料等也是保存在存储器当中。

4.1.1 存储器分类

按存储介质分类

- 半导体存储器:存储元件由半导体器件组成的,优点是体积小、功耗低、存取时间短,缺点是当电源消失时,所存信息也会消失,它是一种

易失性存储器。- 双极型(TTL)半导体存储器:高速

- MOS 半导体存储器:制造简单、成本低廉、功耗小

- 磁表面存储器:在金属或塑料基体的表面上涂一层磁性材料作为记录介质,工作时磁层随载体高速运转,用

磁头在磁层上进行读写操作,不易失。- 磁盘

- 磁带

- 磁鼓

- 磁心存储器:由硬磁材料、环状元件组成,在磁心中穿有驱动线和读出线进行读写操作,不易失的永久存储器。

- 光盘存储器:由激光、磁光材料组成,应用激光在记录介质上进行读写的存储器,具有非易失性的特点。

按存取方式分类

- 存取时间与物理地址无关(随机访问)

- 随机存储器(RAM):在程序的执行过程中可读可写

- 只读存储器(ROM):在程序的执行过程中只读

- 存取时间与物理地址有关(串行访问)

- 顺序存取存储器 — 磁带

- 直接存取存储器 — 磁盘

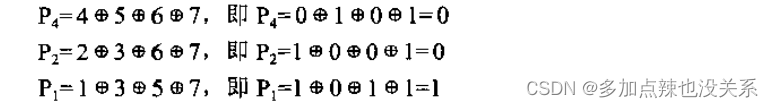

按在计算机中的作用分类

4.1.2 存储器的层次结构

存储器的三个特性:速度、容量和价格/位(简称位价)。

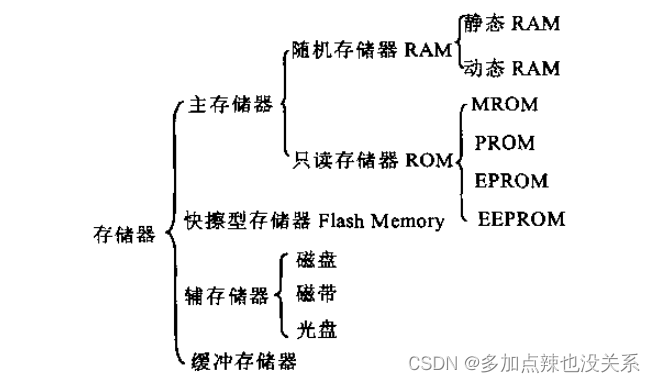

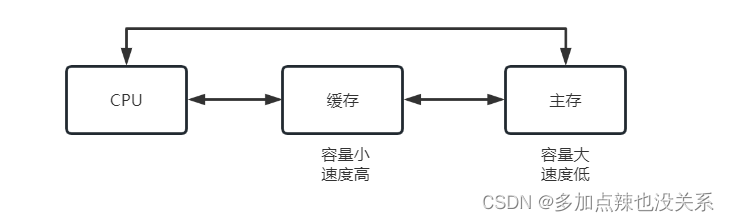

存储器分层结构图:

CPU 不能直接访问辅存,辅存只能与主存交换信息,因此辅存的速度可以比主存慢得多。

存储器的层次结构主要体现在缓冲---主存和主存---辅存这两个存储层次上。

从 CPU 角度来看,缓存—主存 这一层次的速度接近于缓存,高于主存;主存–辅存 这一层次,从整体分析,其速度接近主存,容量接近于辅存。现代的计算机系统几乎都具有这两个存储层次,构成了缓存、主存、辅存三级存储系统。

主存—辅存这一层次形成了虚拟存储系统。在这个系统中,程序员编程的地址范围与虚拟存储器的地址空间相对应。虚拟存储器中用到的地址叫作虚地址(虚存地址、虚拟地址)或叫逻辑地址,而主存的实际地址称为物理地址或实地址。

4.2 主存储器

4.2.1 概述

主存储器是存储器子系统中的一类,用来存放程序和数据,它可以直接与CPU 交换信息。

主存中还必须配置两个寄存器 MAR 和 MDR。

- MAR(Memory Address Register):存储器地址寄存器,用来存放欲访问的存储单元的地址。

- MDR(Memory Data Register):存储器数据寄存器,用来存放从存储体某单元取出的代码或者准备往某存储单元存入的代码。

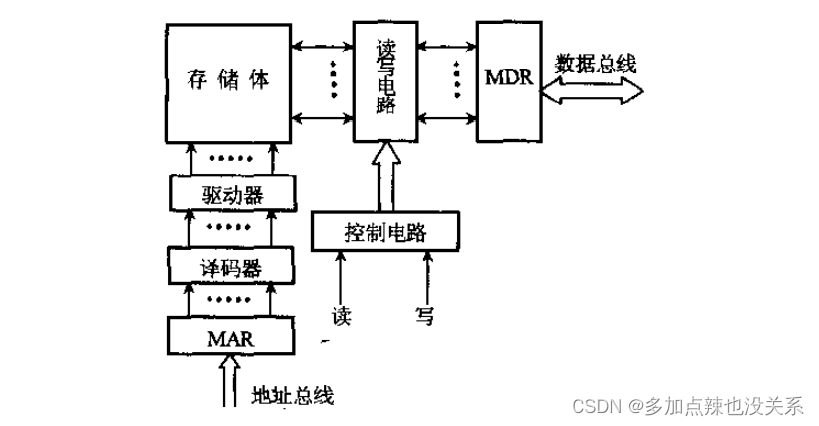

主存的基本组成:

驱动器、译码器和读写电路均制作在存储芯片中,而 MAR 和 MDR 制作在 CPU 芯片内,存储芯片和 CPU 芯片可通过总线连接。

实际上,根据 MAR 中的地址访问某个存储单元时,还需要经过地址译码、驱动等电路,才能找到所需访问的单元。读出时,需经过读出放大器,才能将被选中单元的存储字送到 MDR。写入时,MDR 中的数据也必须经过电路才能真正写入到被选中的单元中。

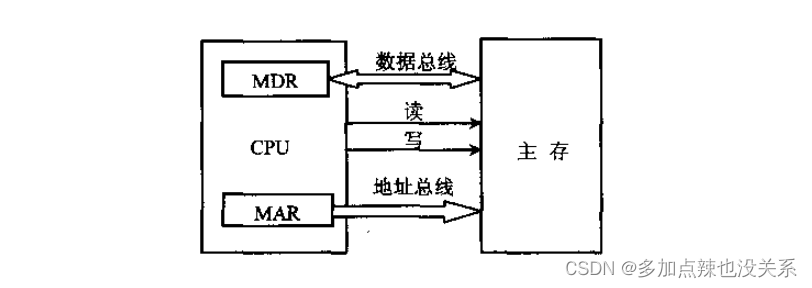

主存和 CPU 的联系:

CPU 和主存之间的连接信号分成:数据总线、控制总线和地址总线。

数据总线完成 CPU 和主存之间的信息传输,所以数据总线直接连在 MDR 寄存器上,是双向的,可能读出也可能进行写入;地址总线连接在 MAR 寄存器和主存之间,给出要访问内存单元的地址,从 CPU 送到主存,所以是单向的;控制总线也是单向的,由 CPU 送至主存储器。

主存中存储单元地址的分配:

主存各存储单元的空间位置是由单元地址号来表示的,而地址总线是用来指出存储单元地址号的,根据该地址可读出一个存储字。

在主存中数据的存放可以按照:① 以高位字节地址为字地址;② 以低位字节地址为字地址。两种方式进行存放。它的原理可参考博客:【主存中存储单元地址的分配】

主存的技术指标:

- 存储容量:是指主存能存放二进制代码的总数。

- 存储容量 = 存储单元个数 × 存储字长

- 存储速度:是由存取时间和存取周期来表示的。

- 存取时间:又叫存储器的访问时间,它是指启动一次存储器操作(读或写)到完成该操作所需的全部时间。

- 存取周期:是指存储器进行连续两次独立的存储器操作(如连续两次读操作)所需的最小间隔时间。

- 存储器的带宽:单位时间(位/秒)里能够读取或者是写入多少位数据。

4.2.2 半导体存储芯片简介

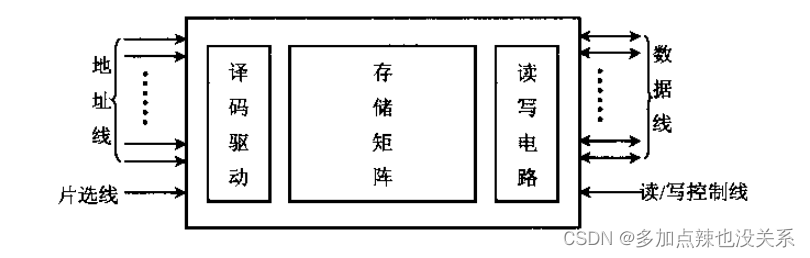

半导体存储芯片的基本结构:

- 译码驱动:能把地址总线送来的信号翻译成对应存储单元的选择信号,该信号在读写电路的配合下完成对被选中单元的读写操作。

- 读写电路:包括读出放大器和写入电路,用来完成读写操作。

存储芯片是通过地址总线、数据总线和控制总线与外部连接:

- 地址线:单向输入,其位数与芯片容量有关

- 数据线:双向,其位数与芯片可读出或写入的数据位数有关

地址线和数据线共同反映存储芯片的容量。

| 地址线 | 数据线 | 芯片容量 |

|---|---|---|

| 10 | 4 | 210× 4 = 1K × 4 位 |

| 14 | 1 | 214× 1 = 16K × 1 位 |

| 13 | 8 | 213× 8 = 8K × 8 位 |

- 控制总线

- 读/写控制线:决定芯片进行读/写操作

- WE‾\overline{\text{WE}}WE:低电平写,高电平读

- OE‾\overline{\text{OE}}OE: 允许读

- 片选线:选择存储芯片

- CS‾\overline{\text{CS}}CS:芯片选择信号

- CE‾\overline{\text{CE}}CE:芯片使能信号

- 读/写控制线:决定芯片进行读/写操作

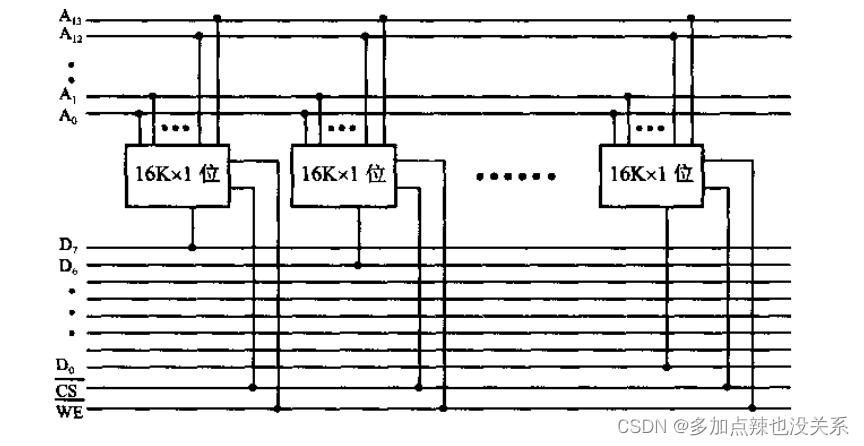

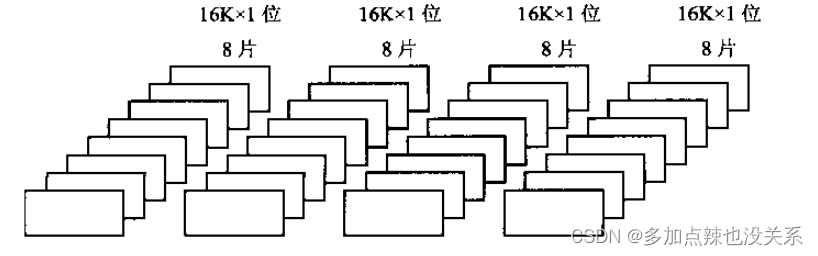

用 16K × 1 位的存储芯片组成 64K × 8 位的存储器

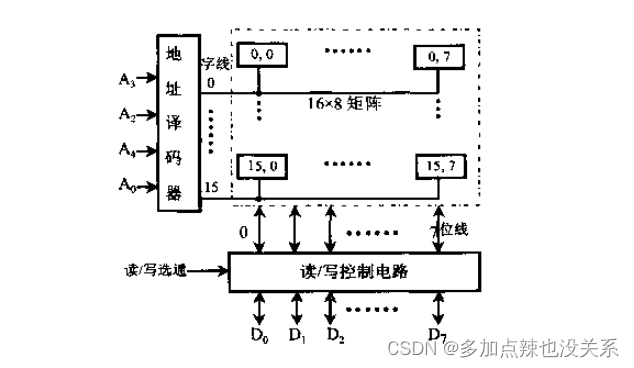

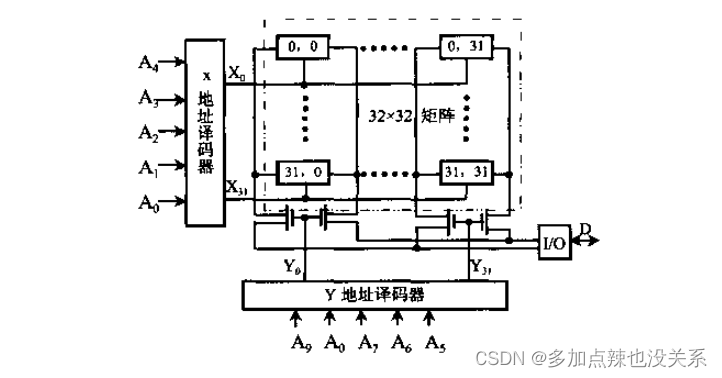

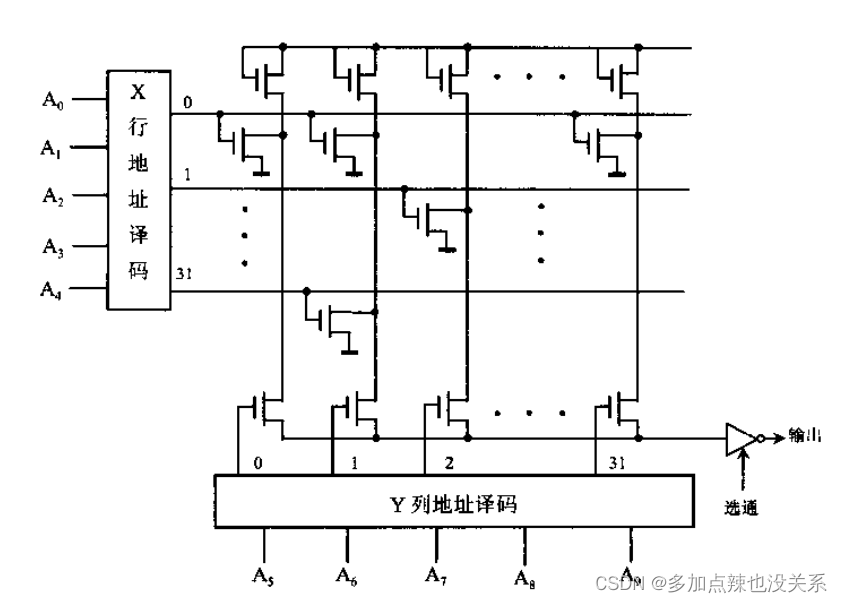

半导体存储芯片的译码驱动方式:

半导体存储芯片的译码驱动方式有两种:线选法和重合法。关于译码不太理解的可以去看:《数字逻辑设计-哈工大:P35》

-

线选法

上图是一个 16 × 1 字节线法存储芯片的结构示意图,它的特点是用一根字选线(字线),直接选中一个存储单元的各位(如一个字节),这种方式结构比较简单,但只适用于容量不大的存储芯片。 -

重合法

上图是一个1K × 1 位重合法结构示意图,由于被选单元是由 X、Y 两个方向的地址决定的,故称重合法。

4.2.3 随机存取存储器(RAM)

随机存储器按存储信息原理的不同可分为:静态 RAM和动态 RAM。

静态 RAM(Static RAM 或记作 SRAM):

存储器中用于寄存 “0” 和 “1” 代码的电路叫做存储器的基本单元电路。

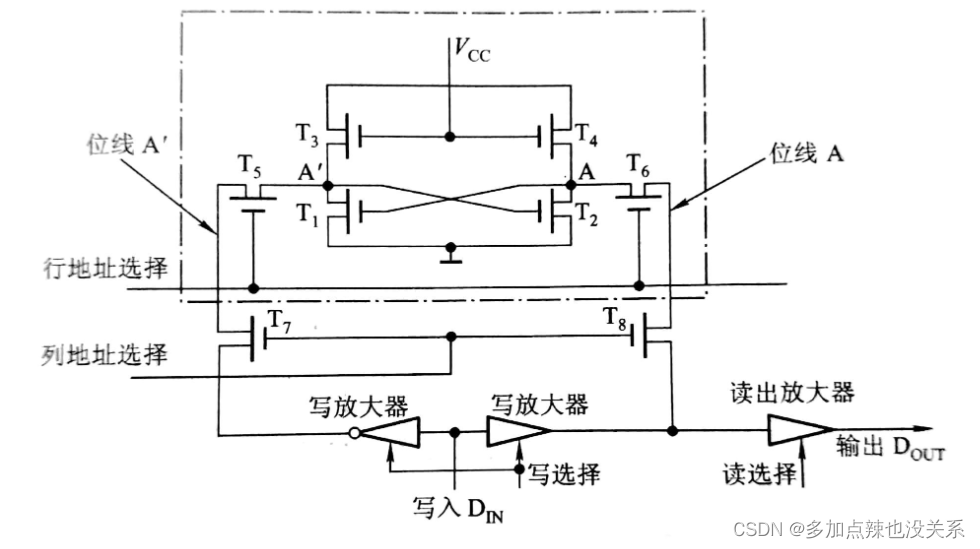

(1)静态 RAM 的基本单元电路

- T1 ~ T4 触发器

- T5、T6 行开关

- T7、T8 列开关,一列共用

- A 触发器原端

- A’ 触发器非端

静态 RAM 基本单元的 读操作:① 行选 – > T5、T6 开;② 列选 – > T7、T8 开;③ 读选择有效;④ VA – > T6 – > T8 – > 读放 – > DOUT

静态 RAM 基本单元的 写操作:① 行选 – > T5、T6 开;② 列选 – > T7、T8 开;③ 写选择有效;④ DIN – > 两个写放 (左:DIN – > 相反 – > T7 – > T5 – > A’;右:DIN – > T8 – > T6 – > A)

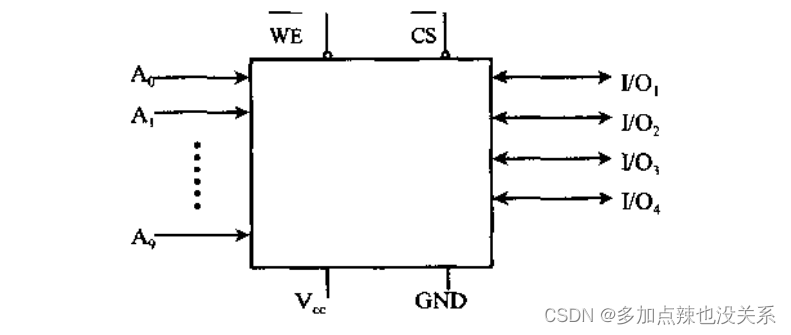

(2)静态 RAM 芯片举例(Intel 2114 芯片)

- A0 ~ A9 为地址输入端

- I / O1 ~ I / O4 为数据输入 / 输出端

- CS‾\overline{\text{CS}}CS 为片选信号(低电平有效)

- WE‾\overline{\text{WE}}WE 为允许信号(低电平为写)

- VCC 为电源端

- GND 为接地端

动态 RAM(Dynamic RAM 或 DRAM):

动态 RAM 都是靠电容存储电荷的原理来寄存信息的,若电容上存有足够多的电荷表示存 “1”,电容上无电荷表示存 “0”。

(1)动态 RAM 的基本单元电路

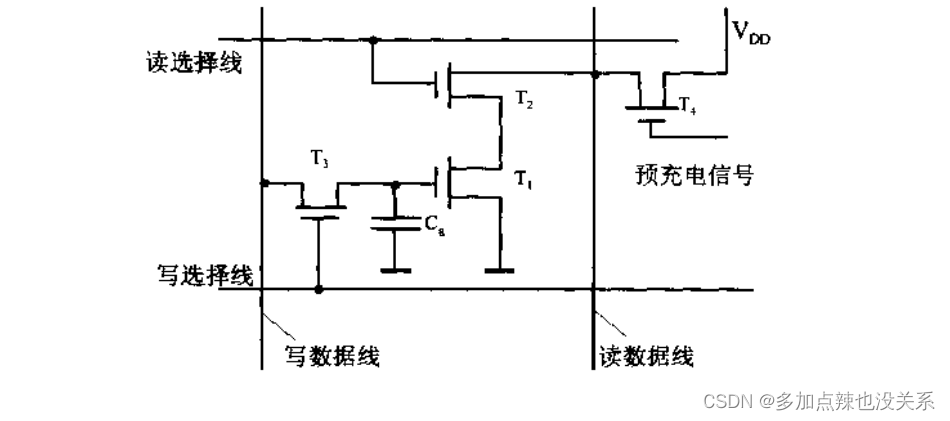

常见动态 RAM 的基本单元电路可分为三管式和单管式两种。

-

三管 MOS 动态 RAM 基本单元电路

- 读出时,先对预充电管 T4 置一预充电信号(在存储矩阵中,每一列共用一个 T4管),使读数据线高达电平 VDD。然后由读选择线打开 T2,若 T1的极间电荷 Cg存有足够多的电荷(被认为原存 “1”),使 T1 导通,则因 T2、T1导通接地,使读数据线降低为零电平,读出 “0” 信息。若 Cg 没有足够电荷(原存 “0”),则 T1截止,读数据线为高电平不变,读出 “1” 信息。可见,由读出线的高低电平可区分其是读 “1” 还是读 “0”,只是它与原存信息反相。

- 写入时,将写入信号加到写数据线上,然后由写选择线打开 T3,这样,Cg便能随输入信息充电(写 “1”)或放电(写 “0”)。

-

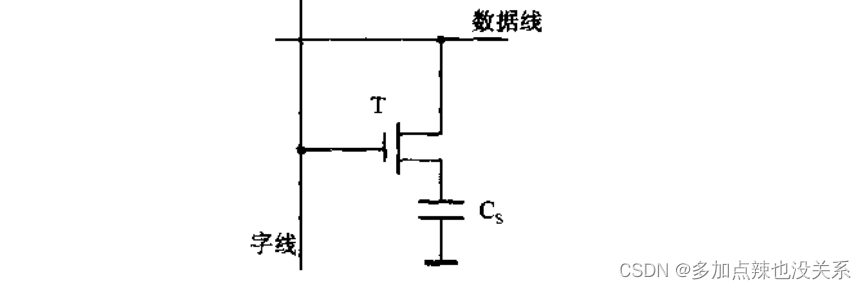

单管 MOS 动态 RAM 基本单元电路

- 读出时,字线上的高电平使 T 导通,若 CS 有电荷,经 T 管在数据线上产生电流,可视为读出 “1”。若 CS 无电荷,则数据线上无电流,可视为读出 “0”。读操作结束时,CS 的电荷已泄放完毕,故是破坏性读出,必须再生。

- 写入时,字线为高电平使 T 导通,若数据线上为高电平,经 T 管对 CS 充电,使其存 “1";若数据线为低电平,则 CS 经 T 放电,使其无电荷而存 “0”。

(2)动态 RAM 芯片举例

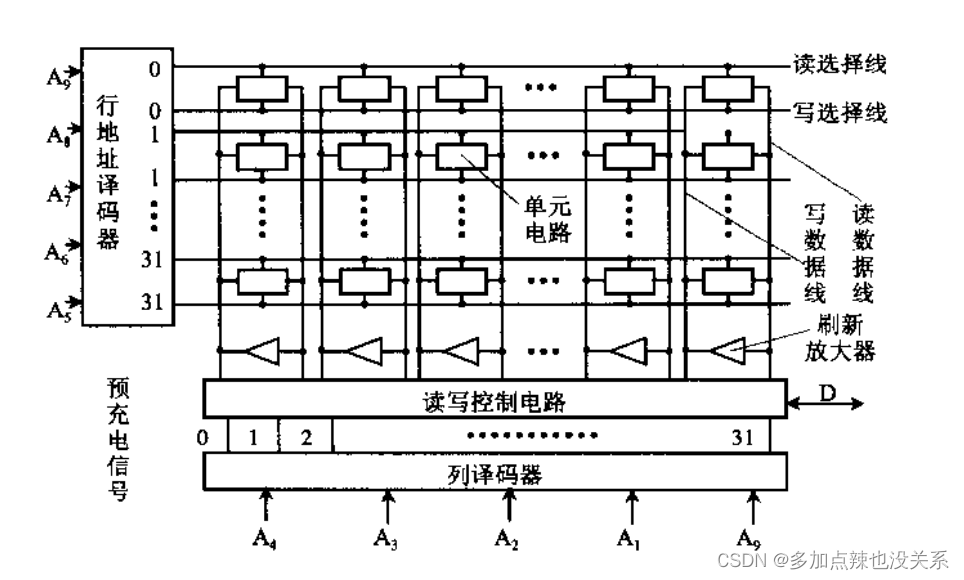

1K×1 位三管 MOS 动态 RAM 结构示意图:

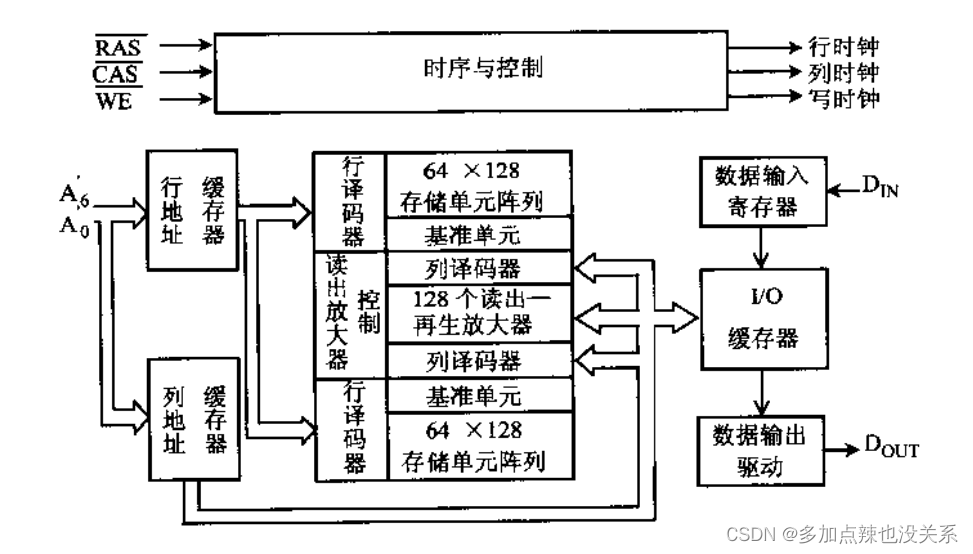

4116 动态 RAM(16K×1位)芯片结构:

(3)动态 RAM 的刷新

动态 RAM 是利用电容存储电荷的方式来保存信息的,电容很容易漏电,在一段时间之内,如果不对电容当中的信息进行进行再生的话,电容信息就会丢失,因此,必须采用定时刷新的方法,在一定的时间内,对动态 RAM 的全部基本单元电路必作一次刷新,一般取 2ms,这个时间叫作刷新周期,或再生周期。

对动态 RAM 的刷新只和行地址有关,和列地址无关,也就是说每一次刷新操作,刷新的是动态 RAM 当中的每行所有的基本单元电路。

动态 RAM 的刷新有三种方法:

- 集中刷新:是在规定的一个刷新周期内,对全部存储单元集中一段时间逐行进行刷新,此刻必须停止读/写操作。

- 分散刷新:是指对每行存储单元的刷新分散到每个读/写周期内完成。

- 异步刷新:集中刷新与分散刷新相结合,

动态 RAM 和 静态 RAM 的比较:

| 比较项目 | DRAM | SRAM |

|---|---|---|

| 存储原理 | 电容 | 触发器 |

| 集成度 | 高 | 低 |

| 芯片引脚 | 少 | 多 |

| 功耗 | 小 | 大 |

| 价格 | 低 | 高 |

| 速度 | 慢 | 快 |

| 刷新 | 有 | 无 |

4.2.4 只读存储器(ROM)

按 ROM 的原始定义,一旦注入原始信息后是不能改变的,但随着用户的需要,希望能修改 ROM 原始信息,便出现了用户可以一次性写的 ROM,之后又出现了能对信息进行擦除,并且可以多次写的 ROM。

1. 掩膜 ROM(MROM)

掩膜 ROM(MacroRead Only Memory),中文全称掩膜式只读存储器。掩膜式只读存储器中的信息是已经被生产厂家制作到芯片中的,是不可更改的,使用者不能对其进行编写。

行列选择线交叉处有 MOS 管为 “1”,行列选择线交叉处无 MOS 管为 “0”。

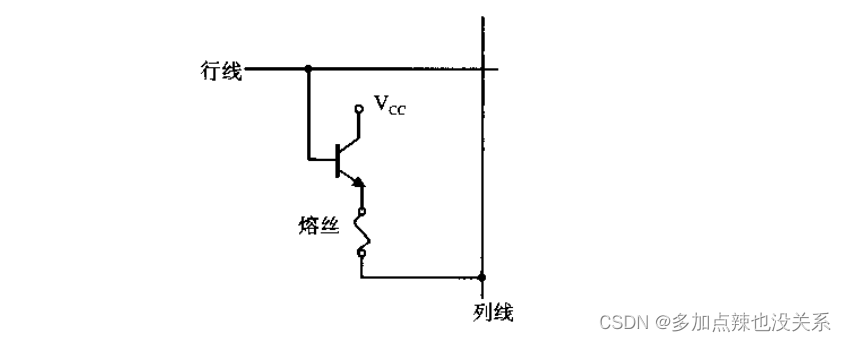

2. PROM(一次性编程)

PROM 是可以实现一次性编程的只读存储器。

如上图所示是一个 双极型镍铬熔丝式单元电路 ,这里面有一个熔丝,如果进行读出或者写入的话,就可以通过熔丝通和断来保存信息,熔丝断为 “0”,熔丝未断为 “1”,熔丝断了之后是不能再给它接回去的,所以是一次性编程的 ROM。

3. EPROM(多次性编程)

EPROM 是一种可擦洗可编程的只读存储器。它可以由用户对其所存信息作任意次的改写。

目前用得较多的 EPROM 是用浮动栅雪崩注入型 MOS 管构成,又称 FAMOS 型 EPROM。

D 端加正电压 – > 形成浮动栅 – > S 与 D 不导通为 “0”

D 端不加正电压 – > 不形成浮动栅 – > S 与 D 导通为 “1”

如果需要进行重新写入的话,就需要驱散浮动栅,浮动栅的驱散可以直接使用紫外线照射。

4. EEPROM(多次性编程)

EEPROM 是指带电可擦可编程只读存储器,是一种掉电后数据不丢失的存储芯片。EEPROM 可以在电脑上或专用设备上擦除已有信息,重新编程,一般用在即插即用。

5. Flash Memory(闪速型存储器)

快闪存储器(英语:flash memory),是一种电子式可清除程序化只读存储器的形式,允许在操作中被多次擦或写的存储器。这种科技主要用于一般性数据存储,以及在计算机与其他数字产品间交换传输数据,如储存卡与U盘。闪存是一种特殊的、以宏块抹写的 EPROM。早期的闪存进行一次抹除,就会清除掉整颗芯片上的数据。

4.2.5 存储器与CPU的连接

1. 存储容器的扩展

由于单片存储芯片的容量总是有限的,很难满足实际的需要,因此,必须将若干存储芯片连在一起才能组成足够容量的存储器,这就叫存储容量的扩展,通常有位扩展和字扩展。

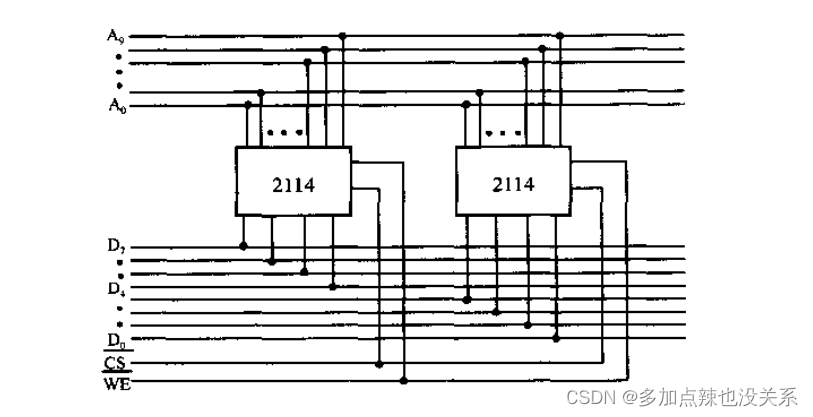

(1)位扩展

位扩展是指增加存储字长,如 2 片 1K×4 位的芯片,可组成 1K×8 位的存储器。

又如,将 8 片 16K×1 位的存储芯片连接,可组成一个 16K×8 位的存储器。

(2)字扩展

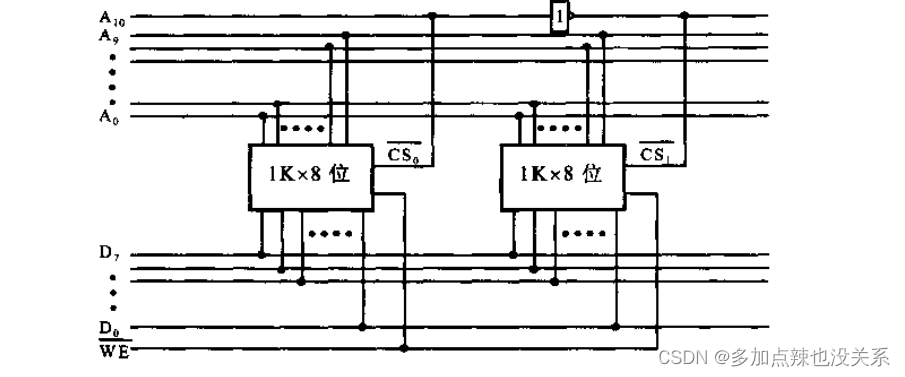

字扩展是指增加存储器字的数量,如用 2 片 1K×8 位的存储芯片,可组成一个 2K×8 位的存储器。

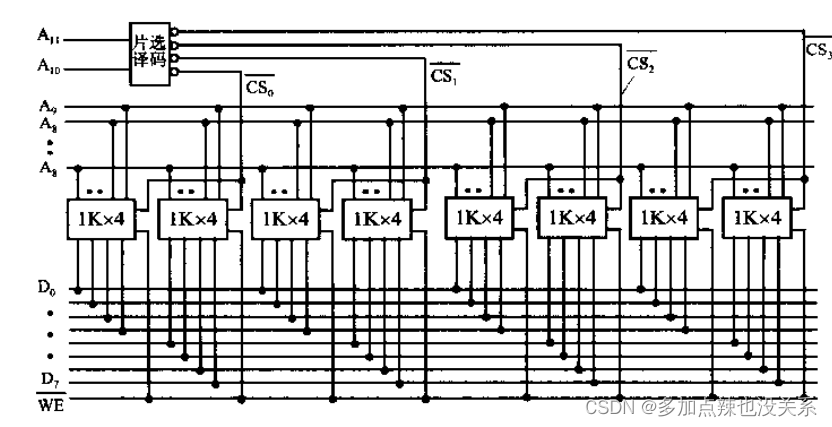

(3)字、位扩展

字、位扩展是指既增加存储字的数量,又增加存储字长,如用 8 片 1K×4 位的芯片组成 4K×8 位的存储器。

2. 存储器与 CPU 的连接

- 地址线的连接

- 存储芯片容量不同,其地址线数也不同,而 CPU 的地址线数往往比存储芯片的地址线数要多。通常总是将 CPU 地址线的低位与存储芯片的地址线相连。CPU 地址线的高位或作存储芯片扩充时用,或作其他用法,如作为片选信号等。

- 数据线的连接

- CPU 的数据线数与存储芯片的数据线数也不一定相等,此时,必须对存储芯片扩位,使其数据位数与 CPU 的数据线数相等。

- 读/写命令线的连接

- CPU 读/写命令线一般可直接与存储芯片的读/写控制端相连,通常高电平为读,低电平为写。

- 片选线的连接

- 片选信号的连接是 CPU 与存储芯片正确工作的关键,由于存储器是由许多存储芯片叠加组成的,哪一片被选中完全取决于该存储芯片的片选控制端 CS‾\overline{\text{CS}}CS 是否能接收到来自 CPU 的片选有效信号。片选有效信号与 CPU 的访存控制信号 MREQ‾\overline{\text{MREQ}}MREQ(低电平有效)和地址有关。

- 合理选择存储芯片

- 合理选择存储芯片主要是指存储芯片类型(RAM 或 ROM)和数量的选择。通常选用 ROM 存放系统程序、标准子程序和各类常数等。RAM 则是为用户编程而设置的。此外,在考虑芯片数量时,要尽量使连线简单方便。

- 其他

- 比如时序的配合问题、速度问题、负载匹配问题等等。

4.2.6 存储器的校验

- 为什么要对存储器中的信息进行校验?

- 为了能够校验出信息是否正确,如何进行编码?

- 纠错或检错能力与什么因素有关?

- 校验出信息出错后是如何进行纠错的?

- 你还知道哪些容错编码?原理是什么?

在计算机运行过程中,由于种种原因致使数据在存储过程中可能出现差错,所以需要对存储器中的信息进行校验。

编码的检测能力和纠错能力和什么有关?

任意两组合法代码之间二进制位的最少差异数,也就是编码的最小距离。

纠错理论公式:

L - 1 = D + C(PS:D>=C)

- L — 编码的最小距离

- D — 检测错误的位数

- C — 纠正错误的位数

1. 海明码的组成

海明码又称汉明码,是由 Richard Hanming 于 1950 年提出的,它具有一位纠错能力。

- 海明码采用奇偶校验

- 海明码采用分组校验

- 海明码的分组是一种非划分方式,分为 3 组,每组有 1 位校验位,共包括 4 位数据位

| P3P2P1 | 校验结果 |

|---|---|

| 000 | 无差错 |

| 001 | P1 出错 |

| 101 | P5 出错 |

| 110 | P6 出错 |

| 111 | P7 出错 |

校验位是只对一组数据进行校验,不会和其它组共有位置,所以海明码的校验位在 P1、P2、P4 ,也就是 2x 位上。

组成海明码的三要素:

- 海明码的组成需添加 2k>= n + k + 1 位检测位

- 检测位的位置在 2i( i = 0,1,2,3,…)

- 检测位的取值与该位所在的检测 “小组” 承担的奇偶校验任务有关

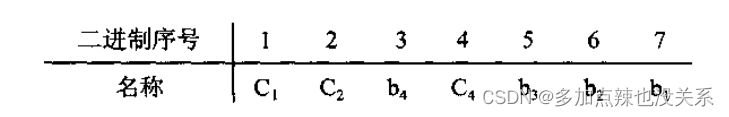

举例:求 0101 按 “偶校验” 配置海明码

解:因为 n = 4 ,根据 2k>= n + k + 1 可得 k = 3

汉明码排序如下:

C1 对应 P1、P3、P5、P7 所在的组,P3、P5、P7 中有1个0和2个1,由于是偶校验,所以C1 为 0,同理可得 C2 为1,C4 为 0

即 0101 的汉明码为 0100101

2. 海明码的纠错

海明码的纠错过程实际上是对传送后的海明码形成新的检测位 Pi( i = 0,1,2,4,8,…),根据 Pi 的状态,便可直接指出错误的位置。Pi 的状态是由原检测位 Ci 及其所在小组内 “1” 的个数确定的。

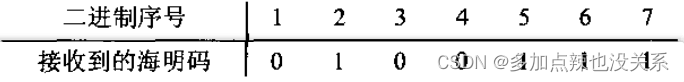

举例:已知接收到的汉明码为 0100111,按偶配原则配置,原本传送的信息是什么?

则新的检测位为

即 P4P2P1 = 110

第 6 位出错,可纠正为 0100101

故要求传送的信息为 0101

PS:这一块东西可能有点难以理解,可参见博客:《汉明码(海明码)》通俗易懂,或者是看:B站:计算机组成原理(唐朔飞)-P36~P38

4.2.7 提高访存速度的措施

在计算机的发展过程中,CPU 速度的提高是非常快的,但是存储器速度的提升却非常的有限,两者之间的差在逐渐的增大,CPU 执行程序时所需要的指令、数据都来自于内存,运行结果也要保存到内存当中,如果存储器很慢,CPU 再快也无法提高整机的速度,这种现象在计算机结构领域称为存储墙,是目前影响计算机性能的主要因素之一。

为了解决此类问题,可通过以下几种方式去解决:

- 采用高速器件

- 采用层次结构 Cache-主存

- 调整主存结构

- 单体多字系统

- 多体并行系统

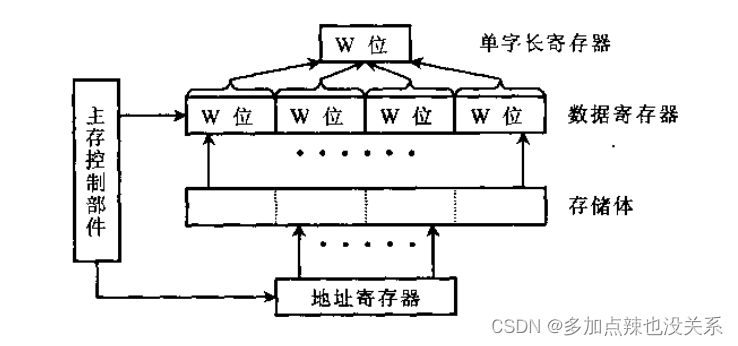

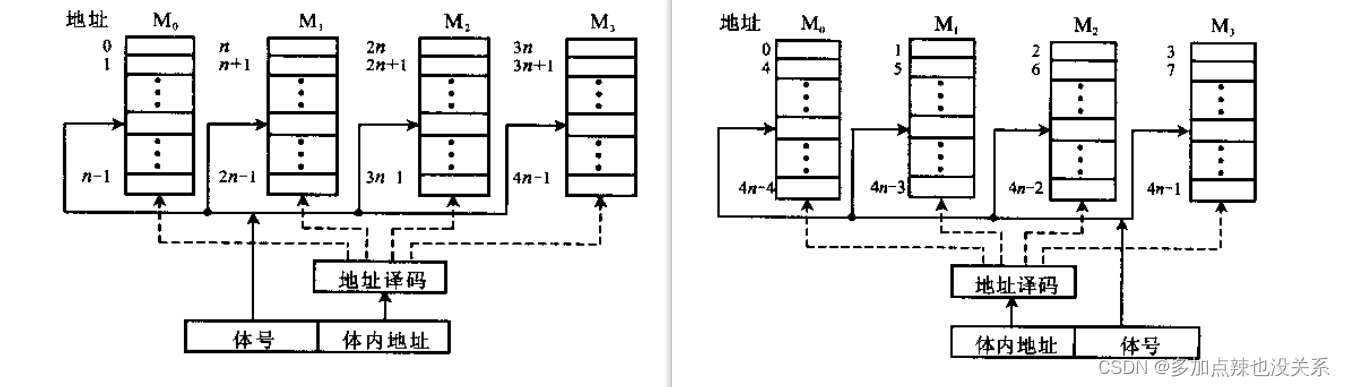

- 单体多字系统

4.3 高速缓冲存储器(Cache)

4.3.1 概述

高速缓冲存储器是存在于主存(DRAM)与CPU之间的一级存储器, 由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得多, 接近于CPU的速度。在计算机存储系统的层次结构中,是介于中央处理器和主存储器之间的高速小容量存储器。它和主存储器一起构成一级的存储器。高速缓冲存储器和主存储器之间信息的调度和传送是由硬件自动进行的。

程序访问的局部性原理:程序访问的局部性原理包括时间局部性和空间局部性。时间局部性是指在最近的未来要用到的信息,很可能是现在正在使用的信息,因为程序中存在循环。空间局部性是指在最近的未来要用到的信息,很可能与现在正在使用的信息在存储空间上是连续的,因为指令通常是顺序存放、顺序执行的,数据一般也是以向量、数组等形式簇聚地存储在一起的。

高速缓冲技术就是利用程序访问的局部性原理,把程序中正在使用的部分存放在一个高速的、容量较小的Cache 中,使 CPU 的访存操作大多针对 Cache 进行,从而大大提高程序的执行速度。

Cache 的工作原理:

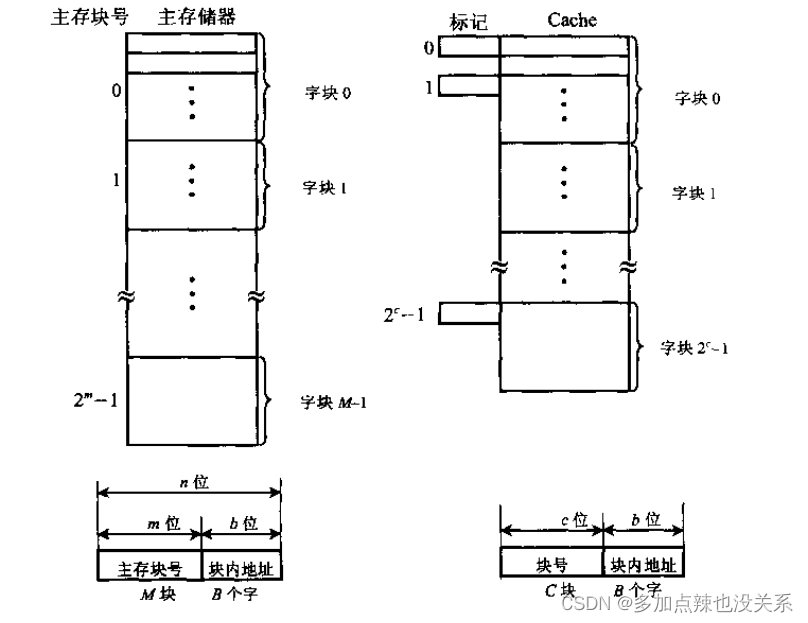

缓存块 C 远小于主存的块数 M,内存块和 Cache 块的大小是相同的,所以块内地址位数也是相同的,另外,一个块在内存和 Cache 之间进行传送的时候是整体进行传送,块内字节的顺序不会发生任何变化,即内存的块内地址部分和 Cache 的块内地址部分的指是完全相等的。Cache 上有一个标记,它标记的是主存块和 Cache 块之间的对应关系,如果一个主存块调用到 Cache 当中,就能将主存块号写到标记当中,将来 CPU 给出一个内存地址,它希望在 Cache 当中访问到这个数据,首先要确定这个块是否已经被送到 Cache 当中,就会拿给出地址的主存块号和 Cache 中的标记进行对比,如果和某一个标记正好相等并且 Cache 块是有效的,这个 Cache 块中就保存了需要在内存中访问的信息。

主存和缓存之间是按照块进行存储的,按块进行传送的、块的大小是相同的、块内地址也是完全相同的。

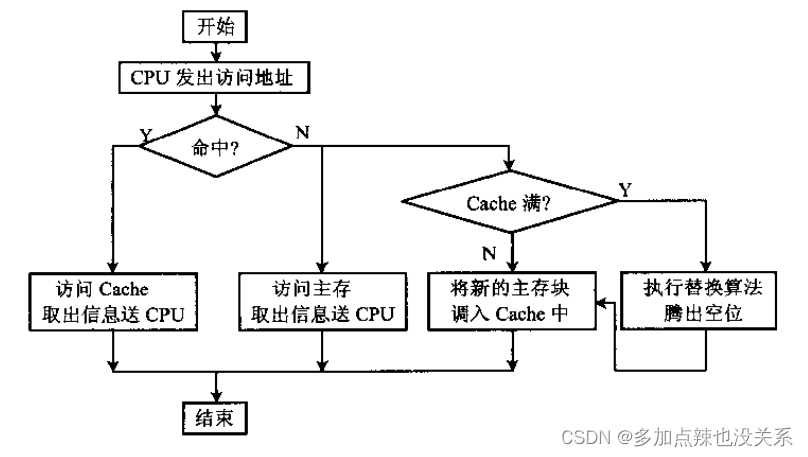

任何时刻都有一些主存块处于缓存块中。CPU 欲读取主存某字时,有两种可能;一种时所需要的数已在缓存中,即可直接访问 Cache;另一种事所需的数不在 Cache 内,此时需将该数所在的主存整个字块一次调入 Cache 种。第一种情况称为 CPU 访问 Cache 命中,第二种情况称 CPU 访问 Cache 不命中,通常用命中率来衡量 Cache 的效率,命中率是指 CPU 要访问的信息已在 Cache 内的比率,它是高速缓冲存储器最重要的技术指标,命中率与 Cache 的容量与块长有关,一般而言,Cache 容量越大,其 CPU 的命中率就越高。

块长取一个存取周期内从主存调出信息长度。

Cache - 主存系统的效率:效率 e 与 命中率 有关,e = (访问 Cache 的时间 / 平均访问时间) × 100%

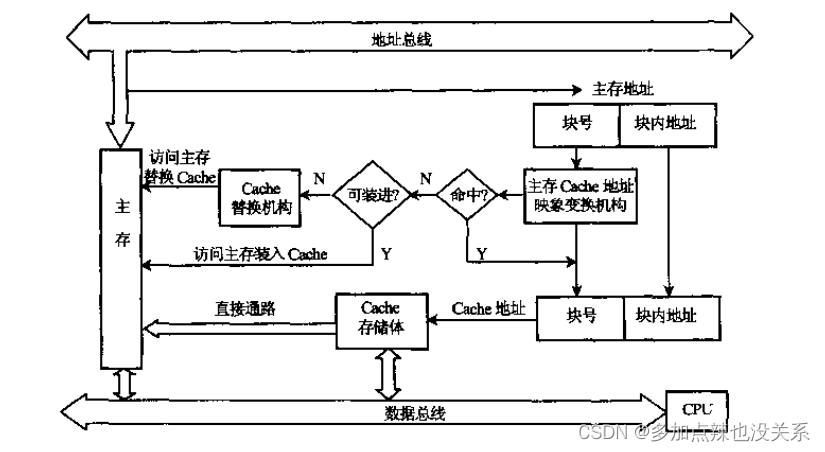

Cache 的基本结构:

高速缓冲存储器主要由三大部分组成:

- Cache 存储体:存放由主存调入的指令与数据块

- 地址转换部件:建立目录表以实现主存地址到缓存地址的转换

- 替换部件:在缓存已满时按一定策略进行数据块替换,并修改地址转换部件

Cache 的读操作:

Cache 写操作:

在对 Cache 块内写入信息的时候,必须与被映射象的主存块内的信息完全一致。通常有以下几种方法来保证 Cache 与主存内容保持一致性的问题。

- 写直达法

- 写操作时数据既写入 Cache 又写入主存

- 写操作时间就是访问主存的时间

- Cache 块退出时,不需要对主存执行写操作,更新策略比较容易实现

- 写回法

- 写操作时只把数据写入 Cache 而不写入主存

- 当 Cache 数据被替换出去时才写回主存

- 写操作时间就是访问 Cache 的时间

- Cache 块退出时,被替换的块需写回主存,增加了 Cache 的复杂性

Cache 的改进:

- (1)增加 Cache 的级数

片载(片内)缓存:单一缓存,缓存直接与 CPU 制作在同一个芯片内- 优点:① 外部总线的利用率高;② 存取速度快;③ 系统的整体效率高

- 缺点:容量不大,CPU 欲访问的信息可能不在缓存中,就会去访问主存,如果访问次数多了,就会影响整机的速度

片外缓存:两级缓存,在主存和片内缓存之间,再加一级缓存- 优点:由静态 RAM 组成,从片外缓存调入片内缓存的速度jjiu能提高,而 CPU 占用外部总线的时间就会大大下降,整机工作速度明显提高

- (2)统一缓存和分立缓存

统一缓存:是指指令和数据都存放在同一缓存内的 Cache分开缓存:是指指令和数据分别存放在两个缓存中,一个叫指令 Cache,一个叫数据 Cache- 两种缓存的选用主要考虑如下两个因素:

- 与主存结构有关

- 与机器对指令执行的控制方式有关

4.3.2 Cache — 主存地址映象

由主存地址映象到 Cache 地址称为地址映象,可分为:① 直接映象;② 全相联映象;③ 组相联映象;④ 段相联映象。

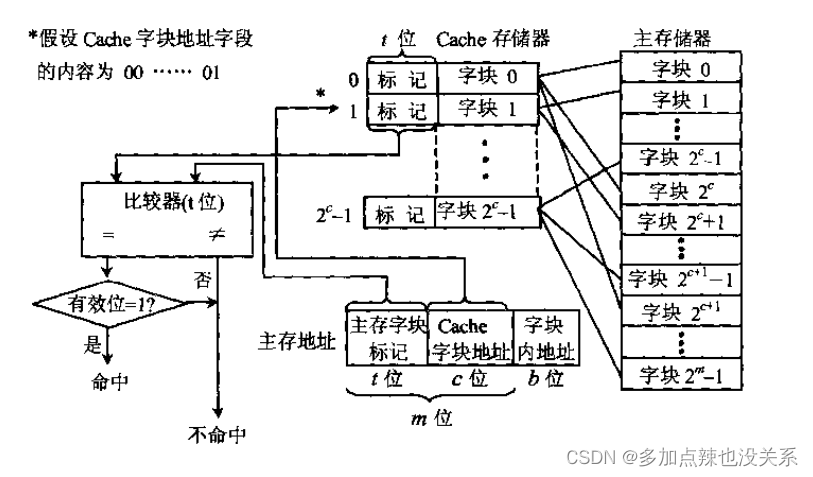

-

直接映射:是指主存当中任意一个给定的

块,它只能映射到,或者是只能装载到某一个指定的 Cache 块当中。

每个缓存块 i可以和若干个主存块对应,但是每个主存块 j只能和一个缓存块对应- 优点:实现简单,只需利用主存地址的某些位直接判断,即可确定所需字块是否在缓存中。

- 缺点:不够灵活,每个主存块只能固定地对应某个缓存块;当程序恰好要重复访问对应同一缓存位置的不同主存块时,就要不停地进行替换,从而降低了命中率。

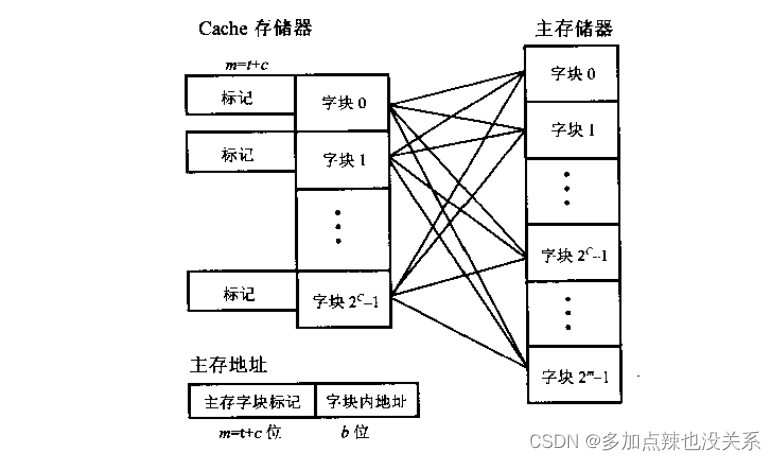

-

全相联映射:允许主存中每一字块映象到 Cache 中

任何一块位置上。

- 优点:方式灵活,命中率更高,缩小了块冲突率。

- 缺点:所需的逻辑电路甚多,成本较高,实际的 Cache 还要采用各种措施来减少地址的比较次数。

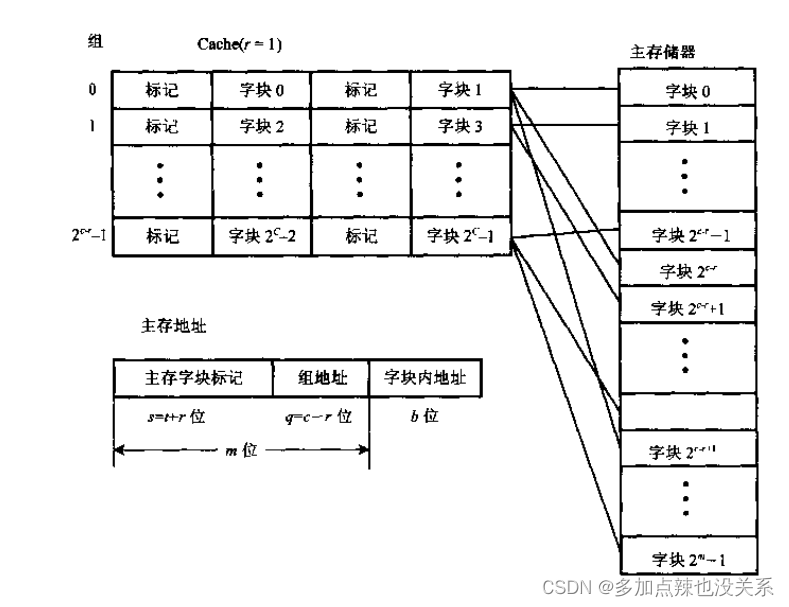

-

组相联映射:是对直接映象和全相联映象的一种折衷。

某一主存块 j按模Q映射到缓存的第i 组中的任一块

-

段相联映射:是直接映象和全相联映象两者结合的又一种方式。它是将主存和 Cache 都分成若干段,且使它们每段都包含的块数相等,段之间采用全相联映象,段内块之间采用直接映象。

4.3.3 替换算法

当新的主存块需要调入 Cache 并且它的可用空间位置又被占满时,就产生了一个替换算法问题。

-

先进先出(FIFO)算法- FIFO 算法的原则总是将最先调入 Cache 的字块替换出来,它不需要随时记录各字块的使用情况,所以容易实现、开锁小。但其缺点是可能把一些需要经常使用的程序(如循环程序〉块也作为最早进入 Cache的块而被替换出去。

-

近期最少使用(LRU)算法- LRU算法是将近期最少使用的块替换出来。它需要随时记录Cache中各个字块的使用情况,以便确定哪个字块是近期最少使用的字块。LRU算法的平均命中率比FIFO高,尤其是当分组容量加大时(组相联映象〉更能提高LRU算法的命中率。

4.4 辅助存储器

4.4.1 概述

辅助存储器作为主存的后援设备,又称作外部存储器,简称外存,它与主存一起组成了存储器系统的 主存 --- 辅存层次,与主存相比,辅存具有容量大、速度慢、价格低、可脱机保持信息等特点,属 “非易失性” 存储器。

特点:不直接参与 CPU 交换信息

目前,广泛用于计算机系统的辅助存储器有硬磁盘、软磁盘、磁带、光盘等。前三种均属磁表面存储器。

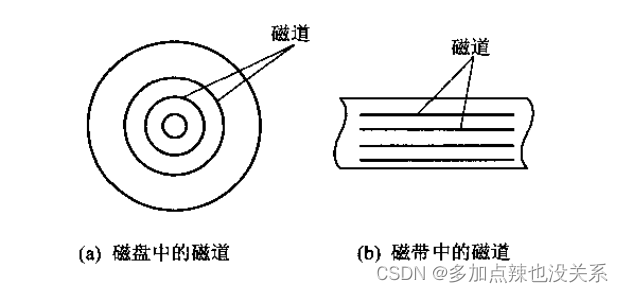

磁表面存储器是在不同形状(如盘状、带状等)的载体上,涂有磁性材料层,工作时,靠载磁体高速运动,由磁头在磁层上进行读写操作,信息被记录在磁层上,这些信息的轨迹就是磁道。

磁表面存储器的主要技术指标:

- (1)

记录密度:是指单位长度内所存储的二进制信息量。 - (2)

存储容量:是指外存能存储的二进制信息总数量,一般以位或字节为单位。 - (3)

平均寻址时间:分为两个部分,一个是磁头寻找到目标磁道的寻道时间,其二是磁头等待欲读写的磁道区段旋转到磁头下方所需要的等待时间。 - (4)

数据传输率:是指单位时间内磁表面存储器向主机传送数据的位数或字节数。 - (5)

误码率:是衡量磁表面存储器出错概率的参数,它等于从辅存出错时,出错信息位数和读出的总信息位数之比。

4.4.2 磁记录原理和记录方式

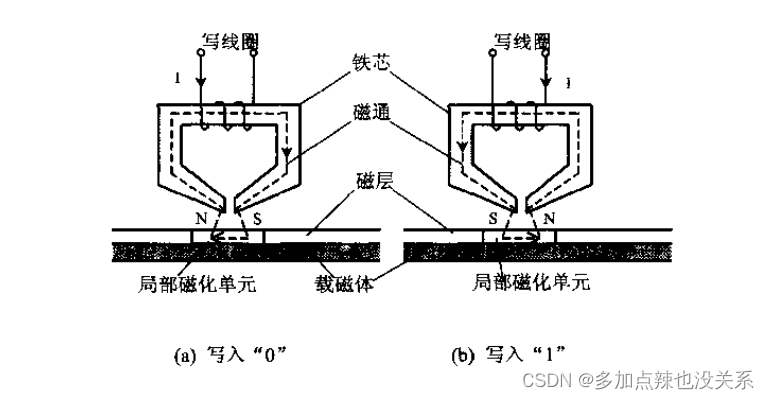

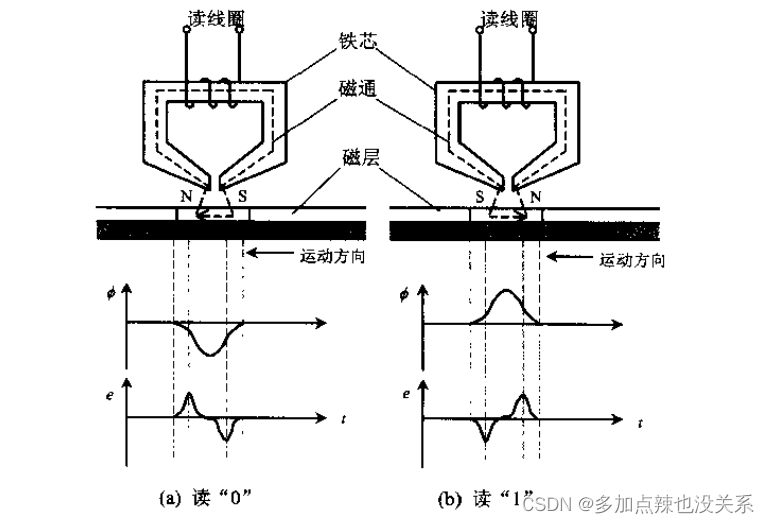

磁记录原理:

磁表面存储器通过磁头和记录介质的相对运动完成读写操作。

- 写操作:记录介质在磁头下方匀速通过,对写入线圈输入一定方向和大小的电流,使磁头导磁体磁化,产生一定方向和强度的磁场,根据写入驱动电流的不同方向,使磁层表面被磁化的极性方向不同,以区别记录 “0” 或 “1”。

- 读操作:记录介质在磁头下方匀速通过,磁头相对于一个个被读出的磁化单元作切割磁力线的运动,从而在磁头读线圈中产生感应电势,其方向正好和磁通的变化方向相反,由于原来磁化单元的剩磁通 ф 的方向不同,感应电势方向也不同,便可读出 “1” 或 “0” 两种不同信息。

磁表面存储器的记录方式:

- 归零制(RZ)

- 不归零制(NRZ)

- 见 “1” 就翻的不归零制(NRZ1)

- 调相制(PM)

- 调频制(FM)

- 改进调频制(MFM)

评价记录方式的主要指标为:① 编码效率;② 自同步能力

4.4.3 硬磁盘存储器

硬磁盘存储器的类型:

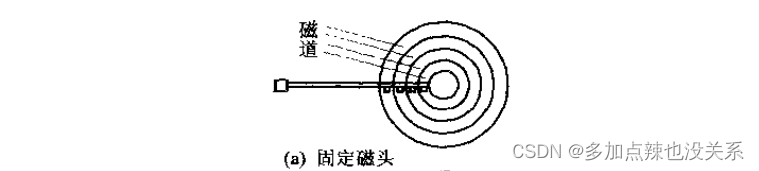

按照磁头是否固定可划分为:

- 固定磁头:磁头位置固定不动,磁盘上的每一个磁道都对应一个磁头,特点是省去了磁头沿盘片径向运动所需寻找磁道的时间,存取速度快,只要磁头进入工作状态即可进行读写操作。

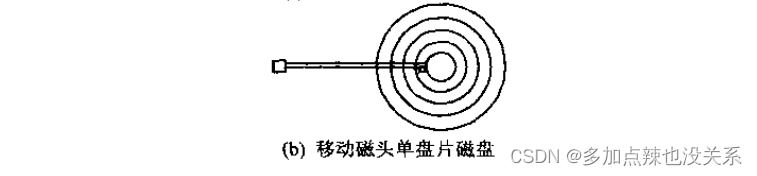

- 移动磁头:在存取数据时,磁头在盘面上作径向运动,这类存储器可以由一个盘片组成,也可由多个盘片装在一个同心主轴上,每个记录面各有一个磁头。

按硬盘盘片是否可更换分为:

- 可换盘磁盘存储器:是指盘片可以脱机保存。

- 固定盘磁盘存储器:是指磁盘不能从驱动器中取下,更换时要把整个 “头盘组合体” 一起更换。

硬磁盘存储器的结构:

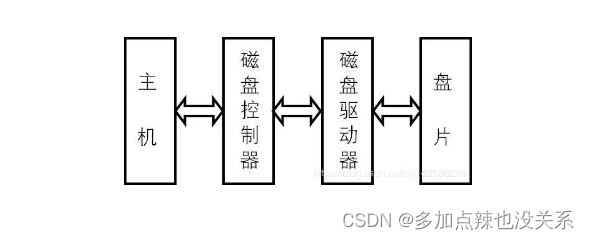

硬磁盘存储器是由磁盘驱动器、磁盘控制器和盘片组成。

硬磁盘存储器的发展方向:

- 半导体盘

- 提高磁盘记录密度

- 提高传输率和缩短存取时间

- 采用磁盘阵列 RAID

硬磁盘的磁道记录格式:

- 定长记录格式

- 不定长记录格式

4.4.4 软磁盘存储器

软磁盘存储器的盘片是用类似塑料薄膜唱片的柔性材料制成的,简称软盘。

与硬盘的比较:

| 硬盘 | 软盘 | |

|---|---|---|

| 速度 | 高 | 低 |

| 磁头 | 固定、活动 | 活动 |

| 读写过程 | 靠浮动磁头读写,磁头不接触盘片 | 直接接触盘片进行读写 |

| 盘片 | 固定盘、盘组大部分不可换 | 可换盘片 |

| 价格 | 高 | 低 |

| 环境 | 苛刻 | 要求不苛刻 |

4.4.5 光盘存储器

磁带存储器也属磁表面存储器,其记录原理方式与磁盘存储器是相同的。从存取方式来看,磁盘存储器属于直接存取设备,而磁带存储器必须按顺序进行存取,既磁带上的文件是按磁带头顺序存放的。由于磁带容量比较大,位价格也比磁盘低,格式统一便于互换,因此仍是一种用于脱机存储的后备存储器。

磁带存储器是由磁带和磁带机两部分组成。

4.4.6 循环冗余校验码(CRC码)

磁表面存储器由于磁介质表面的缺陷、尘埃等原因,致使出现多个错误码。CRC (Cyclic Redundancy Check)码可以发现并纠正信息在存储或传送过程中连续出现的多位错误代码。因此 CRC校验码在磁介质存储器和计算机之间通信方面得到广泛应用。

4.4.7 光盘存储器

光盘存储器采用光存储技术,利用激光写入和读出。

- 第一代光存技术 — 采用非磁性介质 — 不可擦写

- 第二代光存技术 — 采用磁性介质 — 可擦写

光盘的存储原理:

光盘存储器利用激光束在记录表面上存储信息,根据激光束和反射光的强弱不同,可实现信息的读写。

- 只读型光盘(CD-ROM)和 只写一次型光盘(WORM) —

热作用(物理或化学变化) - 可擦写型光盘 —

热磁效应

上篇:第三章:系统总线

相关文章:

计算机组成原理|第四章(笔记)

目录第四章 存储器4.1 概述4.1.1 存储器分类4.1.2 存储器的层次结构4.2 主存储器4.2.1 概述4.2.2 半导体存储芯片简介4.2.3 随机存取存储器(RAM)4.2.4 只读存储器(ROM)4.2.5 存储器与CPU的连接4.2.6 存储器的校验4.2.7 提高访存速…...

【Unity3D-BUG记录】Unity3D中出现“动画片段必须标记为Legacy的警告”消除方法

推荐阅读 CSDN主页GitHub开源地址Unity3D插件分享简书地址我的个人博客 大家好,我是佛系工程师☆恬静的小魔龙☆,不定时更新Unity开发技巧,觉得有用记得一键三连哦。 一、前言 在开发中可能会遇到下面的警告: The AnimationClip…...

)

Spring Bean的定义(含创建Bean的三种方式)

🏆 文章目标:复习和理解下Spring Bean的定义 🍀 Spring Bean的定义(含创建Bean的三种方式) ✅ 创作者:Jay… 🎉 个人主页:Jay的个人主页 🍁 展望:若本篇讲解内…...

vue的路由-vue router(一)

vue的路由-vue router一、路由的基本使用HTMLrouter-linkrouter-viewJavaScript二、带参数的动态路由匹配三、嵌套路由四. 编程式导航导航到不同的位置替换当前位置横跨历史篡改历史五. 命名路由六. 命名视图嵌套命名视图七. 重定向和别名重定向别名八. 将 props 传递给路由组件…...

DevOps流水线搭建-PHP版本

一、介绍流水线发布代码1、官网https://www.jenkins.io/zh2、kubesphere里的介绍https://kubesphere.io/zh/docs/v3.3/devops-user-guide/how-to-use/pipelines/choose-jenkins-agent/3、git仓库可以自己写点测试代码,提交,待会测试用https://gitee.com/…...

)

C语言之按位取反~(七十一)

计算机存储数据基本知识计算机中二进制数包括(正数和负数)是以补码形式存储。符号位:补码的最左侧首位是符号位,0表示正数,1表示负数。二进制有三种形式:原码、反码、补码。正数的补码和反码:是…...

C# 委托

Action 在 C# 中,Action 是一个预定义的委托类型,表示一个不带参数和返回值的方法。它的定义如下: public delegate void Action();Action 委托可以用于表示任何没有参数和返回值的方法。例如: // 定义一个不带参数和返回值的方…...

)

leetcode究极刷题笔记(11~15)

(11)盛最多水的容器(中等) 实现思路: 定义两个指针(a,b),分别指向数组的前后位置,如果此时a的值小于b的话,就将a右移一位,如果此时b指向的值小于…...

【C语言】一篇带你从零了解 枚举

文章目录什么是枚举枚举类型的定义枚举的优点枚举的使用什么是枚举 枚举是 C 语言中的一种基本数据类型 可以让数据更简洁,更易读。 枚举顾名思义就是 一 一 列举。 把可能的取值 一 一列举。 比如我们现实生活中: 一周的星期一到星期日是有限的7天&…...

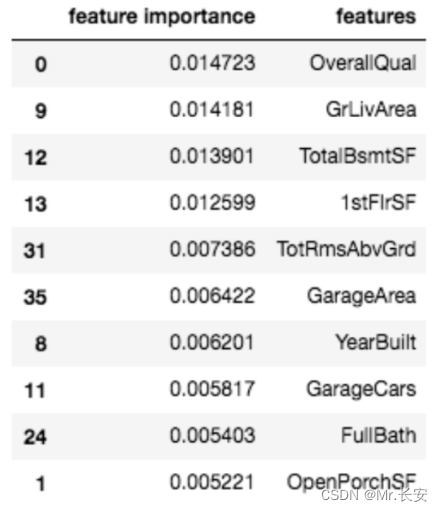

用Pytorch搭建一个房价预测模型

本文参加新星计划人工智能(Pytorch)赛道:https://bbs.csdn.net/topics/613989052 目录 一、项目介绍 二、准备工作 三、实验过程 3.1数据预处理 3.2拆分数据集 3.3构建PyTorch模型 3.3.1.数据转换 3.3.2定义模型架构 3.3.3定义损失准则和优化器 3.3.4创建…...

《Netty》从零开始学netty源码(十五)之ServerSocketChannel

在NioServerSocketChannel中调用newChannel方法创建java原生的channel,过程如下: ServerSocketChannel是一个抽象类,WEPollSelectorProvider调用openServerSocketChannel方法创建的是它的实现类ServerSocketChannelImpl,类结构如下…...

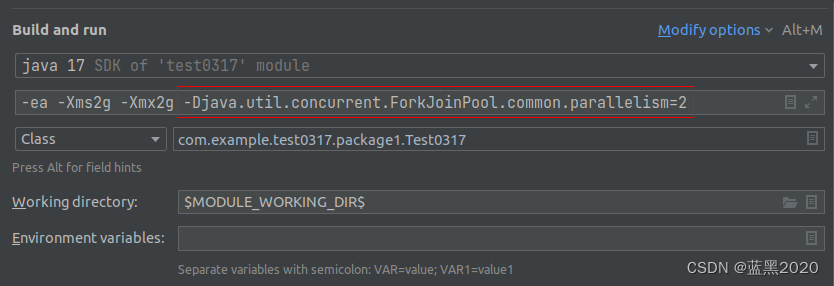

Java stream性能比较

环境 Ubuntu 22.04IntelliJ IDEA 2022.1.3JDK 17CPU:8核 ➜ ~ cat /proc/cpuinfo | egrep -ie physical id|cpu cores physical id : 0 cpu cores : 1 physical id : 2 cpu cores : 1 physical id : 4 cpu cores : 1 physical id : 6 cpu cores : 1 physical id …...

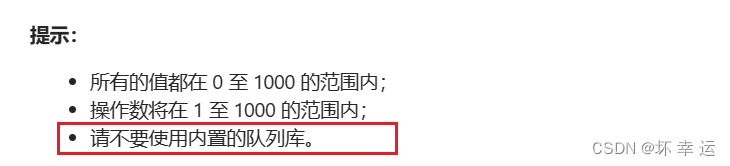

【数据结构与算法】设计循环队列

文章目录👑前言如何设计循环队列设计循环队列整体的代码📯写在最后👑前言 🚩前面我们 用队列实现了一个栈 ,用栈实现了一个队列 ,相信大家随随便便轻松拿捏,而本章将带大家上点难度,…...

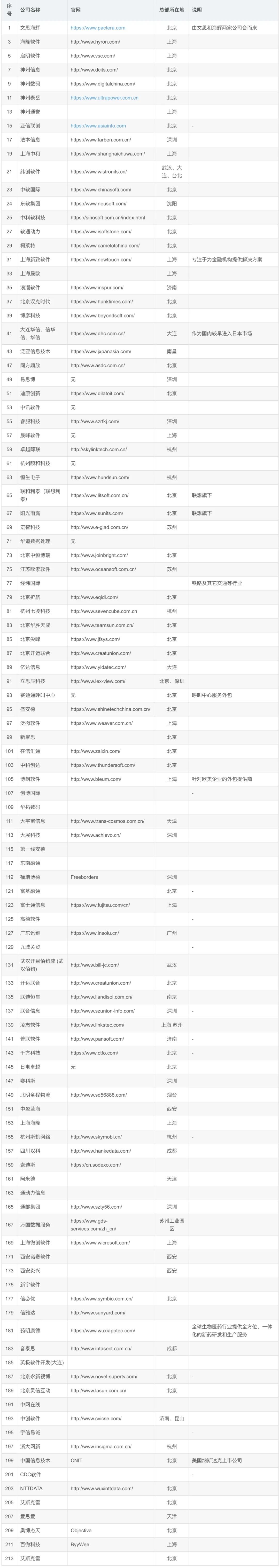

最新版!国内IT软件外包公司汇总~

金三银四已经过去一半,再过几个月又将迎来毕业季,大家有没有找到心仪的工作机会呀?有很多同学说今年的金三银四似乎不存在了。小李:今年的金三银四变成了铜三铁四,不断地投递又不断地造拒。小王:大量已读不…...

MySQL的COUNT语句,竟然都能被面试官虐的这么惨!?

关于数据库中行数统计,无论是MySQL还是Oracle,都有一个函数可以使用,那就是COUNT 但是,就是这个常用的COUNT函数,却暗藏着很多玄机,尤其是在面试的时候,一不小心就会被虐。不信的话请尝试回答下…...

数位DP 详解及其案例实战 [模板+技巧+案例]

零. 案例引入 1.案例引入 leetcode233. 数字 1 的个数 给定一个整数 n,计算所有小于等于 n 的非负整数中数字 1 出现的个数。 输入:n 13 输出:6 2.暴力解 对于上述的案例,暴力解肯定是可行的,但时间复杂度较高,对…...

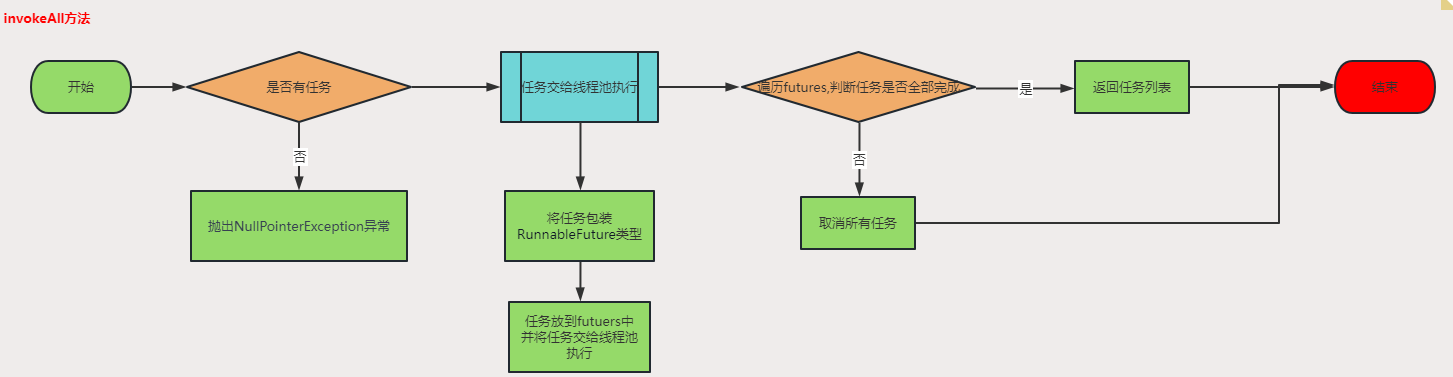

并发编程(六)—AbstractExecutorService源码分析

一、AbstractExecutorService简介AbstractExecutorService是一个抽象类,实现了ExecutorService接口,提供了线程池的基本实现。它是Java Executor框架的核心类,提供了线程池的基本操作,如提交任务、管理线程池、执行任务等。自定义…...

015行为型-职责链模式

目录定义标准模式实现:职责链变体使用链表实现使用数组实现应用场景日志输出spring过滤器spirng 拦截器mybatis动态sql定义 责链模式是一种设计模式,其目的是使多个对象能够处理同一请求,但是并不知道下一个处理请求的对象是谁。它能够解耦请…...

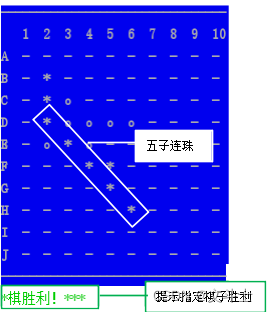

python例程:五子棋(控制台版)程序

目录《五子棋(控制台版)》程序使用说明程序示例代码可执行程序及源码下载路径《五子棋(控制台版)》程序使用说明 在PyCharm中运行《五子棋(控制台版)》即可进入如图1所示的系统主界面。 图1 游戏主界面 具…...

leveldb的Compaction线程

个人随笔 (Owed by: 春夜喜雨 http://blog.csdn.net/chunyexiyu) 1. leveldb的Compaction全局线程 在leveldb中,有一个全局的后台线程BGThread,用于数据库的MinorCompact与MajorCompact。 重点关注“全局线程”: 这个标识着无论一个进程打开…...

GPEN快速上手教程:手机自拍模糊修复,30秒获取高清证件照

GPEN快速上手教程:手机自拍模糊修复,30秒获取高清证件照 你是不是也遇到过这种情况:急着要用证件照,翻遍手机相册却发现每张自拍都模糊不清?要么是光线太暗,要么是手抖拍糊了,要么就是像素太低…...

)

GESP三级语法知识(六、string 入门与基础操作)

🌟 第一课:《string 入门与基础操作》🏰 第一章:string 是什么?(升级版小火车)1、🎯 故事以前我们用的是:👉 char数组 小火车 🚂(要自…...

中科蓝讯AB565X蓝牙耳机通话电流音、回声、杂音?手把手教你用PC工具调通它

中科蓝讯AB565X蓝牙耳机通话问题全解析:从硬件排查到参数调优实战指南 当你手握一款基于中科蓝讯AB565X芯片的蓝牙耳机样机,却在通话测试中遭遇电流音、回声和杂音时,那种挫败感我深有体会。作为深耕音频调试领域多年的工程师,我经…...

深入解析dlopen:动态库加载的机制与实践

1. 动态库加载的两种方式 在C/C开发中,动态库(Dynamic Library)的使用是提升代码复用性和灵活性的重要手段。动态库加载主要分为隐式链接和显式链接两种方式,它们各有特点,适用于不同场景。 隐式链接是最常见的方式&am…...

2026年零基础部署 OpenClaw 快速接入api图文步骤流程

OpenClaw怎么集成?2026年阿里云新手3分钟安装喂奶级流程。本文面向零基础用户,完整说明在轻量服务器与本地Windows11、macOS、Linux系统中部署OpenClaw(Clawdbot)的流程,包含环境配置、服务启动、Skills集成、阿里云百…...

Polars 2.0大规模清洗性能翻倍的7个底层优化技巧:基于真实金融风控流水线压测数据

第一章:Polars 2.0大规模数据清洗性能跃迁的工程意义Polars 2.0 的发布标志着 Rust 原生 DataFrame 库在工程落地层面实现关键突破——其基于 Arrow 2.0 和全新查询优化器(QOv2)重构的执行引擎,将典型 ETL 清洗任务的吞吐量提升达…...

猫抓插件:突破网页资源限制的媒体捕获解决方案

猫抓插件:突破网页资源限制的媒体捕获解决方案 【免费下载链接】cat-catch 猫抓 chrome资源嗅探扩展 项目地址: https://gitcode.com/GitHub_Trending/ca/cat-catch 在数字内容爆炸的时代,我们每天浏览的网页中蕴含着丰富的视频、音频和图片资源。…...

解锁B站视频下载:5个高效技巧让你轻松获取心仪内容

解锁B站视频下载:5个高效技巧让你轻松获取心仪内容 【免费下载链接】BilibiliDown (GUI-多平台支持) B站 哔哩哔哩 视频下载器。支持稍后再看、收藏夹、UP主视频批量下载|Bilibili Video Downloader 😳 项目地址: https://gitcode.com/gh_mirrors/bi/B…...

Blender3mfFormat插件:3MF文件处理全攻略

Blender3mfFormat插件:3MF文件处理全攻略 【免费下载链接】Blender3mfFormat Blender add-on to import/export 3MF files 项目地址: https://gitcode.com/gh_mirrors/bl/Blender3mfFormat 一、项目核心价值解析 Blender3mfFormat作为Blender的专业级3MF文件…...

如何快速完成黑苹果安装?OpCore Simplify终极简化指南

如何快速完成黑苹果安装?OpCore Simplify终极简化指南 【免费下载链接】OpCore-Simplify A tool designed to simplify the creation of OpenCore EFI 项目地址: https://gitcode.com/GitHub_Trending/op/OpCore-Simplify 厌倦了繁琐的黑苹果配置过程&#x…...

](https://img-blog.csdnimg.cn/79a005cac9b143a788f89e25c8f5707b.png)