DDRPHY数字IC后端设计实现系列专题之后端设计导入,IO Ring设计

本章详细分析和论述了 LPDDR3 物理层接口模块的布图和布局规划的设计和实 现过程,包括设计环境的建立,布图规划包括模块尺寸的确定,IO 单元、宏单元以及 特殊单元的摆放。由于布图规划中的电源规划环节较为重要, 影响芯片的布线资源和 供电稳定性等,所以在本章中单独讨论。对于布局阶段, 本章主要分析了布局的主要 几个阶段以及布局的结果。

3.1 建立环境

本次后端设计布局布线工具采用 Cadence 公司的 Innovus,在使用该工具进行后 端设计之前, 后端设计者需要将网表文件、时序约束、单元库等数据信息导入到

Innovus 的 EDI 环境。将数据信息导入该环境所使用的主要命令如下: Set init_gnd_net {GND_COREDDR_VSSQ}

Set init_lef_file {all.lef ANT.lef}

Set init_mmmc_file {viewDefinition.tcl}

Set init_pwr_net {VCC_CORE VCC_PUB_SW CORE_VDD

DDR_VDDQ[0] DDR_VDDQ[1] DDR_VDDQ[2] PLL_VDD}

Set init_top_cell {top}

Set init_verilog top.v

并将这些初始信息写入到 init.global 文件中,最后,将编写的 init.globals 导入 EDI。 其中通过 init_mmmc_file 编写多模式多管角(Multi Mode Multi Corner ,MMMC)环 境,用来导入时序信息和噪声库信息,简单范例如图 3.1 所示;

图 3.1 MMMC 环境范例

3.2 布图规划设计

当设计约束文件,门级网表文件,工艺库文件,技术文件等都准备完全,并且环 境建立好之后,就可以开始进行布图规划(Floorplan)了。随着集成电路进入深亚微 米级别,合理的布图规划成为数字后端中十分关键的一步,基本占用整个后端设计中 三分之一的时间。在布图规划阶段,需要确定芯片的尺寸,摆放宏单元,I/O 单元以 及特殊单元,合理的 blockage 的创建,以及确定 pin 的位置。需要说明的是, 布图规 划要结合后面的 congestion 以及 timing violation 等来进行调整与优化,是一个不断迭 代更新与改进的过程,一个好的布图规划很大程度的影响着设计收敛的难易以及后端 设计的时间。所以后端设计人员需要考虑和分析各个角度, 投入较多精力来进行布图 规划。下面是本次设计的详细的后端布局规划内容。

3.2.1 确定 DDR block 尺寸

芯片尺寸的大小决定了流片的成本。在一个 project 中,模块的尺寸一般由顶层 与模块共同决定。本次设计先从模块出发,再根据顶层的要求,最终确定 LPDDR3 物 理层接口模块的尺寸。

Block 中各个单元的数量与面积决定了它的形状与面积,本次设计中 DDRblock 包含的单元的数目与面积如下表所示。

Innovus 中,utilization 的计算公式如下:

utilization = Sleaf cell ÷ S可用 (3-1)

其中,utilization 表示利用率,Sleaf cell 表示 leaf cell 的面积,S 可用表示可用来放置 标准单元的而面积。leaf cell 包括标准单元与硬模块(hard macro),如果硬模块的布 局状态是 fixed ,则硬模块的面积不算在 Sleaf cel 跟 S 可用 内。为了统一计算,Innovus 将 以 site 来进行计算。本次设计中,选用 9track 的物理库,site 高度为 0.9μm ,宽度 0.14μm 。在一般的布图规划时,通常将 standard cell 的初始使用率设置在 60%左右。 考虑到本次 DDR 的高频性,故将标准单元的使用率设置在 50%左右即可。另外, 为 了标准单元的放置以及绕线的方便,将该模块设计为矩形。结合顶层的要求, 最终将 LPDDR3 物理层接口模块的尺寸设计为 1700μm×4795μm。

3.2.2 放置 IO 单元与宏单元

本次设计的 IO 单元是由 synopsys 公司提供的 IP ,所以 IO 单元部分位置及相对 位置的摆放需要符合 synopsys 的 DDR PHY 后端实现规格,。 下面分析一些主要检查 内容[40]。

(1)IO 单元邻接

IO 单元间的信号线,电源地线需要通过邻接才能成功传输。

(2)I/O 的信号功率比例

该项指的是一对 VDDQ/VSSQ 插槽对可以支持的信号插槽数,即为了能够使 IO 单元得到足够的功率进行工作。在此分析中,需要考虑电压降(IR Drop),电子迁移 (electro-migration ,EM)等多种影响。本次设计中,与 Data PHY 相关的 IO 选择信 号功率之比约 2 :1,该比率为大多数封装类型和外部存储器子系统提供了良好的电 气和时序性能。对于命令通道信号与电源的比率选择 3:1。因为数据通道的速率是字 节通道速率的 2 倍,所以命令通道有更高的信号功率比例。

(3)内部 VERF 隔离要求

pad 框架中需要内部 VERF 单元为 SSTL 输入提供比较参考,数据通道都需要一 个 PVREF 单元,每个 PVREF 单元内部可提供一个稳定的 VERF 电平值,又因为数 据字节通道和与命令字节通道的有不同的 PVREF 单元和MVREF 总线,所以需要通 过 PZQIO 单元作为两通道相关 IO 单元的边界来隔离 MVREF 总线。另外 PZQIO 单 元以 PZCTRL 的形式有自己的 VREF cell,所以将 PZQ 和 PZCTRL 单元相邻摆放并 且放在命令通道和数据字节通道之间进行隔离。PZQ 和 PZCTRL 单元切断 ZIOH 和 MVREF 总线,从而形成 3 个单独的 ZIOH / MVREF 岛。具体的摆放如图 3.2 所示:

(4)CKE 模式要求

当 DDR 处于 CKE 模式,即处于保持锁存使能状态的时候,为了节省在该模式下 的功率,关闭 DDR 接口其他信号的 VDDQ IO 电源,在后端实现中将与该模式信号 相关的 IO 单元放在一个信号孤岛(signal island)内。这时信号孤岛需要使电源总线 MVDDQ 与 VDDQ 电源隔离,并与其它掉电的 DDR 接口 IO 隔离,即在封装和 PCB 上隔离。VDDQ 隔离是通过在 CKE 信号孤岛周围使用两个 PFILL5_ISO 单元以及在 信号孤岛中两个VDDQ_ESD 单元来实现的,使用VDDQ_ESD 信号是为了实现VDDQ电源和 ESD 保护。另外在 CKE 信号孤岛中,需要 PVREF 单元来提供 IO 单元的驱动 强度,又由于 CKE 信号孤岛的 ZIOH 总线需要与其它IO 总线隔离,因此需要在 CKE 保留岛的边界上放置两个 PVSSQZB_ZQ 单元。CKE 信号孤岛的 IO 单元的摆放示意 如图 3.3 所示。

(5)VDDQ ESD 计算

IO 单元库具有两个不同的 PVDDQ 单元,PVDDQ_ESD 和 PVDDQ_CAP 。 PVDDQ_ESD 单元包含用于静电释放(Electro-Static Discharge ,ESD)保护的 ESD clamp,而 PVDDQ_CAP 没有 clamp,但在其空间内有额外的 VDDQ-VSSQ 去耦电容。

MVDDQ 网络的 ESD 要求表明,如果 clamp cell 仅在信号 IO 单元的一侧,则从 信号 IO 到 ESD clamp cell 的总线电阻必须小于 0.5 ohm;如果 clamp cell 位于信号 IO 单元的两侧,则 IO 到最近的 clamp cell 的总线电阻必须小于 1 ohm。根据 Synopsys DDR PHY 的规则,VDDQ 水平总线电阻 R_MVDDQ 为 0.04ohm。对于摆放在 IO 单 元块末端的信号 IO,到最近 clamp 的间隔= 0.5 / 0.04 = 12.5 或 12 个 IO cell 的距离。 对于摆放在 IO 单元块内部的信号 IO,到最近 clamp 的间隔= 1 / 0.04 = 25 个 cell 的距 离。

(6)PLL 供电

PLL 模块需要 VAA_PLLIO 单元供电。在本次设计中,一共使用了9 个 VAA_PLL IO 单元分别为数据字节通道和命令通道提供 PLL 电源,供电电压为 1.8v。

(7)数据字节通道 IO 单元摆放

由第二章可知,本次设计有 4 个数据字节通道,且每两个字节通道共用一个 PLL 模块。每个字节通道含有 8 位 DQ 数据信号和一个 DM 数据掩模信号,每个字节通道 的 DQS / DQS_b 信号实际上是字节通道的时钟,字节通道布局规划的目标是最大程 度地减少选通数据引脚偏移。理想情况下,应该将 DQS / DQS_b 选通信号放置在字 节通道的的中间,如图 3.4 所示:

8)地址命令字节通道的IO 摆放

CK/CK_b 信号是命令通道的时钟,地址命令字节通道的IO 摆放的目标是最大程 度地减少时钟到数据端口时钟偏斜。因此,CK/CK_b 时钟应放置在通道的中央,然后时钟对的每一侧分别放上地址和命令插槽。具体如图 3.5 所示:

9)PEND IO 单元

LPDDR3 物理层接口所需要的 SSTL IO 单元放置在连续的外围焊盘框架 (peripheral pad frame)中,并且字节通道和 AC 通道首尾相连,Pad 框的末端通过 PEND cell 结束。

10)确定宏单元的位置

每个 AC 和 DATX8 宏单元的两侧都有向 I/O 单元发送信号的引脚(包括标准引 脚和备用引脚),在设计中,使用最靠近 I/O 单元的 PHY 引脚。PLL 宏模块有两种单 元,一种单元用于管芯的南侧或北侧(PLL_NS),另一种单元用于管芯的东侧或西侧 (PLL_EW)。 PLL 始终与 AC 或 DATX8 邻接。图 3.6 显示了宏单元和不同组引脚 的位置。

PLL pllin_ *引脚是 PLL 的输入(pllin_x1 和 pllin_x4x2)时钟,并连接至内核。 PLLpllout_ *引脚是 PLL 的输出时钟(pllout_x1 和 pllout_x4x2),邻接到 AC 或 DATX8 输入(ctl_clk 和 ddr_clk)时钟。 AC 和 DATX8 上的核心引脚连接到核心 PUB 信号。 AC 和 DATX8 上的 NS I/O 引脚用于连接管芯北侧或南侧的 SDRAM 信号的 I/O。同 样,AC 和 DATX8 上的 EW I/O 引脚用于连接至芯片东侧或西侧 SDRAM 信号的 I / O。

本次设计中的 I/O 均为东西 EW 方向,所以本次宏单元摆放也选择东西方向的摆 放,如图 3.5 中左侧或右侧部分所示意。并且为了最大程度的减小 I/O 单元与宏单元 的路由距离,减少延时和串扰,必须保证同一个通道(数据字节通道和地址命令字节 通道)内的宏单元与 PHY 与IO 单元按顺序摆放。

按照以上分析的内容,并结合时序等的调整,确定了 I/O 单元与宏单元的摆放位 置如图 3.7 所示:

图 3.7 IO 与宏单元布局图

下次再继续更新DDRPHY floorplan和powerplan内容。

相关文章:

DDRPHY数字IC后端设计实现系列专题之后端设计导入,IO Ring设计

本章详细分析和论述了 LPDDR3 物理层接口模块的布图和布局规划的设计和实 现过程,包括设计环境的建立,布图规划包括模块尺寸的确定,IO 单元、宏单元以及 特殊单元的摆放。由于布图规划中的电源规划环节较为重要, 影响芯片的布线资…...

EDA --软件开发之路

之前一直在一家做数据处理的公司,从事c开发,公司业务稳定,项目有忙有闲,时而看下c,数据库,linux相关书籍,后面跳槽到了家eda公司,开始了一段eda开发之路。 eda 是 electric design …...

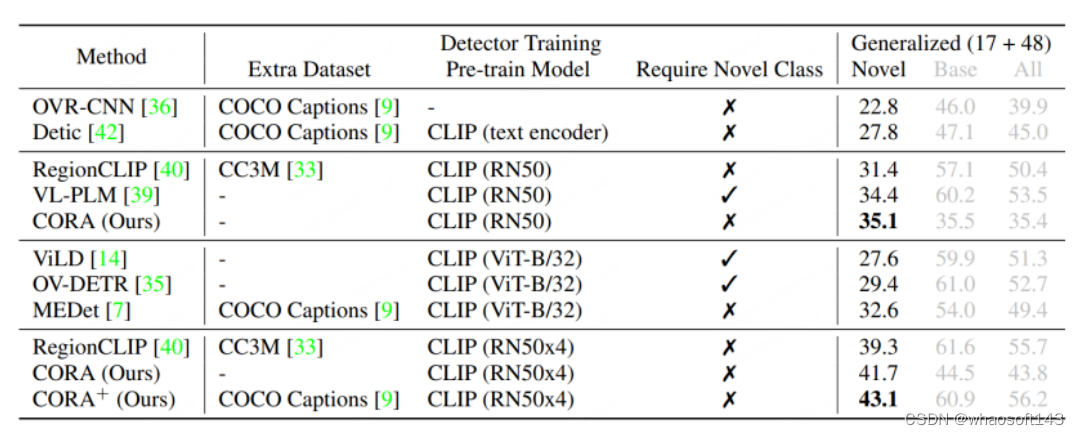

51c~目标检测~合集2

我自己的原文哦~ https://blog.51cto.com/whaosoft/12377509 一、总结 这里概述了基于深度学习的目标检测器的最新发展。同时,还提供了目标检测任务的基准数据集和评估指标的简要概述,以及在识别任务中使用的一些高性能基础架构,其还涵盖了…...

计算机低能儿从0刷leetcode | 33.搜索旋转排列数组

题目:33. 搜索旋转排序数组 思路:看到时间复杂度要求是O(log N)很容易想到二分查找,普通的二分查找我们已经掌握,本题中的数组可以看作由两个分别升序的数组拼成,在完全升序的部分中进行二分查找是容易的,…...

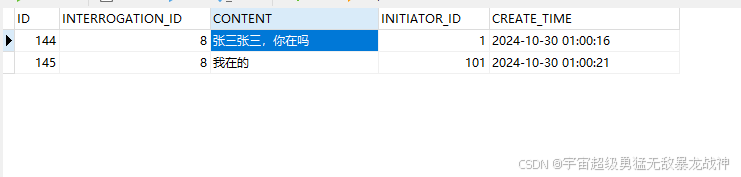

SpringBoot+VUE2完成WebSocket聊天(数据入库)

下载依赖 <!-- websocket --><dependency><groupId>org.springframework.boot</groupId><artifactId>spring-boot-starter-websocket</artifactId></dependency><!-- MybatisPlus --><dependency><groupId>com.ba…...

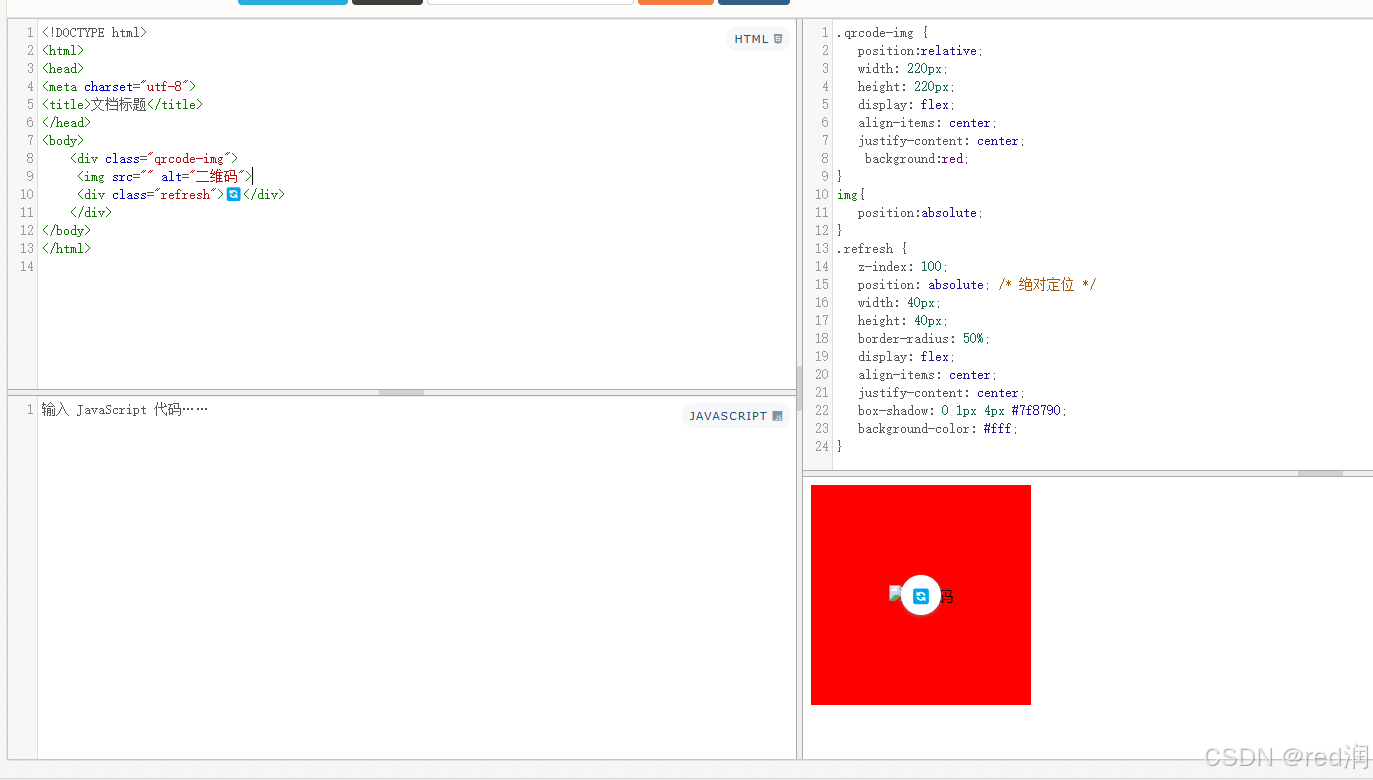

理解 CSS 中的绝对定位与 Flex 布局混用

理解 CSS 中的绝对定位与 Flex 布局混用 在现代网页设计中,CSS 布局技术如 flex 和绝对定位被广泛使用。然而,这两者结合使用时,可能会导致一些意想不到的布局问题。本文将探讨如何正确使用绝对定位元素,避免它们受到 flex 布局的…...

Redis 事务 问题

前言 相关系列 《Redis & 目录》《Redis & 事务 & 源码》《Redis & 事务 & 总结》《Redis & 事务 & 问题》 参考文献 《Redis事务详解》 Redis事务是什么? 标准的事务是指执行时具备原子性/一致性/隔离性/持久性的一系列操作。…...

Cpp学习手册-进阶学习

C标准库和C20新特性 C标准库概览: 核心库组件介绍: 容器: C 标准库提供了多种容器,它们各有特点,适用于不同的应用场景。 std::vector: vector:动态数组,支持快速随机访问。 #in…...

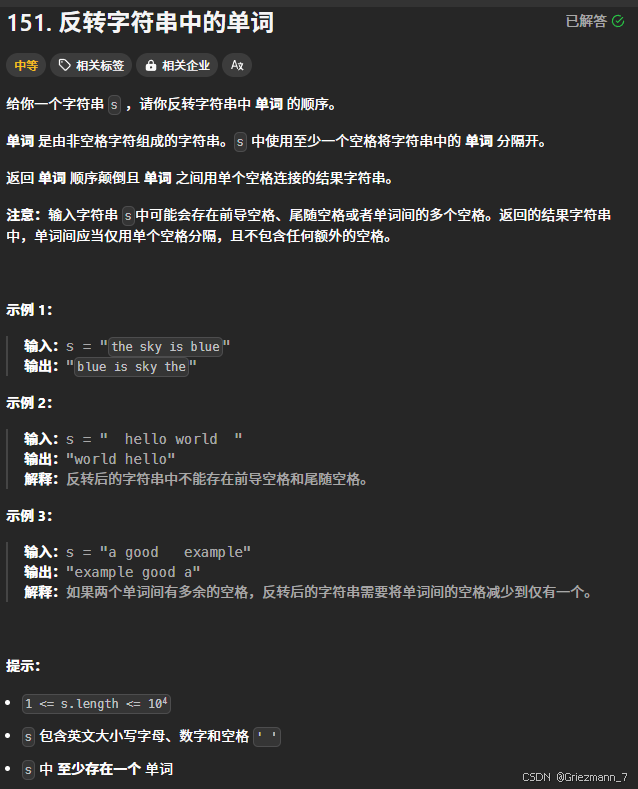

代码随想录-字符串-反转字符串中的单词

题目 题解 法一:纯粹为了做出本题,暴力解 没有技巧全是感情 class Solution {public String reverseWords(String s) {//首先去除首尾空格s s.trim();String[] strs s.split("\\s");StringBuilder sb new StringBuilder();//定义一个公共的字符反转…...

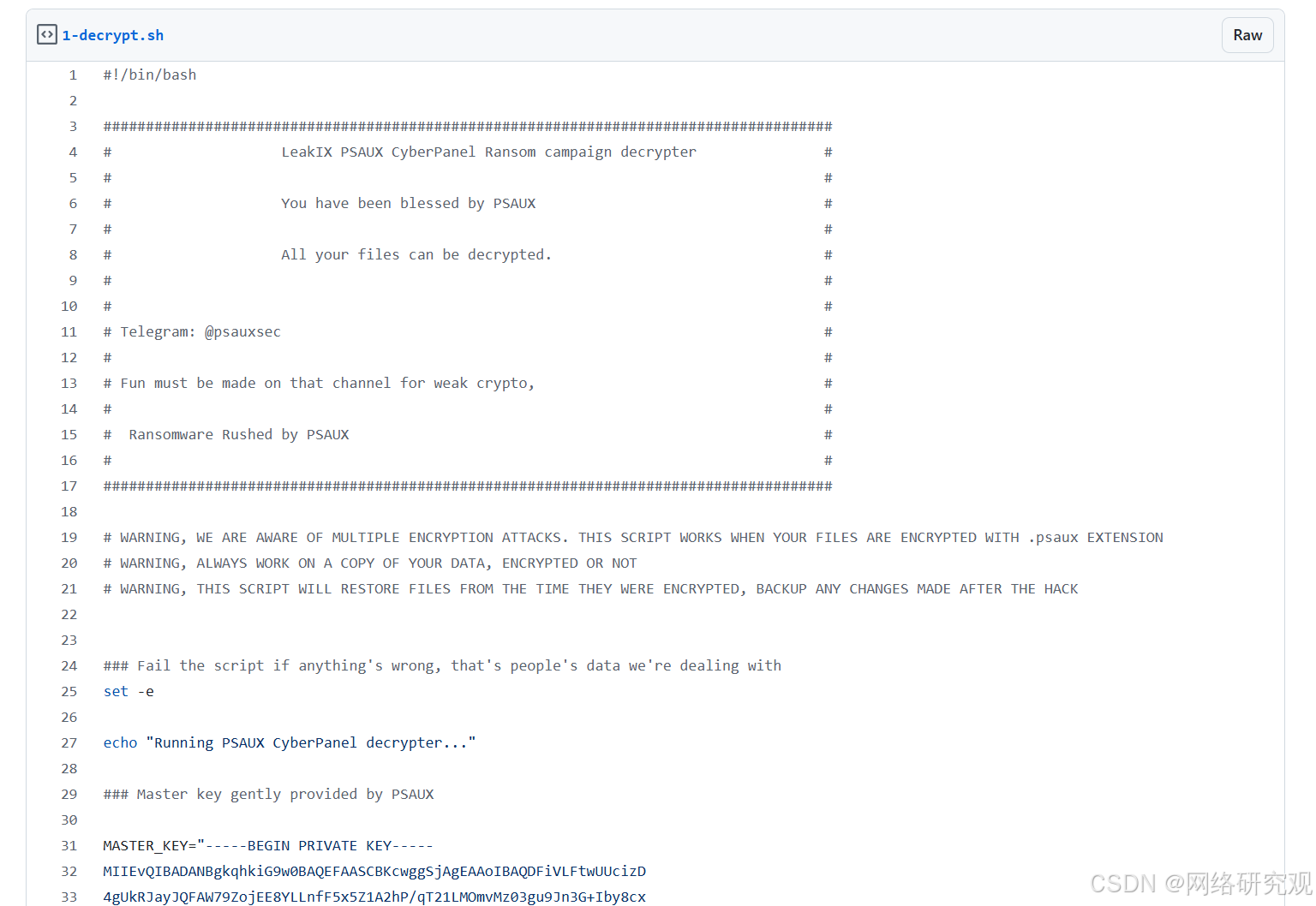

勒索软件通过易受攻击的 CyberPanel 实例攻击网络托管服务器

一个威胁行为者(或可能多个)使用 PSAUX 和其他勒索软件攻击了大约 22,000 个易受攻击的 CyberPanel 实例以及运行该实例的服务器上的加密文件。 PSAUX 赎金记录(来源:LeakIX) CyberPanel 漏洞 CyberPane…...

Open WebUI + openai API / vllm API ,实战部署教程

介绍Open WebUI + Ollama 的使用: https://www.dong-blog.fun/post/1796 介绍vllm 的使用:https://www.dong-blog.fun/post/1781 介绍 Ollama 的使用: https://www.dong-blog.fun/post/1797 本篇博客玩个花的,Open WebUI 本身可以兼容openai 的api, 那来尝试一下。 仅供…...

InsuranceclaimsController

目录 1、 InsuranceclaimsController 1.1、 保险理赔结算 1.2、 生成预约单号 1.3、 保存索赔表 InsuranceclaimsController using QXQPS.Models; using QXQPS.Vo; using System; using System.Collections; using System.Collections.Generic; using System.Li…...

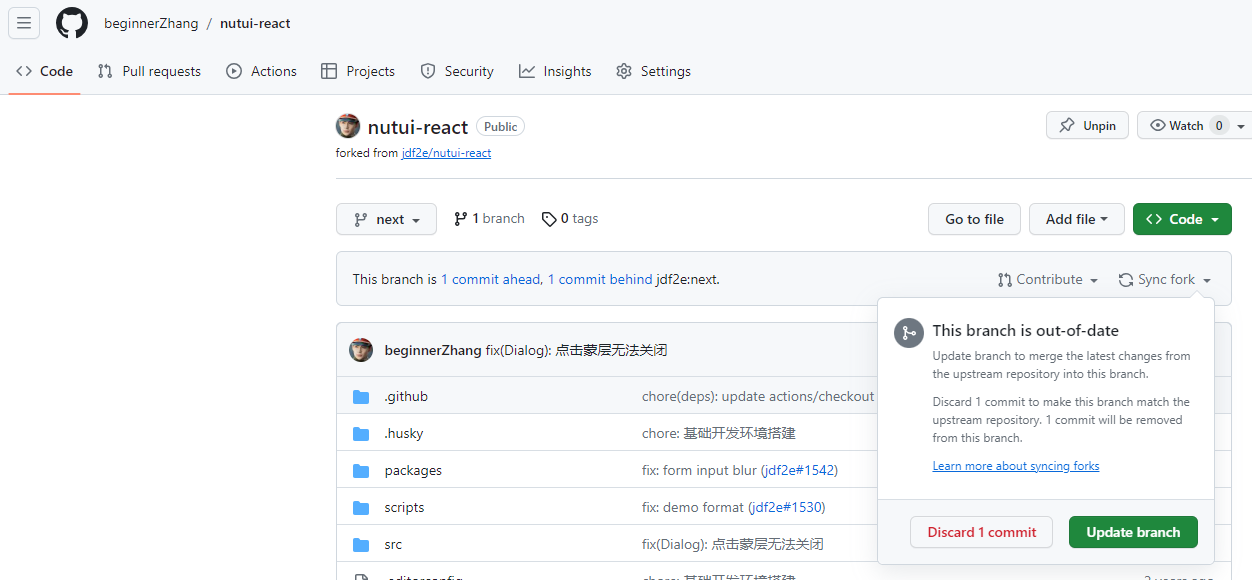

如何成为开源代码库Dify的contributor:解决issue并提交PR

前言 Dify 是一个开源的大语言模型(LLM)应用开发平台,它融合了后端即服务(Backend as Service)和LLMOps的理念,旨在简化和加速生成式AI应用的创建和部署。Dify提供了一个用户友好的界面和一系列强大的工具…...

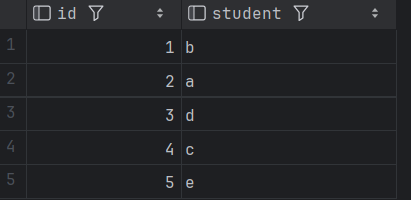

SQL进阶技巧:巧用异或运算解决经典换座位问题

目录 0 问题描述 1 数据准备 2 问题分析 2.1 什么是异或 2.2异或有什么特性? 2.3 异或应用 2.4 本问题采用异或SQL解决方案 3 小结 0 问题描述 表 seat中有2个字段id和student id 是该表的主键(唯一值)列,student表示学生姓名。 该表的每一行都表示学生的姓名和 ID。…...

进行监控)

【MySQL】 运维篇—数据库监控:使用MySQL内置工具(如SHOW命令、INFORMATION_SCHEMA)进行监控

随着应用程序的增长,数据库的性能和稳定性变得至关重要。监控数据库的状态和性能可以帮助数据库管理员(DBA)及时发现问题,进行故障排查,并优化数据库的运行效率。通过监控工具,DBA可以获取实时的性能指标、…...

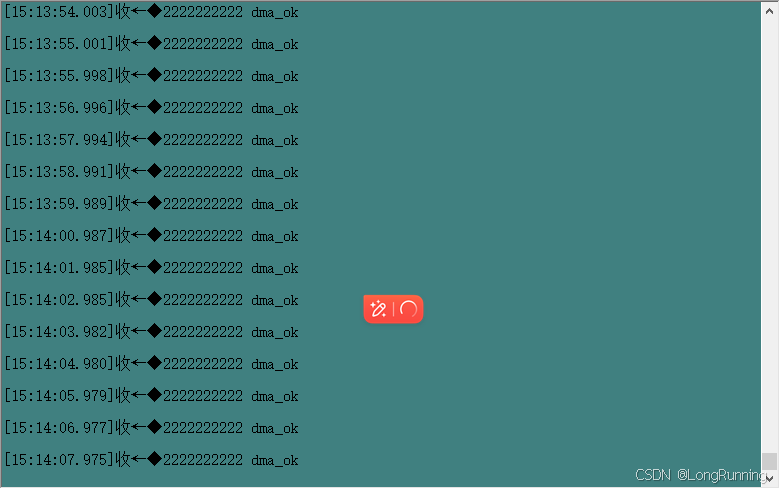

【温酒笔记】DMA

参考文档:野火STM32F103 1. Direct Memory Access-直接内存访问 DMA控制器独立于内核 是一个单独的外设 DMA1有7个通道DMA2有5个通道DMA有四个等级,非常高,高,中,低四个优先级如果优先等级相同,通道编号越…...

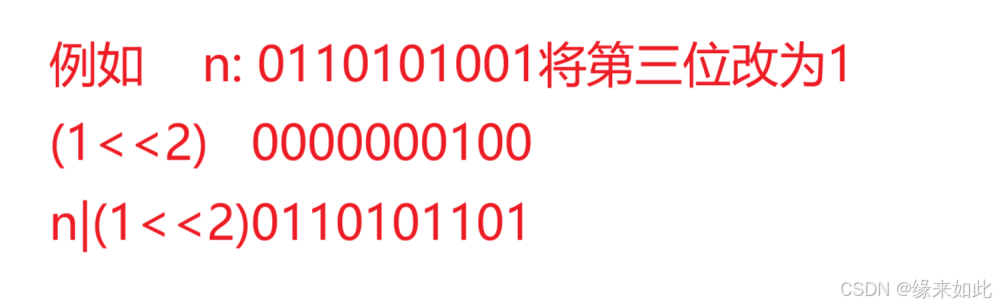

力扣判断字符是否唯一(位运算)

文章目录 给一个数n,判断它的二进制位中第x位是0还是1(从0开始计数)将一个数n的二进制位第X位修改为1(从0开始计数)将一个数n的二进制第x位修改为0(从0开始计数)提取一个数n二进制中最右侧的1去掉一个数n二进制表示中最右侧的1 今天我们通过判断字符是否唯一这个题来了解位运算…...

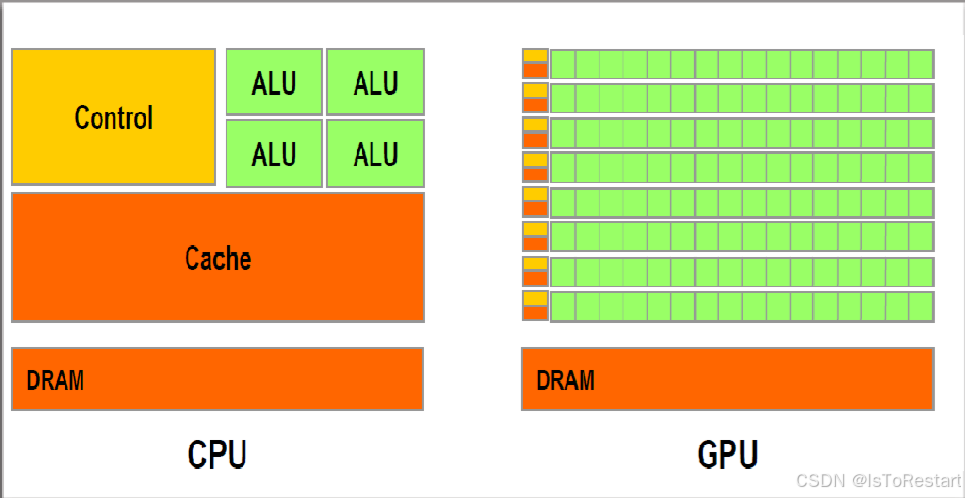

GPU和CPU区别?为什么挖矿、大模型都用GPU?

GPU(图形处理单元)和CPU(中央处理单元)是计算机中两种不同类型的处理器,它们在设计和功能上有很大的区别。 CPU是计算机的大脑,专门用于执行各种通用任务,如操作系统管理、数据处理、多任务处理等。它的架构设计旨在适应多种任务,…...

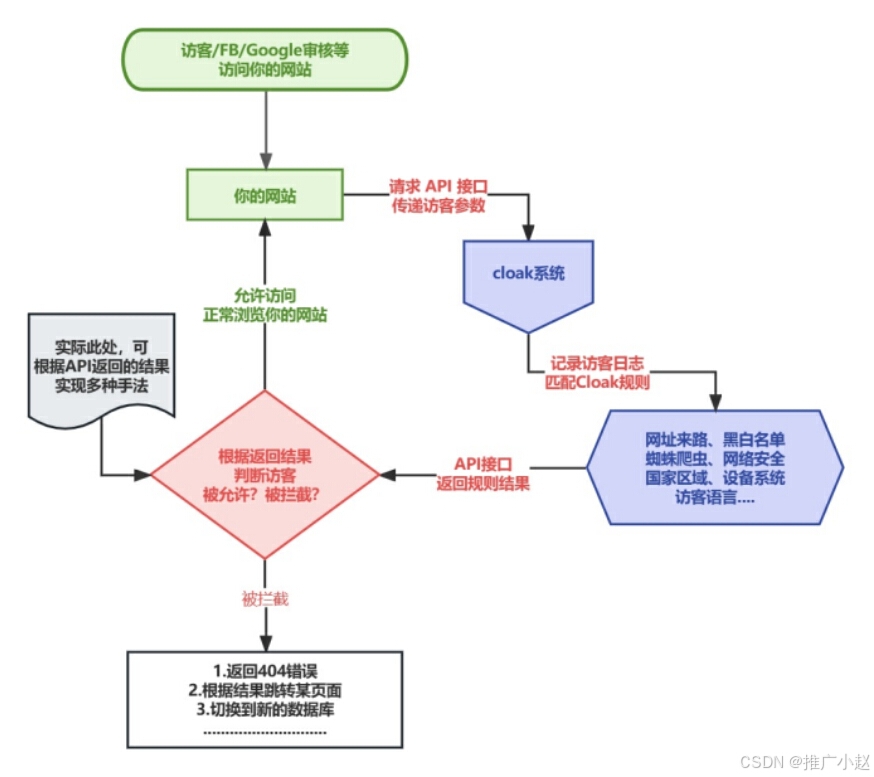

新兴斗篷cloak技术,你了解吗?

随着互联网技术的飞速发展,网络营销领域也经历了翻天覆地的变革。 从最早的网络横幅广告到如今主流的搜索引擎和社交媒体营销,广告形式变得越来越多样。 其中,搜索引擎广告一直以其精准投放而备受青睐,但近年来,一项名…...

:不变子群的几道例题)

【抽代复习笔记】34-群(二十八):不变子群的几道例题

例1:证明,交换群的任何子群都是不变子群。 证:设(G,o)是交换群,H≤G, 对任意的a∈G,显然都有aH {a o h|h∈H} {h o a|h∈H} Ha。 所以H⊿G。 【注:规范的不变子群符号是一个顶角指向左边…...

轻量级批量任务编排利器batchai:从原理到实战应用

1. 项目概述:一个被低估的批量任务编排利器在数据处理、模型训练、自动化测试这些日常开发工作中,我们常常会遇到一个看似简单却异常繁琐的问题:如何高效、可靠地管理成百上千个独立但又相似的任务?比如,你需要用不同的…...

基于AI的抖音自动回复系统:架构、部署与高阶运营实战

1. 项目概述与核心价值作为一个在内容运营和私域流量领域摸爬滚打了多年的老手,我深知在抖音这样的平台上,与粉丝的每一次互动都至关重要。一条及时的评论回复,一句贴心的私信问候,往往就是转化和留存的关键。但现实是,…...

保姆级教程:用Python和baostock复现Fama-French三因子模型,手把手教你分析A股

用Python实战Fama-French三因子模型:从理论到A股分析全流程解析 在量化投资领域,Fama-French三因子模型犹如一盏明灯,为理解股票收益提供了清晰的框架。不同于传统CAPM模型的单一市场视角,这一诺奖级理论通过引入市值和账面市值比…...

3D数字孪生项目 LCP 优化指南

LCP(Largest Contentful Paint,最大内容绘制时间)是衡量页面加载体验的核心指标,在 3D 开发项目中尤为关键。 与传统网页不同,3D 数字孪生系统的 LCP 问题往往是 CPU GPU 网络 资源 主线程 共同阻塞的结果…...

高性能MCP服务器实战:AI应用通信优化与性能调优指南

1. 项目概述:一个为AI应用提速的“高速公路”接口最近在折腾AI应用开发的朋友,估计都绕不开一个词:MCP(Model Context Protocol)。简单来说,它就像是一个标准化的“插头”,让不同的AI模型&#…...

基于Whisper语音识别的reCAPTCHA v2音频挑战本地破解方案

1. 项目概述:本地化AI驱动的reCAPTCHA v2音频挑战破解方案 如果你在自动化测试、数据采集或者某些需要绕过验证码的合法合规场景中,被Google的reCAPTCHA v2(尤其是那个恼人的“我不是机器人”复选框)卡住过,那你一定知…...

脉搏血氧仪原理与ADuC7024微控制器应用解析

1. 脉搏血氧仪的核心原理与医疗价值脉搏血氧仪作为现代医疗监护的"第五生命体征"监测设备,其核心功能是实时测量动脉血氧饱和度(SpO2)和心率。这项技术之所以能成为临床标准,关键在于其无创、快速、可靠的特性。血氧饱和度的医学定义是血红蛋白…...

Qt 容器实战:用 QMap<QString, QList<T>> 实现一对多关系映射

在 Qt 开发中,经常遇到一个分类对应多个条目的场景,比如: 设置面板中"网络"分类下有多个配置项 商品系统中"电子产品"分类下有多个商品 权限系统中"管理员"角色有多个权限点 这类一对多关系,用 QMap<QString, QList<T>> 是极为优…...

开源机械爪框架openclaw-mini:轻量可编程,快速实现自动化抓取

1. 项目概述:一个轻量级、可编程的“机械爪”开源框架最近在折腾一些桌面级的自动化小项目,比如自动浇花、整理桌面小零件,或者给家里的智能家居做个物理开关,总感觉市面上的成品要么太“重”(价格贵、体积大ÿ…...

Go语言错误处理:error接口与错误包装详解

Go语言错误处理:error接口与错误包装详解 1. Go语言错误处理哲学 Go语言采用显式错误处理的哲学,与其他语言的异常机制不同。在Go中,错误被视为一种普通的返回值,函数通过返回error类型来表示可能出现的错误。这种设计使得错误处理…...