周期法频率计的设计

目录

周期法频率计

分析:

设计过程:

周期法频率计

对于低频信号,应用周期法进行测频。周期法测频的基本原理是:应用标准频率信号统计被测信号两个相邻脉冲之间的脉冲数,然后通过脉冲数计算出被测信号的周期,再根据频率与周期之间的倒数关系计算出频率值。

分析:

(1)10mHz信号的周期为100秒。若应用50MHz晶振信号统计被测信号的周期,则两个相邻脉冲之间需要统计(50×106×100=)5×109个脉冲,因此需要应用33位二进制计数器(233=8588934592>5×109)进行计数。 (2)被测信号的周期以两个相邻脉冲的边沿为基准进行测量。

信号边沿检测的通用方法是:应用同步寄存器来捕获和存储被测频率信号。若应用三级右移寄存器作为同步器,如图所示,当存储数据Q0Q1Q2=x10 时,表示检测到被测信号的上升沿,存储数据Q0Q1Q2=x01时,表示检测到被测信号的下降沿,其中x表示无关位。

描述信号边沿检测电路的Verilog代码参考如下:

module edge_detector (input det_clk, // 时钟,50MHzinput rst_n, // 复位信号,低电平有效input x_signal, // 被测信号output wire rising_edge, // 上升沿标志,高电平有效output wire fall_edge // 下降沿标志,高电平有效);reg [0:2] sync_reg; // 三级同步寄存器定义// 同步移存过程always @( posedge det_clk or negedge rst_n ) if ( !rst_n ) sync_reg <= 3'b000;else sync_reg <= { x_signal, sync_reg[0:1] };// 边沿检测逻辑assign rising_edge = sync_reg[1] & ~sync_reg[2];assign fall_edge = ~sync_reg[1] & sync_reg[2];

endmodule

设计过程:

对于周期法频率计,状态机内部需要定义4个状态:复位(RESET)、空闲(IDLE)、计数(COUNT)和结束(DONE)。 状态转换的基本思路是: (1)复位信号有效时,强制状态机处于RESET状态; (2)复位信号撤销后,状态机转入IDLE状态,等待被测信号的有效沿。 (3)检测到第一个有效沿时,状态机转入COUNT状态,开始进行计数; (4)检测到第二个有效沿时,状态机转入DONE状态,停止计数并输出周期计数值; (5)状态机处于DONE时,下一个时钟脉冲转入IDLE状态。

根据上述状态转换图,描述周期测量状态机的Verilog代码参考如下:

module period_detector (input det_clk, // 检测电路时钟,50MHzinput rst_n, // 复位信号,低电平有效input x_signal, // 被测频率信号output reg [32:0] period_value // 周期测量值);// 状态定义及编码localparam RESET = 4'b0001;localparam IDLE = 4'b0010;localparam COUNT = 4'b0100;localparam DONE = 4'b1000;// 内部线网和变量定义reg [0:2] sync_reg; // 移位寄存变量(* synthesis,probe_port,keep *) wire fall_edge; // 下降沿标志reg [3:0] current_state,next_state; // 现态与次态(* synthesis,probe_port,keep *) wire cnt_en; // 计数允许信号(* synthesis,probe_port,keep *) reg [32:0] period_cnt; // 周期计数值// 下降沿检测逻辑assign fall_edge = ~sync_reg[1] & sync_reg[2];// 计数允许逻辑assign cnt_en = ( current_state == COUNT );// 同步移存过程always @( posedge det_clk or negedge rst_n ) if ( !rst_n ) sync_reg <= 3'b000;else sync_reg [0:2] <= { x_signal, sync_reg[0:1] }; // 状态机转换过程always @( posedge det_clk or negedge rst_n )if ( !rst_n ) current_state <= RESET; else current_state <= next_state;// 次态逻辑描述always @ ( current_state )case ( current_state )RESET: next_state <= IDLE;IDLE: if ( fall_edge ) next_state <= COUNT;else next_state <= IDLE;COUNT: if ( fall_edge ) next_state <= DONE;else next_state <= COUNT;DONE: next_state <= IDLE;default: next_state <= RESET;endcase// 周期计数过程always @( posedge det_clk ) if ( current_state == IDLE )period_cnt <= {33{1'b0}};else if ( cnt_en )period_cnt <= period_cnt + 1'b1;// 计数锁存过程always @ ( current_state )if ( current_state == DONE )period_value <= period_cnt;

endmodule

上述状态机代码的仿真波形如图所示。从图中可以看出,状态机时序正确。

应用状态机统计到被测信号周期的计数值period_value后,还需要将计数值转换为周期值,然后再换算为频率值。 由于状态机的时钟为50MHz,所以标准信号的周期 Tdet_clk=20ns,因此被测信号的周期值Tx为 Tx = period_value × Tdet_clk = period_value × 20 (ns) 因此,被测信号的频率值为 fx = 1/Tx = 109/ (period_value × 20) = 5×107/ period_value (Hz) 由上式可以看出,需要应用除法器来计算被测信号的频率值。

测量10mHz~10kHz低频信号的频率,定义被测信号的频率大于等于1Hz时,频率值以“4位整数+4位小数”的格式显示,被测信号的频率小于1Hz时,频率值以“8位小数”的格式显示。

设fx=qqq...qqqq.rrrr rrrr...r。为处理方便,先将计算得到的频率值fx扩大108倍,因此,当频率小于1Hz时除法的商即为实际的频率值,以“8位小数”格式显示。当频率大于小于1Hz时,再缩小104倍(相当于将fx只扩大104倍),则以“4位整数+4位小数”加上小数点显示时,即为实际的频率值。 由于被除数5×1015需要用53位二进制数(252<5×1015<253)表示,而除数period_value为33位二进制数,因此需要定制53位二进制数除以33位二进制数的除法器。

在“DIVIDER_for_freqor_inst.v”前打√,表示生成例化模板文件,以便可以应用例化语句调用定制的除法器。

根据上述处理思路,将周期计数值转换为频率的Verilog描述代码参考如下:

module period2freq (input [32:0] period_value, // 33位周期计数值output wire [27:0] freq_value, // 频率值,需要应用BIN28toBCD转换为8个BCD码output wire DP_flag // 小数点标志);// 内部线网定义wire [52:0] div_quotient; // 53位除法商数wire [32:0] div_remain; // 33位除法余数wire [52:0] freq_temp; // 商数÷10000// 除法器IP例化 DIVIDER_for_freqor DIVIDER_for_freqor_inst (.denom ( period_value ), // 分母,周期计数值.numer ( 53'd5000000000000000 ), // 分子,常数5×1015.quotient ( div_quotient ), // 除法商数,53位.remain ( div_remain ) // 除法余数,33位);// 频率显示值和小数点标志输出assign freq_temp = div_quotient/10000; assign freq_value = (div_quotient<100000000)? // 小于108?div_quotient[27:0] : // 小于1Hz,以“8位小数”显示freq_temp[27:0]; // 大于等于1Hz,以“4位整数+4位小数”显示assign DP_flag = ( div_quotient<100000000 )? 0 : 1; endmodule

20路分频式信号源,输出信号频率为:0.01~6103Hz,由4.5节中模块fx32.v简化而来。

module fx20 ( input clk50, // 时钟,50MHzinput [4:0] fsel, // 频率选择output reg fpout // 信号源输出);// 内部变量定义reg [31:0] q; // 计数变量// 计数逻辑描述always @(posedge clk50 ) q <= q + 1'b1;// 输出选择过程 always @(fsel,q) case (fsel) // 根据fsel分频输出5'b01100: fpout = q[12]; // 6103.515625Hz5'b01101: fpout = q[13]; // 3051.7578125Hz 5'b01110: fpout = q[14]; // 1525.87890625Hz 5'b01111: fpout = q[15]; // 762.939453125Hz5'b10000: fpout = q[16]; // 381.4697265625Hz 5'b10001: fpout = q[17]; // 190.7348631825Hz5'b10010: fpout = q[18]; // 95.367431640625Hz5'b10011: fpout = q[19]; // 47.6837158203125Hz5'b10100: fpout = q[20]; // 23.84185791015625Hz5'b10101: fpout = q[21]; // 11.920928955078125Hz5'b10110: fpout = q[22]; // 5.9604644775390625Hz5'b10111: fpout = q[23]; // 2.9802322876953125Hz5'b11000: fpout = q[24]; // 1.490116119384765625Hz5'b11001: fpout = q[25]; // 0.7450580596923828125Hz5'b11010: fpout = q[26]; // 0.37252902984619140625Hz5'b11011: fpout = q[27]; // 0.186264514923095703125Hz5'b11100: fpout = q[28]; // 0.0931322574615478515625Hz5'b11101: fpout = q[29]; // 0.04656612873077392578125Hz5'b11110: fpout = q[30]; // 0.023283064365386962890625Hz5'b11111: fpout = q[31]; // 0.0116415321826934814453125Hzdefault: fpout = q[14]; // 1525.87890625Hzendcaseendmodule

相关文章:

周期法频率计的设计

目录 周期法频率计 分析: 设计过程: 周期法频率计 对于低频信号,应用周期法进行测频。周期法测频的基本原理是:应用标准频率信号统计被测信号两个相邻脉冲之间的脉冲数,然后通过脉冲数计算出被测信号的周期ÿ…...

【Linux】drop cache与reclaim的区别

前言 在 Linux 内核中,drop cache和reclaim是两种不同的内存管理机制,它们的目的和实现方式有所不同。 Drop Cache 定义 drop cache 是一种手动操作,允许用户通过向 /proc/sys/vm/drop_caches 写入特定的值,直接清除系统中的缓…...

【Linux课程学习】:命令行参数,环境变量

🎁个人主页:我们的五年 🔍系列专栏:Linux课程学习 🌷追光的人,终会万丈光芒 🎉欢迎大家点赞👍评论📝收藏⭐文章 目录 命令行参数: 用命令行参数实现不同…...

HTB:WifineticTwo[WriteUP]

目录 连接至HTB服务器并启动靶机 信息搜集 使用rustscan对靶机TCP端口进行开放扫描 使用nmap对靶机开放端口进行脚本、服务扫描 使用curl访问靶机8080端口 使用浏览器直接访问/login路径 漏洞利用 使用searchsploit搜索该WebAPP漏洞 Payload USER_FLAG:bb…...

mac安装Pytest、Allure、brew

安装环境 安装pytest 命令 pip3 install pytest 安装allure 命令:brew install allure 好吧 那我们在安装allure之前 我们先安装brew 安装brew 去了官网复制了命令 还是无法下载 如果你们也和我一样可以用这个方法哦 使用国内的代码仓库来执行brew的安装脚本…...

关于相机选型的一些参数说明

上一篇:关于相机的一些参数计算(靶面、视野等) 目录 1.卷帘快门和全局快门1.1 卷帘快门1.2 全局快门PS:视觉伺服与快门选择 2.黑白和彩色3.CCD和CMOS3.1 CCD3.2 CMOSCCD VS CMOS 4.面阵和线扫4.1 面阵4.2 线扫4.3 面阵 VS 线扫 5.…...

深入解析 Cron 表达式高级用法:Spring 与 Linux Crontab 的全面对比与实践20241120

深入解析 Cron 表达式高级用法:Spring 与 Linux Crontab 的全面对比与实践 任务调度是后台服务中的重要组成部分,无论是定期数据备份、日志归档还是周期性报表生成,Cron 表达式始终是描述这些任务规则的核心工具。本文将聚焦 Spring Cron 表…...

24软专 数据结构

1、A[n],k,将数组向右循环移动k位。要求时间复杂度O(n),空间O(1)。 思路:采用三次反转数组的操作,可以实现时间复杂度为O(n),空间复杂度为O(1)的算法。 void moveElem(int array[],int k,int length){//a…...

洛谷 P1616 疯狂的采药 C语言 记忆化搜索

题目: https://www.luogu.com.cn/problem/P1616?contestId215526 完全背包问题,最后一个超出空间了。完全背包和就是无限次的拿,公式跟01背包差不多。 但是,只有当前能拿和拿不下,换下一个。注意要处理好边界条件。…...

#渗透测试#红蓝攻防#HW#SRC漏洞挖掘01之静态页面渗透

免责声明 本教程仅为合法的教学目的而准备,严禁用于任何形式的违法犯罪活动及其他商业行为,在使用本教程前,您应确保该行为符合当地的法律法规,继续阅读即表示您需自行承担所有操作的后果,如有异议,请立即停…...

element-plus入门教程:Button

一、Button组件概述 Element Plus的Button组件是一个常用的操作按钮,提供了多种类型、尺寸、状态等配置选项,以满足不同的交互需求。 二、安装Element Plus 在Vue 3项目中,可以通过npm或yarn来安装Element Plus。 npm install element-pl…...

oneplus6线刷、trwp、magisk(apatch)、LSPosed、Shamiko、Hide My Applist

oneplus6线刷android10.0.1 oneplus6线刷包(官方android10.0.1)下载、线刷教程: OnePlus6-brick-enchilada_22_K_52_210716_repack-HOS-10_0_11-zip 启用开发者模式 设置 / 连续点击6次版本号 : 启用开发者模式设置/开发者模式/{打开 usb调试, 打开 网络adb调试,…...

flux的版本

1.flux1-dev.safetensors https://huggingface.co/black-forest-labs/FLUX.1-devhttps://huggingface.co/black-forest-labs/FLUX.1-dev原生的23.8G的模型。原生12B的模型,float16的。需要配合ae.safetensors,flux1-dev.safetensors以及clip-l和T5的权重使用,注意ae.sft和f…...

Kafka 数据倾斜:原因、影响与解决方案

Kafka:分布式消息系统的核心原理与安装部署-CSDN博客 自定义 Kafka 脚本 kf-use.sh 的解析与功能与应用示例-CSDN博客 Kafka 生产者全面解析:从基础原理到高级实践-CSDN博客 Kafka 生产者优化与数据处理经验-CSDN博客 Kafka 工作流程解析:…...

【从零开始的LeetCode-算法】3297. 统计重新排列后包含另一个字符串的子字符串数目 I

给你两个字符串 word1 和 word2 。 如果一个字符串 x 重新排列后,word2 是重排字符串的 前缀,那么我们称字符串 x 是 合法的 。 请你返回 word1 中 合法 子字符串的数目。 示例 1: 输入:word1 "bcca", word2 "…...

【2024APMCM亚太赛A题】完整参考论文与代码分享

A题 一、问题重述二、问题分析问题一:水下图像分类问题二:退化原因建模问题三:针对单一退化的图像增强方法问题四:复杂场景的综合增强模型问题五:针对性增强与综合增强的比较 三、问题假设退化特征独立性假设物理模型普…...

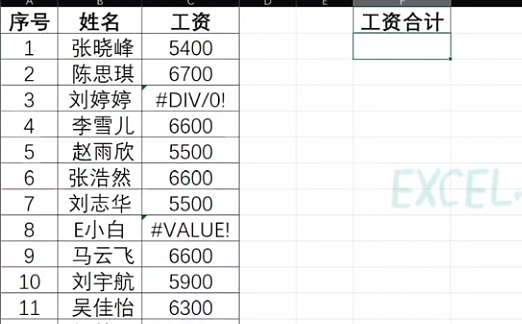

Excel求和如何过滤错误值

一、问题的提出 平时,我们在使用Excel时,最常用的功能就是求和了,一说到求和你可能想到用sum函数,但是如果sum的求和区域有#value #Div等错误值怎么办?如下图,记算C列中工资的总和。 直接用肯定会报错&…...

Android 常用命令和工具解析之GPU相关

目录 1、GPU基本信息 1.1 获取GPU基本信息 1.2 伪造GPU基本信息 2、GPU内存信息 3、经典案例 案例1:GPU伪造信息方案 案例2:GPU内存统计算法 GPU 指的是 Graphics Processing Unit,即图形处理单元。GPU 是一种专门用于处理图形和图像相…...

刷题——【模板】二维前缀和

前缀和 题目题目链接题解方法一方法二 题目 描述 给你一个 n 行 m 列的矩阵 A ,下标从1开始。 接下来有 q 次查询,每次查询输入 4 个参数 x1 , y1 , x2 , y2 请输出以 (x1, y1) 为左上角 , (x2,y2) 为右下角的子矩阵的和, 输入描述&#x…...

Xilinx 7 系列 FPGA的各引脚外围电路接法

Xilinx 7系列FPGA的外围电路接法涉及到多个方面,包括电源引脚、时钟输入引脚、FPGA配置引脚、JTAG调试引脚,以及其他辅助引脚。 本文参考资料: ds180 - 7 Series FPGAs Data Sheet - Overview ds181 - Artix 7 FPGAs Data Sheet - DC and AC…...

MGeo地址实体对齐镜像快速上手:5分钟部署,支持自定义阈值

MGeo地址实体对齐镜像快速上手:5分钟部署,支持自定义阈值 1. 引言:地址数据混乱,是时候换个思路了 你有没有被这样的问题困扰过? 公司CRM系统里,同一个客户因为地址写法不同,被重复记录了十几…...

番茄小说离线阅读解决方案:打造你的个人数字图书馆

番茄小说离线阅读解决方案:打造你的个人数字图书馆 【免费下载链接】fanqienovel-downloader 下载番茄小说 项目地址: https://gitcode.com/gh_mirrors/fa/fanqienovel-downloader 在数字阅读时代,你是否曾遇到过这样的困扰:网络信号不…...

飞书机器人告警配置避坑指南:夜莺监控常见报错解决方案

飞书机器人告警配置避坑指南:夜莺监控常见报错解决方案 深夜的告警风暴里,飞书机器人突然罢工是什么体验?上周三凌晨2点,当我面对满屏的Key Words Not Found和sign match fail报错时,终于理解了为什么运维工程师的咖啡…...

HoRain云--Vue3组件开发:从入门到精通的终极指南

🎬 HoRain 云小助手:个人主页 ⛺️生活的理想,就是为了理想的生活! ⛳️ 推荐 前些天发现了一个超棒的服务器购买网站,性价比超高,大内存超划算!忍不住分享一下给大家。点击跳转到网站。 目录 ⛳️ 推荐 …...

不用花钱买token版)

本地部署openclaw(window环境下)不用花钱买token版

步骤一:参考视频到安装 openclaw 前就行(剩下的步骤和博主不太样) 步骤 2 1、免费注册一个 NVIDIA NIM 账户: 【点击前往】 登入后在设置中心生成你自己的API Keys ,过期时间选择永不过期,目前可以直接免…...

NVIDIA Profile Inspector实战手册:从参数调试到显卡性能全面优化

NVIDIA Profile Inspector实战手册:从参数调试到显卡性能全面优化 【免费下载链接】nvidiaProfileInspector 项目地址: https://gitcode.com/gh_mirrors/nv/nvidiaProfileInspector 在PC硬件优化领域,专业工具与普通用户之间往往存在技术鸿沟。N…...

ide-eval-resetter:突破JetBrains IDE试用期限制的创新方案——2026开发者必备指南

ide-eval-resetter:突破JetBrains IDE试用期限制的创新方案——2026开发者必备指南 【免费下载链接】ide-eval-resetter 项目地址: https://gitcode.com/gh_mirrors/id/ide-eval-resetter 问题引入:JetBrains IDE试用期限制的痛点分析 作为开发…...

PyTorch核心模块实战指南:从nn.Sequential到nn.MaxPool2d的深度解析

1. 快速上手nn.Sequential:像搭积木一样构建神经网络 第一次接触PyTorch时,我被各种复杂的网络结构吓到了——直到发现nn.Sequential这个"乐高积木盒"。这个容器让我能用拼积木的方式组合网络层,比如下面这个图像分类器的经典结构&…...

Pixel Couplet Gen入门必看:Streamlit Components封装像素春联React组件

Pixel Couplet Gen入门必看:Streamlit Components封装像素春联React组件 1. 项目介绍 Pixel Couplet Gen是一款基于ModelScope大模型驱动的创意春联生成器。与传统春联设计不同,它采用了独特的8-bit像素游戏风格,将中国传统春节元素与复古电…...

长上下文与RAG

读到一篇探讨RAG技术的文章,很受用,遂记录一下。核心结论:RAG不会被无限上下文取代。 原文地址:LLM无限上下文了,RAG(Retrieval Augmented Generation)还有意义吗? - 今日头条 以下…...