打怪升级之FPGA组成原理(LE部分)

FPGA芯片逻辑单元的原理

不论你使用哪一款FPGA芯片,其核心可编程逻辑单元都是从一段内存种按顺序读取执行并执行的过程。具体来说,FOGA芯片内部包括可编程逻辑块(LAB)、可配置输入输出单元(IOE)、时钟管理模块、嵌入式RAM(BRAN,在Cyclone IV中是M9K)、丰富的布线资源、内嵌和底层功能单元和嵌入式专用硬核等。

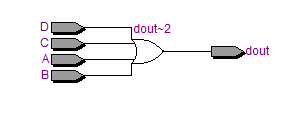

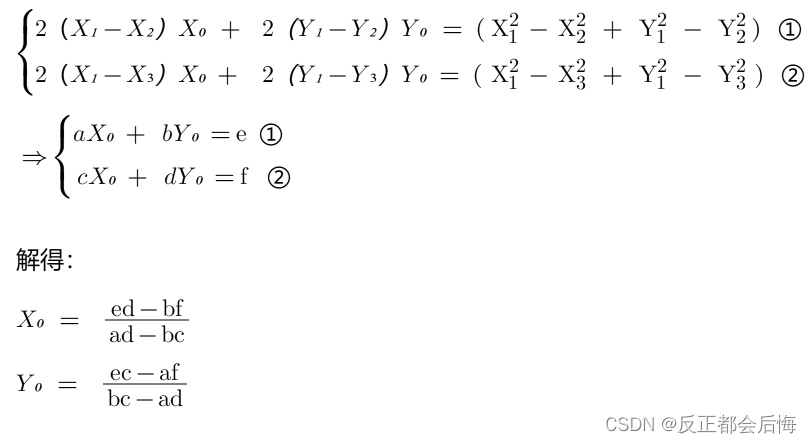

FPGA通过查找表来等效实现所有可能的门电路。一个查找表可以实现与门、或门、非门、加减法等各种组合逻辑。查找表可以直接由Quartus综合出来,可以实现Verilog里的各种语法。比如下面这段代码:

module top(input A,input B,input C,input D,output dout);assign dout = A | B | C | D;endmodule

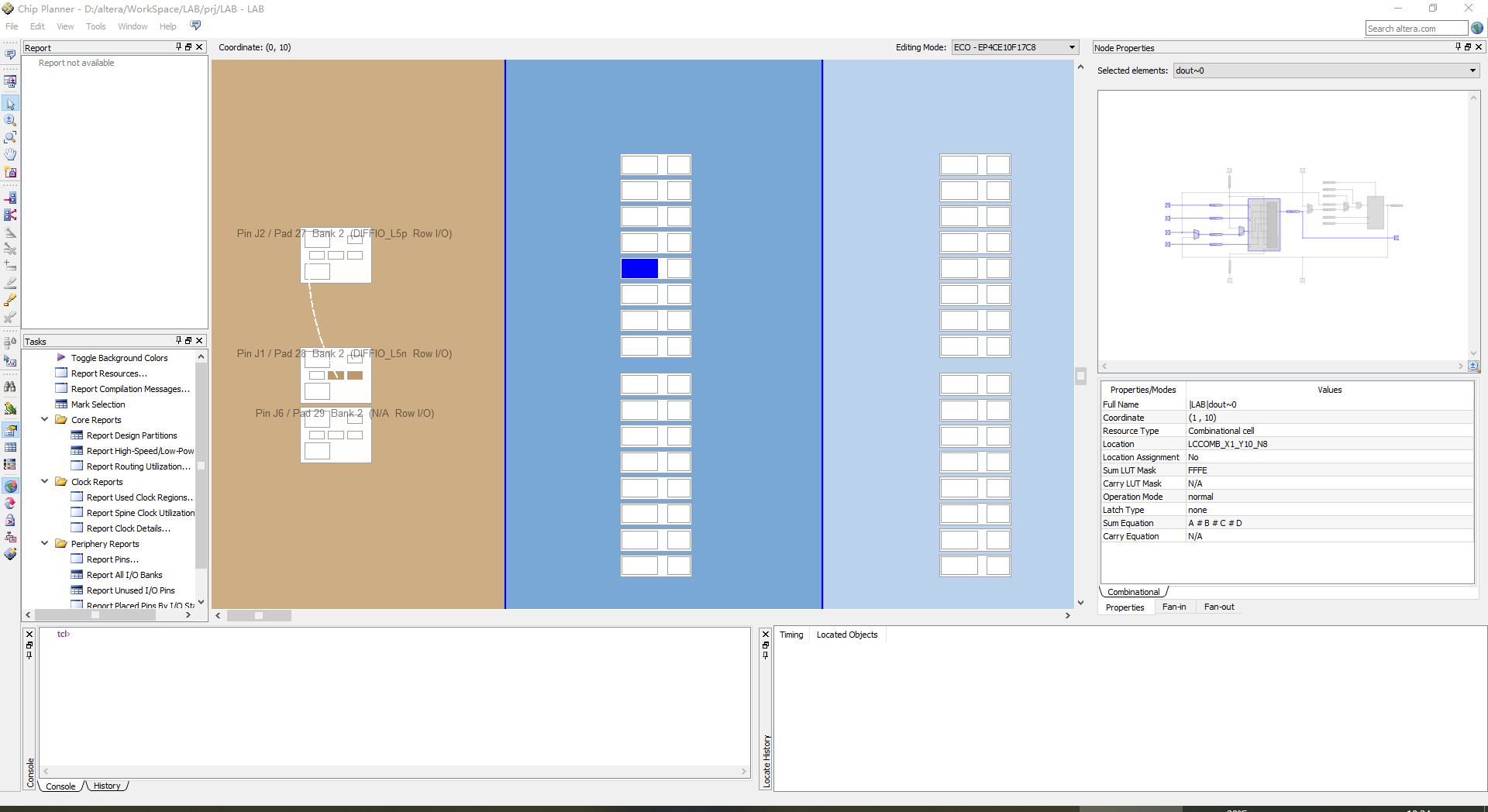

就可以实现一个与门结构。我们可以综合出这样的电路,在Quartus中看它对应的RTL视图与Chip planner中的对应:

打开Chip planner找到上述资源位置:

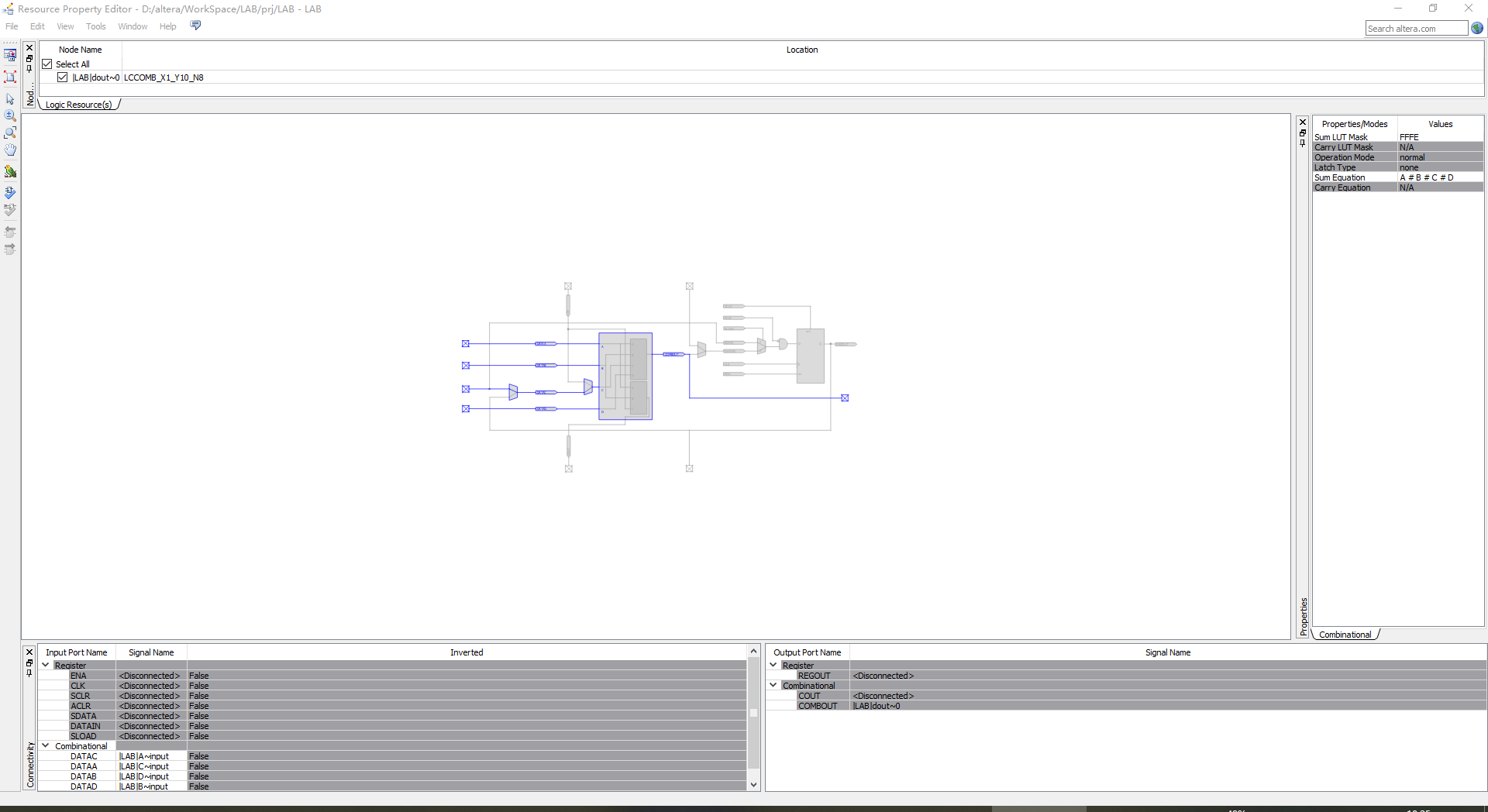

双击进入资源分配界面:

双击进入资源分配界面:

这样的查找表就是最基本的结构了。一个查找表LUT的内部会有一个SRAM存储器。针对地址的不同,SRAM的值也会不同,这样就等效的实现了门电路结构。

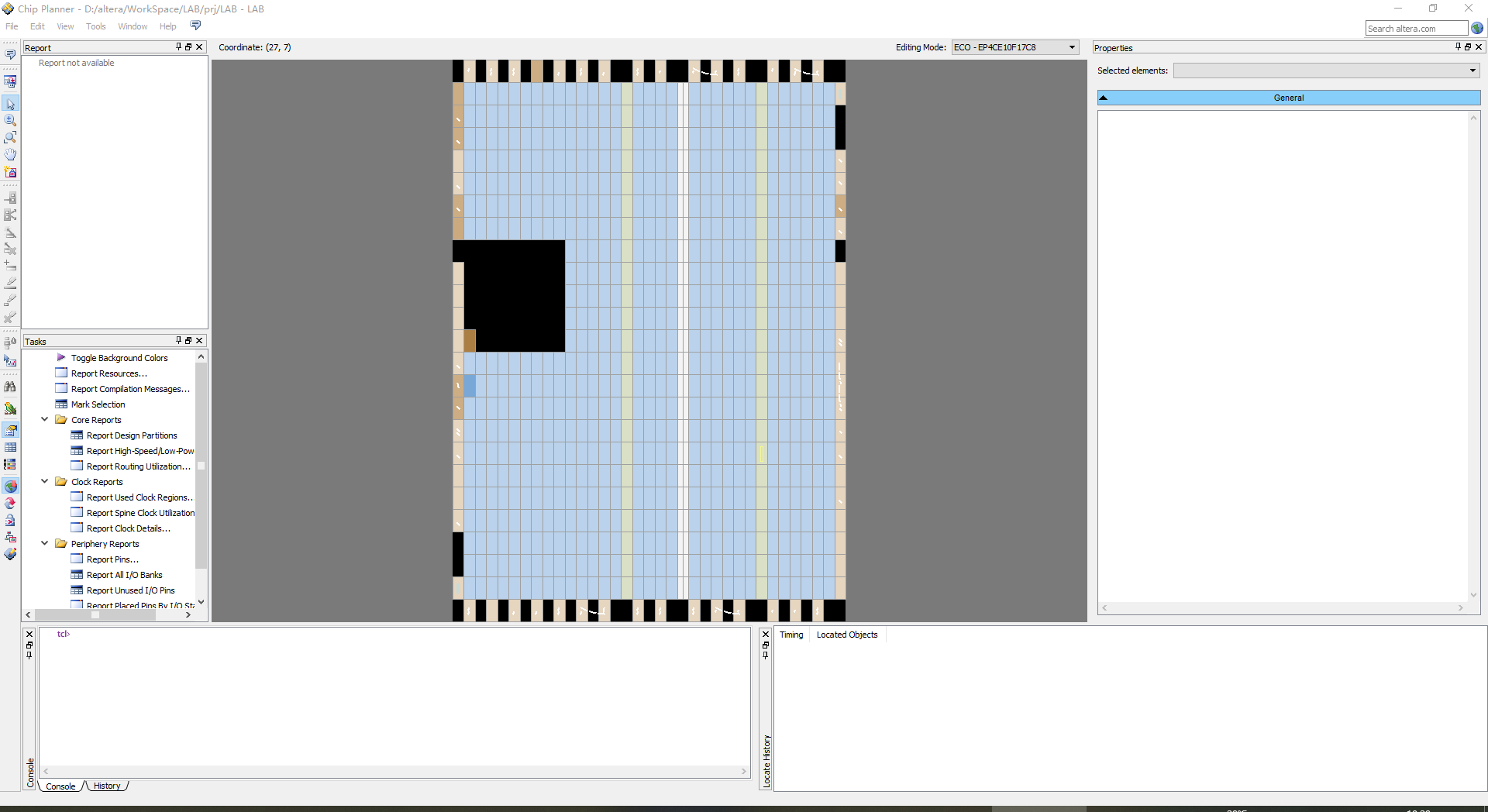

对FPGA而言,由基本的查找表组成LE,由LE组成LAB,由LAB、MK9(内存)、DSP、I/O共同构成了整个芯片的资源分布:

上图就是Cyclone IV E芯片的资源分布,其中蓝色代表LAB资源,浅绿代表M9K内存资源,白色代表DSP资源,浅棕色代表I/O资源。

对XILIMX、ALTERA等厂家的FPGA进行编程,实际上就是把需要进行运算的结果计算出来并存储在SRAM中,输入发生相应变化时,将SRAM中的值输出。

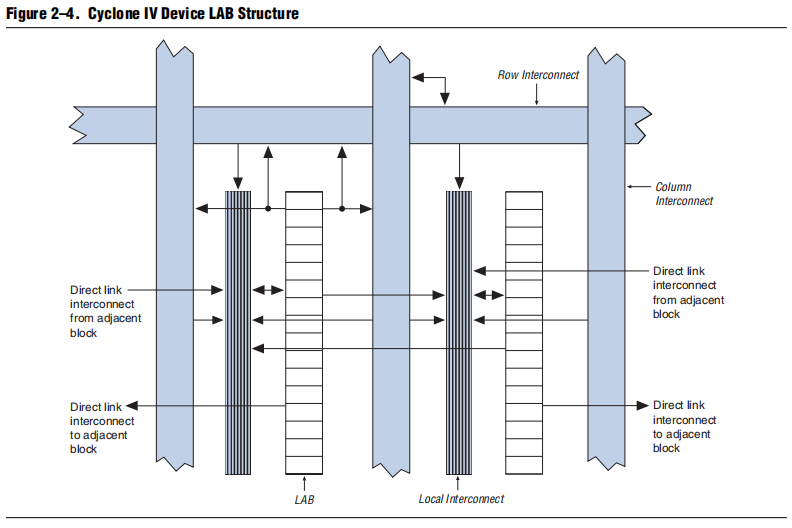

对于一个可编程逻辑块(LAB)而言,包含了以下要素:

1.一个逻辑块包含了16个逻辑单元(LE);

2.一个LAB控制信号;

3.一个LE进位链;

4.一个寄存器链;

5.本地互联;

本地互联在同一个LAB和LE之间传输信号,寄存器链连接把一个LE寄存器的输出传输到LAB中相邻的LE寄存器上。

Cyclone IV 基本组成

Cyclone IV器件的M9K存储器模块都具有9Kbit的嵌入式SRAM存储器。可以把M9K模块配置成单端口、简单双端口RAM以及FIFO缓冲器或者ROM。

Cyclone IV器件的嵌入式乘法器可以在单一模块中实现一个18 X 18 或9 X 9 乘法器。Altera针对乘法器模块提供了一套DSP IP核。包括有限脉冲响应(FIR),快速傅里叶变换(FFT)和数字控制震荡器(NCO)功能。

Cyclone IV器件的I/O支持可编程总线保持、可编程上拉电阻、可编程延迟、可编程驱动能力以及可编程slew-rate控制,从而实现了信号完整性以及热插拔的优化。

Cyclone IV 器件支持符合单端 I/O 标准的校准后片上串行匹配 (Rs OCT) 或者驱动阻抗匹配 (Rs)。 在 Cyclone IV GX 器件中,高速收发器 I/O 位于器件的左侧。器件的顶部,底部及右侧可以实现通用用户 I/O。

Cyclone IV 器件包含了高达 30 个全局时钟 (GCLK) 网络以及高达 8 个 PLL (每个 PLL上均有五个输出端 ),以提供可靠的时钟管理与综合。您可以在用户模式中对Cyclone IV 器件 PLL 进行动态重配置来改变时钟频率或者相位。

Cyclone IV 器件支持位于器件顶部,底部和右侧的 SDR、 DDR, DDR2 SDRAM 和 QDRII SRAM 接口。Cyclone IV E 器件也支持这些接口位于器件左侧。接口可能位于器件的两个或多个侧面,以实现更灵活的电路板设计。Altera® DDR SDRAM 存储器接口解决方案由一个 PHY 接口和一个存储控制器组成。Altera 提供了 PHY IP,您可以将它与您自己定制的存储控制器或 Altera 提供的存储控制器一起使用。Cyclone IV 器件支持在 DDR和 DDR2 SDRAM 接口上使用纠错编码(ECC) 位。

Cyclone IV 器件使用 SRAM 单元存储配置数据。每次器件上电后,配置数据会被下载到Cyclone IV 器件中。低成本配置选项包括 Altera EPCS 系列串行闪存器件以及商用并行闪存配置选项。这些选项实现了通用应用程序的灵活性,并提供了满足特定配置以及应用程序唤醒时间要求的能力。

逻辑单元(LE)基本组成

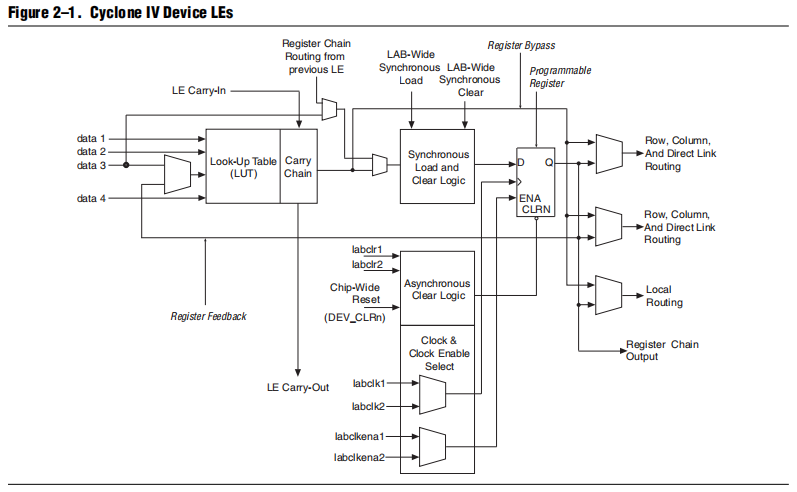

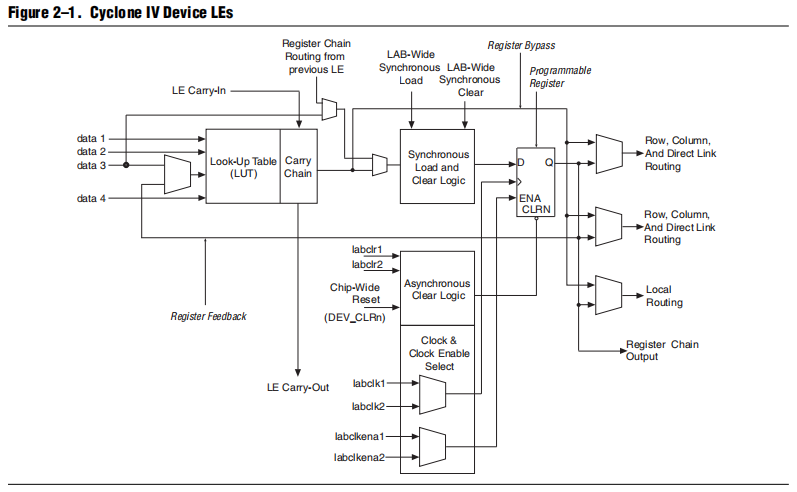

一个LE单元由以下内容组成:

1.一个四输入查找表(LUT),以实现四种变量的任意功能;

2.一个可编程寄存器;

3.一个进位链连接;

4.一个寄存器连接;

实际上不止有这一种LE结构,但我们可以以此为典型进行分析:

一个LE单元包括LUT、控制信号逻辑、同步加载清零逻辑、可编程寄存器等。其中最核心的时LUT和可编程寄存器。可编程寄存器可以配置成D、JK、T或者SR触发器。

如果没有时序逻辑功能,则LE适用于一般的逻辑应用和组合功能;如果有计算需求,会利用到外置的DSP模块做计算。

相关文章:

打怪升级之FPGA组成原理(LE部分)

FPGA芯片逻辑单元的原理 不论你使用哪一款FPGA芯片,其核心可编程逻辑单元都是从一段内存种按顺序读取执行并执行的过程。具体来说,FOGA芯片内部包括可编程逻辑块(LAB)、可配置输入输出单元(IOE)、时钟管理模块、嵌入式RAM(BRAN,在Cyclone IV…...

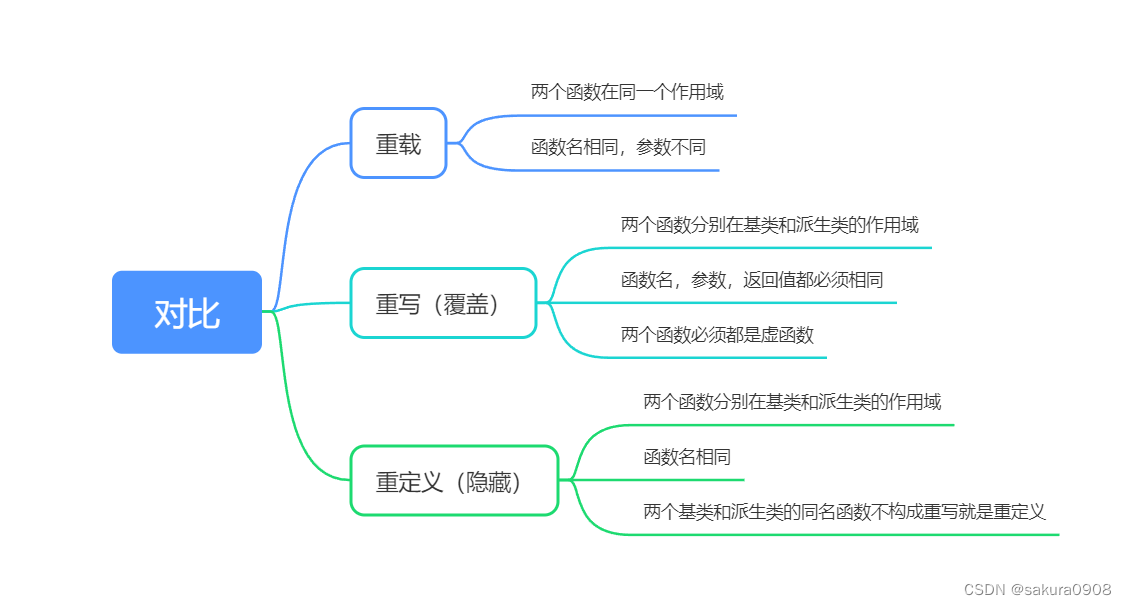

c++的多态

目录 1、多态 1.1多态的构成条件 1.2多态的好处 2、虚函数 2.1虚函数重写 2.2虚函数的默认参数 2.3纯虚函数重写 2.4抽象类 2.5虚析构,纯虚析构重写 3、重载、覆盖(重写)、隐藏(重定义)的对比 编辑 多态是c面向对象三大特性之一 程序调用函数时&#…...

【数据结构与算法】堆的实现(附源码)

目录 一.堆的概念及结构 二.接口实现 A.初始化 Heapinit 销毁 Heapdestroy B.插入 Heappush 向上调整 AdjustUp 1.Heappush 2.AdjustUp C.删除 Heappop 向下调整 AdjustDown D.堆的判空 Heapempty 堆顶数据 Heaptop 堆的大小 Heapsize 三.源码 Heap.h He…...

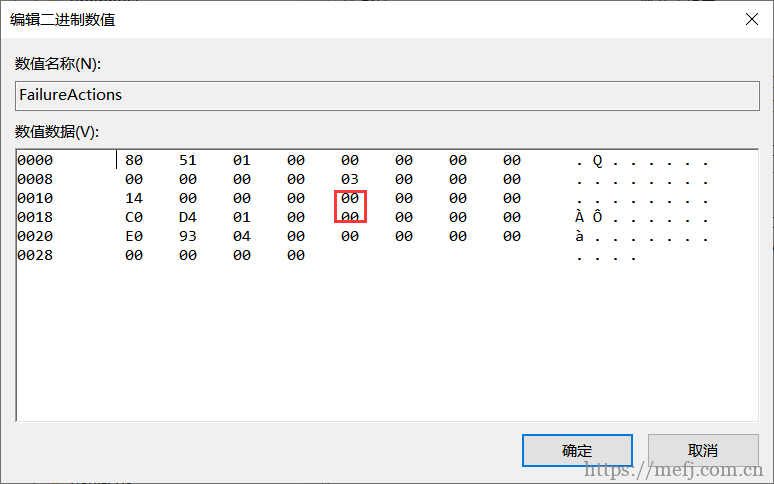

win10彻底永久关闭自动更新【亲测有效】

一、禁用Windows Update服务 1、同时按下键盘 Win R,打开运行对话框,然后输入命令 services.msc ,点击下方的“确定”打开服务,如下图所示。 2、找到 Windows Update 这一项,并双击打开,如图所示。 3、右击…...

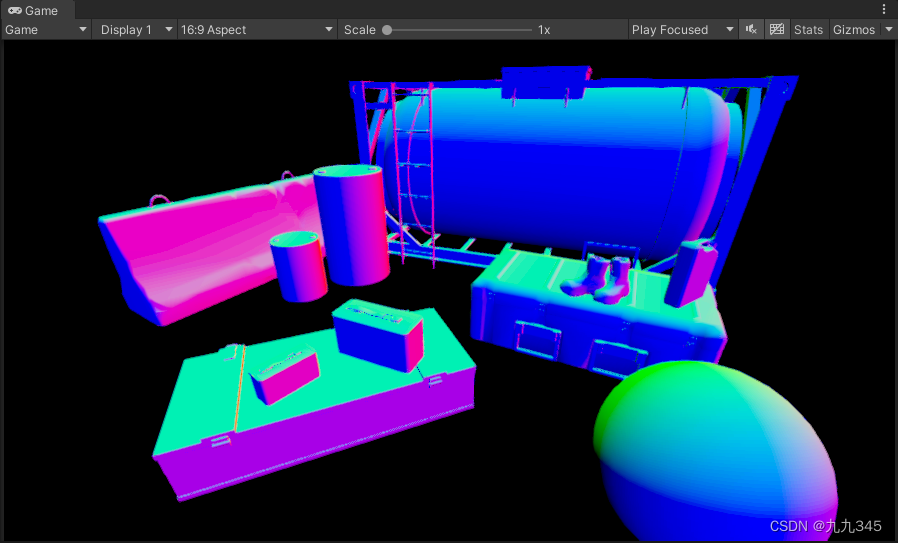

【Unity UPR】造个获取深度法线纹理的轮子

描边需要深度法线纹理的加持,效果才能达到最好,但URP下很多版本不支持直接获取_CameraNormalsTexture,而我本人也尝试了一下在12.1.7下偷懒直接拿SSAO里的Depth Normal图, 虽然也能实现吧,但是需要打开SSAO的同时&…...

用 Python解析HTML页面

用 Python 解析 HTML 页面 在网络爬取的过程中,我们通常需要对所爬取的页面进行解析,从中提取我们需要的数据。网页的结构通常是由 HTML 标签所组成的,通过对这些标签的解析,可以得到网页中所包含的有用信息。在 Python 中&#…...

python logging 详解

python logging 详解1. 导入logging模块2. 配置日志记录器3. 记录日志消息4. 自定义日志记录器5. 日志轮换6. 日志过滤器7. 日志异常跟踪8. 日志输出到控制台和文件9. 使用配置文件10. 使用第三方库11. format格式详解12. 总结Python的logging模块提供了灵活的日志记录功能&…...

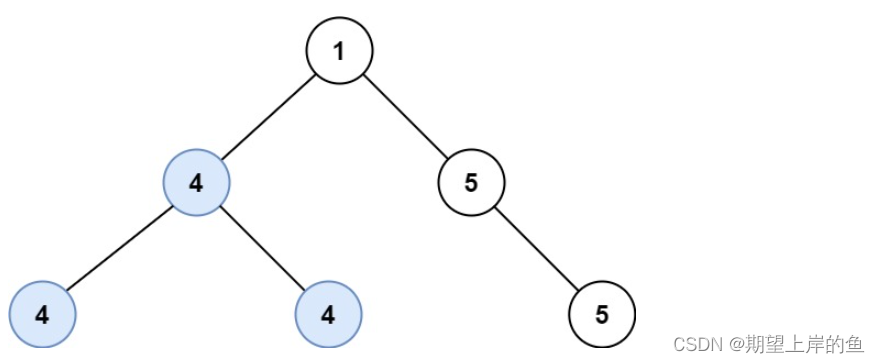

( “树” 之 DFS) 687. 最长同值路径 ——【Leetcode每日一题】

687. 最长同值路径 给定一个二叉树的 root ,返回 最长的路径的长度 ,这个路径中的 每个节点具有相同值 。 这条路径可以经过也可以不经过根节点。 两个节点之间的路径长度 由它们之间的边数表示。 示例 1: 输入:root [5,4,5,1,1,5] 输出&…...

Elasticsearch解决不能修改索引、字段问题解决方案

问题1: 由于es索引不能删除,不能修改,在不影响原数据的情况下,并且生产服务不停机的情况下,怎么修改索引,并保留原索引内的数据? 基于kibanna的dev Tools执行参数,淘汰postman&…...

面试官在线改简历 | 只有6秒!程序员简历这样写才能抓住科技公司大佬的眼球

其实每一份简历 每一个瑞库特 可能也就平均花6秒钟的时间看一看 来进行一个快速的筛选 一份好的简历到底应该长什么样 同时呢在我们写简历的过程当中 应该避免什么样子的错误和误区 那我们今天呢来聊聊这个简历的事 大家知道 每次到了招聘高分期啊这些大的公司 像谷歌Facebook…...

IM即时通讯-7-如何设计通知提醒

本文大纲 本文从为什么做通知提醒, 以及如何设计通知提醒, 以及如何衡量通知提醒三方面解释了如何设计通知提醒。 对于重点的如何设计通知提醒, 通过拆分前台和后台, 前台采用自建或者二方通道, 后台采用厂商信令通道…...

赛狐ERP | 亚马逊选品方法与策略详解:如何挑选最优质的产品?

亚马逊作为全球电商巨头,其产品种类之丰富也是无人能及。然而,在如此繁杂的商品体系下,如何选品成为了摆在商家面前的一道难题。本文将从亚马逊选品的目标、方法、策略三个方面进行详细介绍。 一、选品的目标 在进行选择之前,必…...

【GCU体验】基于PyTorch + GCU跑通ResNet50模型并测试GCU性能

一、环境 地址:启智社区:https://openi.pcl.ac.cn/ 二、计算卡介绍 云燧T20是基于邃思2.0芯片打造的面向数据中心的第二代人工智能训练加速卡,具有模型覆盖面广、性能强、软件生态开放等特点,可支持多种人工智能训练场景。同时具备灵活的可…...

【机器视觉------标定篇(二)】三点成圆算法(求相机旋转中心)

应用场景 机器视觉项目应用中,相机安装在机器人上,并且需要定位产品返回坐标偏差以及角度偏差。 与九点标定配合使用,实现精准角度补偿。 算法输入 不共线的三点坐标 A(X₁,Y₁) ,B(X₂,Y₂&…...

AUTOSAR E2E详细介绍

E2E概述 E2E(End-To-End)是AUTOSAR为功能安全ISO26262提出的一个安全模块。这里的端(End)并不是指ECU与ECU之间,而是指通信ECU上的SW-C与SW-C之间。 在车载网络中,信息交换通常是从一个ECU发送信号,另一个ECU接收信号。对E2E而言,通常是从源SW-C生成信号,经过RTE(R…...

Dream 主题使用手册 - 基础篇

Dream 主题基于 Halo 博客系统开发,本文将介绍本主题一些功能的使用,文档将持续更新。 一、安装 & 更新 1.1 安装包安装 & 更新 进入主题 Release 界面:https://github.com/nineya/halo-theme-dream/releases 下载主题压缩包 halo…...

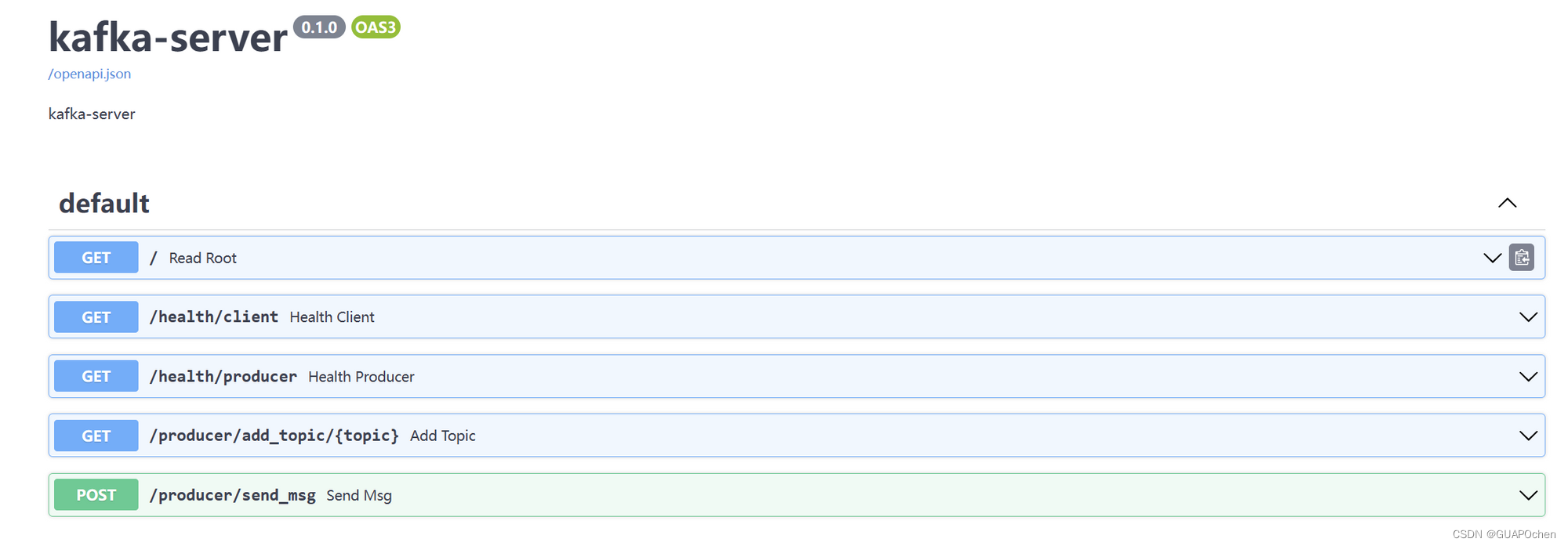

WSL下的Kafka开发容器:Docker搭建、API、整合

背景介绍 Kafka是一个分布式流处理平台,可以处理大规模数据流并支持实时数据流的处理。 本文介绍了如何在WSL下使用Docker搭建Kafka容器,并使用Python的kafka-python库和FastAPI框架实现了一个简单的API。同时,还将该服务整合到一个整体的d…...

下载安装)

cv2(OpenCV)下载安装

cv2对应库是OpenCV,官网下载链接:https://www.lfd.uci.edu/~gohlke/pythonlibs/#opencv 最好下载对应python版本的,通过pip命令安装可能会出现版本过高或者过低的问题,导致import cv2没问题,但是内部函数无法调用。 …...

【剑指 offer】旋转数组的最小数字

✨个人主页:bit me👇 ✨当前专栏:算法训练营👇 旋 转 数 组 的 最 小 数 字核心考点:数组理解,二分查找,临界条件 描述: 有一个长度为 n 的非降序数组,比如[1,2,3,4,5]…...

GB 9706.1-2020 医用电气设备第1部分:基本安全和基本性能的通用要求-1

这是份什么文件 这是一份中华人民共和国国家标准,具体为GB9706.1—2020,标准适用于医用电气设备,并规定了医用电气设备基本安全和基本性能的通用要求。主要涵盖了医疗电器设备与患者接触的各种要求,包括电气安全、机械防护、防护辐…...

Unity Figma Bridge:设计-开发一体化协同的技术架构解决方案

Unity Figma Bridge:设计-开发一体化协同的技术架构解决方案 【免费下载链接】UnityFigmaBridge Easily bring your Figma Documents, Components, Assets and Prototypes to Unity 项目地址: https://gitcode.com/gh_mirrors/un/UnityFigmaBridge Unity Fig…...

90%的人只用了Superpowers 10%的能力,实战案例带你走通全流程

装了Superpowers还是不会用?这套完整工作流,让你的AI从“工具”变“搭档”你可能已经在 GitHub 上给 Superpowers 点过 Star 了,甚至在本地环境里跑了一遍安装流程。但说实话,你大概率只触发了其中一两个 Skill——写代码时偶尔触…...

有钱才懂爱:赚到钱你再去谈男女关系,你会发现,择偶逻辑都变了。 没钱的时候,你看到的是一堆条件:房子、车子、工作、家境。 有钱了之后,那些条件你都自己有了

先谋生,再谋爱:有钱之后,我才看懂了男女关系的真相 目录 先谋生,再谋爱:有钱之后,我才看懂了男女关系的真相 没钱的时候,你谈的从来都不是爱情,是“生存合伙” 钱是最好的过滤器,它能帮你滤掉所有的“功能性需求” 底层的“忠诚”,很多时候只是“没有选择”的同义词…...

Hitboxer:终极免费SOCD按键重映射工具,3分钟彻底解决游戏输入冲突

Hitboxer:终极免费SOCD按键重映射工具,3分钟彻底解决游戏输入冲突 【免费下载链接】socd Key remapper for epic gamers 项目地址: https://gitcode.com/gh_mirrors/so/socd 还在为游戏中同时按下相反方向键导致角色卡顿而烦恼吗?Hitb…...

ThinkPad双风扇终极控制指南:TPFanControl2完全使用教程

ThinkPad双风扇终极控制指南:TPFanControl2完全使用教程 【免费下载链接】TPFanCtrl2 ThinkPad Fan Control 2 (Dual Fan) for Windows 10 and 11 项目地址: https://gitcode.com/gh_mirrors/tp/TPFanCtrl2 你是否为ThinkPad笔记本的风扇噪音而烦恼ÿ…...

告别卡顿!用Sunshine打造私人游戏串流服务器的完整指南

告别卡顿!用Sunshine打造私人游戏串流服务器的完整指南 【免费下载链接】Sunshine Self-hosted game stream host for Moonlight. 项目地址: https://gitcode.com/GitHub_Trending/su/Sunshine 你是否曾经梦想过在任何设备上流畅玩PC游戏?无论是躺…...

智在记录 AI 语音转文字效果全景展示

在日常的工作和生活中,我们常常面临这样的困境:一场长达两小时的头脑风暴会议结束后,整理纪要却要花掉半天时间;课堂上老师语速飞快,笔记记得手忙脚乱,回头复习时却发现关键逻辑断档;或是医生叮…...

安装部署Keystone

一、以下命令安装了Keystone组件的必要软件包。 [rootcontroller ~]# yum -y install openstack-keystone httpd mod_wsgi 二、MariaDB数据库配置 [rootcontroller ~]# mysql -uroot -p000000 查看当前已有数据库: show databases;第2步,新建“keyston…...

时间序列预测中的注意力剪枝技术:SPAT方法解析

1. 项目概述:当时间序列预测遇上注意力剪枝在多元时间序列预测领域,Transformer架构凭借其强大的注意力机制已成为主流解决方案。这种机制通过动态计算序列元素间的关联权重,能够有效捕捉电力负荷、交通流量等场景中的复杂时序模式。然而在实…...

给工程师的傅里叶变换:从信号处理到图像压缩,用Python代码理解核心推导

给工程师的傅里叶变换:从信号处理到图像压缩,用Python代码理解核心推导 当你在Spotify上听歌时,算法如何从嘈杂环境中分离人声?手机拍照时,JPEG压缩为何能大幅减小文件体积却保持清晰?这些看似不相关的技术…...