Chapter8 :Physical Constraints(ug903)

8.1About Physical Constraints(关于物理约束)

Xilinx®Vivado®集成设计环境(IDE)允许通过设置对象属性值对设计对象进行物理约束。示例包括:

•I/O约束,如位置和I/O标准

•布局约束,如单元位置

•布线约束,如固定布线

•配置约束,如配置模式

与时序约束类似,物理约束必须保存在Xilinx设计约束(XDC)文件或Tcl脚本中,以便在打开设计时可以与网表一起加载。将设计加载到内存中后,可以使用Tcl控制台或使用Vivado design Suite IDE编辑工具以交互方式输入新的约束。大多数物理约束是通过对象上的特性来定义的:

set_property <property> <value> <object list>使用Pblock命令的区域约束除外。

8.1.1 Critical Warning(严重警告)

对于XDC文件中的无效约束,包括应用于设计中找不到的对象的约束,会发出严重警告。有关属性定义和用法,请参阅《Vivado Design Suite Properties Reference Guide》 (UG912).。

建议:Xilinx强烈建议您查看所有关键警告,以确保设计受到适当约束。无效的约束在交互应用时会导致错误。

8.2Netlist Constraints(网表约束)

网表约束是在网表对象(如ports, pins, nets 或者cells)上设置的,需要综合和实现才能以特殊方式处理它们。

重要:请确保了解使用这些约束的影响。它们可能会增加设计面积,降低设计性能,或者两者兼而有之。

网表约束包括:

• CLOCK_DEDICATED_ROUTE

• MARK_DEBUG

• DONT_TOUCH

• LOCK_PINS

8.2.1CLOCK_DEDICATED_ROUTE

在网络上设置CLOCK_DEDICATED_ROUTE,以指示时钟信号的路由方式。

CLOCK_DEDICATED_ROUTE属性在时钟网络上用于覆盖默认路由。这是一种高级控制,需要格外小心,因为它可能会影响时间的可预测性和可调度性。

例如,当专用时钟路由不可用时,CLOCK_DEDICATED_ROUTE可以设置为FALSE。

值FALSE允许Vivado工具使用通用路由资源将时钟从输入端口路由到全局时钟资源,如BUFG或MMCM。只有当设备封装引脚分配被锁定,并且时钟输入无法分配给适当的具有时钟功能的输入引脚(CCIO)时,才应将其作为最后手段。除非与FIXED_ROUTE一起使用,否则路由将是次优且不可预测的。有关此属性的更多信息,请参阅《UltraFast Design Methodology Guide for FPGAs and SOCs 》(UG949)中的时钟约束。

8.2.2 MARK_DEBUG

它可以在编译流中的任何点连接到逻辑调试工具。有关更多信息,请参阅 Vivado Design Suite User Guide: Programming and Debugging (UG908).

8.2.3 DONT_TOUCH

在叶单元、分层单元或网络对象上设置DONT_TOUCH,以便在网表优化期间保留它。

DONT_TOUCH最常用于:

•防止网络被优化掉。具有DONT_TOUCH的网络不能通过综合或实现来吸收。这有助于逻辑探测或调试设计中的意外优化。要保留具有多个层次分段的网络,请将DONT_TOUCH放置在最靠近其驱动的网络分段的网络PARENT(get_property PARENT$net)上。

•防止合并手动复制的逻辑。有时最好手动复制逻辑,例如跨大区域的高扇出驱动程序。将DONT_TOUCH添加到手动复制的驱动(以及原始驱动)会阻止综合和实现优化这些单元。

注意:使用reset_property可重置DONT_TOUCH属性。将DONT_TOUCH属性设置为0不会重置该属性。

提示:避免在分层单元上使用DONT_TOUCH进行实现,因为Vivado IDE实现不会使逻辑分层变平。在综合中使用KEEP_HIERARCHY来维护应用XDC约束的逻辑层次结构。

8.2.4 LOCK_PINS

LOCK_PINS是一个单元属性,用于指定逻辑LUT输入(I0、I1、I2…)和LUT物理输入引脚(A6、A5、A4…)之间的映射。常见的用途是强制将时序关键LUT输入映射到最快的A6和A5物理LUT输入。

8.2.4.1LOCK_PINS Constraint Example One(LOCK_PINS约束示例一)

将I1映射到A6,将I0映射到A5(交换默认映射)。

% set myLUT2 [get_cells u0/u1/i_365]

% set_property LOCK_PINS {I0:A5 I1:A6} $myLUT2

# Which you can verify by typing the following line in the Tcl Console:

% get_property LOCK_PINS $myLUT28.2.4.2LOCK_PINS Constraint Example Two(LOCK_PINS约束示例二)

对于LUT6映射I0到A6,I1到I5的映射无关紧要。

% set_property LOCK_PINS I0:A6 [get_cell u0/u1/i_768]8.2.3 I/O Constraints(IO约束)

I/O约束配置:

•端口

•连接到端口的单元典型约束包括:

•I/O标准

•I/O位置

Vivado设计套件支持许多与集成软件环境(ISE)设计套件相同的I/O约束。以下I/O属性列表并非详尽无遗。

•有关I/O属性的完整列表、有关I/O端口和I/O单元属性的更多信息以及正确语法的编码示例,请参阅Vivado Design Suite properties Reference Guide(UG912)。注意:除非另有说明,否则所有属性都应用于端口对象。

•有关这些属性背后的应用程序和方法的更多信息,请参阅设备SelectIO™文档,例如7 Series FPGAs SelectIO Resources User Guide (UG471)。

•DRIVE:设置输出缓冲区驱动强度(mA),仅适用于某些I/O标准。

•IOSTANDARD:设置I/O标准。

•SLEW:设置设备输出的转换速率(转换速率)行为。

•IN_TERM:设置输入端口的输入端接电阻的配置。

•DIFF_TERM:打开或关闭IBUFDS_DIFF_OUT等原语的100欧姆差分终端。

•KEEPER:在三态输出或双向端口上应用弱驱动程序,以在不驱动时保持其值。

•PULLTYPE:在三态输出或双向端口上应用弱逻辑低电平或高电平,以防止其浮动。

•DCI_CASCADE:定义一组主库和从库。DCI参考电压从主存储器组链接到从存储器组。在IOBANK对象上设置DCI_CASACDE。

•INTERNAL_VREF:释放I/O组的VREF引脚,转而使用内部生成的VREF。在IOBANK对象上设置INTERNAL_VREF

•IODELAY_GROUP:使用IDELAYCTRL将一组IDELAY和IODELAY单元分组,以实现IDELAYCTRL在设计中的自动复制和放置。

•IOB:告诉放置者尝试将FF放在I/O逻辑中,而不是放在结构切片中。此属性必须分配给寄存器,而不是分配给端口。

重要:ISE设计套件和Vivado设计套件在IOB处理方面存在显著差异。Vivado工具允许在端口和连接到端口的寄存器单元上设置IOB。如果在端口及其寄存器上设置了冲突的值,则以寄存器上的值为准。Vivado工具仅使用TRUE和FALSE值。值FORCE被解释为TRUE,而值AUTO被忽略。

与ISE不同,如果不能遵守IOB true的设置,Vivado工具会生成严重警告,而不是错误。

•IOB_TRI_REG:用于UltraScale中的HDIO+™ 设备。告诉放置者尝试将驱动三态信号的FF放在I/O逻辑中的HDIO组IOB上,而不是放在结构片上。此属性必须分配给寄存器,而不是分配给端口。

8.4 Placement Constraints(布局约束)

将布局约束应用于单元,以控制它们在设备中的位置。Vivado集成设计环境(IDE)支持许多与集成软件环境(ISE)设计套件和Integrated Software Environment (ISE) Design Suite and the PlanAhead™ 工具。

•LUTNM:应用于两个LUT的唯一字符串名称,以控制它们在单个LUT站点上的位置。与HLUTNM不同,LUTNM可以用于组合属于不同层次单元的LUT。

•HLUTNM:应用于同一层次结构中的两个LUT的唯一字符串名称,以控制它们在单个LUT站点上的位置。在多次实例化的单元中使用HLUTNM。

•PROHIBIT:禁止放置在站点。

•PBLOCK:连接到逻辑块,将它们约束到设备中的物理区域。PBLOCK是一个只读单元属性,是为其分配单元的PBLOCK的名称。只有使用XDC Tcl命令add_cells_to_Pblock和remove_cells_from_block才能更改Cell Pblock成员身份。

•PACKAGE_PIN:指定目标设备包引脚上设计端口的位置。

•LOC:将一个逻辑元素从网表中放置到设备上的一个位置。

•BEL:将网表中的逻辑元素放置到设备切片内的特定BEL。

8.4 .1Placement Types

工具中有两种类型的布局:

•固定布局(Fixed Placement)

•未固定布局(Unfixed Placement)

固定布局

固定布局是用户通过以下操作之一指定的布局:

•手动布局

•XDC约束

•在内存中加载的设计单元对象上使用IS_LOC_FIXED或IS_BEL_FIXED。

未固定的布局(Unfixed Placement)

非固定布局是由实施工具执行的布局。通过将布局设置为固定,实现无法在下一次迭代或增量运行期间移动受约束的单元。固定位置保存在XDC文件中,在该文件中显示为简单的LOC或BEL约束。

•IS_LOC_FIXED:将LOC约束从未固定提升为固定。

•IS_BEL_FIXED:将BEL约束从未固定提升为固定。

8.4 .2Placement Constraint Examples(布局约束示例)

8.4 .2.1(布局约束示例1)

将块RAM定位在RAMB18_X0Y10并固定其位置。

% set_property LOC RAMB18_X0Y10 [get_cells u_ctrl0/ram0]8.4 .2.2(布局约束示例2)

将LUT放置在切片内的C5LUT BEL位置,并固定其BEL分配。

% set_property BEL C5LUT [get_cells u_ctrl0/lut0]8.4 .2.3(布局约束示例3)

将输入总线寄存器定位在ILOGIC单元中,以缩短输入延迟。

% set_property IOB TRUE [get_cells mData_reg*]8.4 .2.4(布局约束示例4)

将两个小LUT组合为一个LUT6_2,该LUT6_2同时使用O5和O6输出。

% set_property LUTNM L0 [get_cells {u_ctrl0/dmux0 u_ctrl0/dmux1}]8.4 .2.5(布局约束示例5)

防止布局器使用块RAM的第一列。

% set_property PROHIBIT TRUE [get_sites {RAMB18_X0Y* RAMB36_X0Y*}]8.4 .2.6(布局约束示例6)

防止布局器使用时钟区域X0Y0。

% set_property PROHIBIT TRUE [get_sites -of [get_clock_regions X0Y0]]8.4 .2.7(布局约束示例7)

防止布局器使用SLR0。

% set_property PROHIBIT TRUE [get_sites -of [get_slrs SLR0]]重要:将BEL和LOC属性同时指定给单元时,必须在LOC之前指定BEL。

8.5Routing Constraints(布线约束)

布线约束应用于网络对象,以控制其布线资源。

8.5.1 Fixed Routing(固定布线)

固定布线是锁定布线的机制,类似于ISE中的定向布线。锁定网络布线资源涉及三个网络属性。见下表。

表10:网络属性

| 属性 | 功能 |

| ROUTE | 只读网络 属性 |

| IS_ROUTE_FIXED | 标记整个布线为固定布线的标志 |

| FIXED_ROUTE | 网络的固定布线部分 |

为了保证网络布线可以固定,它的所有单元也必须事先固定。

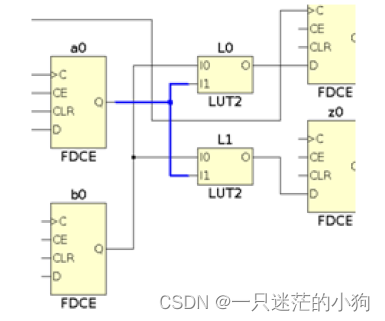

以下是一个完全固定布线的示例。该示例采用下图中的设计,并创建约束来固定netA(蓝色选中)的路由。

图95:图解布线约束的简单设计

在内存中加载已实现的设计后,可以查询任何网络的路由信息:

% set net [get_nets netA]

% get_property ROUTE $net

{ CLBLL_LL_CQ CLBLL_LOGIC_OUTS6 FAN_ALT5 FAN_BOUNCE5 { IMUX_L17

CLBLL_LL_B3 } IMUX_L11 CLBLL_LL_A4 }路由被定义为一系列相对的路由节点名称,扇出使用嵌入式大括号表示。路由是通过在网络上设置以下属性来固定的:

% set_property IS_ROUTE_FIXED TRUE $net要在XDC文件中对约束进行反向注释以供将来运行,还必须保留连接到固定网络的所有单元的位置。可以通过在原理图或设备视图中选择单元来查询此信息,并在“Properties ”窗口中查看它们的LOC/BEL属性值。或者,您可以直接从Tcl控制台查询这些值:

% get_property LOC [get_cells {a0 L0 L1}] SLICE_X0Y47 SLICE_X0Y47

SLICE_X0Y47

% get_property BEL [get_cells {a0 L0 L1}] SLICEL.CFF SLICEL.A6LUT

SLICEL.B6LUT由于固定布线通常是定时关键的,因此还必须在LUT的LOCK_pins属性中捕获LUT引脚映射,以防止路由器交换引脚。同样,您可以从Tcl控制台查询每个逻辑引脚的站点引脚:

% get_site_pins -of [get_pins {L0/I1 L0/I0}] SLICE_X0Y47/A4 SLICE_X0Y47/A2

% get_site_pins -of [get_pins {L1/I1 L1/I0}] SLICE_X0Y47/B3 SLICE_X0Y47/B2修复netA路由所需的完整XDC约束包括:

set_property BEL CFF [get_cells a0] set_property BEL A6LUT [get_cells L0]

set_property BEL B6LUT [get_cells L1]

set_property LOC SLICE_X0Y47 [get_cells {a0 L0 L1}] set_property LOCK_PINS

{I1:A4 I0:A2} [get_cells L0] set_property LOCK_PINS {I1:A3 I0:A2}

[get_cells L1]

set_property FIXED_ROUTE { CLBLL_LL_CQ CLBLL_LOGIC_OUTS6 FAN_ALT5

FAN_BOUNCE5 {

IMUX_L17 CLBLL_LL_B3 } IMUX_L11 CLBLL_LL_A4 } [get_nets netA]如果使用交互式Tcl命令而不是XDC,则可以使用place_cell命令同时指定多个放置约束,如下所示:

place_cell a0 SLICE_X0Y47/CFF L0 SLICE_X0Y47/A6LUT L1 SLICE_X0Y47/B6LUT有关place_cell的更多信息,请参阅Vivado Design Suite Tcl Command Reference Guide (UG835)。

8.6 Configuration Constraints(配置约束)

配置约束是应用于当前设计的比特流生成的全局约束。这包括诸如配置模式之类的约束。

8.6.1配置约束示例1

将CONFIG_MODE设置为M_SELECTMAP。

% set_property CONFIG_MODE M_SELECTMAP [current_design]8.6.2配置约束示例2

打开调试比特流。

% set_property BITSTREAM.GENERAL.DEBUGBITSTREAM Yes [current_design]8.6.3配置约束示例3

禁用CRC检查。

% set_property BITSTREAM.GENERAL.CRC Disable [current_design] 有关比特流生成属性和定义的列表,请参阅Vivado Design中的此链接Suite User Guide: Programming and Debugging (UG908).

相关文章:

Chapter8 :Physical Constraints(ug903)

8.1About Physical Constraints(关于物理约束) XilinxVivado集成设计环境(IDE)允许通过设置对象属性值对设计对象进行物理约束。示例包括: •I/O约束,如位置和I/O标准 •布局约束&…...

星标3.5k,一款国产的轻量级开源在线项目任务管理工具

今天给大家推荐一个轻量级的开源在线项目任务管理工具:DooTask 图片 DooTask 提供各类文档协作工具、在线思维导图、在线流程图、项目管理、任务分发、即时IM,文件管理等工具。 高效便捷的团队沟通工具 针对项目和任务建立群组,工作问题可…...

【华为OD机试真题2023B卷 JAVA】字符串摘要

华为OD2023(B卷)机试题库全覆盖,刷题指南点这里 字符串摘要 知识点字符串排序 时间限制:1s 空间限制:256MB 限定语言:不限 题目描述: 给定一个字符串的摘要算法,请输出给定字符串的摘要值。 1、去除字符串中非字母的符号。 2、如果出现连续字符(不区分大小写),则输…...

Java线程概述 (一)线程介绍

文章目录 🐒个人主页🏅JavaSE系列专栏📖前言:🪅什么是程序 、进程、线程?🪅线程的生命周期🪅多线程🪅守护者线程🪅线程并行与并发🪅死锁…...

操作系统第三章——存储系统(下)

锦衣雪华玉颜色,回眸一笑天下倾 文章目录 3.2.1 虚拟内存的基本概念知识总览传统存储方式的特征,缺点局部性原理虚拟内存的定义如何实现虚拟内存技术知识总结 3.2.2 请求分页管理方式知识总览页表机制缺页中断机制地址变换机制知识回顾 3.2.3 页面置换算…...

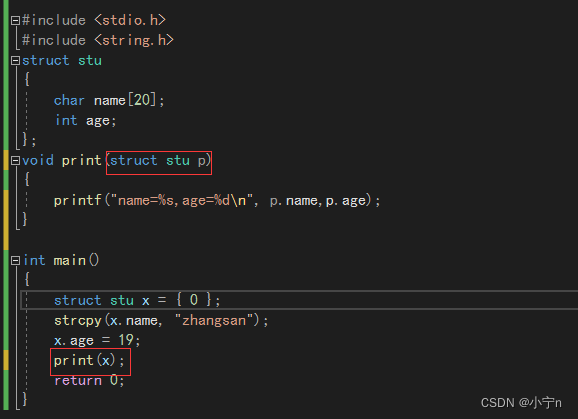

初识结构体

目录 结构体的声明 结构体的基础知识 结构体的声明 结构体成员的类型 结构体变量的定义和初始化 定义 初始化 结构体成员的访问 结构体变量访问成员 结构体指针访问指向变量的成员 结构体传参 传地址 传结构体 结论 结构体的声明 结构体的基础知识 数组ÿ…...

协程并发下数据汇总:除了互斥锁,还有其他方式吗?

1. 简介 本文介绍了在并发编程中数据汇总的问题,并探讨了在并发环境下使用互斥锁和通道两种方式来保证数据安全性的方法。 首先,通过一个实例,描述了一个并发拉取数据并汇总的案例,并使用互斥锁来确保线程安全。然后,…...

5、Ray-Actor模型和并发编程

5、Ray-Actor模型和并发编程 导航 1.简介和背景 2.Ray的基本概念和核心组件 3.分布式任务调度和依赖管理 4.对象存储和数据共享 5.Actor模型和并发编程 6.Ray的高级功能和扩展性 7.使用Ray构建分布式应用程序的案例研究 8.Ray社区和资源 9.核心框架介绍...

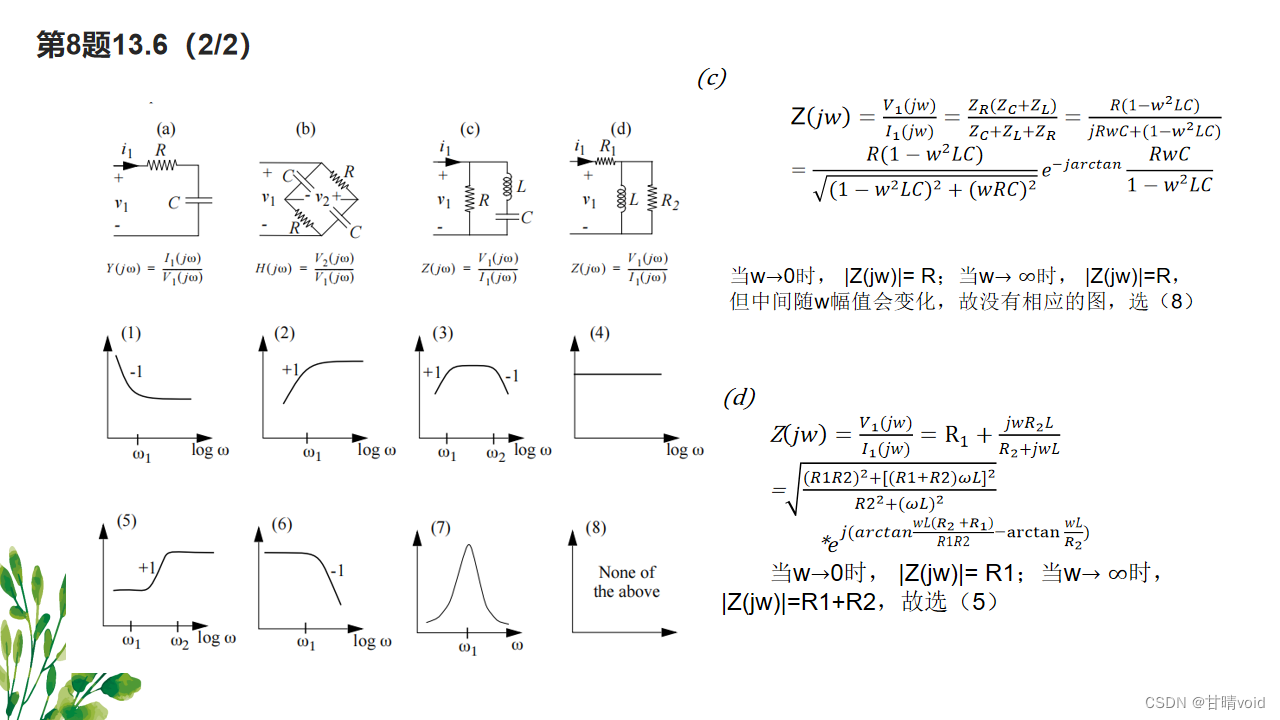

HNU-电路与电子学-小班2

第二次讨论 讨论题目: 1、电子秤的电桥电路可以分别用 1 个压控电阻、 2 个压控电阻、 3 个压控电阻、 4 个压控电阻实现吗?试写出每种实现的 U AB 输出表达式,并分析哪种实现电桥 电压的灵敏度(SV/ △ R )高。 …...

二分图匹配算法

匈牙利算法、Hopcroft-Karp算法和Kuhn-Munkres算法是三种常见的二分图匹配算法,它们在实现方式、时间复杂度和适用场景上有所差异。以下是它们的区别和优缺点: 匈牙利算法: 实现方式:匈牙利算法使用深度优先搜索(DFS)来寻找增广路…...

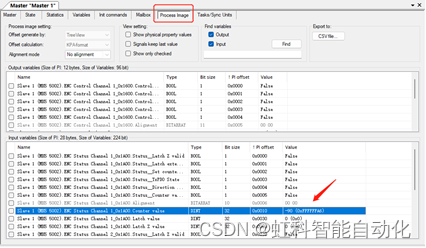

虹科技术 | 虹科EtherCAT增量编码器输入模块数据采集实操测试

1. 背景介绍 编码器是将信号或数据进行编制、转换为可用以通讯、传输和存储的信号形式的设备。编码器把角位移或直线位移转换成电信号,前者称为码盘,后者称为码尺。按照读出方式编码器可以分为接触式和非接触式两种;按照工作原理编码器可分为…...

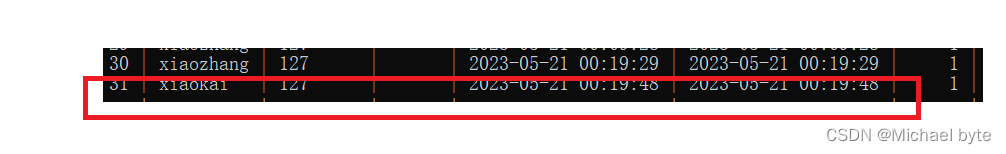

2023.05.21 学习周报

文章目录 摘要文献阅读1.题目2.背景3.现存问题和解决方法4.方法4.1 Variational mode decomposition (VMD)4.2 Bidirectional LSTM 5.实验5.1 数据标准化5.2 评价指标5.3 实验过程及结果 6.结论和展望 优劣解距离法有限元1.求解一个简单的传热问题2.有限元如何实现 总结 摘要 …...

资深程序员深度体验ChatGPT一周发现竟然....

周一打卡上班,老板凑到我跟前:“小李啊,这周有个新需求交给你做一下,给我们的API管理平台新增一个智能Mock的功能...”。我条件反射般的差点脱口而出:“这个需求做不了..”。不过在千钧一发之间,我想起了最…...

带你深入了解Android Handler的用法

Android中,Handler是一类用于异步消息传递和线程之间通信的基础框架。一个Handler是一个线程的处理器,可以接收消息,并调度运行它们。使用Handler,应用程序可以将处理器与一个线程关联,以将来的时间运行任务。而使用Ha…...

生于零售的亚马逊云科技,如何加速中国跨境电商企业出海?

导读:跨境电商进入精耕细作的新阶段。 作为中国企业出海的重要领域之一,近几年跨境电商行业处在快速发展中。商务部数据显示,2022年中国跨境电商出口达1.55万亿,同比增长11.7%。2023年1-2月,跨境电商进出口总额同比增长…...

兄弟组件传值$on无法接收值

方法一 前提是必须引入EventBus,而且该方法一刷新数据就没了 1.组件A里,点击事件里面使用$emit传入数据 2.组件A里,mounted里面使用$on接收数据,并把数据赋给EventBus EventBus.$on(detail,(data) > { EventBus.senddata d…...

Spring事务及事务传播机制

一.事务的含义:多个操作封装在一起,要么同时执行成功,一旦有一个操作执行失败,那么全部执行失败。这里给大家举个例子:比如A给B转账50元,而B没有收到这50元,此时A转账B这个操作也需要进行回滚,恢复到A给B没…...

npm i 常见问题

需要注意的是,如果你在使用 NPM 安装包的过程中遇到了任何问题,可以尝试使用 --verbose 参数打印更详细的错误信息,以便更好地诊断问题。例如: npm install --verbose 1、vue老项目缺少编译环境安装依赖报错的问题 待下载的项目…...

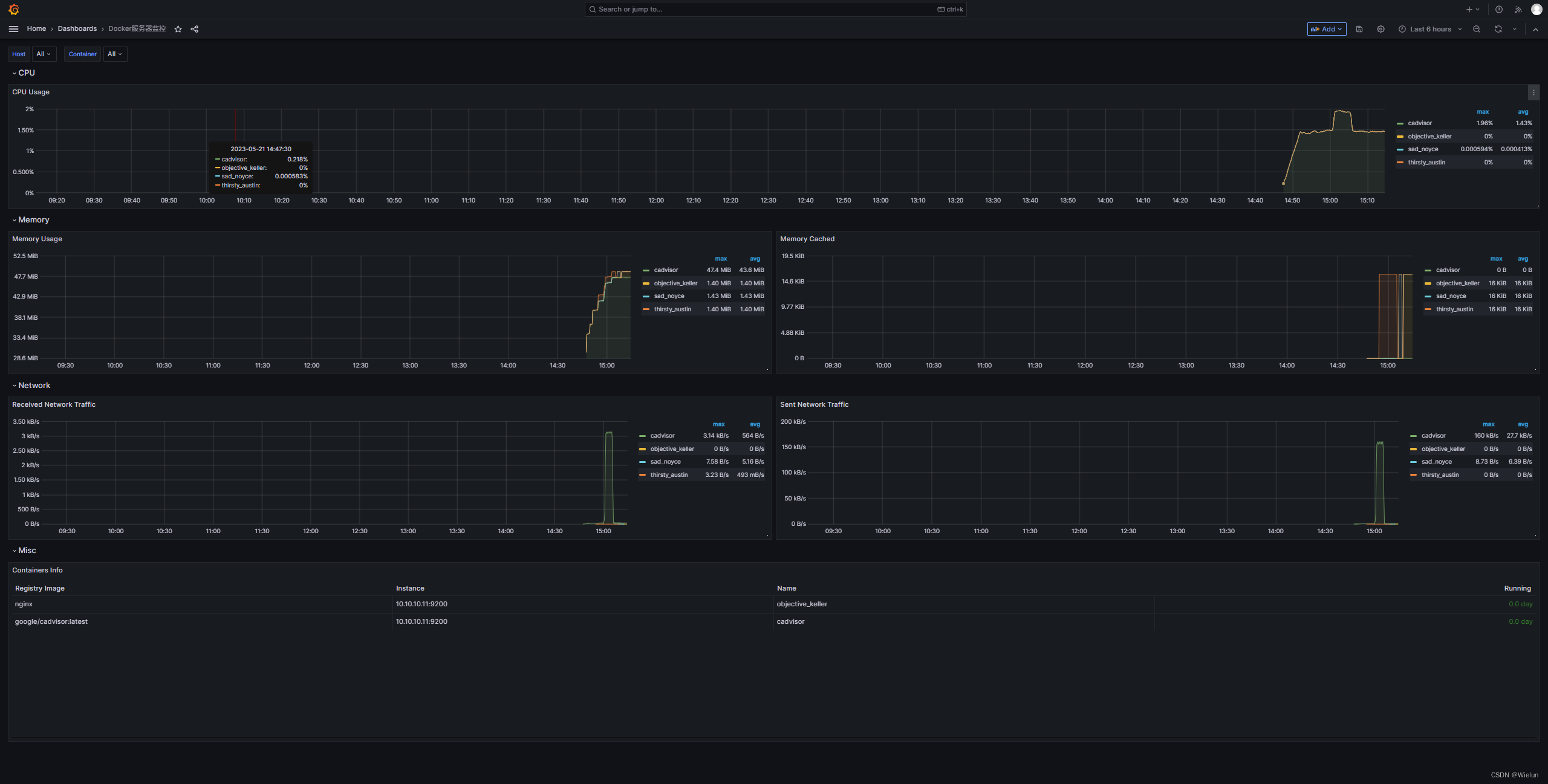

Prometheus+Grafana监控系统

一、简介 1、Prometheus简介 官网:https://prometheus.io 项目代码:https://github.com/prometheus Prometheus(普罗米修斯)是一个最初在SoundCloud上构建的监控系统。自2012年成为社区开源项目,拥有非常活跃的开发人员…...

基于脉冲神经网络的物体检测

访问【WRITE-BUG数字空间】_[内附完整源码和文档] 研究的意义在于探索脉冲神经网络在目标检测上的应用,目前主流的脉冲神经网络训练算法有直接BP训练、STDP无监督训练和训练好的ANN的转化,虽然训练算法众多,但是SNN仍然没有一套成熟的训练算…...

CVPR2025新思路:把对抗扰动本身当成‘训练数据’,聊聊PSP-UAP背后的设计哲学

CVPR2025新思路:对抗扰动作为训练数据的革命性设计哲学 对抗样本研究领域正在经历一场范式转变——从单纯制造攻击工具到重新思考扰动本身的语义价值。PSP-UAP(Pseudo-Semantic Prior Universal Adversarial Perturbation)的突破性在于&#…...

深入解析PG332 ERNIC:基于RoCE v2的嵌入式RDMA加速引擎

1. PG332 ERNIC:重新定义嵌入式网络加速 第一次接触PG332 ERNIC这个IP核时,我正为一个工业视觉项目头疼——传统TCP/IP协议栈的延迟让机械臂控制指令总是慢半拍。直到测试了基于RoCE v2的ERNIC方案,端到端延迟直接从毫秒级降到微秒级…...

OpenClaw性能优化指南:Qwen3-14b_int4_awq模型调用加速技巧

OpenClaw性能优化指南:Qwen3-14b_int4_awq模型调用加速技巧 1. 为什么需要性能优化? 上周我尝试用OpenClaw自动处理100份PDF文档时,遇到了严重的性能瓶颈。原本预计2小时完成的任务,实际运行了整整8小时。经过排查发现ÿ…...

017、任务运行时间统计与运行状态跟踪:你的系统真的在“干活”吗?

017、任务运行时间统计与运行状态跟踪:你的系统真的在“干活”吗? 去年调试一个电机控制项目,系统偶尔会丢脉冲。用逻辑分析仪抓信号,发现任务调度周期出现了几毫秒的抖动。老板问我:“到底是哪个任务偷了时间?”我愣了半天——FreeRTOS默认只告诉我任务在运行,可没告诉…...

别再只用Speedtest了!自建LibreSpeed测速站,监控家庭宽带/公司内网真实表现

自建网络测速站:用LibreSpeed打造精准带宽监控系统 每次看到运营商宣传的"千兆宽带",你是否怀疑过实际使用中根本达不到承诺速度?公共测速网站的结果总让人将信将疑——它们可能被ISP特殊优化,或是受限于服务器位置。更…...

+vue 高校宿舍管理系统 宿舍可视化全能宿管(附源码))

计算机毕业设计 | 基于node(Koa)+vue 高校宿舍管理系统 宿舍可视化全能宿管(附源码)

1,绪论 1.1 项目背景 随着科技的发展,智能化管理越来越重要。大学生在宿舍的时间超过了1/3,因此良好的宿舍管理对学生的生活和学习极为关键。学生宿舍管理系统能够合理安排新生分配宿舍,不浪费公共资源,减轻学校管理…...

)

【数据结构与算法】第30篇:哈希表(Hash Table)

一、什么是哈希表1.1 基本思想哈希表通过哈希函数将关键字映射到数组的某个位置,实现快速访问。textkey → 哈希函数 → 数组下标 → 访问/存储示例:hash(key) key % 10key25 → 25%105 → 存入下标5key37 → 37%107 → 存入下标71.2 哈希冲突不同的key…...

视觉化看板工具怎么选?9 款创意团队项目协作平台优势分析

本文将深入对比 9 款支持视觉化看板的项目协作工具:Worktile、Trello、Asana、monday.com、ClickUp、Wrike、Notion、Jira、Teambition,重点分析它们在创意团队中的项目管理能力、适用场景、部署方式、协作效率与安全合规差异,帮助企业选型者…...

)

SPSS老版本用户必看:如何用R3.2.5实现高级统计分析(附完整语法示例)

SPSS老版本用户必看:如何用R3.2.5实现高级统计分析(附完整语法示例) 对于长期使用SPSS老版本的研究者来说,面对日益复杂的数据分析需求时,常常会遇到软件功能受限的困境。特别是在临床医学和社会科学研究中,…...

Koa2调试终极指南:10个高效定位代码问题的技巧

Koa2调试终极指南:10个高效定位代码问题的技巧 【免费下载链接】koa2-note 《Koa2进阶学习笔记》已完结🎄🎄🎄 项目地址: https://gitcode.com/gh_mirrors/ko/koa2-note GitHub 加速计划 / ko / koa2-note 项目中的《Koa2进…...