【FPGA项目】沙盘演练——基础版报文收发

第1个虚拟项目

前言

点灯开启了我们的FPGA之路,那么我们来继续沙盘演练。

用一个虚拟项目,来入门练习,以此步入数字逻辑的大门。

Key Words:FIFO 、SOF 、EOF、计数器、缓存、时序图、方案设计

一、项目要求

- 输入报文长度64~2048字节;

- 输入报文之间最小间隔为两拍;

- 输出报文的前两拍添加16bit报文长度信息;第1拍为报文长度高8位;第2拍为报文长度低8位;第3拍开始为输入报文;

| 信号 | I/O | 位宽 | 描述 |

| 系统接口信号 | |||

| i_sys_clk | I | 1 | 系统时钟,125Mhz |

| i_rst_n | I | 1 | 硬复位,低有效 |

| 输入接口信号 | |||

| i_sop_in | I | 1 | 输入报文头指示信号,高有效 |

| i_eop_in | I | 1 | 输入报文尾指示信号,高有效 |

| i_vld_in | I | 1 | 输入报文数据有效信号,高有效 |

| i_data_in | I | 8 | 输入报文数据 |

| 输出接口信号 | |||

| o_sop_out | O | 1 | 输出报文头指示信号,高有效 |

| o_eop_out | O | 1 | 输出报文尾指示信号,高有效 |

| o_vld_out | O | 1 | 输出报文数据有效信号,高有效 |

| o_data_out | O | 8 | 输出报文数据 |

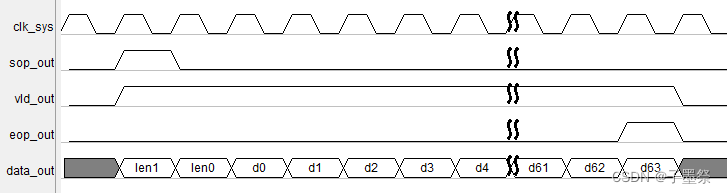

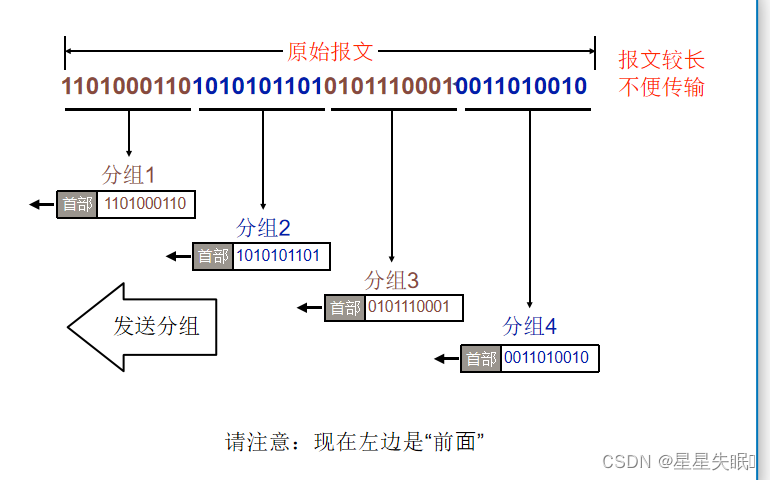

输入接口时序

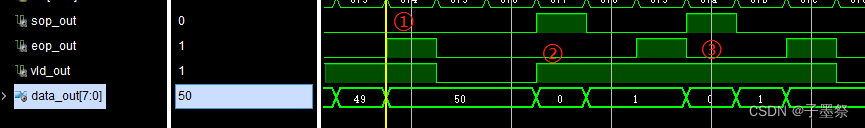

输出接口时序

二、项目方案设计

2.1项目需求

- 输出报文;

- 输出报文长度;

- 报文与报文长度输出满足时序要求;

2.2项目方案

1. 要求输出报文,且报文输出在报文长度输出之后,所以需要先对输入报文进行缓存,根据输入报文的位宽和长度范围,此处选择合适的同步FIFO即可;(如果是IC,那么就需要自己写FIFO,可以参考本博客的FIFO介绍)

这里项目提出了第1个要求,掌握FIFO的使用。

2. 要求输出报文长度,所以需要对输入报文长度进行计数,并将其缓存;

此处有坑,若只用寄存器对长度进行缓存,存在被后续报文长度覆盖的风险,故需要第2个FIFO对报文长度进行缓存。

3. 要求先输出报文长度然后紧跟着输出报文,此处需要对时序进行设计,需要掌握FIFO的读写时序,需要理解fpga的时钟沿采样。

理解:时钟沿采样及数据下一时钟沿变化。

2.3项目代码

module zmj0001(input sys_clk,input rst_n,input sop_in,input eop_in,input vld_in,input [7:0] data_in,output sop_out,output eop_out,output vld_out,output [7:0] data_out);当然这不是唯一的设计方案,可以先自行考虑设计及验证。

若需完整代码工程,🐟搜索“zmj0001”

项目重难点:

- FIFO的使用及时序的设计

- 考虑包间隔2 clk cycle

- 考虑长包+超短包的情况

时序设计可以用TimingDesigner软件,简单易用,需要的可以下载。

三、仿真验证

可以使用计数器来产生数据源data_in;

`timescale 1ns / 1psmodule zmj0001_tb();reg sys_clk ;

reg rst_n ;

reg [7 :0] data_in ;

reg vld_in ;

reg sop_in ;

reg eop_in ;

reg [11 :0] cnt ;

wire sop_out ;

wire eop_out ;

wire vld_out ;

wire [7:0] data_out ;initial

beginsys_clk = 0;rst_n = 0;#100rst_n = 1;

end

always #5 sys_clk = ~sys_clk; //100Mhz

//用计数器来产生data_in

always @(posedge sys_clk or negedge rst_n)beginif(~rst_n)cnt <= 12'b0;else if(cnt > 2048)cnt <= cnt;elsecnt <= cnt + 12'b1;

end

always @(posedge sys_clk or negedge rst_n)beginif(~rst_n)begindata_in <= 8'b0;sop_in <= 1'b0;eop_in <= 1'b0;vld_in <= 1'b0;endelse begindata_in <= 8'b0;sop_in <= 1'b0;eop_in <= 1'b0;vld_in <= 1'b0;if((cnt > 'd10 && cnt <= 'd60)|(cnt > 'd68 && cnt <= 'd668))begindata_in <= data_in + 1'b1;vld_in <= 1'b1;endif((cnt == 'd11)|(cnt == 'd69))sop_in <= 1'b1;if((cnt == 'd60)|(cnt == 'd668))eop_in <= 1'b1;if((cnt == 'd62) | (cnt == 'd63))begin //63 66data_in <= data_in + 1'b1;vld_in <= 1'b1;sop_in <= 1'b1;eop_in <= 1'b1;endend

end zmj0001 u_zmj0001(.sys_clk (sys_clk ), .rst_n (rst_n ),.sop_in (sop_in ),.eop_in (eop_in ),.vld_in (vld_in ),.data_in (data_in ),.sop_out (sop_out ),.eop_out (eop_out ),.vld_out (vld_out ),.data_out (data_out ));endmodule

具体modelsim使用及与vivado的联合仿真,脚本编写请参考其他博文,后续FPGA其他专栏再考虑写相关内容。

验证时重点关注边界情况。

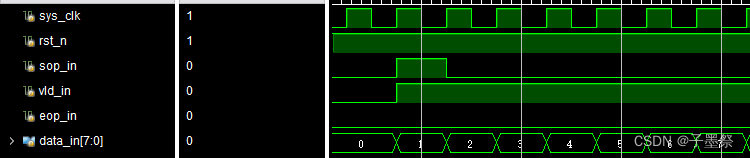

输入:

共4包数据,长包+超短包+超短包+长包,包间隔均为2clk cycle

data_in : 第1包:1-50的累加数;第2包:1;第3包:1;

输出:

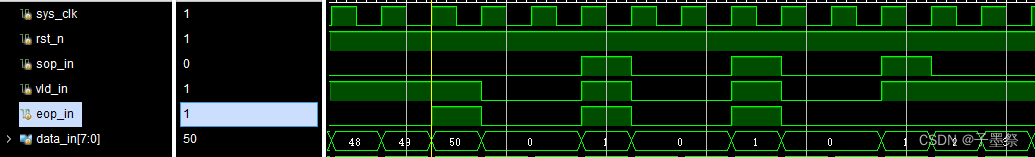

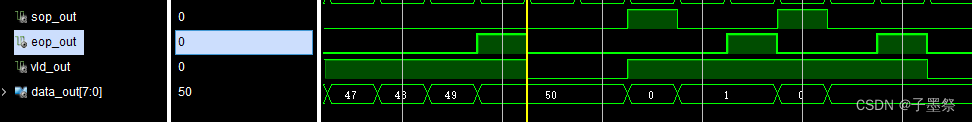

若包间隔<2 clk?

输入:

输出:

可以看到,本设计甚至支持背靠背的超短包输入。

四、项目收获

- 方案设计的重要性:任何项目都是始于方案设计,前期需要花大量的功夫去理清思路,方案设计完成,代码实现只不过是水到渠成的事情。

- 仿真的学习:通过本项目,完成了testbench的编写,仿真验证,是对自己设计的一次检验,是实际项目缩短调试时间的最佳利器。

- 对xilinx IP的使用,对datasheet的阅读学习。

- 对时序的理解,时钟是FPGA的心跳:任何时序操作都是发生在时钟的跳变沿。当采样发生在当前上升沿时刻,数据变化是发生在下一时刻的上升沿。

- 绘画时序图,TimingDesigner的使用。有了时序图,代码就很容易实现了。

五、进阶考虑

本次虚拟项目旨在用最简单的例子带大家了解数字逻辑设计的一些基本概念,所以很多东西是没有考虑的。比如:

- 如果包间隔小于2个时钟周期怎么办? -----握手与反压

- 如果输入数据有错误怎么办? -----CRC校验

- 如果需要跨时钟域传输呢? -----CDC处理

- 报文只是简单转发,如果需要做处理呢?-----数据处理

- ...

所以,下一篇将沿着这个思路展开,进阶版的虚拟项目,同样可以作为公司的入职培训。

咱们下期见!

相关文章:

【FPGA项目】沙盘演练——基础版报文收发

第1个虚拟项目 前言 点灯开启了我们的FPGA之路,那么我们来继续沙盘演练。 用一个虚拟项目,来入门练习,以此步入数字逻辑的…...

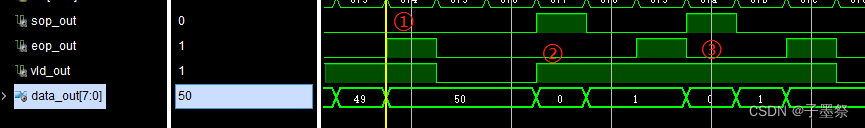

【C++技能树】继承概念与解析

Halo,这里是Ppeua。平时主要更新C,数据结构算法,Linux与ROS…感兴趣就关注我bua! 继承 0. 继承概念0.1 继承访问限定符 1. 基类和派生类对象赋值兼容转换2. 继承中的作用域3. 派生类中的默认成员函数4.友元5.继承中的静态成员6.菱…...

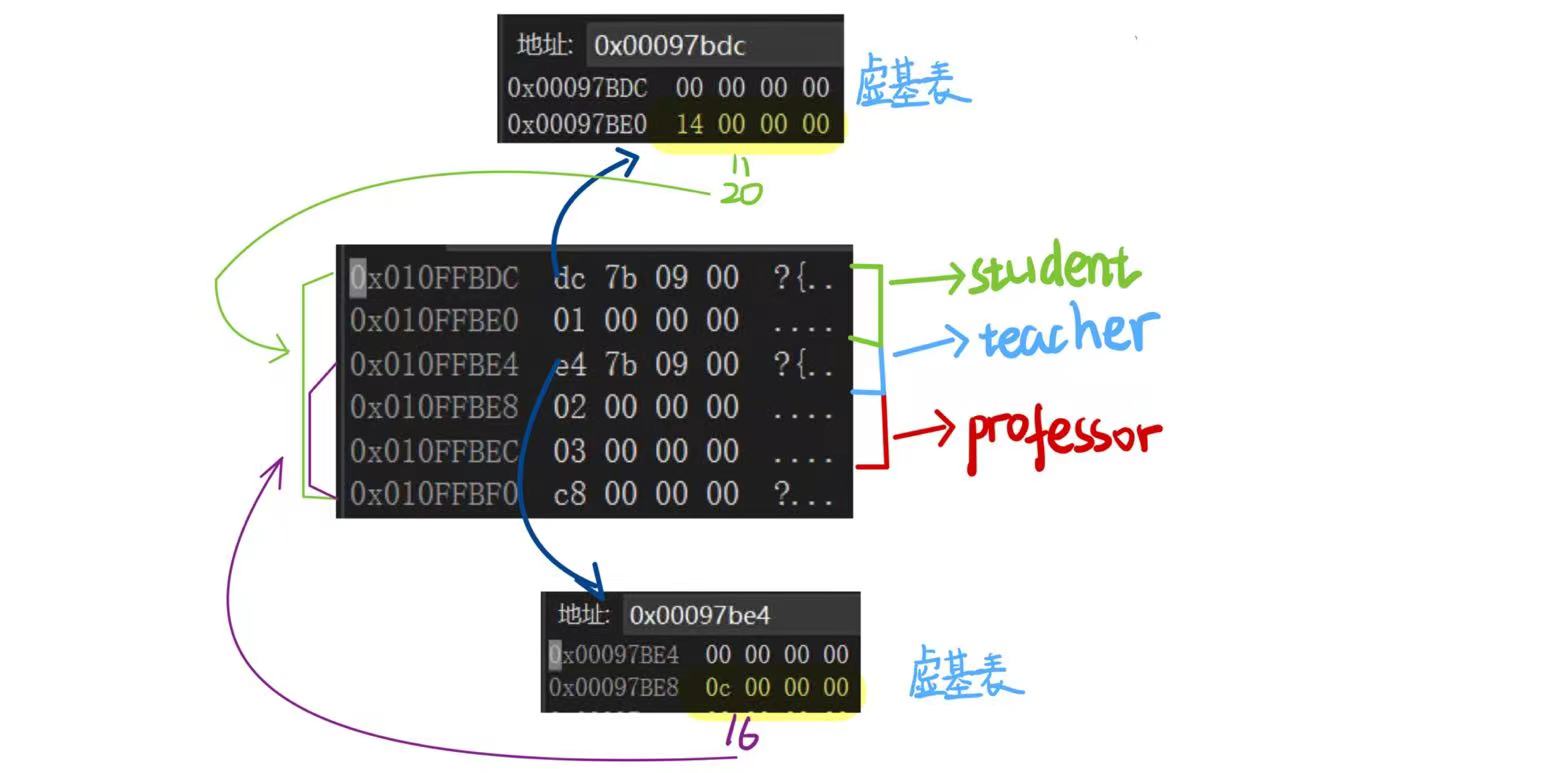

计算机网络 第二节

目录 一,计算机网络的分类 1.按照覆盖范围分 2.按照所属用途分 二,计算机网络逻辑组成部分 1.核心部分 (通信子网) 1.1电路交换 1.2 分组交换 两种方式的特点 重点 2.边缘部分 (资源子网) 进程通信的方…...

无涯教程-机器学习 - 矩阵图函数

相关性是有关两个变量之间变化的指示,在前面的章节中,无涯教程讨论了Pearson的相关系数以及相关的重要性,可以绘制相关矩阵以显示哪个变量相对于另一个变量具有较高或较低的相关性。 在以下示例中,Python脚本将为Pima印度糖尿病数…...

Redis 高可用与集群

Redis 高可用与集群 虽然 Redis 可以实现单机的数据持久化,但无论是 RDB 也好或者 AOF 也好,都解决 不了单点宕机问题,即一旦单台 redis 服务器本身出现系统故障、硬件故障等问题后, 就会直接造成数据的丢失,因此需要…...

修改文件名后Git仓上面并没有修改

场景: 我在本地将文件夹名称由Group → group ,执行git push 后,远程分支上的文件名称并没有修改。 原因: 是我绕过了git 直接使用了系统的重命名操作。 在 Git 中,对于已经存在的文件或文件夹进行大小写重命名是一个敏感的操作…...

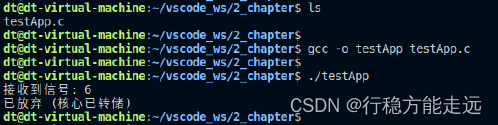

Linux 信号

目录 基本概念信号的分类可靠信号与不可靠信号实时信号与非实时信号 常见信号与默认行为进程对信号的处理signal()函数sigaction()函数 向进程发送信号kill()函数raise() alarm()和pause()函数alarm()函数pause()函数 信号集初始化信号集测试信号是否在信号集中 获取信号的描述…...

深入探讨梯度下降:优化机器学习的关键步骤(二)

文章目录 🍀引言🍀eta参数的调节🍀sklearn中的梯度下降 🍀引言 承接上篇,这篇主要有两个重点,一个是eta参数的调解;一个是在sklearn中实现梯度下降 在梯度下降算法中,学习率…...

高频算法面试题

合并两个有序数组 const merge (nums1, nums2) > {let p1 0;let p2 0;const result [];let cur;while (p1 < nums1.length || p2 < nums2.length) {if (p1 nums1.length) {cur nums2[p2];} else if (p2 nums2.length) {cur nums1[p1];} else if (nums1[p1] &…...

Hive-启动与操作(2)

🥇🥇【大数据学习记录篇】-持续更新中~🥇🥇 个人主页:beixi 本文章收录于专栏(点击传送):【大数据学习】 💓💓持续更新中,感谢各位前辈朋友们支持…...

css transition 指南

css transition 指南 在本文中,我们将深入了解 CSS transition,以及如何使用它们来创建丰富、精美的动画。 基本原理 我们创建动画时通常需要一些动画相关的 CSS。 下面是一个按钮在悬停时移动但没有动画的示例: <button class"…...

LeetCode 面试题 02.05. 链表求和

文章目录 一、题目二、C# 题解 一、题目 给定两个用链表表示的整数,每个节点包含一个数位。 这些数位是反向存放的,也就是个位排在链表首部。 编写函数对这两个整数求和,并用链表形式返回结果。 点击此处跳转题目。 示例: 输入&a…...

一米脸书营销软件

功能优势 JOIN ADVANTAGE HOME PAGE MARKETING 公共主页营销 可同时对多个账户公共主页评论,点赞等 可批量邀请多个好友对Facebook公共主页进行评论点赞等,也可批量登录小号对自己公共主页进行点赞。 GROUP MARKETING 小组营销 可批量针对不同账户进行…...

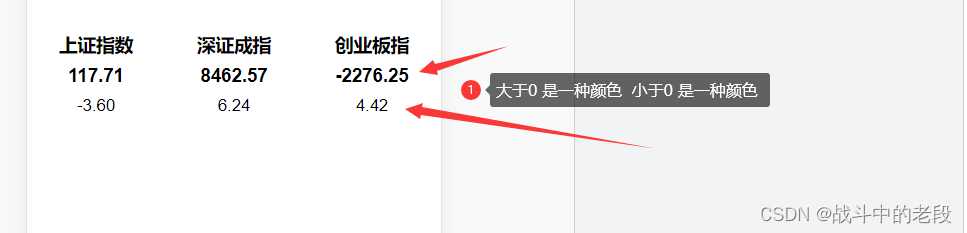

vue 根据数值判断颜色

1.首先style样式给两种颜色 用:class 三元运算符判断出一种颜色 第一步:在style里边设置两种颜色 .green{color: green; } .orange{color: orangered; }在取数据的标签 里边 判断一种颜色 :class"item.quote.current >0 ?orange: green"<van-gri…...

Hugging Face 实战系列 总目录

PyTorch 深度学习 开发环境搭建 全教程 Transformer:《Attention is all you need》 Hugging Face简介 1、Hugging Face实战-系列教程1:Tokenizer分词器(Transformer工具包/自然语言处理) Hungging Face实战-系列教程1:Tokenize…...

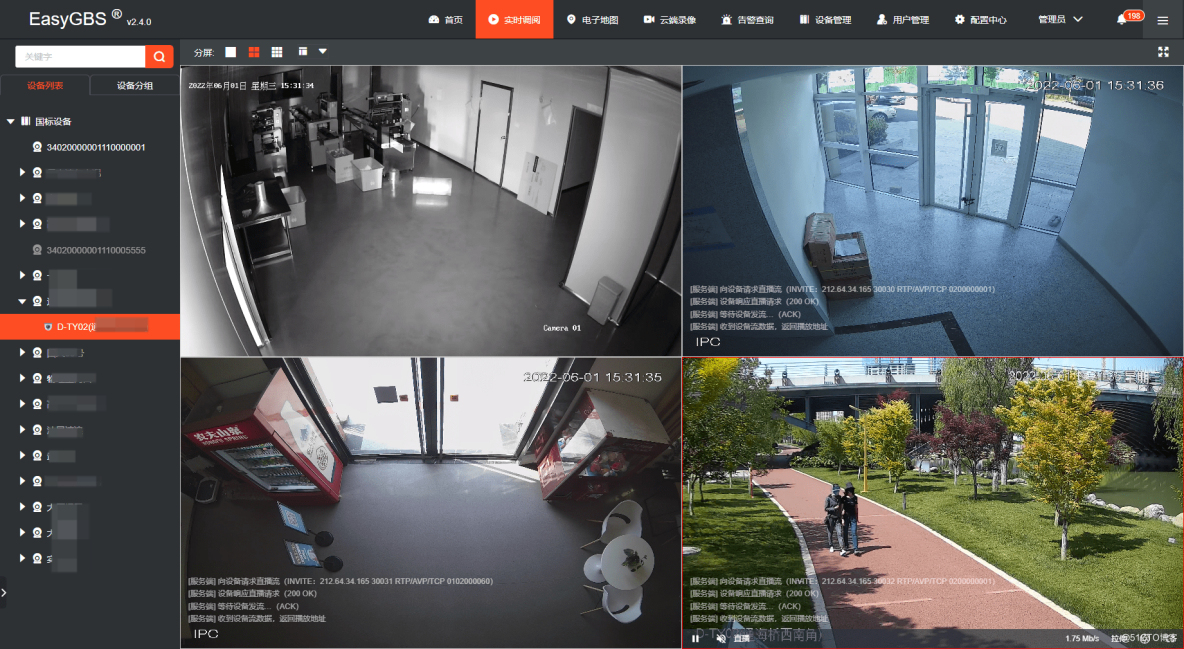

国标视频云服务EasyGBS国标视频平台迁移服务器后无法启动的问题解决方法

国标视频云服务EasyGBS支持设备/平台通过国标GB28181协议注册接入,并能实现视频的实时监控直播、录像、检索与回看、语音对讲、云存储、告警、平台级联等功能。平台部署简单、可拓展性强,支持将接入的视频流进行全终端、全平台分发,分发的视频…...

HTML <th> 标签

实例 普通的 HTML 表格,包含两行两列: <table border="1"><tr><th>Company</th><th>Address</th></tr><tr><td>Apple, Inc.</td><td>1 Infinite Loop Cupertino, CA 95014</td></tr…...

HTTP/1.1协议中的响应报文

2023年8月30日,周三下午 目录 概述响应报文示例详述 概述 HTTP/1.1协议的响应报文由以下几个部分组成: 状态行(Status Line)响应头部(Response Headers)空行(Blank Line)响应体&a…...

TDengine函数大全-选择函数

以下内容来自 TDengine 官方文档 及 GitHub 内容 。 以下所有示例基于 TDengine 3.1.0.3 TDengine函数大全 1.数学函数 2.字符串函数 3.转换函数 4.时间和日期函数 5.聚合函数 6.选择函数 7.时序数据库特有函数 8.系统函数 选择函数 TDengine函数大全BOTTOMFIRSTINTERPLASTLAS…...

非关系型数据库Redis的安装

一、关系型数据库与非关系型数据库的区别:---------面试高频率问题 1、首先了解一下 什么是关系型数据库? 关系型数据库最典型的数据结构是表,由二维表及其之间的联系所组成的一个数据组织。 优点: 易于维护:都是使用…...

STM32duino GNSS库深度解析:Teseo LIV3F驱动与NMEA协议实现

1. 项目概述STM32duino X-NUCLEO-GNSS1A1 是一款面向 STM32 平台的 Arduino 兼容库,专为意法半导体(STMicroelectronics)推出的 X-NUCLEO-GNSS1A1 GNSS 扩展板设计。该扩展板基于意法半导体自研的 Teseo LIV3F 单芯片 GNSS 接收器,…...

DICOM序列实时渲染从28fps到126fps:C++无锁队列+GPU命令缓冲复用+ROI局部重绘的工业级调优日志

第一章:DICOM序列实时渲染性能跃迁全景概览 现代医学影像工作流对DICOM序列的实时可视化提出严苛要求:从百层CT扫描到高分辨率MRI动态序列,传统CPU软渲染方案常遭遇帧率跌破15 FPS、交互延迟超300ms的瓶颈。近年来,GPU加速管线、零…...

先被日本汽车打败,再被中国汽车冲击,欧洲车面临崩盘,已累计裁员50万人!

大众汽车在公布2025年的利润腰斩之后,发布了进一步裁员计划,到2030年将削减5万个工作岗位,占它当下员工总人数的比例大约7.5%,由此业界人士统计了近几年来欧洲诸多车企以及汽车供应链企业宣布的裁员人数,发现欧洲汽车行…...

AI 模型推理中的延迟分析与测试

AI 模型推理中的延迟分析与测试 在人工智能技术快速发展的今天,AI 模型的推理性能成为影响实际应用效果的关键因素之一。无论是智能语音助手、自动驾驶,还是实时推荐系统,延迟的高低直接决定了用户体验的好坏。对 AI 模型推理的延迟进行分析…...

SoftSPIB:支持任意位宽的软件模拟SPI库

1. SoftSPIB:面向非字节对齐SPI通信的软件实现方案1.1 问题起源:硬件SPI的固有局限性在嵌入式系统开发中,SPI(Serial Peripheral Interface)作为最常用的同步串行总线协议,其标准实现通常以8位(…...

效率倍增:用快马AI生成服务器批量管理工具,告别重复劳动

最近在团队里负责服务器运维工作,经常需要同时管理几十台服务器。每次登录、执行重复命令、检查状态都要耗费大量时间,直到发现了用InsCode(快马)平台快速搭建批量管理工具的方法,效率直接翻倍。今天就把这个自动化管理方案分享给大家。 痛点…...

)

CDA Level-2 考试全攻略:从报名到备考的保姆级教程(含最新题库资源)

CDA Level-2 考试全攻略:从报名到备考的保姆级教程 最近两年数据分析师认证热度持续攀升,CDA认证作为国内认可度较高的专业证书之一,Level-2考试通过率常年维持在40%左右。不同于Level-1的基础考核,Level-2更注重实际分析能力与统…...

如何通过哈氏训练提升孩子的学习能力以应对多动症表现和作业拖延症?

如何运用哈氏训练助力孩子克服多动症表现与作业拖延 哈氏训练是一种有效的应对策略,尤其对有多动症表现和作业拖延症的孩子。首先,这种训练方法可以帮助孩子建立稳定的日常作息,提高他们的注意力和自我控制能力。通过结构化的活动和渐进式的任…...

别再只用Chat了!深度挖掘Cursor的‘规则’与‘上下文’功能,打造你的专属AI编程助手

解锁Cursor的隐藏力量:从代码助手到项目级智能架构师 在AI编程工具爆发的时代,大多数开发者仅仅停留在基础对话和代码补全的层面。但Cursor的真正价值远不止于此——它能够成为你项目架构的智能协作者、团队规范的自动化执行者,以及复杂工程问…...

)

【OpenClaw从入门到精通】第54篇:物理隔离“龙虾”——傻福虾盘与Docker沙箱实战对比(2026实测版)

摘要:2026年工信部NVDB平台及CNCERT指南明确要求:OpenClaw需在隔离环境中部署,严禁在办公设备直接运行。本文聚焦两大主流隔离方案——物理隔离(闲置旧电脑/专用硬件盒子)与Docker沙箱,系统拆解从原理到实操的全流程。包含3套完整部署案例、15+安全配置命令、容器逃逸风险…...