Vivado详细使用教程 | LED闪烁示例

文章目录

- 整体流程

- 第一步:新建工程

- 第二步:设计输入

- 第三步:功能仿真

- 第四步:分析与综合

- 第五步:约束输入

- 第六步:设计实现

- 第七步:下载比特流

整体流程

打开软甲------>新建工程------->设计输入------->分析与综合------->约束输入------->设计实现-------->生成和下载比特流

第一步:新建工程

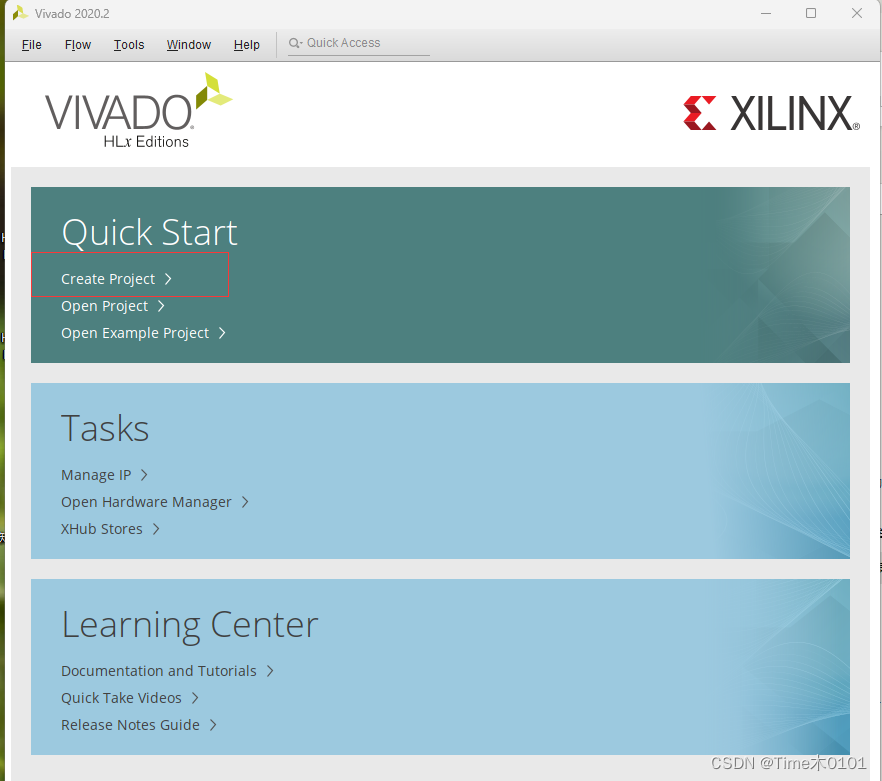

1、这里使用的是Vivado 2020.2版本,打开软件,点击“create Project”创建一个新的工程。

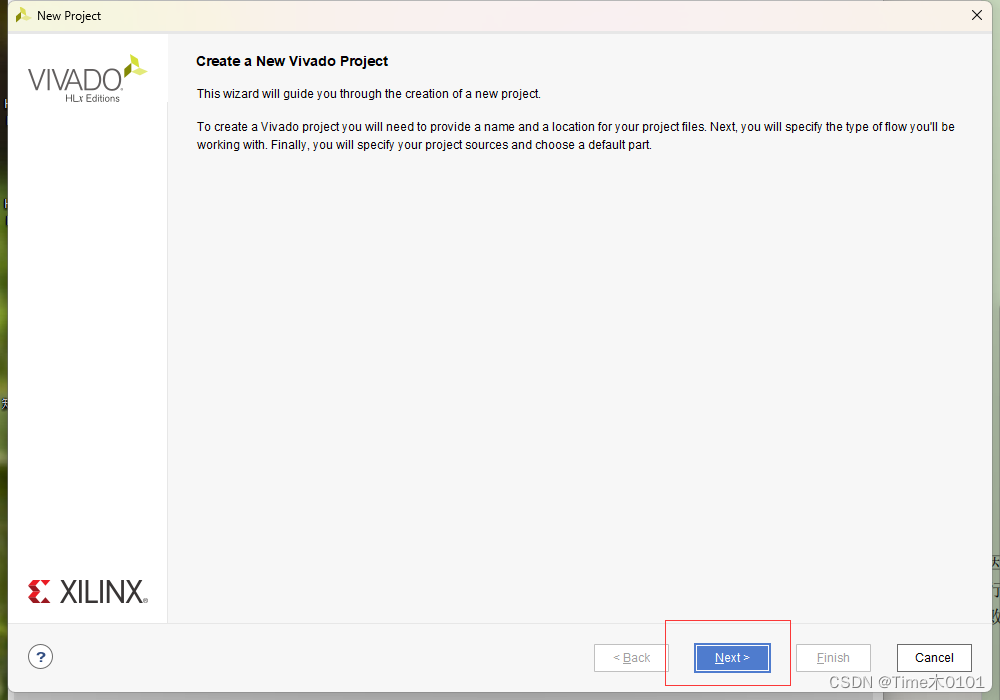

2、点击下一步

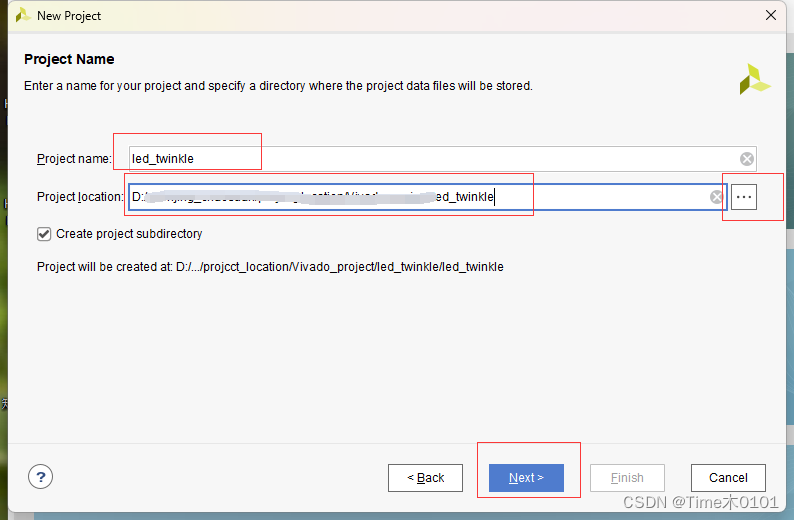

3、输入工程的名称和路径,名称可以贴近这次工程的功能,例如这次的”led_twinkle“

路径地址不包含中文、空格或者其他一些特殊符号。

这里会默认勾选了“Create project subdirectory”选项,Vivado会在所选工程目录下自动创建一个与工程名同名的文件夹,用于存放工程内的各种文件。Vivado 会自动管理工程文件夹内的各种工程文件,并创建相应的子目录,这为大家的开发工作带来了很大的便捷。

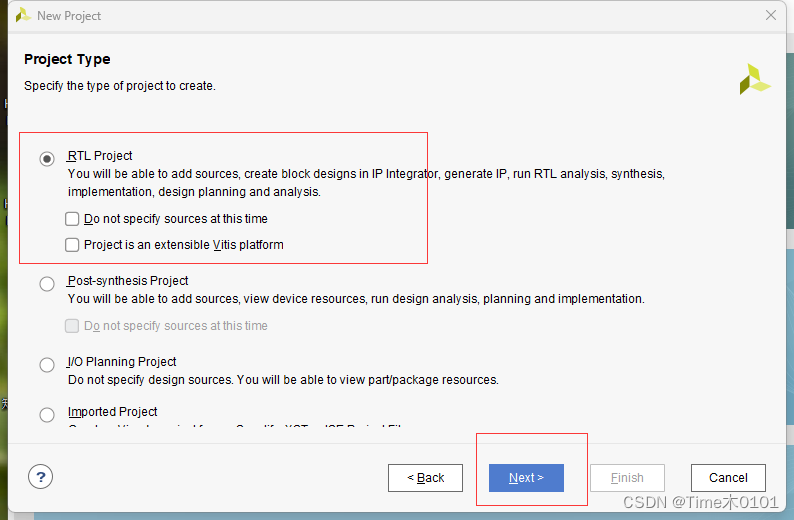

继续点击“Next”,接下来是工程类型的选择,这里选择“RTL Project”,如下图所示:

4、选择RTL Project。

各个选项的含义:

“RTLProject”是指按照正常设计流程所选择的类型,这也是常用的一种类型,“RTL Project”下的“Do not specify sources at this time”用于设置是否在创建工程向导的过程中添加设计文件,如果勾选后,则不创建或者添加设计文件,下面一个不用管。

“Post-synthesis Project”在导入第三方工具所产生的综合后网表时才选择;

“I/O Planning Project”一般用于在开始RTL 设计之前,创建一个用于早期IO规划和器件开发的空工程;“Imported Project”用于从ISE、XST或Synopsys Synplify导入现有的工程源文件;“Example Project”是指创建一个Vivado提供的工程模板。

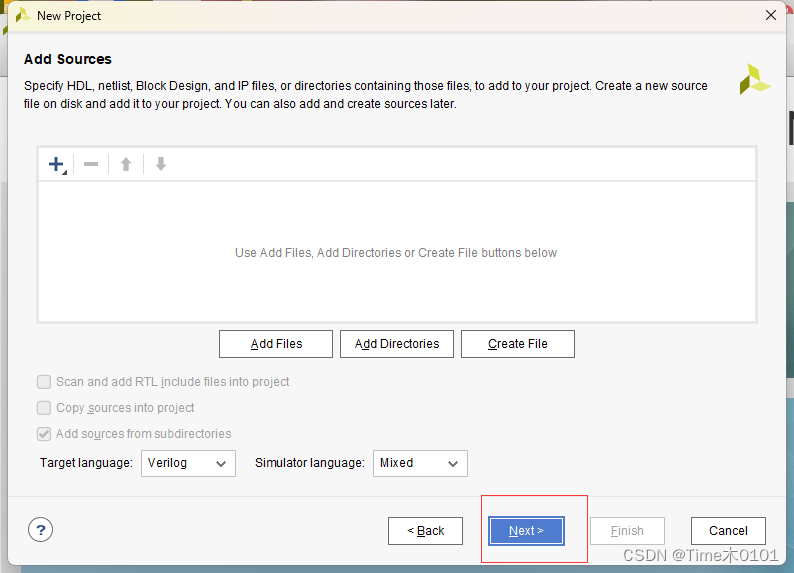

5、选择了“RTL Project”后,点击“Next”,进入添加源文件页面。

如果勾选“RTL Project”下的“Do not specify sources at this time”,则不会出现添加源文件的界面。

在弹出添加源文件的界面后,可以在此处创建/添加源文件,当然也可以直接点击“Next”,创建完工程后再创建/添加源文件。

这里先不添加,直接点击“Next”,如下图所示:

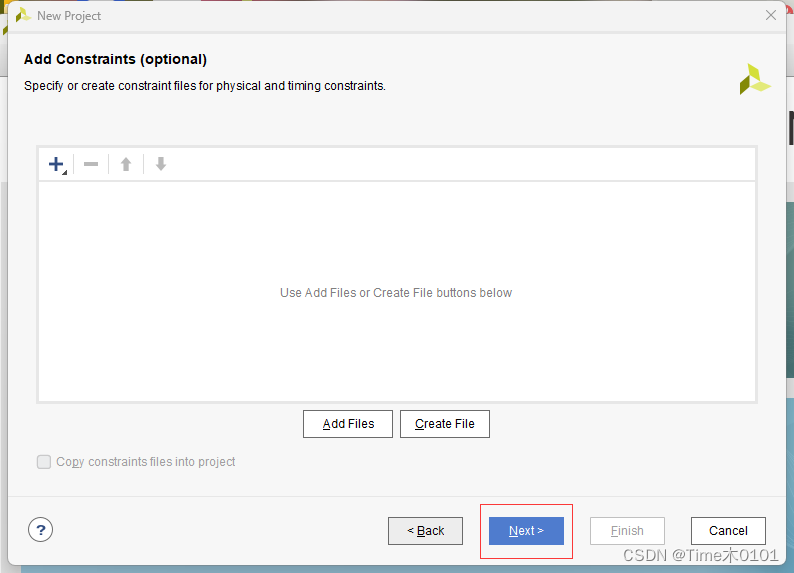

6、接下来是添加约束文件,直接点击“Next”,在创建完工程后创建/添加约束文件.

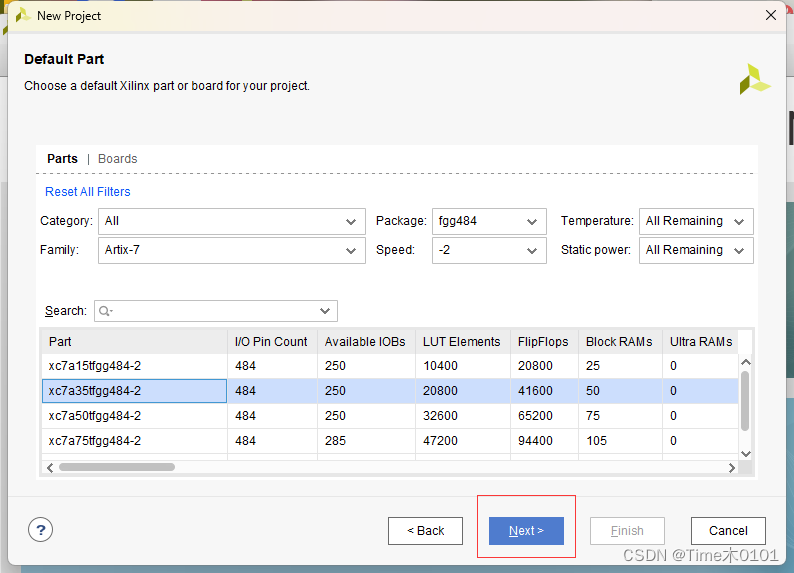

7、接下来是选择器件型号,“Family”一栏选择“Artix-7”、“Package”一栏选择“fgg484”(A7_200T时选择"fbg484”) 、“Speed”一栏选择“-2”,此时下面的器件列表就会自动筛选出符合以上设置条件的器件。

(也可根据实际进行选择)

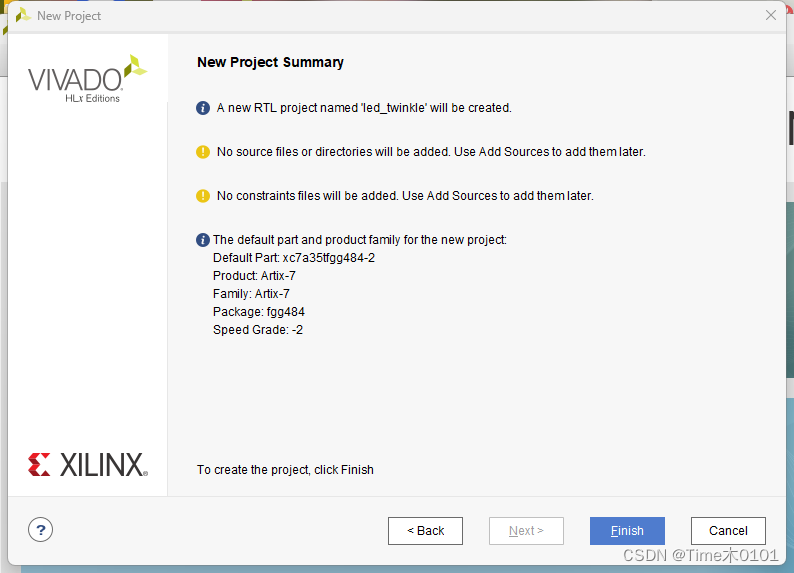

8、检查一下,finish

9、进入工程主界面

10、下面介绍 Vivado 工程主界面中的几个主要子窗口:

(1)Flow Navigator:Flow Navigator 提供对命令和工具的访问,其包含从设计输入到生成比特流的整

个过程。 在点击了相应的命令时,整个 Vivado 工程主界面的各个子窗口可能会作出相应的更改。

(2)数据窗口区域:默认情况下,Vivado IDE 的这个区域显示与设计源文件和数据相关的信息,例如:

• Sources 窗口:显示层次结构(Hierarchy)、IP 源文件(IP Sources)、库(Libraries)和编译顺序(Compile

Order)的视图。

• Netlist 窗口:提供分析后的(elaborated)或综合后的(synthesized)逻辑设计的分层视图。

(3)Properties 窗口:显示有关所选逻辑对象或器件资源的信息。

(4)工作空间(Workspace):工作区显示了具有图形界面的窗口和需要更多屏幕空间的窗口,包括:

• 用于显示和编辑基于文本的文件和报告的 Text Editor。

• 原理图(Schematic)窗口

• 器件(Device)窗口

• 封装(Package)窗口

(5)结果窗口区域:在 Vivado IDE 中所运行的命令的状态和结果,显示在结果窗口区域中,这是一组

子窗口的集合。在运行命令、生成消息、创建日志文件和报表文件时,相关信息将显示在此区域。默认情

况下,此区域包括以下窗口:

• Tcl Console:允许您输入 Tcl 命令,并查看以前的命令和输出的历史记录。

• Messages:显示当前设计的所有消息,按进程和严重性分类,包括“Error”、“Critical Warning”、

“Warning”等等

• Log:显示由综合、实现和仿真运行创建的日志文件。

• Reports:提供对整个设计流程中的活动运行所生成的报告的快速访问。

• Designs Runs:管理当前工程的运行。

(6)主工具栏:主工具栏提供了对 Vivado IDE 中最常用命令的单击访问。

(7)主菜单:主菜单栏提供对 Vivado IDE 命令的访问。常用的命令会一直显示(例如,File > Project >

Open),而其他命令只在设计活动时显示(例如,Reports > ReportDRC)。一些菜单命令有一个相关的键盘快捷方式,该快捷方式列在该菜单命令的旁边。

(8)窗口布局(Layout)选择器:Vivado IDE 提供预定义的窗口布局,以方便设计过程中的各种任务。

布局选择器使大家能够轻松地更改窗口布局,大家也可以使用菜单栏中的“Layout”菜单来更改窗口布局。

第二步:设计输入

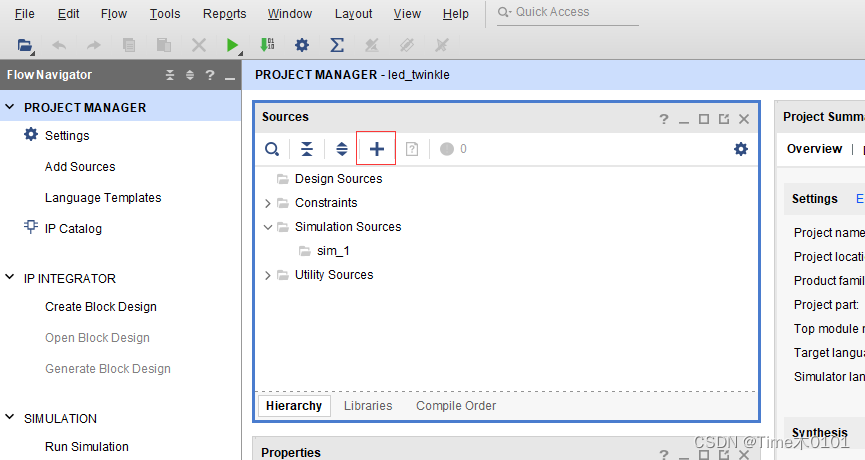

1、创建顶层文件,如图点“+”。

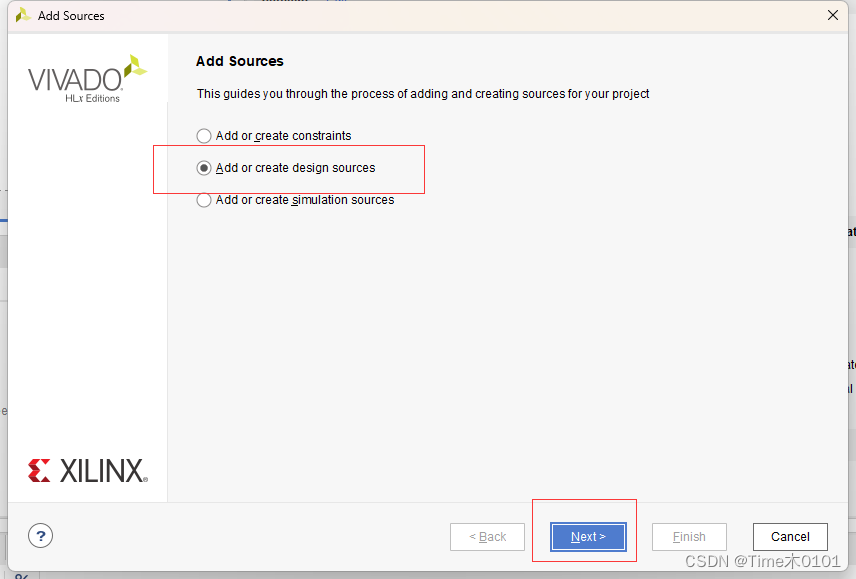

2、如图选择第二个添加设计文件,next。

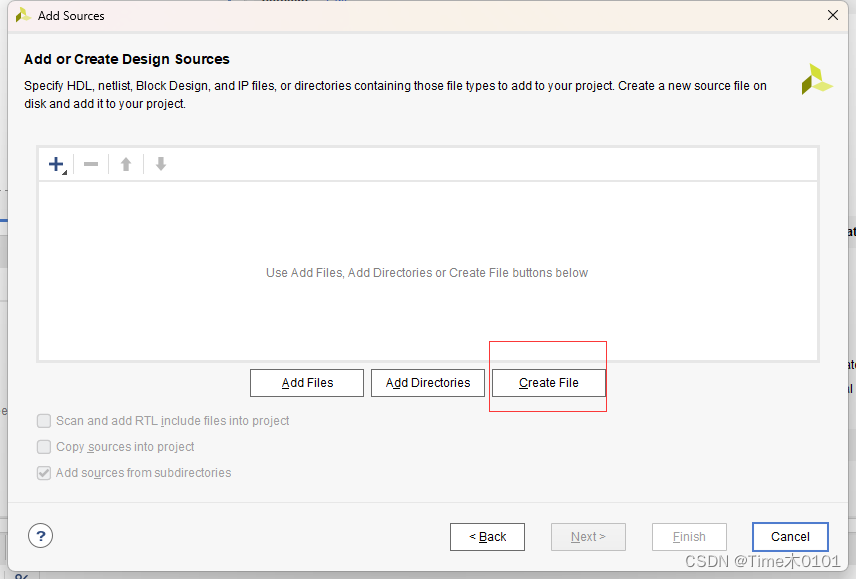

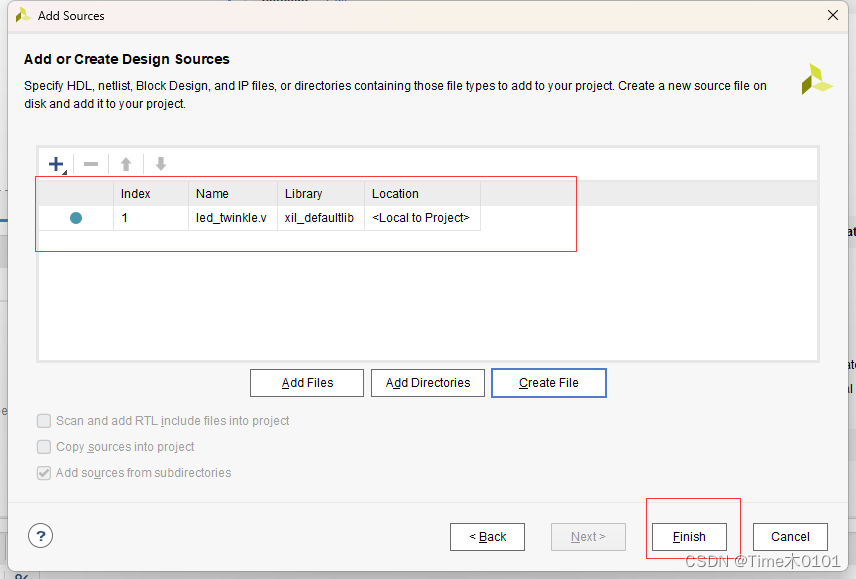

3、如图点创建文件

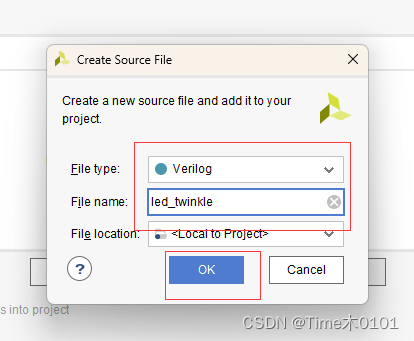

4、填写源文件名称“led_twinkle”,可根据实际文件更改,然后ok。

这时可以看到创建的源文件,finish。

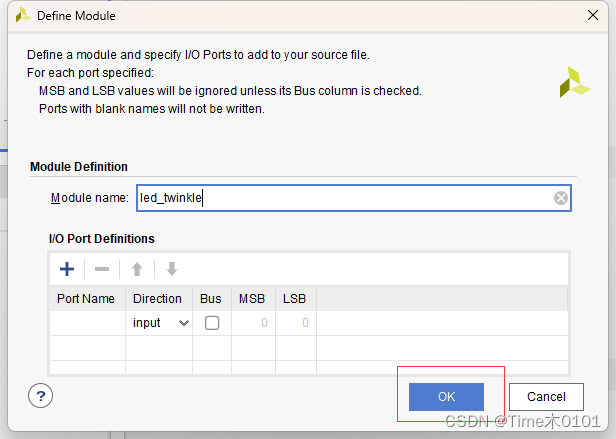

5、然后“OK”

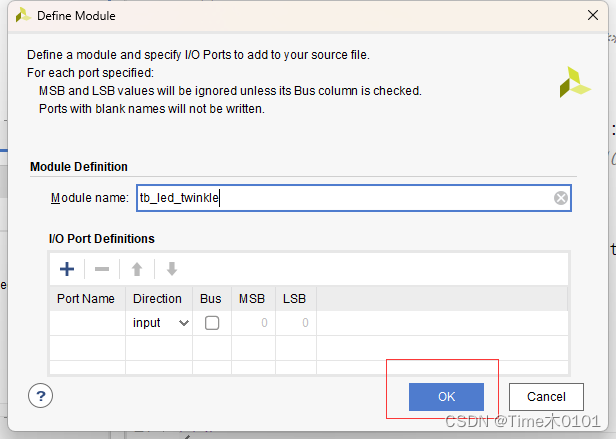

这个窗口用于设置源文件的模块名称和端口列表,Vivado 会根据在此窗口中的设置,自动地在 HDL 源文

件中写入相应的 verilog 语句。我们会手动输入代码,所以这里不作任何设置,直接点击 OK 即可。

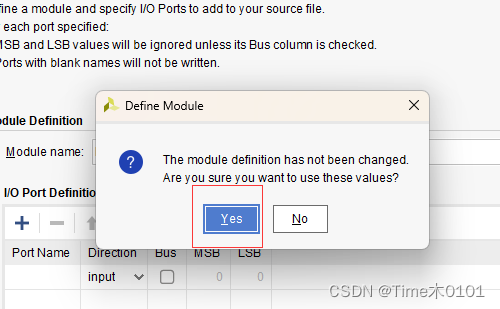

若出现此窗口“YES”

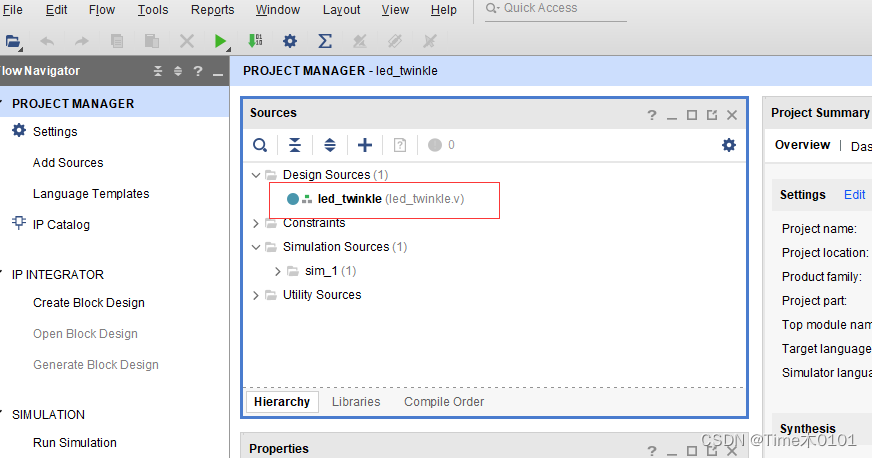

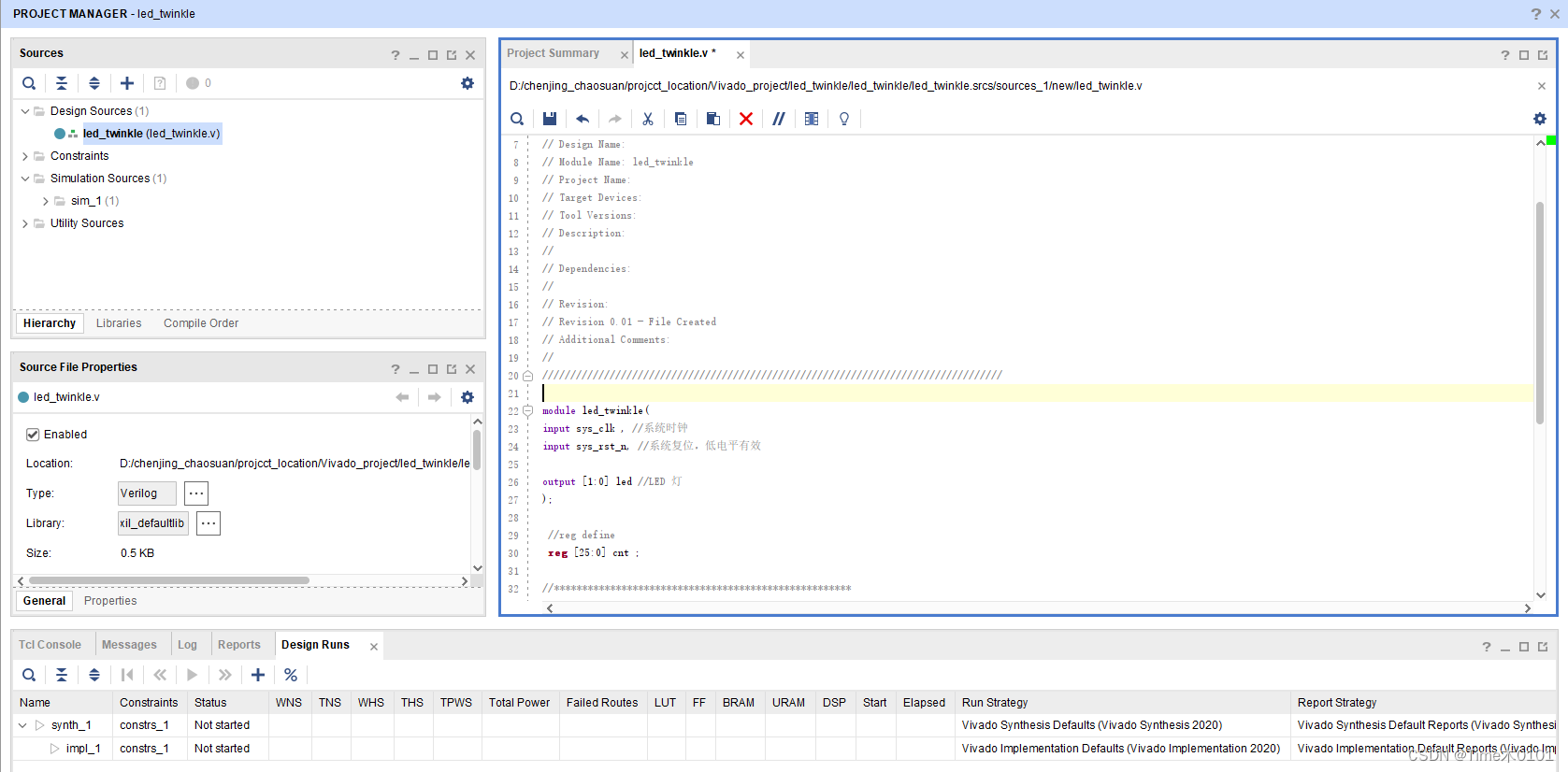

6、这时“Sources”窗口就出现了源文件。

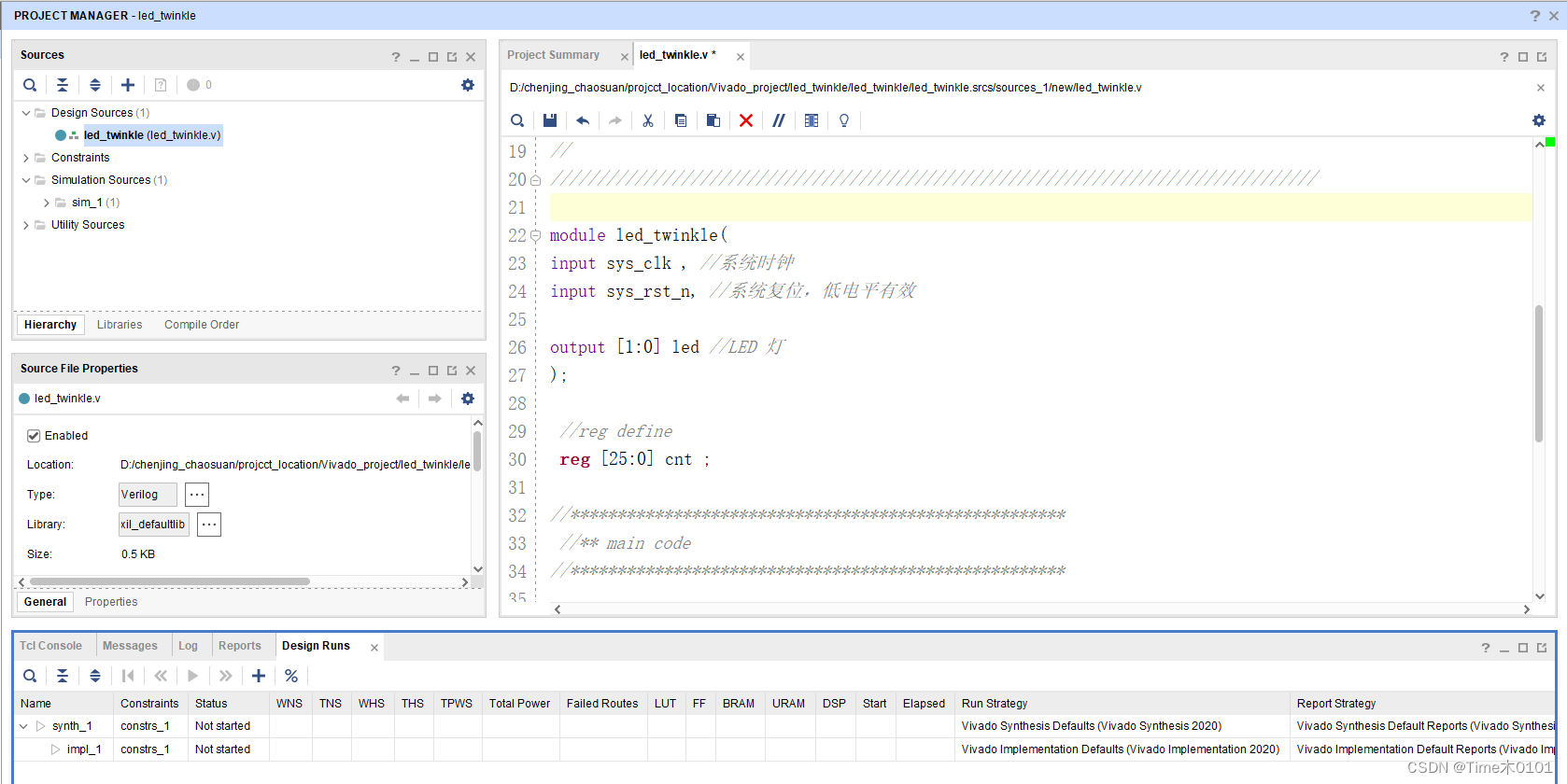

7、双击打开源文件,将其中的代码替换为如下Led登闪烁代码。

module led_twinkle(input sys_clk , //系统时钟input sys_rst_n, //系统复位,低电平有效output [1:0] led //LED 灯

);//reg definereg [25:0] cnt ;//*****************************************************//** main code

//*****************************************************//对计数器的值进行判断,以输出 LED 的状态

assign led = (cnt < 26'd2500_0000) ? 2'b01 : 2'b10 ;

//assign led = (cnt < 26'd5) ? 2'b01 : 2'b10 ; //仅用于仿真//计数器在 0~5000_000 之间进行计数

always @ (posedge sys_clk or negedge sys_rst_n) beginif(!sys_rst_n)cnt <= 26'd0;else if(cnt < 26'd5000_0000)

// else if(cnt < 26'd10) //仅用于仿真cnt <= cnt + 1'b1;elsecnt <= 26'd0;

endendmodule

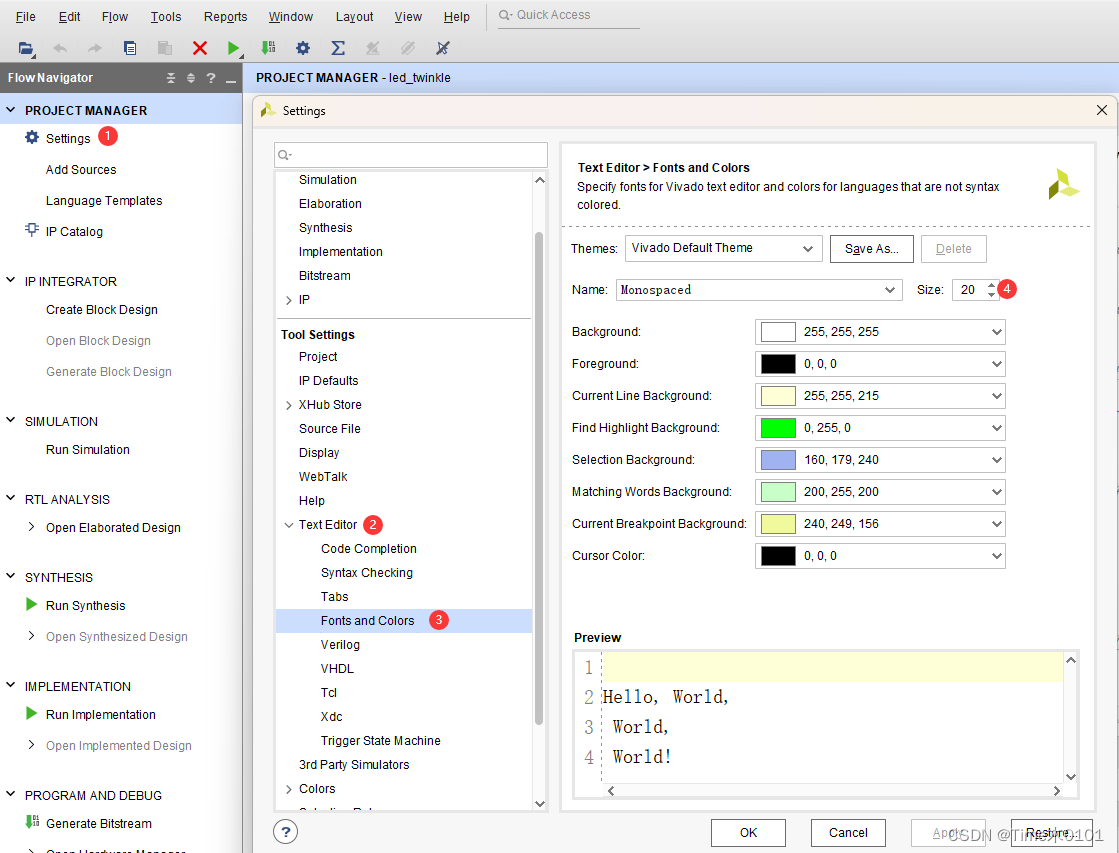

8、可以调整字体大小,如图。

9、写完代码记得保存,如图按钮。保存后vivado会进行语法检查。在大多数情况下,Vivado IDE 会自动识别设计的顶层模块,当然,用户也可以手动指定顶层模块。从“Sources”窗口的右击菜单中选择“Set as Top”来手动定义顶级模块

第三步:功能仿真

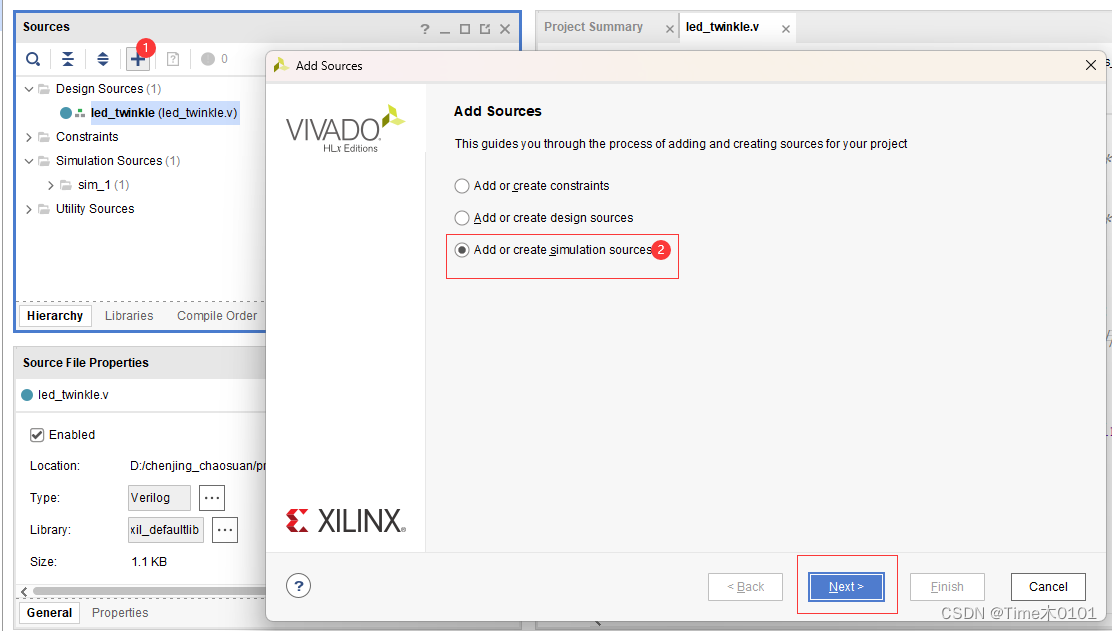

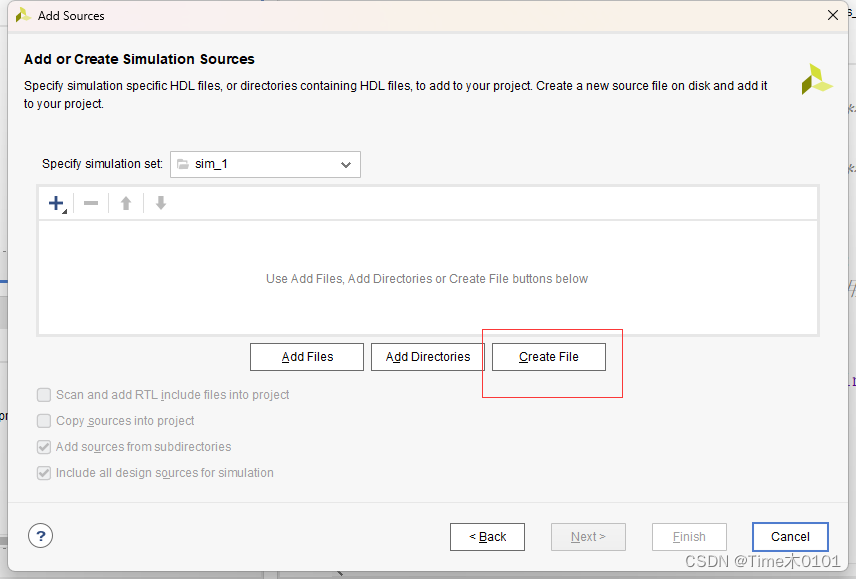

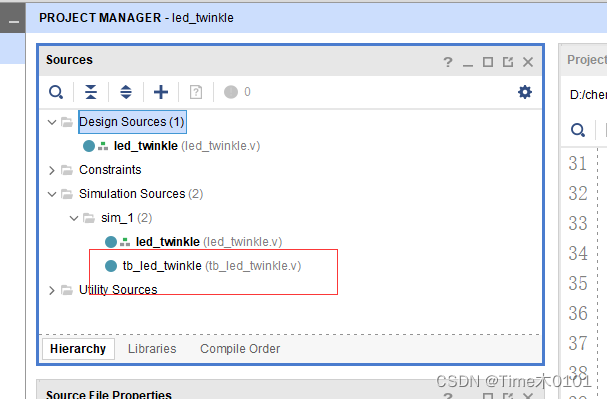

1、我们开始在 Vivado IDE 中进行仿真,首先创建一个 TestBench。我们点击“Sources”窗口中的

“+”号(Add Sources 命令),在弹出的窗口中选择“Add or Create Simulation Sources”,next.

2、直接"create file"

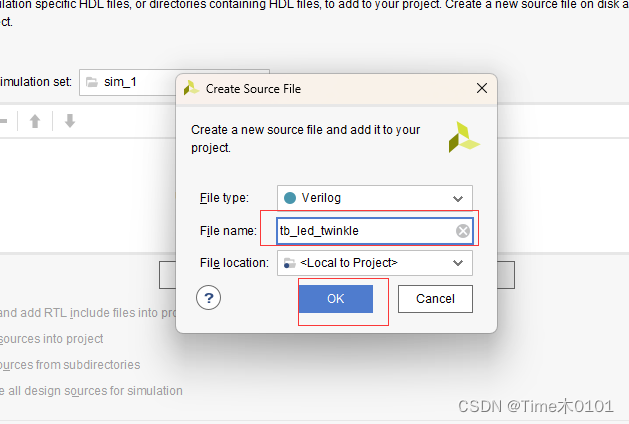

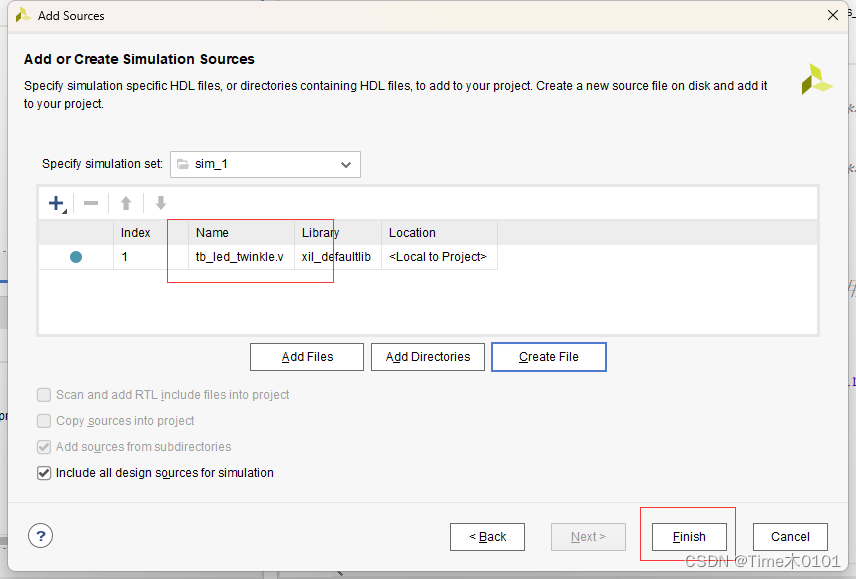

3、输入TestBench的文件名称“tb_led_twinkle”,一般测试文件会在源文件名称前加tb_。这个文件只用于仿真,不能用于设计的综合和实现。然后“OK”

“finish”

“OK”完成TestBench源文件的创建。

如果弹出窗口直接Yes.

这里就可以看到创建的文件了。

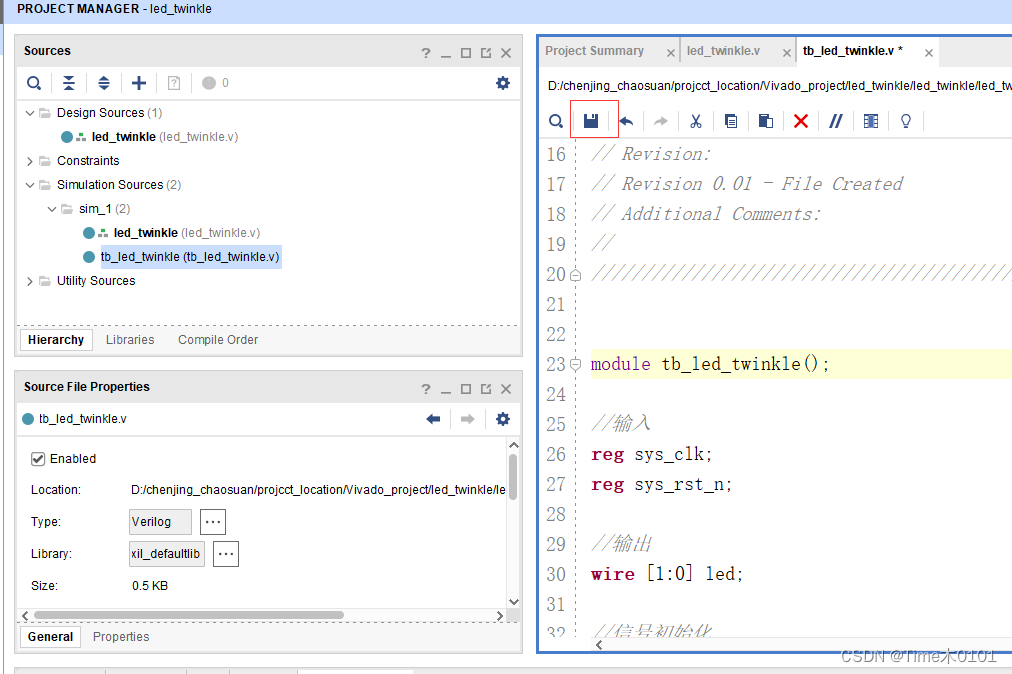

4、双击替换成下面的代码。

`timescale 1ns / 1psmodule tb_led_twinkle();//输入

reg sys_clk;

reg sys_rst_n;//输出

wire [1:0] led;//信号初始化

initial beginsys_clk = 1'b0;sys_rst_n = 1'b0;#200sys_rst_n = 1'b1;

end//生成时钟

always #10 sys_clk = ~sys_clk;//例化待测设计

led_twinkle u_led_twinkle(.sys_clk (sys_clk),.sys_rst_n (sys_rst_n),.led (led)

);endmodule

为了让读者能够更好的理解,这里我们就简单介绍一下 TestBench 源代码。

进行仿真首先要规定时间单位,我们建议大家最好在 Testbench 里面统一规定时间单位,不要在工程代码里定义,因为不同的模块如果时间单位不同可能会为仿真带来一些问题。

代码的第 1 行的 timescale 是 Verilog 语法中的不可综合语法,用于定义仿真的时间表示仿真的单位时间为 1ns,精度为 1ps,这是 Xilinx 官方推荐的仿真单位时间和精度。

代码的第 3 行就是 TestBench 的模块名定义,第 6 行至第 10 行是我们的数据类型定义,到了第 13~18 行是信号的初始化,第 21 行是时钟信号的生成,50MHz 时钟对应周期为 20ns,第 24 行是被测模块的调用。

记得保存。

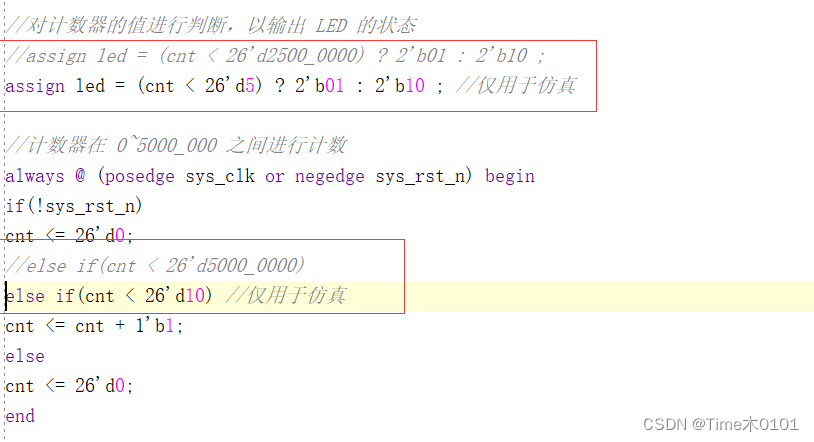

在开始仿真之前,大家有一点需要注意,我们在 Vivado 软件中实现的功能是 LED 闪烁效果,它的间隔

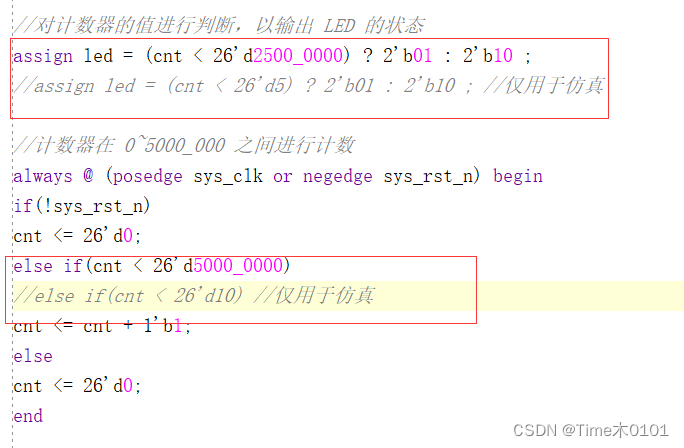

时间是 500ms,如果我们想要仿真这个功能,那么我们仿真软件运行时间最低就是 500ms。这 500ms 在我们看来是很短很短的,而对仿真软件来说是很漫长的,毕竟我们的仿真时间单位可是 1ns。为了便于我们仿真,这里我们需要稍微改动“led_twinkle.v”文件的代码,将计时器 counter 的最大计时值设为 10,如下图所示:

到led_twinkle.v文件改一下注释位置即可。

待仿真结束后进行分析和综合时,再将标记为“仅用于仿真的”的语句注释掉或者直接删除。

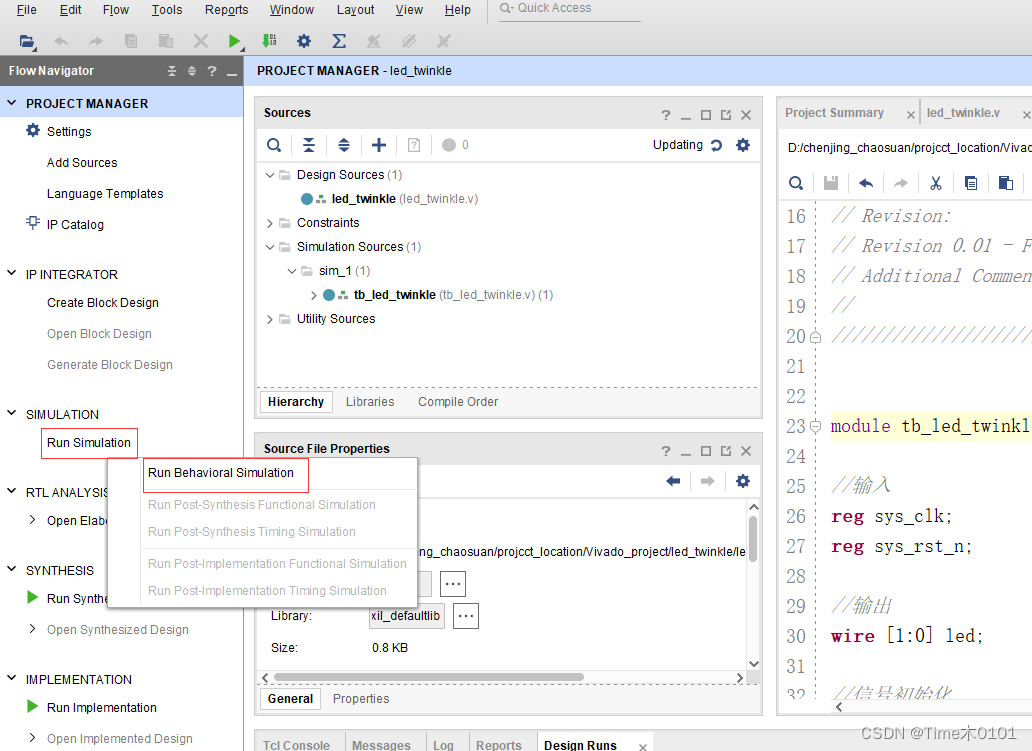

5、如图点击进行仿真。

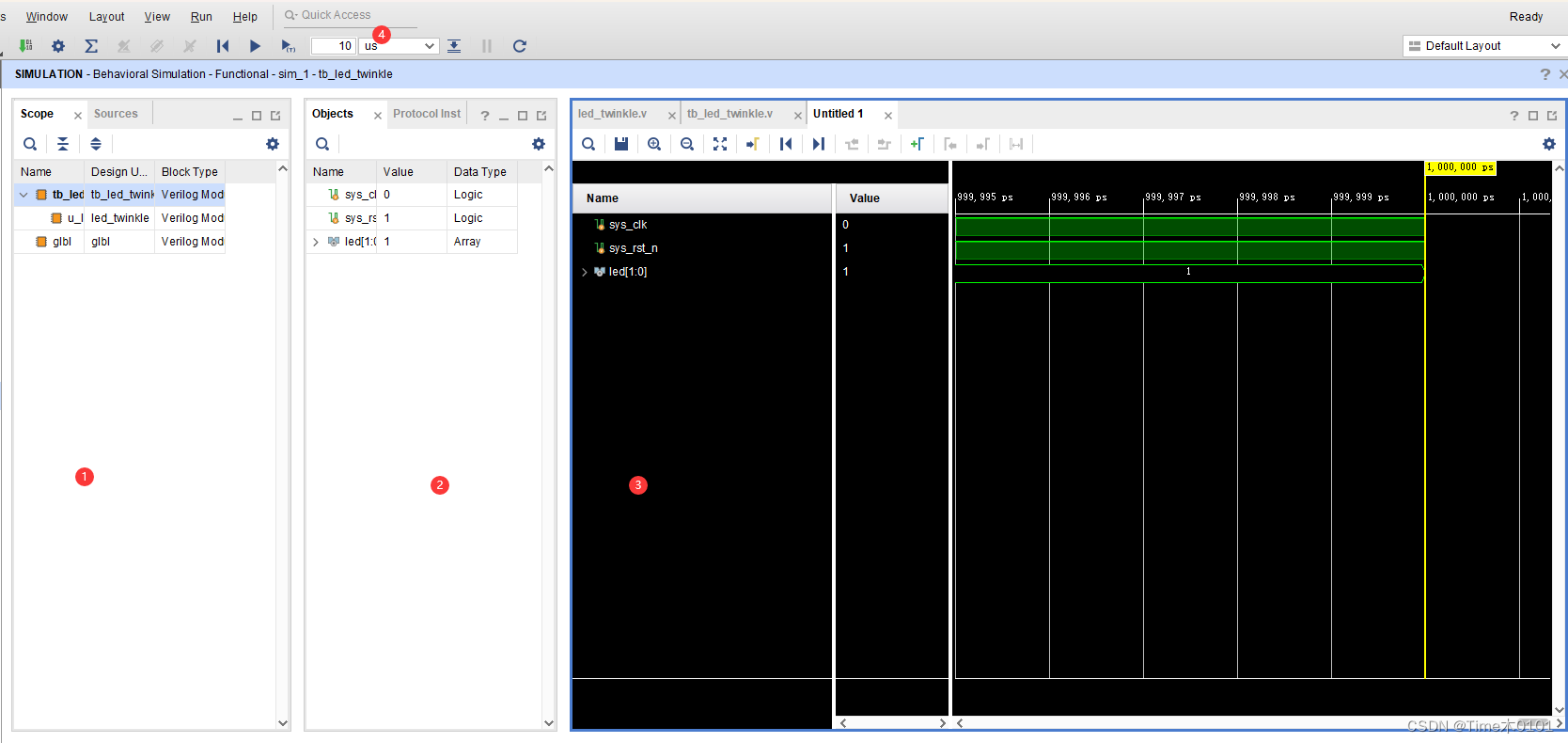

6、到了仿真界面

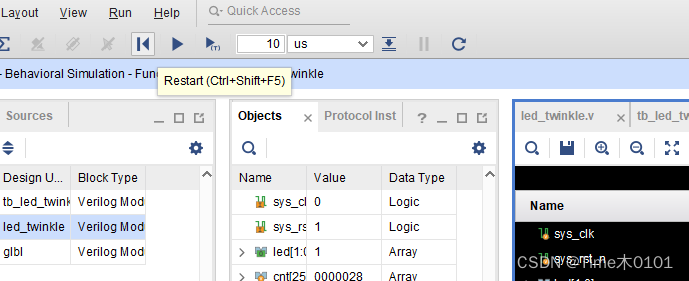

1、下面分别介绍仿真界面中的各个子窗口:

(1)Scope 窗口:Scope(范围)是 HDL 设计的层次划分。在 Scope 窗口中,您可以看到设计层次结

构。当大家选择了一个 Scope 层次结构中的作用域时,该作用域内的所有 HDL 对象,包括 reg、wire 等都会出现在“Objects”窗口中。大家可以在“Objects”窗口中选择 HDL 对象,并将它们添加到波形查看器中。

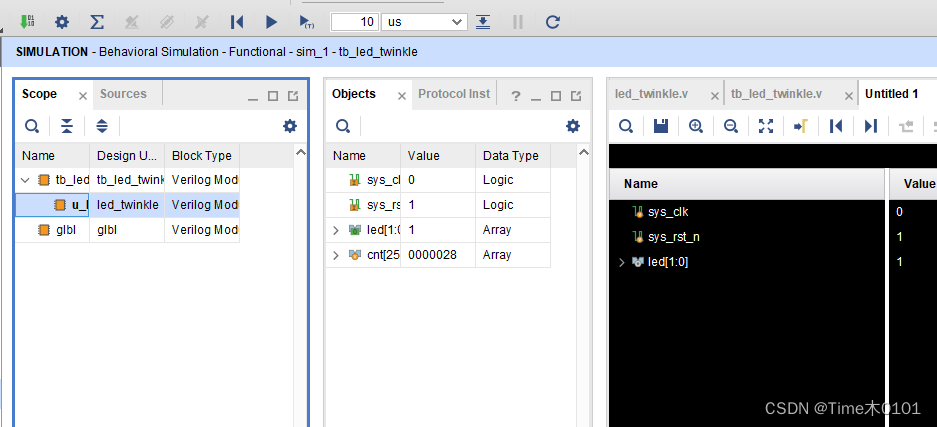

(2)Object 窗口:“Objects”窗口会显示在“Scopes”窗口中选择的范围内的所有 HDL 仿真对象。例

如,我们在 Scope 窗口中选择顶层模块“led_twinkle”,在“Objects”窗口中就会自动显示出 led_twinkle

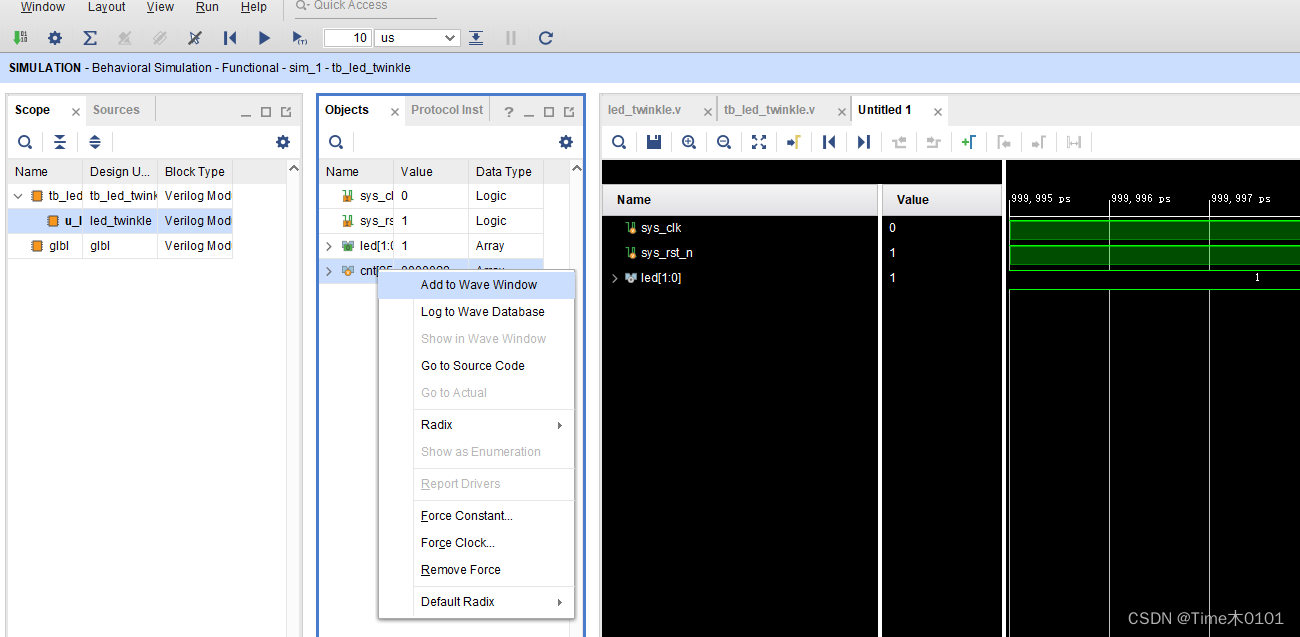

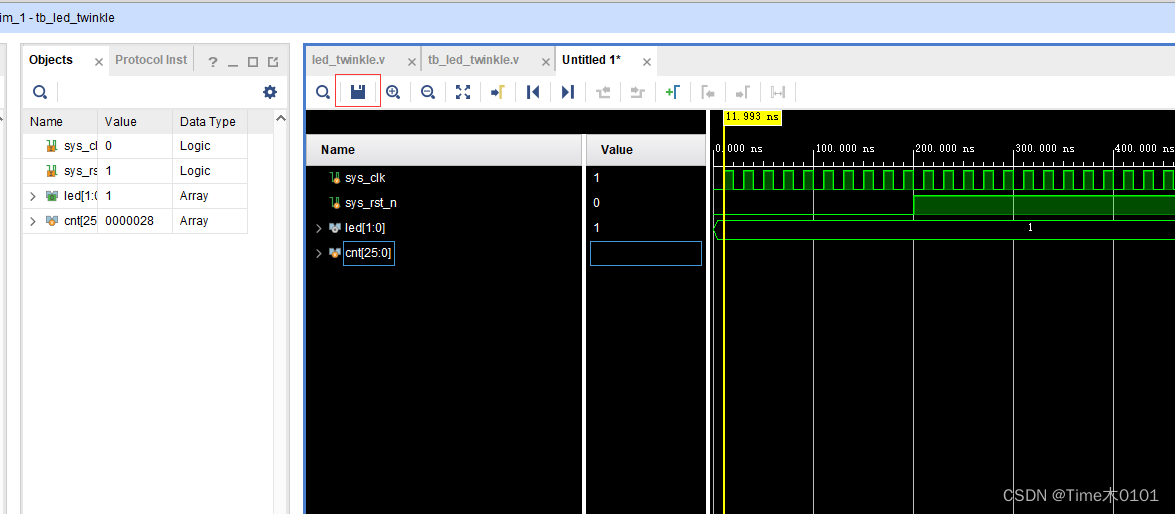

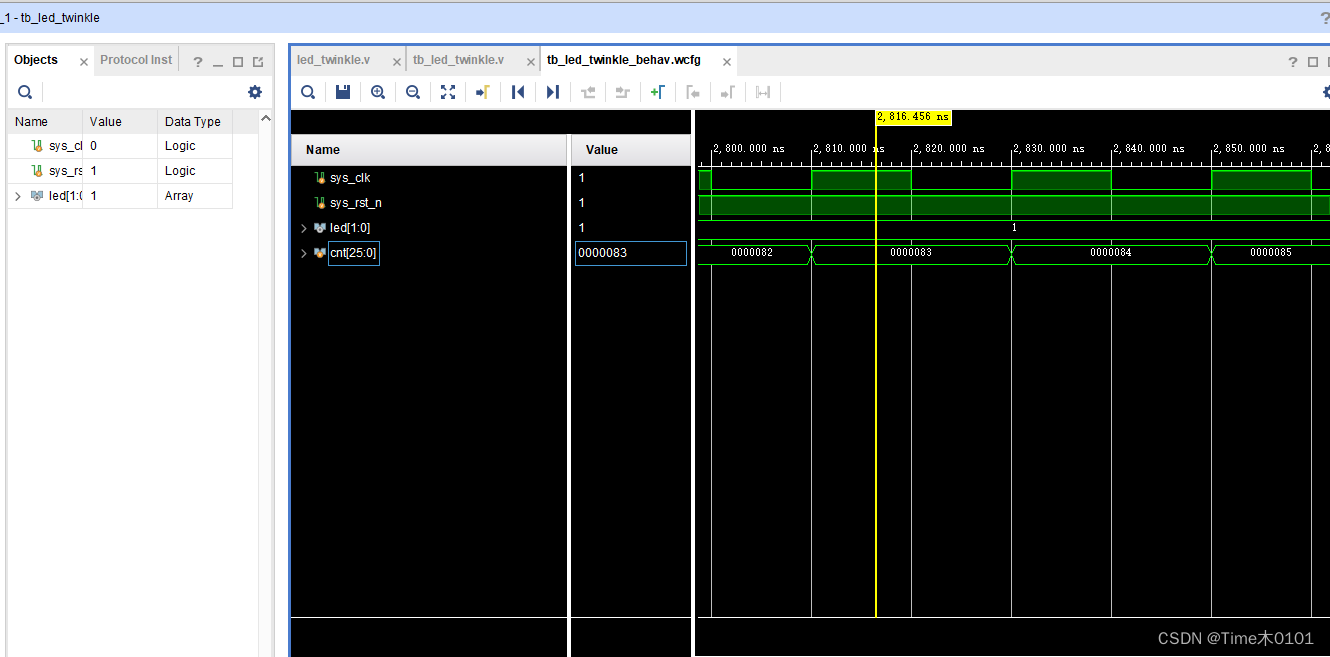

模块中所有的对象。可以看出,在 led_twinkle 顶层模块中除了顶层端口 sys_clk、sys_rst_n 和 led 之外,还包括在内部定义的计数器 cnt。如下图所示:

右击cnt,添加到波形窗口中的“cnt”计数器如下图所示:

图中可以放大缩小波形图。

2、一般来说,每当我们进行一次仿真时,都会把当前波形的配置信息保存下来,包括波形窗口中具有哪

些信号等等,以便在下一次打开仿真器进行仿真时,继续使用上一次仿真的配置信息。我们点击波形窗口中的保存按钮,如下图所示:

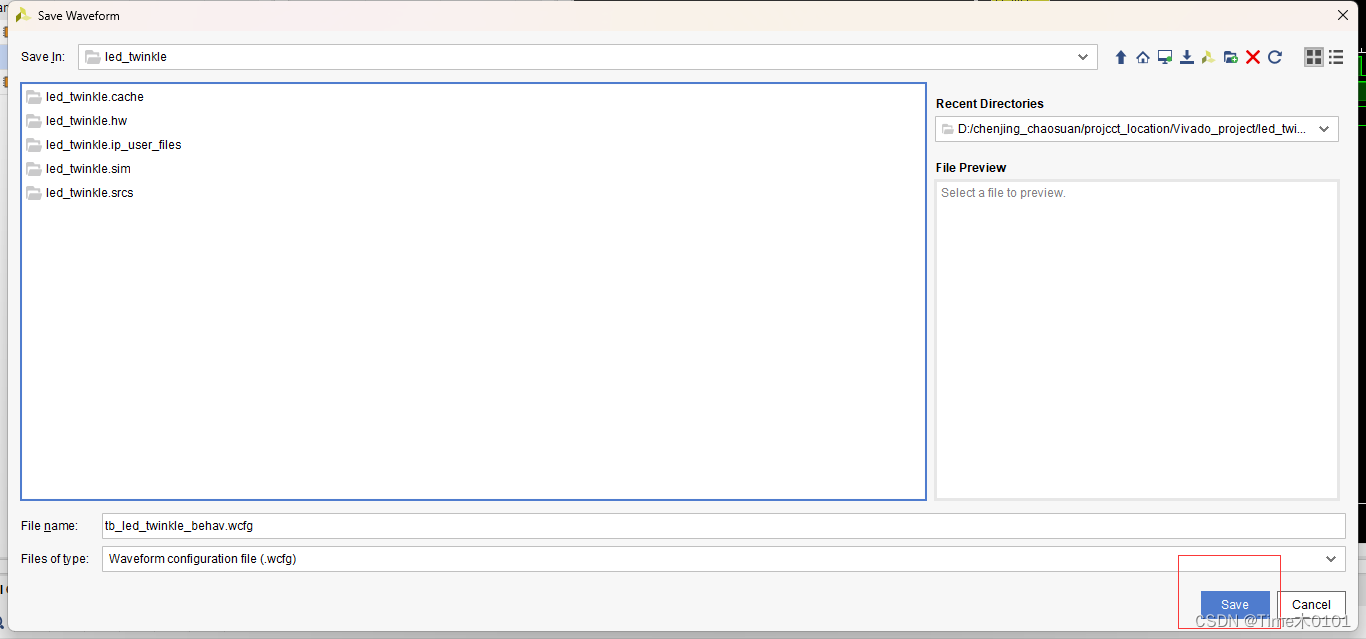

之后会弹出“Save Waveform”对话框,提示用户将当前波形配置信息保存为“.wcfg”后缀的文件,且工具

已经自动地输入了文件名“tb_led_twinkle _behav”,文件的保存目录也被工具自动设置为了当前的工程目录,所以我们保持其默认状态即可,直接点击“Save”。如下图所示:

这里有个地方需要大家注意下,wcfg 文件只是包含波形窗口的配置信息,并不包含波形的数据文件,

波形的数据文件被存储在另外的文件中。

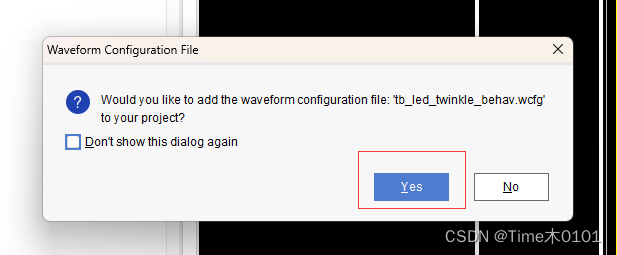

在点击保存后会弹出一个消息框,询问用户是否将刚刚创建的波形配置信息文件 tb_led_twinkle

_behav.wcfg 添加到当前工程中,我们直接点击“Yes” 即可。如下图所示:

(4)仿真工具栏:仿真工具栏包含运行各个仿真动作的命令按钮。从左至右依次是:

• Restart:将仿真时间重置为零,此时波形窗口中原有的波形都会被清除。下次执行仿真时,会从 0

时刻重新开始。

• Run all:运行仿真,直到其完成所有事件或遇到 HDL 语句中的 s t o p 或 stop 或 stop或finish 命令为止。注意,如

果没有在 TestBench 语句中加入 s t o p 或 stop 或 stop或finish 命令,当点击 Run all 命令时,仿真器会无休止地一直仿真下

去,除非用户点击仿真工具栏中的“Break”按钮来手动地结束仿真。但是这里有个地方需要注意,如果此

时需要仿真的设计比较复杂,则仿真器在运行仿真时会耗费电脑大量的 CPU 和内存资源,此时有可能会造

成电脑卡顿甚至死机的情况。所以,如果设计比较复杂,且没有在 TestBench 语句中加入 s t o p 或 stop 或 stop或finish 命

令,最好不要轻易点击 Run all 命令。

• Run For:运行特定的一段时间。紧随在后面的两个文本框用于设定仿真时长的数值大小和时间单位。

• Step:按步运行仿真,每一步仿真一个 HDL 语句。

• Break:暂停当前仿真。

• Relaunch:重新编译仿真源并重新启动仿真。在使用 Vivado 仿真器来调试 HDL 设计时,您可能会根据仿真结果来对您的 HDL 源代码进行修改。在修改完 HDL 源代码后,可以点击 Relaunch 按钮来重新加载UUT 设计和 TestBench,以重新对修改后的 HDL 源代码进行仿真。此时就不需要再关闭并重新打开仿真器了。

介绍完各个窗口和命令按钮的使用后,我们就可以开始仿真了。

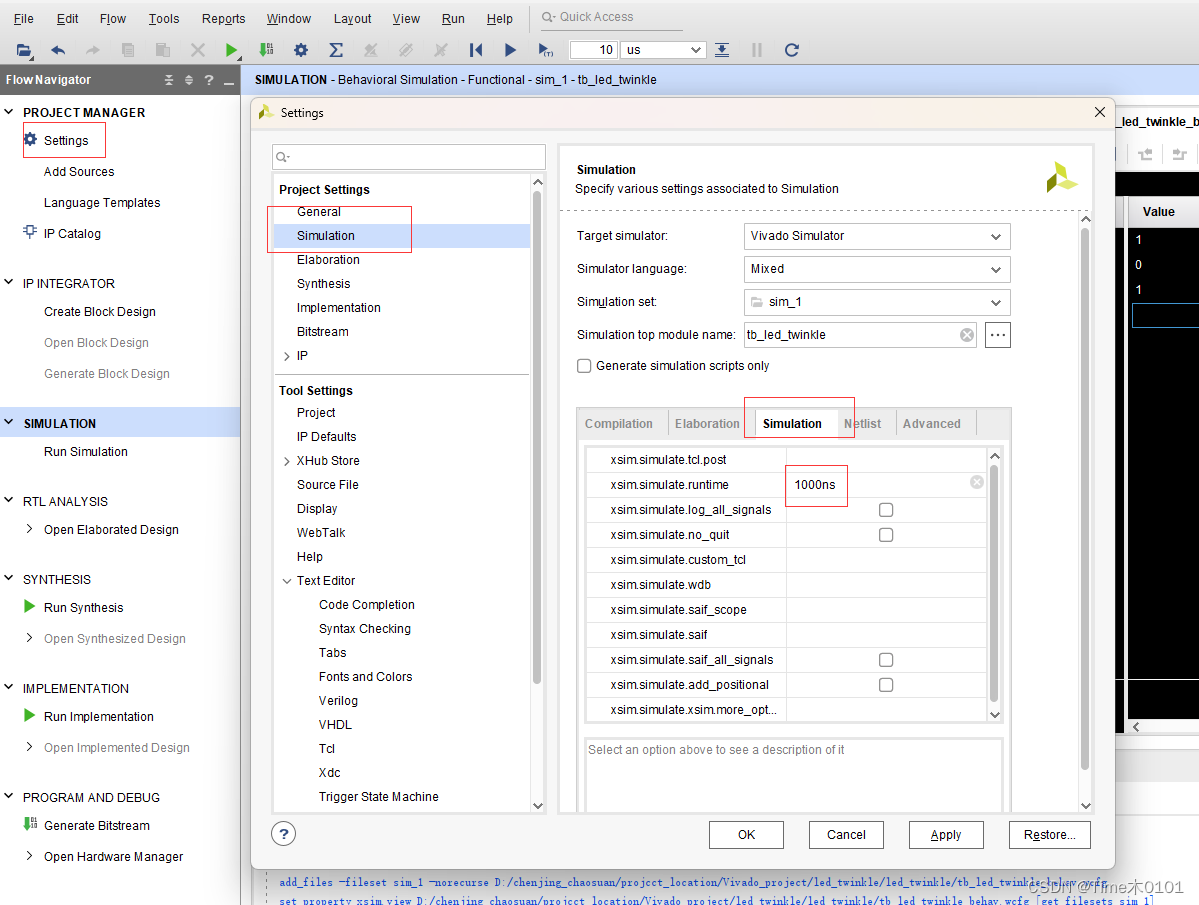

在刚打开仿真器时,仿真器会首先将 TestBench 中的信号加入到波形窗口中,并执行一段时长的仿真,

仿真的时长由 Settings 设置窗口中的参数值指定,如下图所示:

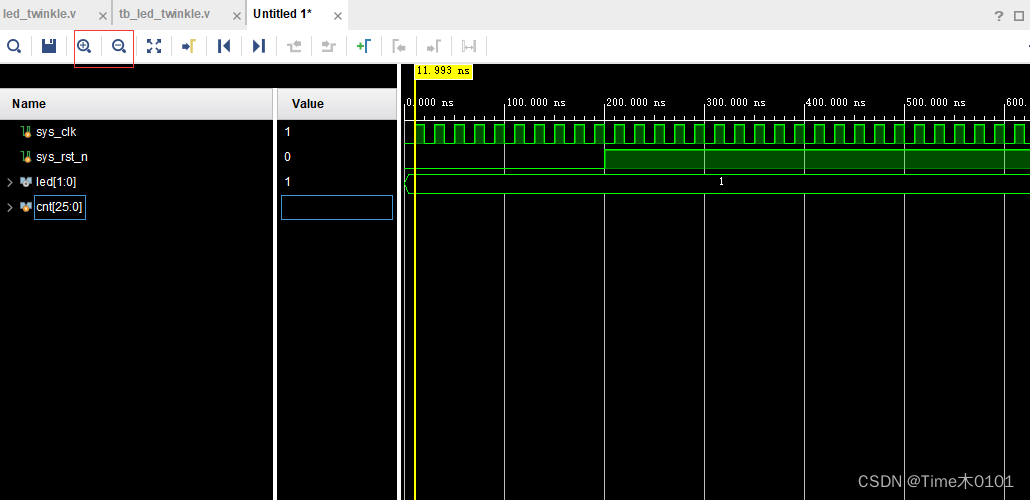

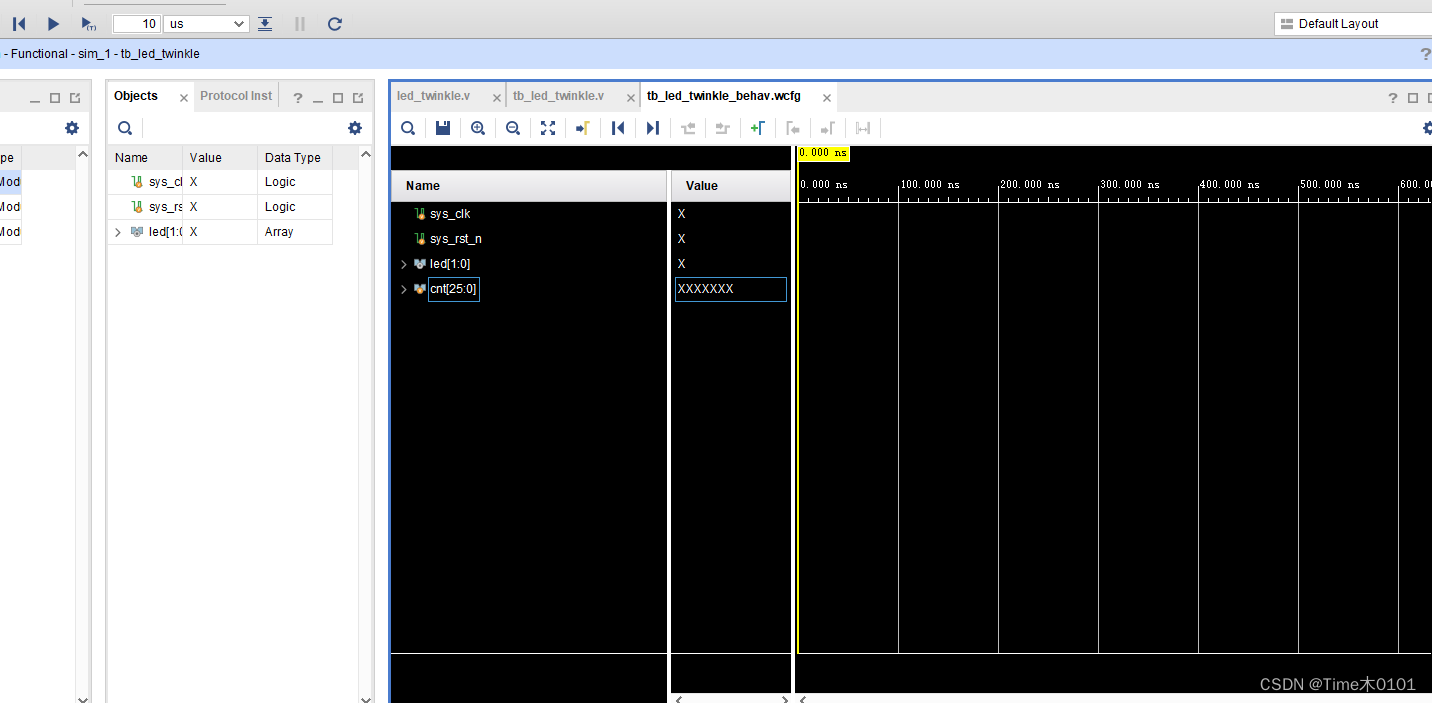

可以看到,仿真器启动后默认立即执行的仿真时长是 1000ns。由于我们是在默认立即执行仿真结束之

后,才加入了“cnt”计数器信号,所以新加入的 cnt 信号并没有波形。此时我们需要将仿真时刻重置为 0,

重新开始仿真。点击 Restart 按钮,波形窗口中的当前仿真时刻点(黄色标尺)就会回归到 0ns,且原先的所有波形都被清除,如下图所示:

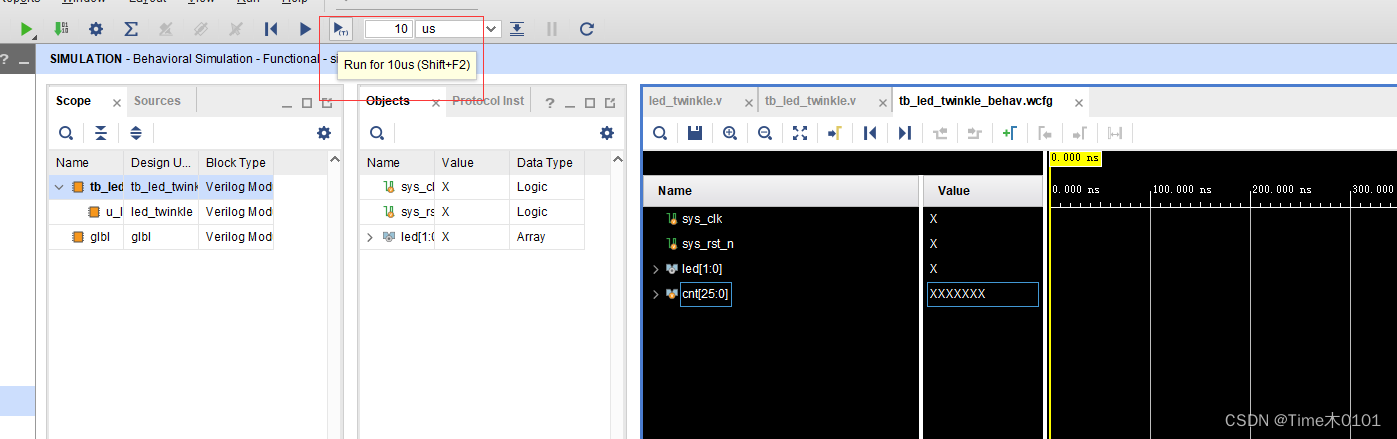

此时点击仿真工具栏中的 Run For 按钮,默认仿真时长是 10us,如下图所示:

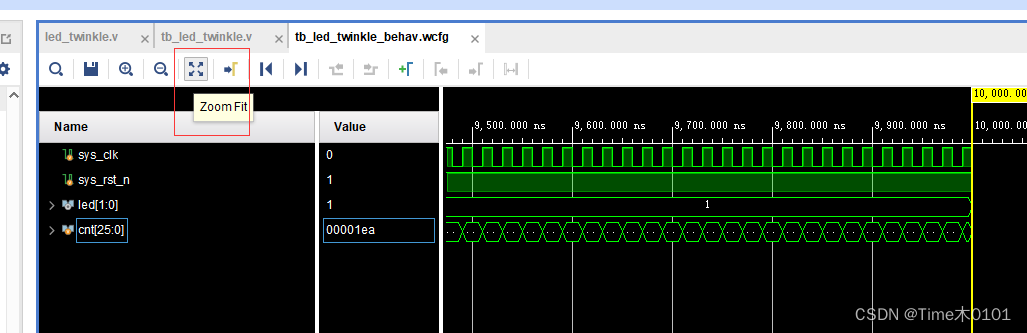

此时就可以看到波形窗口中就出现了波形,我们点击波形窗口中的显示工具栏中的“Zoom Fit”按钮,波

形就会自动缩放到整个窗口,如下图所示:

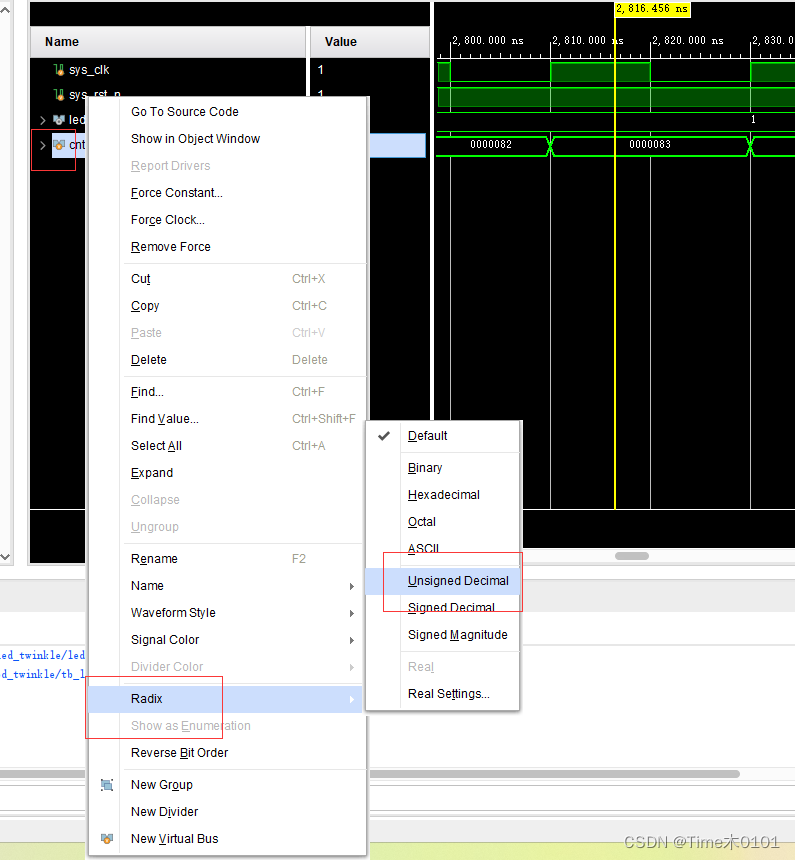

cnt 信号默认显示为 16 进制,为了方便观察,我们将其设置为 10 进制。对 cnt 信号右键,如图。

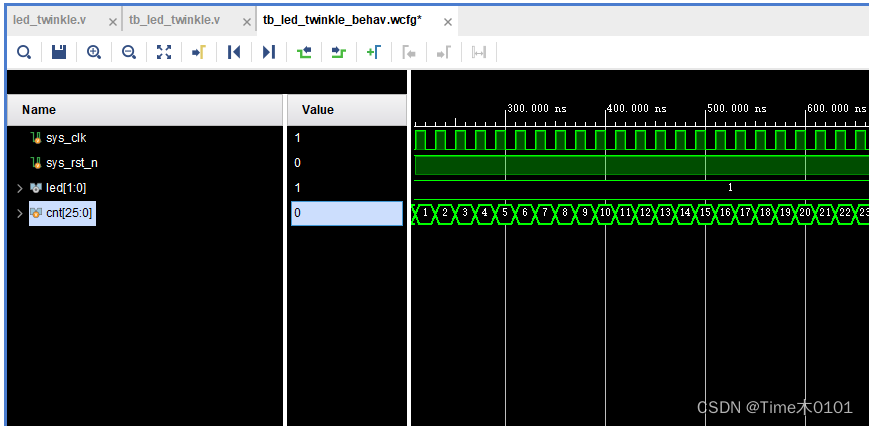

修改显示后的波形如下图所示:

这里可以看出,cnt 每计数到 10,led 就翻转一次。证明我们的 HDL 设计达到了我们想要的功能。

至此,仿真结束。

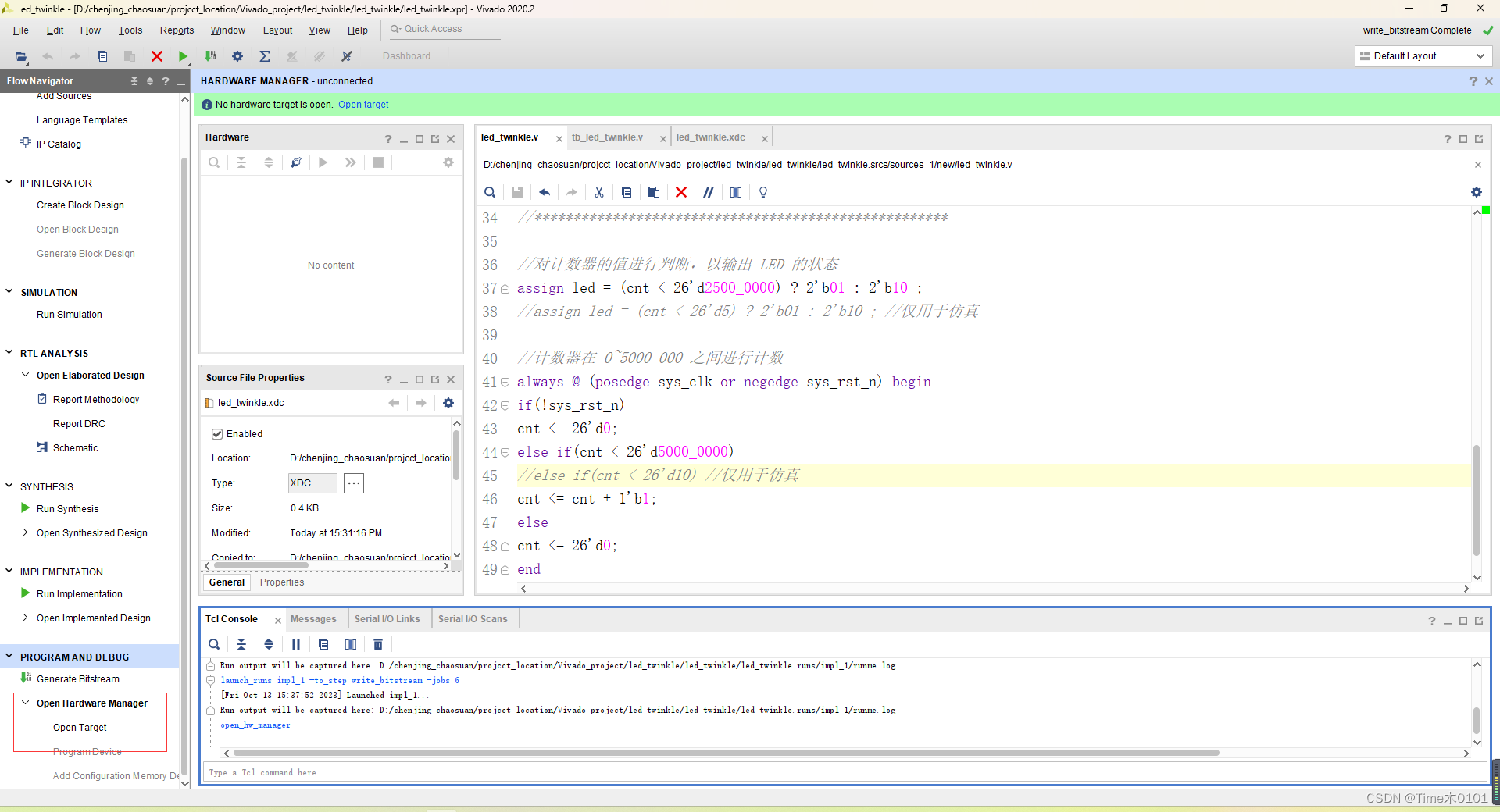

第四步:分析与综合

功能仿真通过之后,就可以对设计进行分析(Elaborated)了。我们首先将源代码中为仿真而修改的部

分恢复成原来的代码,如下图所示:

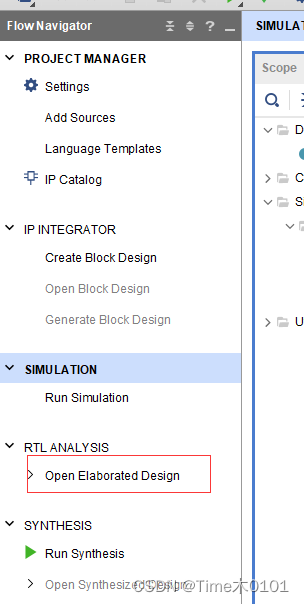

点击“Flow Navigator”窗口中的“Open Elaborated Design”按钮,如下图所示:

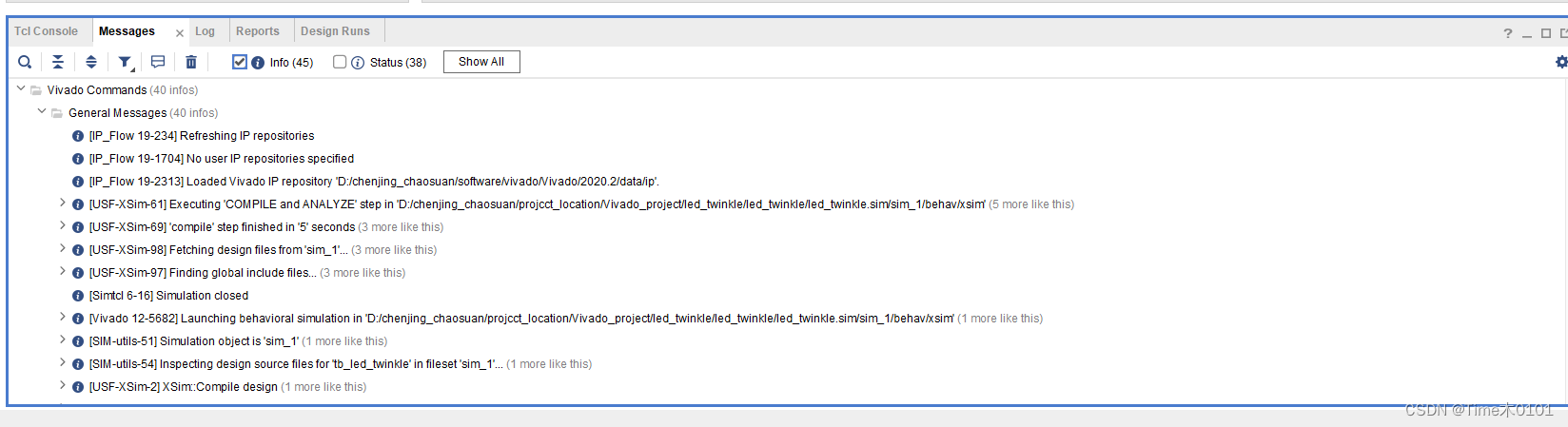

此时,Vivado 会编译 RTL 源文件进行全面的语法检查,并在 Messages 窗口中给出相应的“Error”和

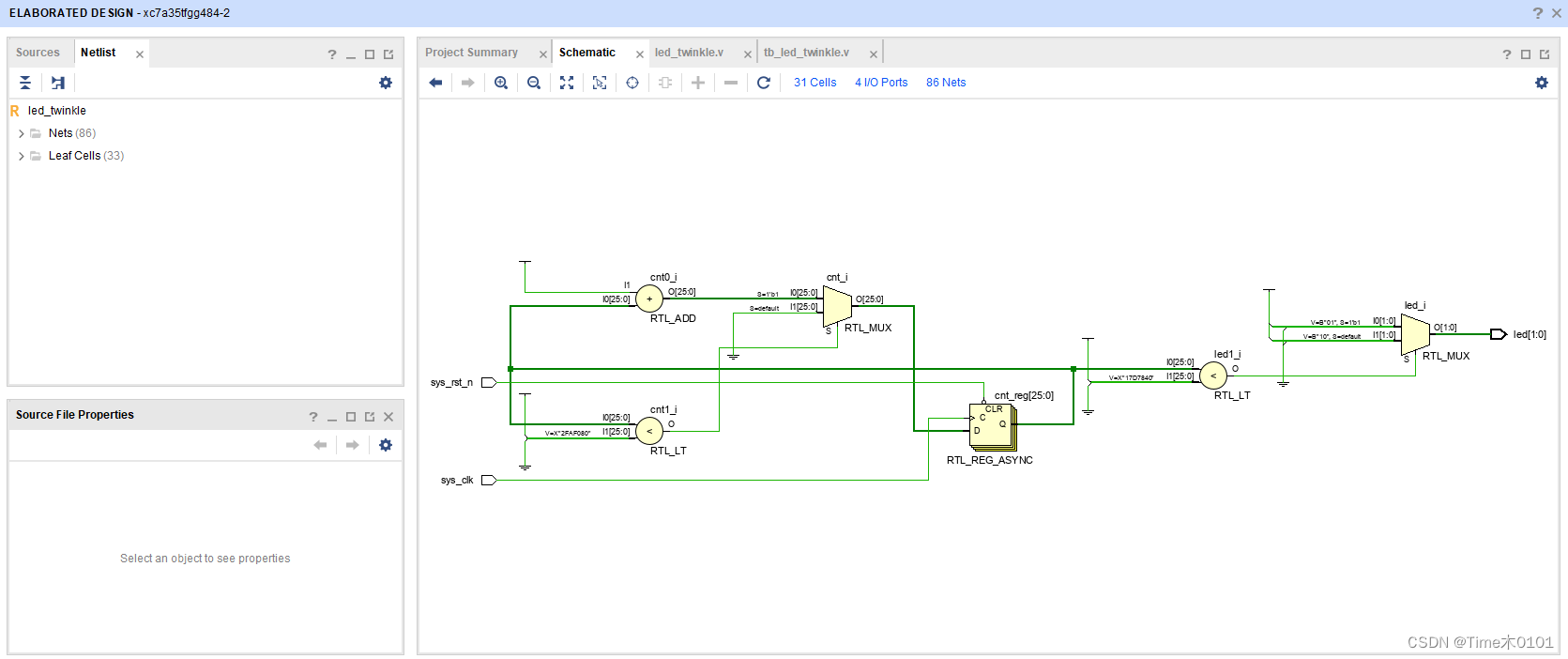

“Warning”。打开分析后(Elaborated)的设计后,Vivado 会生成顶层原理图视图,并在默认 view layout

中显示设计,如下图所示:

可以看到,此时窗口布局已经发生了变化,新增了 Schematic(原理图)、Netlist(网表)等窗口。此

时,底部的 Messages 窗口会显示出现在分析阶段产生的消息,如下图所示:

可以看出,我们的 led_twinkle 源代码并没有产生警告或者错误。

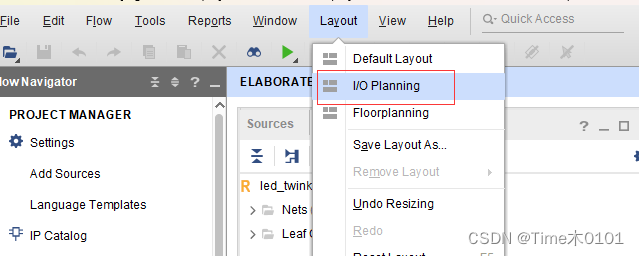

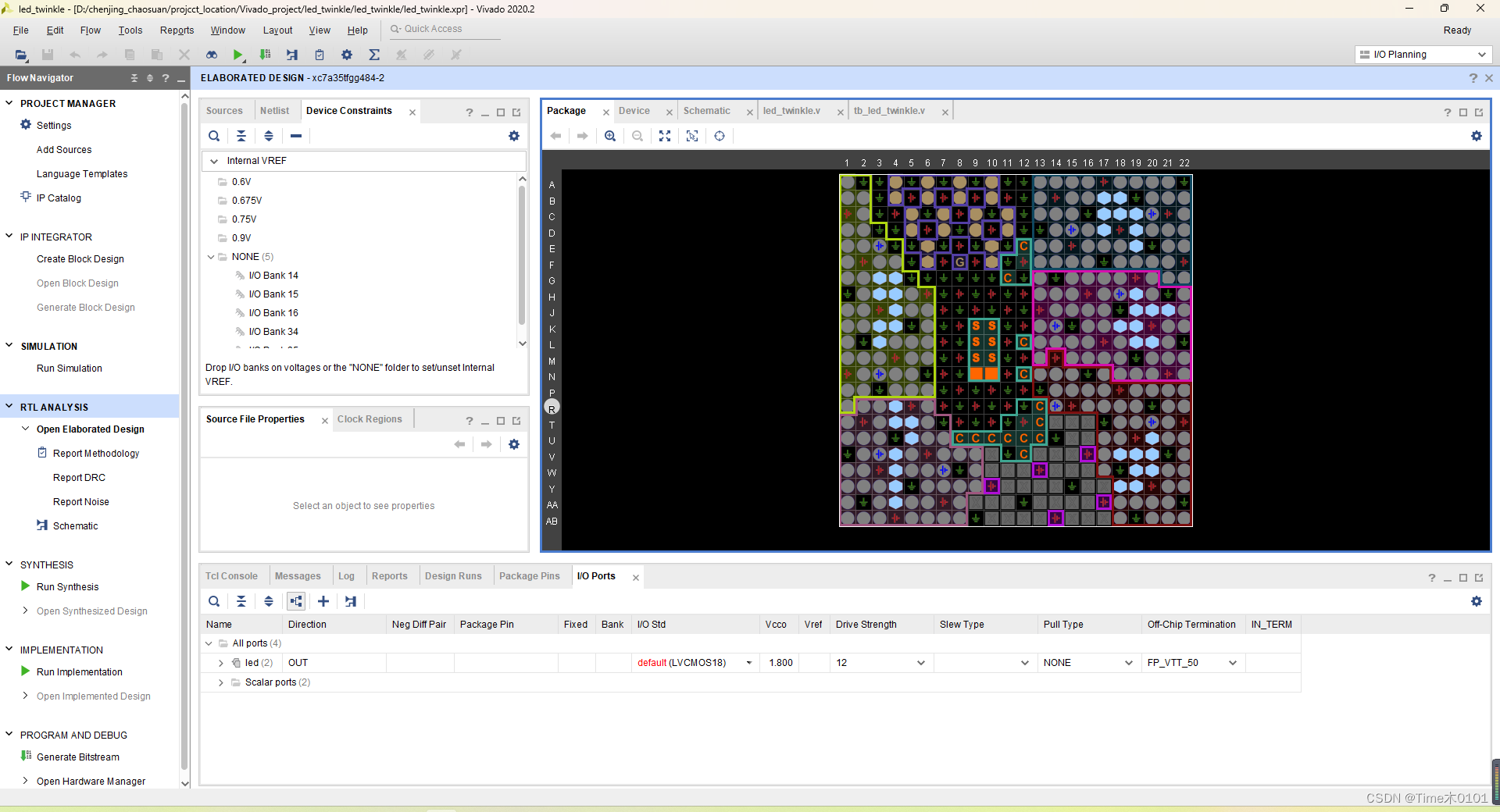

此时,我们也可以进行 I/O 引脚分配,在右上角的窗口布局(Layout)选择器中选择“I/O Planing”,如

下图所示:

此时,窗口布局会打开一些与 IO 规划相关的子窗口,如下图所示:

此时,窗口布局会打开一些与 IO 规划相关的子窗口,如下图所示:

在下方的“I/O Ports”窗口中,就可以进行 IO 的分配了。这里我们暂时不分配,先对设计进行综合,

综合之后再统一输入时序约束和 IO 引脚的物理约束。

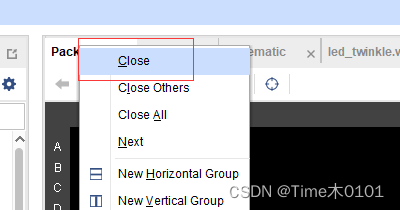

我们首先将打开的分析后的设计关闭。在工作区域的顶部标题栏处,用鼠标右击,在弹出的命令列表

中选择“close”,如下图所示:

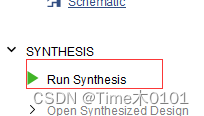

我们点击“Flow Navigator”窗口中的“Run Synthesis”按钮,如下图所示:

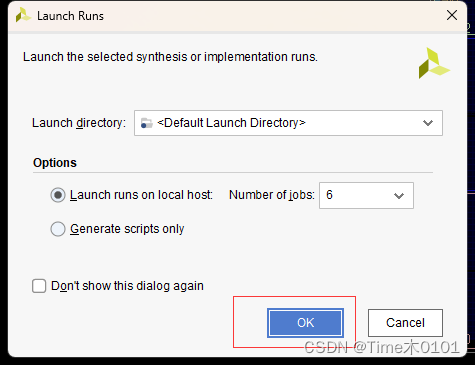

在弹出的窗口中我们直接点击 OK,如下图所示:

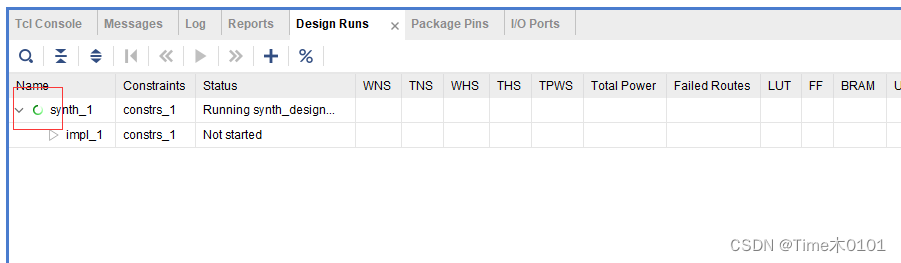

这时可以看到在“Design Runs”窗口中显示正在综合,如下图所示:

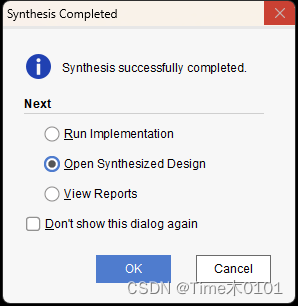

综合完成后,弹出如下窗口:

我们关闭该窗口。接下来进行约束的输入。

第五步:约束输入

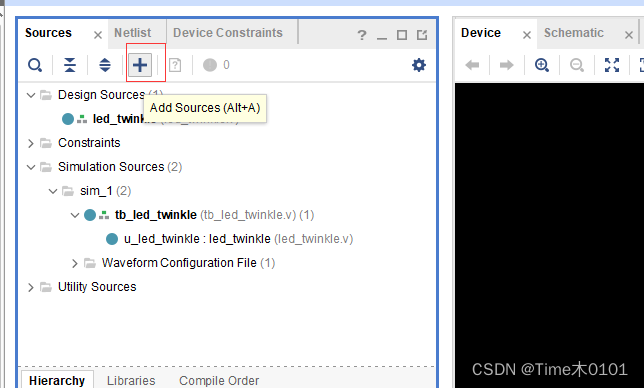

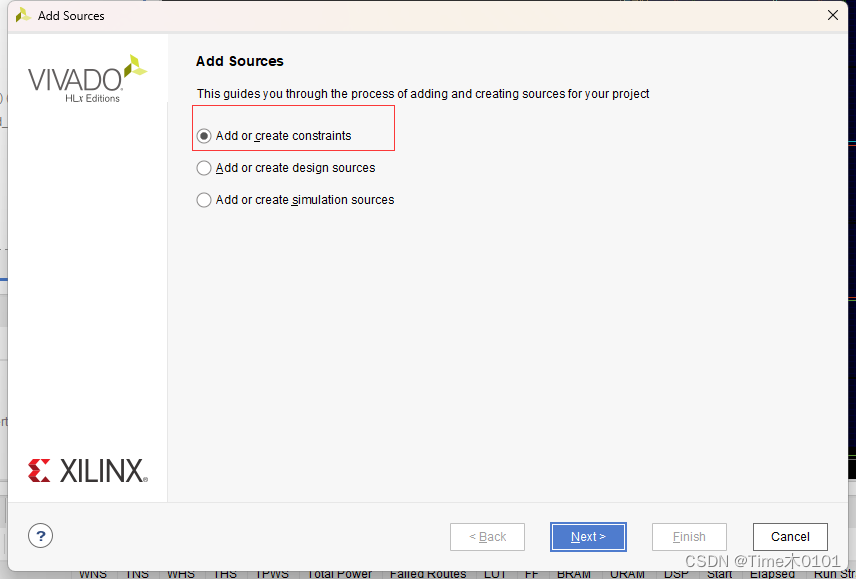

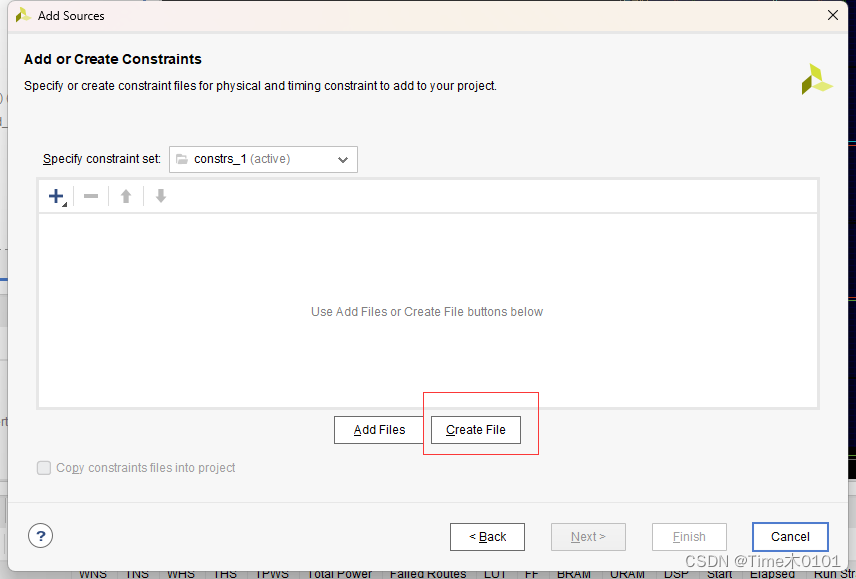

大家首先需要创建一个用于存储约束语句的约束文件。点击“Sources”窗口中的“+”号,在弹出的窗

口选择“Add or create constraints”,如下图所示:

点击 next,在接下来的界面中点击“Create File”,如下图所示:

点击 next,在接下来的界面中点击“Create File”,如下图所示:

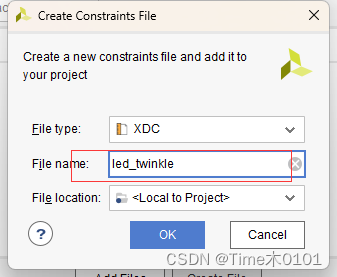

在弹出的对话框中输入约束文件的名称“led_twinkle”,然后点击 OK。

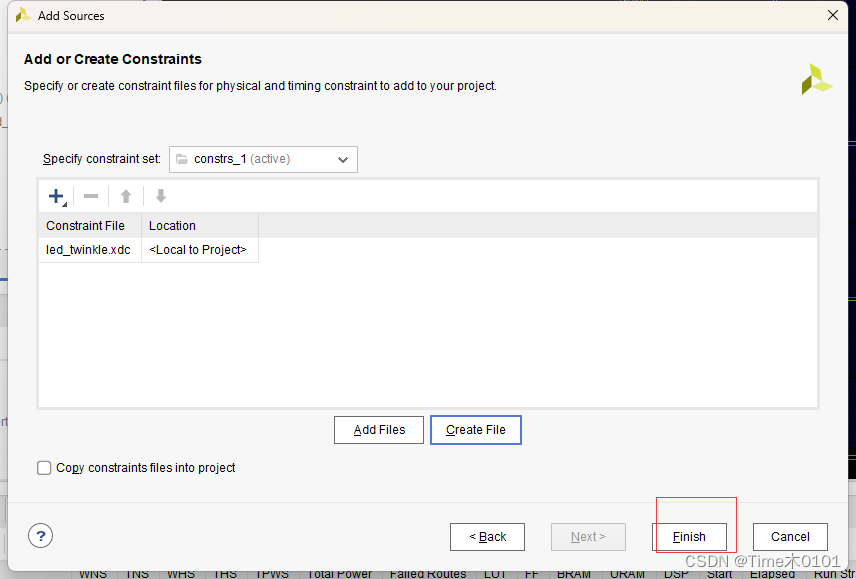

然后直接点击 Finish 即可。

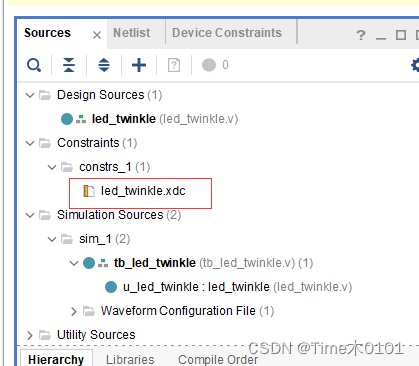

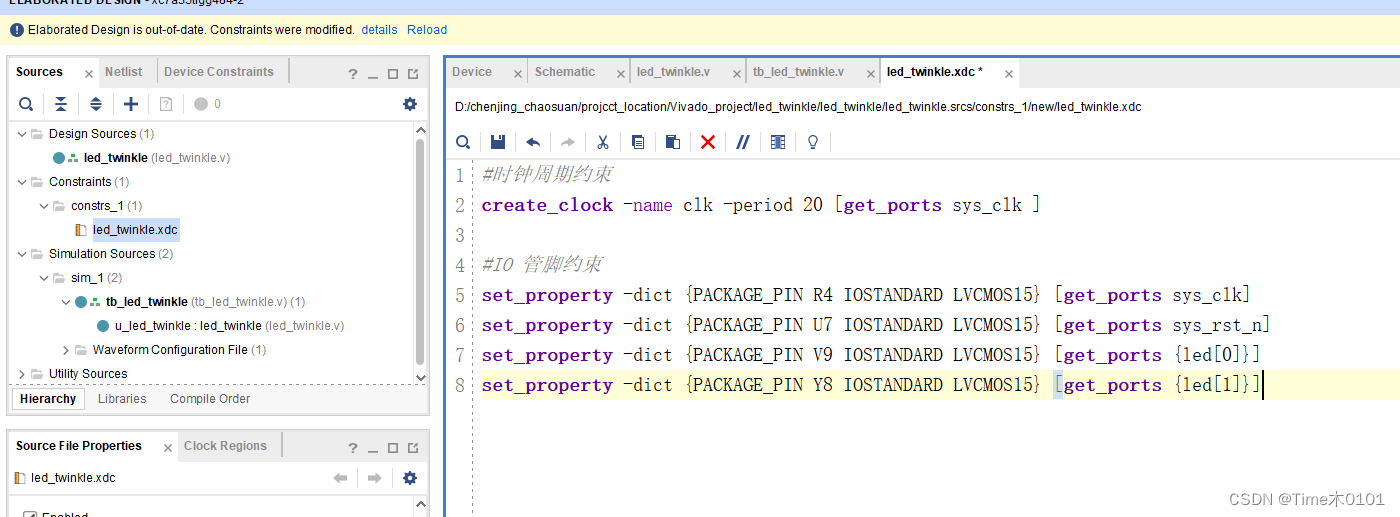

这时我们就可以在“Sources”窗口中看到添加的这个约束文件了,如下图所示:

这里有个地方需要大家注意下,Vivado 的约束文件是以“.xdc”为文件后缀的 ASCII 文本文件,其中

存储的是一条条的 xdc 约束命令。

我们双击打开 led_twinkle.xdc,输入如下内容:

#时钟周期约束

create_clock -name clk -period 20 [get_ports sys_clk ]#IO 管脚约束

set_property -dict {PACKAGE_PIN R4 IOSTANDARD LVCMOS15} [get_ports sys_clk]

set_property -dict {PACKAGE_PIN U7 IOSTANDARD LVCMOS15} [get_ports sys_rst_n]

set_property -dict {PACKAGE_PIN V9 IOSTANDARD LVCMOS15} [get_ports {led[0]}]

set_property -dict {PACKAGE_PIN Y8 IOSTANDARD LVCMOS15} [get_ports {led[1]}]

下面我们以 sys_clk 时钟引脚为例,简要介绍 xdc 文件的语法。第一行以“#”号开头,表示这是一条

注释语句。第二行是有效的约束命令。每一个约束命令单独占用一行,命令的结尾没有如 verilog 中的分号“;”一样的语句结束符号。每一条注释也单独占用一行。命令的第一个关键字代表该命令的名称,其后的所有字段都是该命令的参数列表。例如,在第二行的时钟周期约束命令中,“create_clock”是该命令的名称,它会创建一个时钟;其后的“-name clk”、“-period 20”、“[get_ports sys_clk ]”都是该命令的各个参数,分别表示所创见的时钟的的名称是“clk”、时钟周期是 20ns、时钟源是 sys_clk 引脚。

第 5 行至第 8 行是对 IO 管脚的引脚位置约束和电平标准约束。例如,在第 5 行中,“set_property”是

命令的名称;“PACKAGE_PIN R4”是引脚位置参数,代表引脚位置是 R4;“[get_ports sys_clk]”代表

该约束所要附加的对象是 sys_clk 引脚, “IOSTANDARD LVCMOS15”代表该引脚所使用的电平标准是LVCMOS15。

其他 IO 引脚的约束命令的语法与 sys_clk 引脚是相同的,这里就不再重复了。但是要注意,create_clock约束命令只能在 sys_clk 时钟引脚上使用,其他普通 IO 上不能使用 create_clock 约束命令。

点击 Text Editor 中的保存按钮后,就完成了约束的输入。

另外,为了便于大家的查看,我们整理出了包含开发板上所有引脚分配的表格,该表格位于资料盘/3_

正点原子达芬奇 Pro FPGA 开发板原理图/达芬奇 Pro FPGA 开发板 IO 引脚分配表。

记得保存

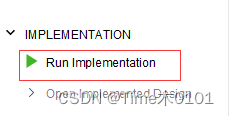

第六步:设计实现

约束输入完毕之后,就可以开始实现设计了。我们点击点击“Flow Navigator”窗口中的“Run

Implementation”按钮,如下图所示:

如果出现窗口直接yes

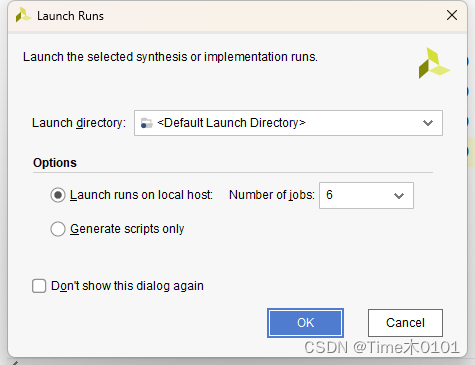

在弹出的界面中直接点击 OK 即可,如下图所示:

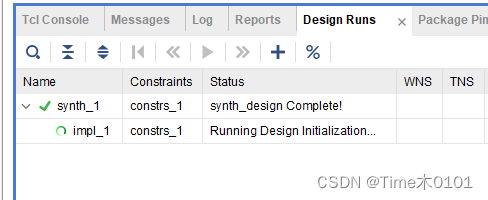

这时可以看到“Design Runs”窗口中显示实现正在进行,如下图所示:

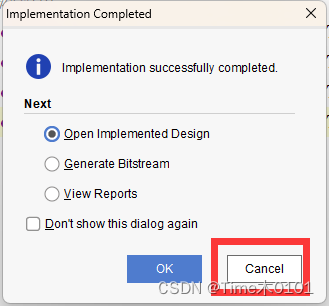

实现完成后会弹出提示窗口,我们直接点击取消来关闭窗口,如下图所示:

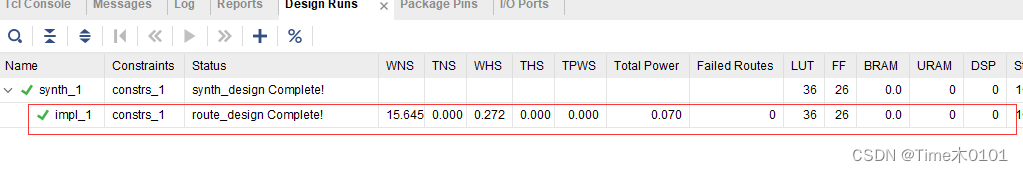

这时我们再次查看“Design Runs”窗口中的实现结果,如下图所示:

第七步:下载比特流

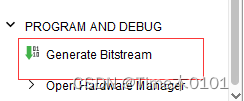

要下载设计,首先要生成用于下载到器件中的比特流文件。我们点击“Flow Navigator”窗口中的

“Generate Bitstream”按钮,如下图所示:

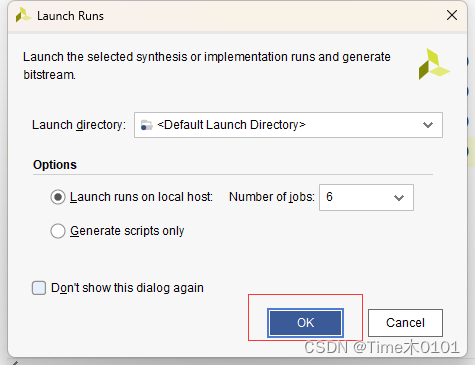

在弹出的窗口中直接点击 OK,如下图所示:

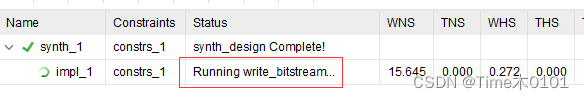

此时我们可以看到在“Design Runs”窗口中显示正在生成比特流,如下图所示:

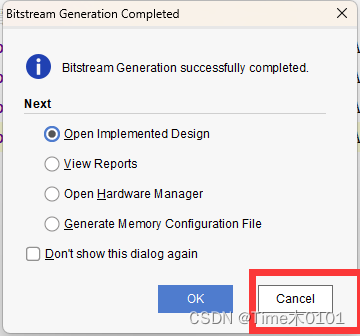

比特流生成完毕之后,Vivado 会弹出提示窗口,我们点击取消关闭该窗口:

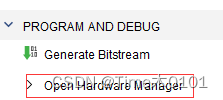

接下来我们开始下载比特流,点击“Flow Navigator”窗口中的“Open Hardware Manager”按钮,如下

图所示:

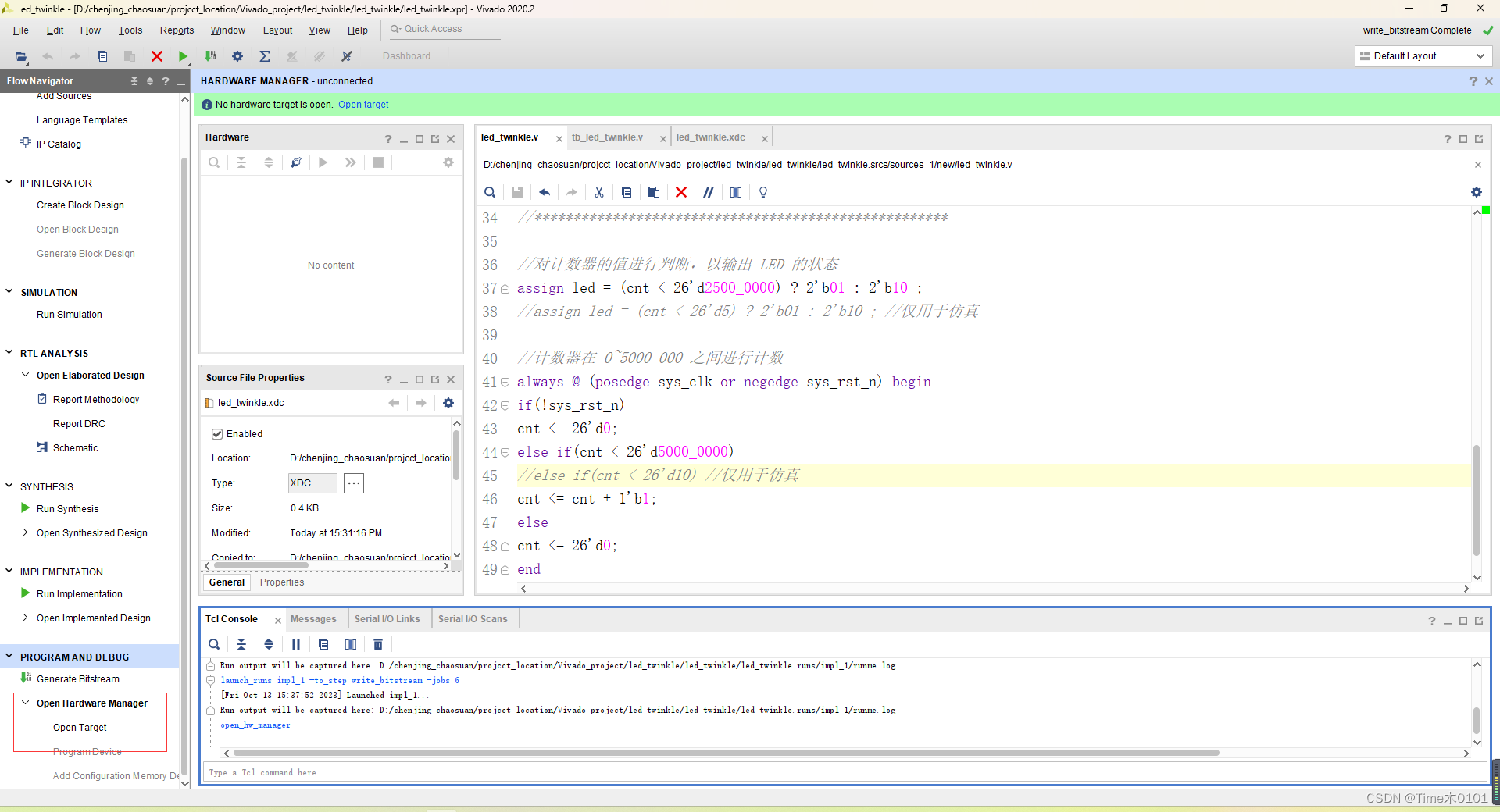

接着 Vivado 就会打开 Hardware Manager,同时窗口布局也跟着发生了变化,如下图所示:

首先我们将下载器一端连接电脑,另一端与开发板上的 JTAG 接口相连接,然后连接开发板电源线。

下面是上板子调试阶段。

这里省略。

此文章为过程记录,学习交流,后期回顾使用,部分文字内容来源于原子哥文档。

相关文章:

Vivado详细使用教程 | LED闪烁示例

文章目录 整体流程第一步:新建工程第二步:设计输入第三步:功能仿真第四步:分析与综合第五步:约束输入第六步:设计实现第七步:下载比特流 整体流程 打开软甲------>新建工程------->设计输…...

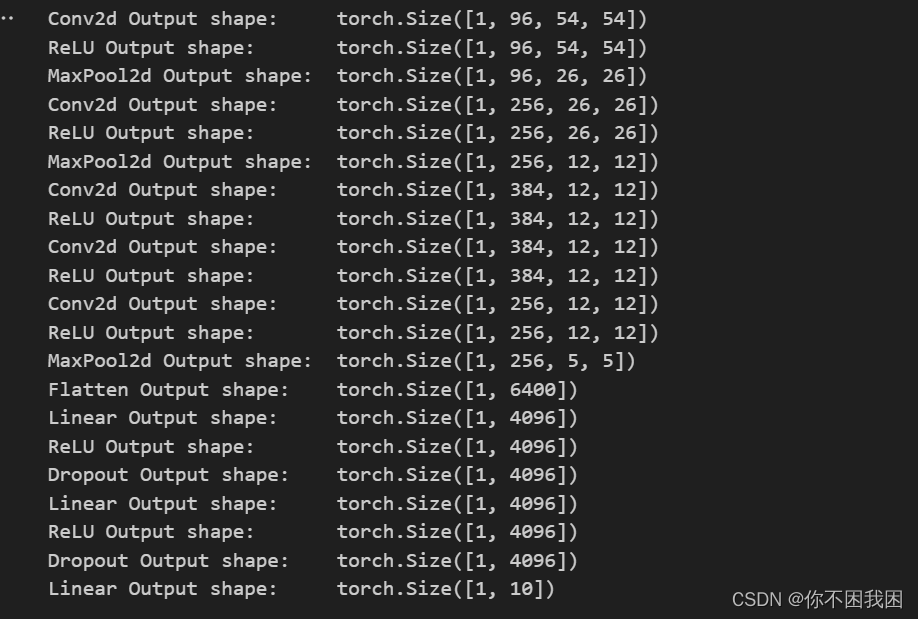

一些经典的神经网络(第17天)

1. 经典神经网络LeNet LeNet是早期成功的神经网络; 先使用卷积层来学习图片空间信息 然后使用全连接层来转到到类别空间 【通过在卷积层后加入激活函数,可以引入非线性、增加模型的表达能力、增强稀疏性和解决梯度消失等问题,从而提高卷积…...

Hadoop-HA-Hive-on-Spark 4台虚拟机安装配置文件

Hadoop-HA-Hive-on-Spark 4台虚拟机安装配置文件 版本号步骤hadoopcore-site.xmlhdfs-site.xmlmapred-site.xmlslavesworkersyarn-site.xml hivehive-site.xmlspark-defaults.conf sparkhdfs-site.xmlhive-site.xmlslavesyarn-site.xmlspark-env.sh 版本号 apache-hive-3.1.3-…...

Hutool工具类参考文章

Hutool工具类参考文章 日期: 身份证:...

【 Python ModuleNotFoundError: No module named ‘xxx‘可能的解决方案大全】

Python ModuleNotFoundError: No module named ‘xxx‘可能的解决方案大全 本文主要介绍了Python ModuleNotFoundError: No module named ‘xxx‘可能的解决方案大全,文中通过示例代码介绍的非常详细,对大家的学习或者工作具有一定的参考学习价值&#x…...

eclipse 配置selenium环境

eclipse环境 安装selenium的步骤 配置谷歌浏览器驱动 Selenium安装-如何在Java中安装Selenium chrome驱动下载 eclipse 启动配置java_home: 在eclipse.ini文件中加上一行 1 配置java环境,网上有很多教程 2 下载eclipse,网上有很多教程 ps&…...

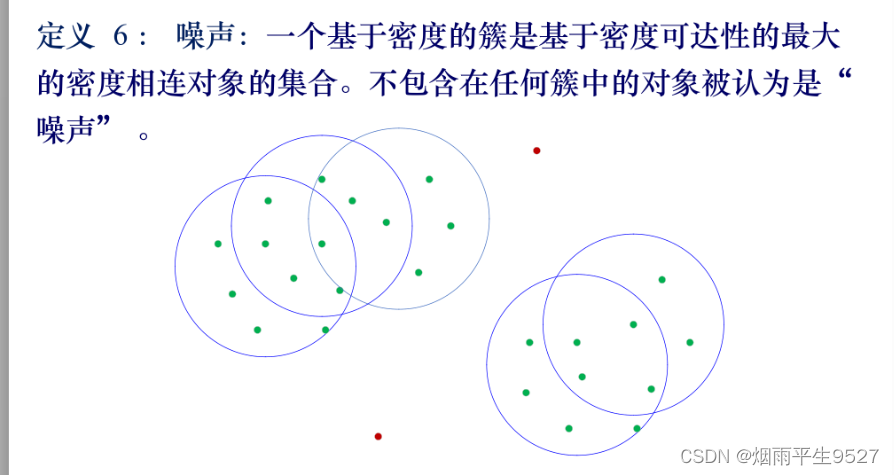

数据挖掘(6)聚类分析

一、什么是聚类分析 1.1概述 无指导的,数据集中类别未知类的特征: 类不是事先给定的,而是根据数据的相似性、距离划分的聚类的数目和结构都没有事先假定。挖掘有价值的客户: 找到客户的黄金客户ATM的安装位置 1.2区别 二、距离和相似系数 …...

在启智平台上安装anconda

安装Anaconda3-5.0.1-Linux-x86_64.sh python版本是3.6 在下面的网站上找到要下载的anaconda版本,把对应的.sh文件下载下来 https://mirrors.tuna.tsinghua.edu.cn/anaconda/archive/ 把sh文件压缩成.zip文件,拖到启智平台的调试页面 上传到平台上 un…...

棒球省队建设实施办法·棒球1号位

棒球省队建设实施办法 1. 建设目标与原则 提升棒球省队整体竞技水平 为了提升棒球省队整体竞技水平,我们需要采取一系列有效的措施。 首先,我们应该加强对棒球运动的投入和关注。各级政府和相关部门应加大对棒球运动的经费投入,提高球队的…...

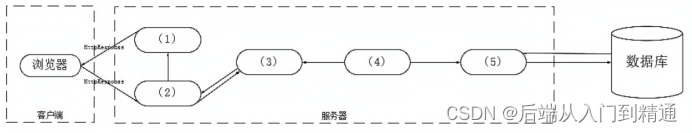

架构案例2017(五十二)

第5题 阅读以下关于Web系统架构设计的叙述,在答题纸上回答问题1至问题3.【说明】某电子商务企业因发展良好,客户量逐步增大,企业业务不断扩充,导致其原有的B2C商品交易平台己不能满足现有业务需求。因此,该企业委托某…...

给四个点坐标计算两条直线的交点

文章目录 1 chatgpt42、文心一言3、星火4、Bard总结 我使用Chatgpt4和文心一言、科大讯飞星火、google Bard 对该问题进行搜索,分别给出答案。先说结论,是chatgpt4和文心一言给对了答案, 另外两个部分正确。 问题是:python 给定四…...

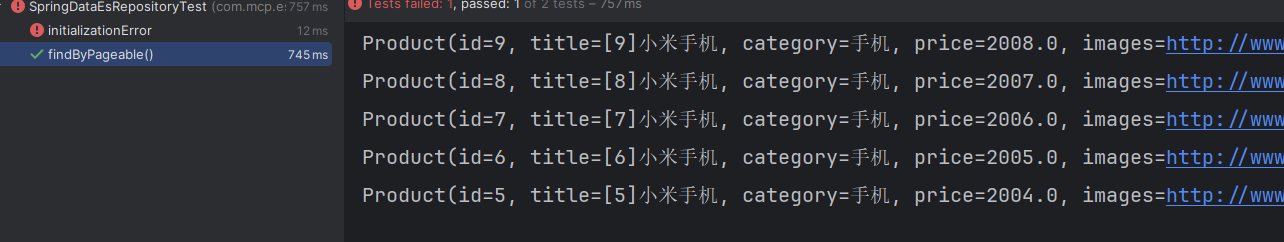

从入门到进阶 之 ElasticSearch SpringData 继承篇

🌹 以上分享 从入门到进阶 之 ElasticSearch SpringData 继承篇,如有问题请指教写。🌹🌹 如你对技术也感兴趣,欢迎交流。🌹🌹🌹 如有需要,请👍点赞…...

中文编程开发语言工具编程案例:计时计费管理系统软件连接灯控器编程案例

中文编程开发语言工具编程案例:计时计费管理系统软件连接灯控器编程案例 中文编程开发语言工具编程案例:计时计费管理系统软件连接灯控器编程案例 中文编程系统化教程,不需英语基础。学习链接 https://edu.csdn.net/course/detail/39036...

YOLOv7改进:动态蛇形卷积(Dynamic Snake Convolution),增强细微特征对小目标友好,实现涨点 | ICCV2023

💡💡💡本文独家改进:动态蛇形卷积(Dynamic Snake Convolution),增强细长微弱的局部结构特征与复杂多变的全局形态特征,对小目标检测很适用 Dynamic Snake Convolution | 亲测在多个数据集能够实现大幅涨点 收录: YOLOv7高阶自研专栏介绍: http://t.csdnimg.…...

从文心大模型4.0与FuncGPT:用AI为开发者打开新视界

今天,在百度2023世界大会上,文心大模型4.0正式发布,而在大洋的彼岸,因为大模型代表ChatGPT之类的AI编码工具来势汹汹,作为全世界每个开发者最爱的代码辅助网站,Stack Overflow的CEO Prashanth Chandrasekar…...

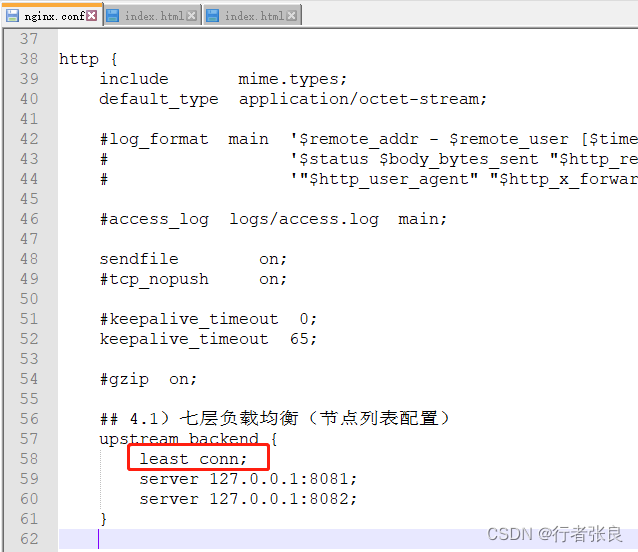

Nginx集群负载均衡配置完整流程

今天,良哥带你来做一个nginx集群的负载均衡配置的完整流程。 一、准备工作 本次搭建的操作系统环境是win11,linux可配置类同。 1)首先,下载nginx。 下载地址为:http://nginx.org/en/download.html 良哥下载的是&am…...

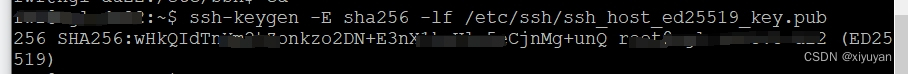

如何生成SSH服务器的ed25519公钥SHA256指纹

最近搭建ubuntu服务器,远程登录让确认指纹,研究一番搞懂了,记录一下。 1、putty 第一次登录服务器,出现提示: 让确认服务器指纹是否正确。 其中:箭头指向的 ed25519 :是一种非对称加密的签名方法…...

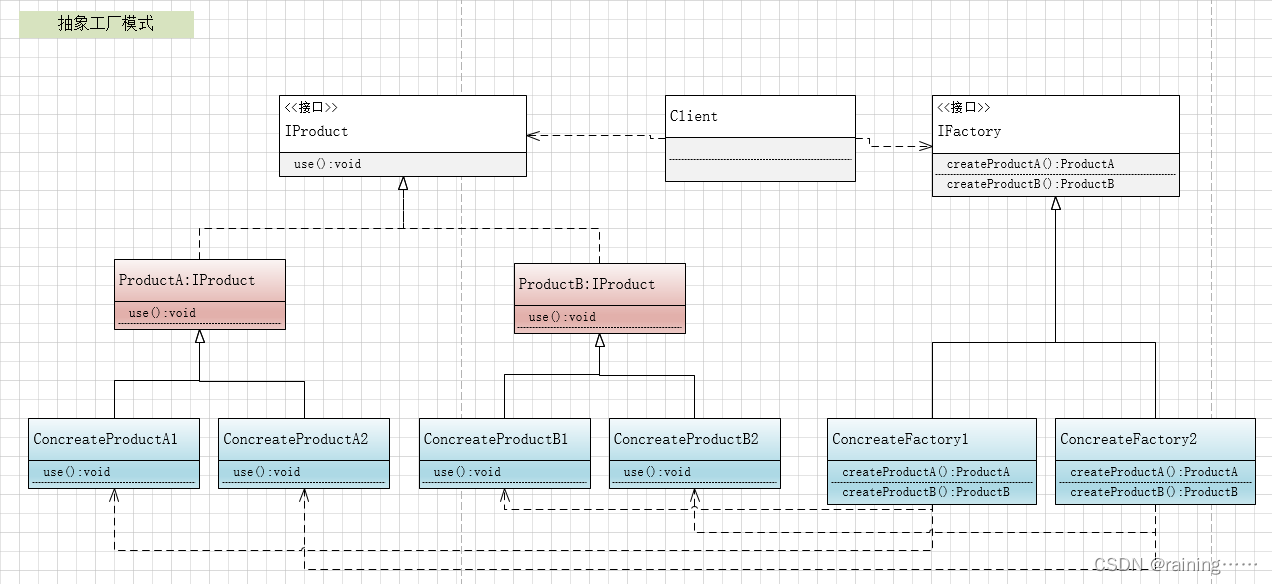

设计模式:抽象工厂模式(C#、JAVA、JavaScript、C++、Python、Go、PHP)

大家好!本节主要介绍设计模式中的抽象工厂模式。 简介: 抽象工厂模式,它是所有形态的工厂模式中最为抽象和最具一般性的一种形态。它用于处理当有多个抽象角色时的情况。抽象工厂模式可以向客户端提供一个接口,使客户端在不必指…...

、远程停止(RemoteStopTransaction))

ocpp-远程启动(RemoteStartTransaction)、远程停止(RemoteStopTransaction)

目录 1、介绍 2、远程启动-RemoteStartTransaction 3、远程停止-RemoteStopTransaction 4、代码 4.1 OcppRechongFeign 4.2 CmdController 4.3 CmdService 4.4 RemoteStartTransactionReq 4.5 接收报文-DataAnalysisController 4.6 接收报文实现类-DataAnalysisServi…...

【网络安全】安全的系统配置

系统配置是网络安全的重要组成部分。一个不安全的系统配置可能会使网络暴露在攻击者面前,而一个安全的系统配置可以有效地防止攻击者的入侵。在本文中,我们将详细介绍如何配置一个安全的系统,包括操作系统配置,网络服务配置&#…...

基于ESP8266与TFT屏的桌面智能天气站DIY全攻略

1. 项目概述:打造一个桌面级的智能天气信息中心 几年前,当我第一次把玩ESP8266这块小芯片时,就被它“麻雀虽小,五脏俱全”的特性震撼了——一个比硬币大不了多少的模块,竟然内置了完整的Wi-Fi协议栈和可编程的微控制器…...

ARM指令集架构与安全指令解析:APAS、ASR与AUT

1. ARM指令集架构概述在处理器设计领域,指令集架构(Instruction Set Architecture, ISA)定义了处理器与软件之间的契约。作为RISC(精简指令集计算机)架构的代表,ARM指令集以其高效能和低功耗特性࿰…...

【亲测免费】 开启高效OCR之旅:Delphi集成Tesseract 4.0完全指南

开启高效OCR之旅:Delphi集成Tesseract 4.0完全指南 【下载地址】Delphi调用Tesseract4.0进行OCR识别已打包全部DLL 本仓库提供了通过Delphi环境调用Google的Tesseract OCR引擎4.0版本的示例代码和所有必要的DLL文件。Tesseract是一款强大的开源文字识别系统…...

英雄联盟R3nzSkin换肤工具:3分钟实现安全免费的全皮肤体验

英雄联盟R3nzSkin换肤工具:3分钟实现安全免费的全皮肤体验 【免费下载链接】R3nzSkin Skin changer for League of Legends (LOL) 项目地址: https://gitcode.com/gh_mirrors/r3n/R3nzSkin R3nzSkin是一款专为英雄联盟玩家设计的开源内存换肤工具,…...

量子纠缠认证协议原理与工程实践

1. 量子纠缠认证协议的核心原理量子纠缠作为量子力学最反直觉的现象之一,在信息安全领域展现出独特优势。当两个量子比特形成贝尔态时,无论相隔多远,对其中一个粒子的测量会瞬间决定另一个粒子的状态。这种非局域关联特性,成为构建…...

【免费下载】 探索语音合成新境界:so-vits-svc-4.1-Stable 资源文件推荐

探索语音合成新境界:so-vits-svc-4.1-Stable 资源文件推荐 【下载地址】so-vits-svc-4.1-Stable资源文件下载 本仓库提供 so-vits-svc-4.1-Stable 资源文件的下载。该资源文件是一个稳定版本的 so-vits-svc 模型,适用于语音合成和相关应用 项目地址: h…...

Tracy安全最佳实践:开发与生产环境的安全配置指南

Tracy安全最佳实践:开发与生产环境的安全配置指南 【免费下载链接】tracy 😎 Tracy: the addictive tool to ease debugging PHP code for cool developers. Friendly design, logging, profiler, advanced features like debugging AJAX calls or CLI s…...

运维开发必备:5分钟搞定CentOS 7下ncurses库的安装与基础使用

运维开发必备:5分钟搞定CentOS 7下ncurses库的安装与基础使用 在服务器运维和自动化工具开发中,命令行界面(CLI)的高效交互能力往往决定了管理效率的上限。当我们需要在无GUI环境的Linux服务器上开发监控面板、配置向导或系统管理…...

热敏电阻测温实战:从原理到Arduino/CircuitPython代码实现

1. 项目概述:从电阻到温度的桥梁在嵌入式开发和电子DIY项目中,温度测量是一个极其常见的需求。无论是环境监测、设备状态反馈,还是简单的温控风扇,你都需要一个可靠的“温度计”。市面上有琳琅满目的温度传感器,从数字…...

别再手动折腾了!用Docker Compose 5分钟搞定Kamailio + MySQL + RTPproxy完整SIP服务栈

5分钟极速搭建Kamailio SIP服务栈:Docker Compose实战指南 在VoIP开发领域,快速搭建可靠的SIP服务环境是每个开发者都会遇到的基础需求。传统的手动部署方式往往需要数小时甚至更长时间,涉及复杂的依赖安装、配置文件修改和服务调优。而今天&…...