基于FPGA的VGA协议实现

目录

一、VGA简介

二、VGA引脚的定义

三、VGA显示原理:

四、VESA标准下的VGA时序:

五、VGA显示模式以及相关参数:

六、数字信号与模拟信号的转换

实战演练一:VGA显示彩条

1、实验目标

2、各模块框图及其波形图

3、模块代码

4、实验结果编辑

实战演练二:显示自定义字符:我爱交大

1、实验目标:

2、各模块框图及其波箱图

3、模块代码:

4、实验结果

一、VGA简介

VGA,英文全称"Video Graphics Array”,译为视频图形阵列,是一种使用模拟信号进行视频传输的标准协议,由IBM公司于1987年推出,因其分辨率高、显示速度快、颜色丰富等优点,广泛应用于彩色显示器领域。

VGA接口:

母头:

公头:

VGA连接线两头都是公头:

使用VGA连接线将计算机和VGA显示器连接起来

二、VGA引脚的定义

1(红基色)、2(绿基色)、3(蓝基色)、13(行同步信号)、14(场同步信号)拐角最为重要

RGB色彩显示标准:根据三原色中红色、绿色、蓝色所占比例以及三原色相互之间的叠加来显示各式各样的颜色

三、VGA显示原理:

VGA显示器逐行扫描原理:逐行扫描是扫描从屏幕左上角一点开始,从左至右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置。在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号HS进行同步;当扫描完所有的行,形成一帧,用场同步信号VS进行帧同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。

四、VESA标准下的VGA时序:

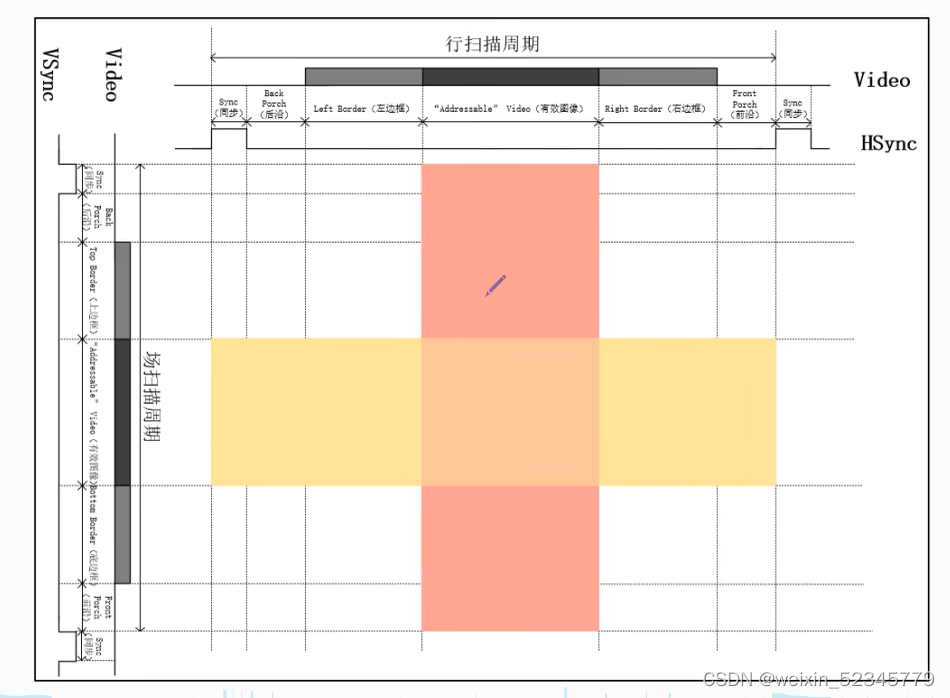

①行同步时序图

Video图像信息,GSync行同步信号

行同步信号自上升沿起到下一个上升沿止为一个周期,这个周期成为行扫描周期,一个完整的行扫描周期包含六个部分:同步、后延、左边框、有效图像、右边框、前沿。这六个部分的基本单位是一个像素,在图像传输过程中,每一个时钟周期传输一个像素点,这六个部分的基本单位也可以称作一个像素时钟周期,在一个完整的行扫描周期内,图像信息是在行同步信号的同步下完成一行图像的扫描,图像信息只有在“有效图像阶段”才是有效的,行同步信号只在同步阶段才保持高电平。

②场同步时序图

场同步信号自上升沿起到下一个上升沿止为一个周期,这个周期成为场扫描周期,一个完整的场扫描周期包含六个部分:同步、后延、左边框、有效图像、右边框、前沿。这六个部分的基本单位是一行。在一个完整的场扫描周期中,图像信息需要在行同步信号和场同步信号的共同作用下完成一帧图像的显示,图像信息只有在“场有效图像”、‘’行有效图像“两个阶段才是有效的

③VGA时序图

红色和黄色相交的位置就是VGA图像的最终显示区域

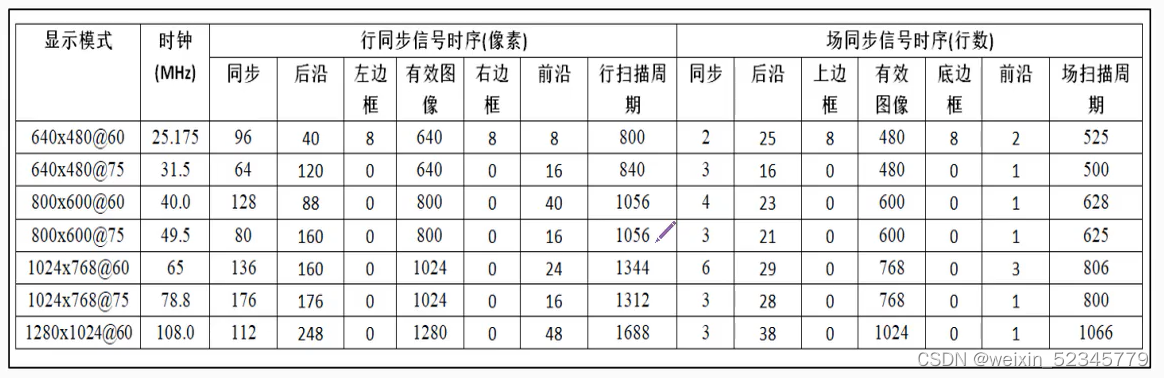

五、VGA显示模式以及相关参数:

显示模式640x480@60,640表示在一个完整的行扫描周期中,有效显示图像每一行有640个像素点,480表示一帧完整的图像有480行

640x480≈30万,表示一帧图片约包含30万个像素点,60是帧率表示在640x480@60显示模式下,每秒刷新图像60次,也就是每秒显示60帧图像。时钟25.175MHZ表示VGA显示的工作时钟,就是像素点扫描的频率,96表示在同步阶段保持96个时钟周期,40表示在后延阶段保持40个时钟周期。行扫描周期800等于行同步信号的六个阶段时钟周期相加

注:行扫描周期x场扫描周期x帧率=时钟F

例:在显示模式640x480@75中,840x500x75=31500000HZ=31.5MHZ

六、数字信号与模拟信号的转换

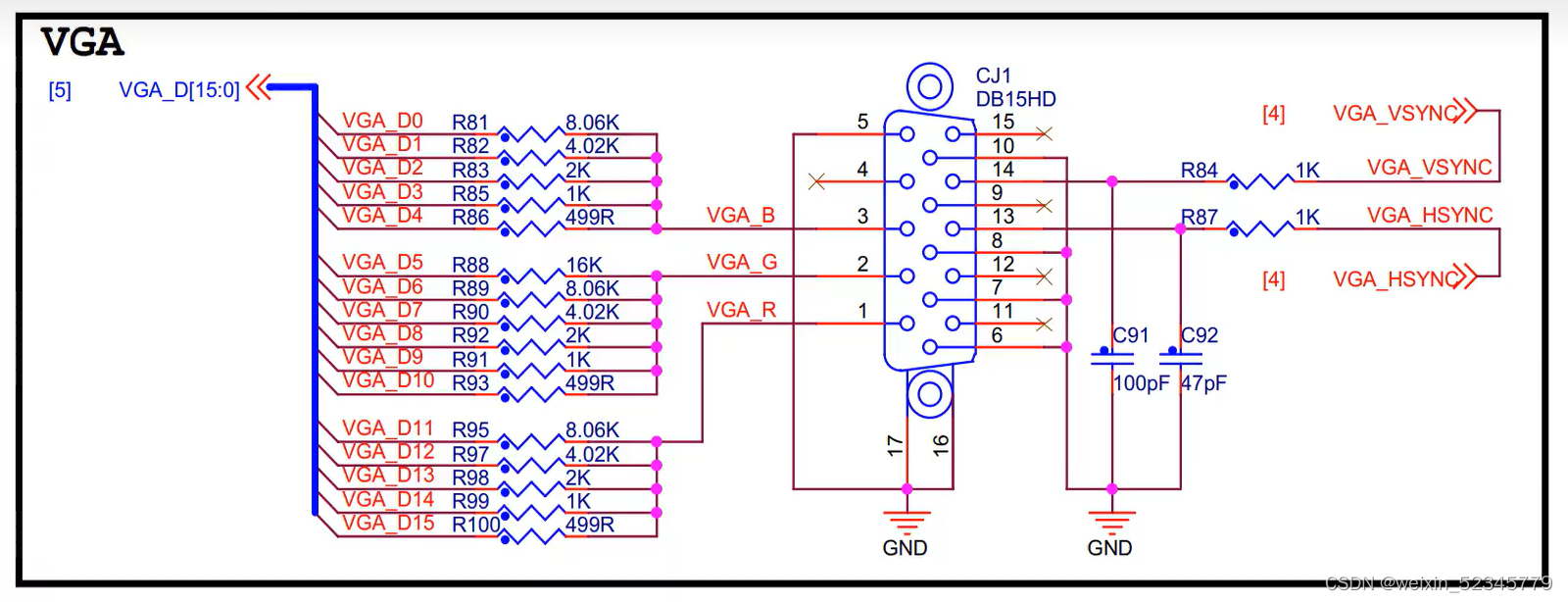

VGA传输协议传输的是模拟信号,VGA显示器只能识别模拟信号,尔FPGA处理的是数字信号,将数字信号转换为模拟限号有两种方式:AD7123等转换芯片(稳定但成本稍高)、权电阻网络(成本低)

权电阻网络原理图

征途系列开发板使用RGB565图像模式,每个像素点的位宽是16位宽(5+6+5)(红+绿+蓝),在图像显示时FPGA通过VGA_D端口将图像信号传输到权电阻网络,经过权电阻网络的数模转换,生成能够被VGA识别的图像信号VGA_R,VGA_G,VGA_B,生成的三路模拟信号的电压范围是0~0.714V,0V表示无色,0.714V表示满色

实战演练一:VGA显示彩条

1、实验目标

驱动VGA显示器,在640x480@60显示模式下显示十种颜色等宽彩条的显示

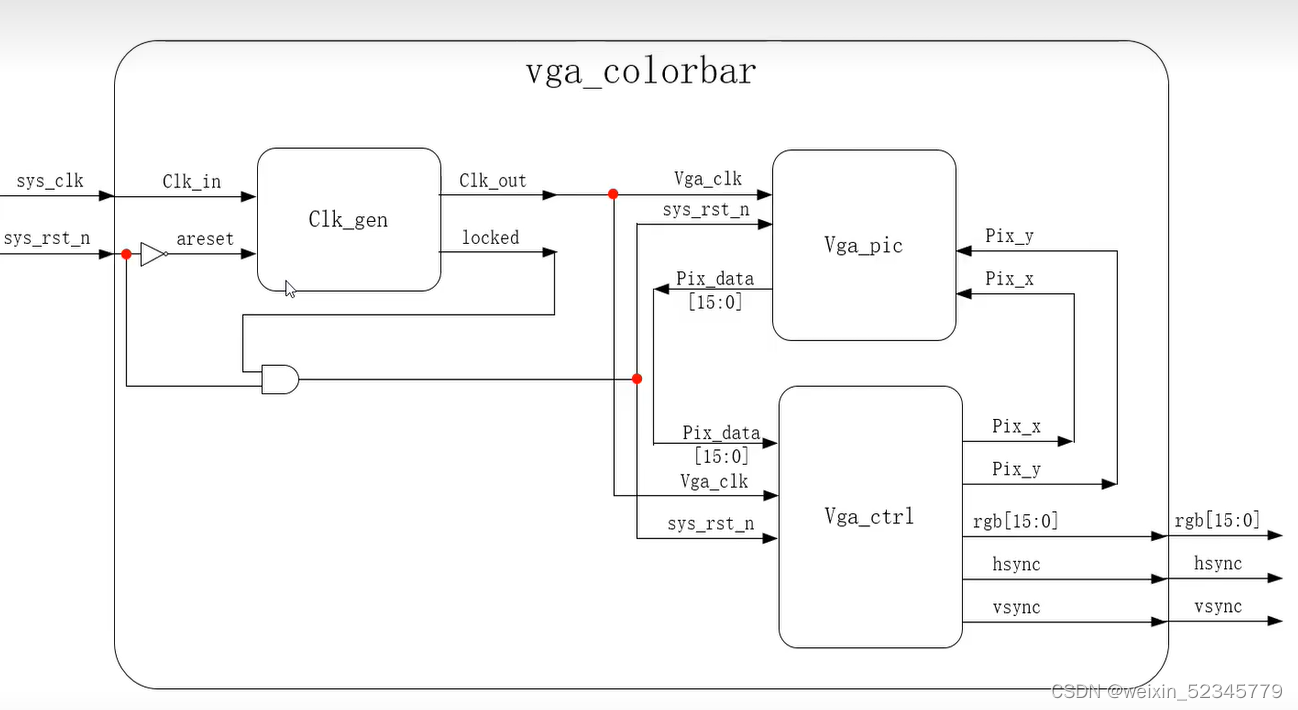

2、各模块框图及其波形图

①②顶层模块:

rgb[15:0]:图像信息,使用的是RGB565图像模式,所以位宽为16位,此信号由FPGA产生然后传输给权电阻网络

hsync:行同步信号,此信号由FPGA产生然后传输给权电阻网络

vsync:场同步限号,此信号由FPGA产生然后传输给权电阻网络

注:locked锁定信号只有为高电平的时候,分频后的时钟信号才是有效的,所以需要将系统复位信号sys_rst_n和locked进行”与''操作后再接入Vga_pic和Vga_ctrl的复位信号

②时钟分频模块:将50MHZ的系统时钟分频成25MHZ,fpga系统时钟为50MHZ,而640x480@60显示模式下时钟频率为25.175MHZ,由于25.175MHZ的频率不太方便生成。为了便于时钟的生成,这里使用25MHZ代替25.175MHZ

CLK_in:输入50MHZ的系统时钟

areset:异步复位信号

CLK_out:输出25Mhz的输出时钟

locked:锁定信号,此信号为高电平则CLK_out才可以被使用

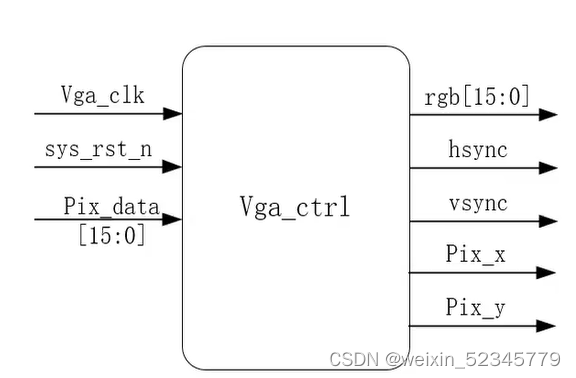

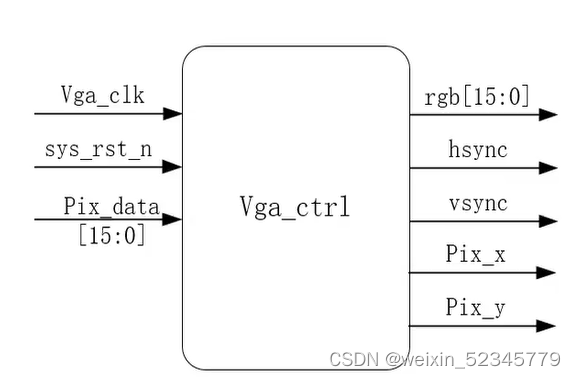

③VGA_ctrl模块:生成rgb[15:0]、hsync、vsync三路信号,以及图像的横纵坐标

Vga_clk:分频后产生的25MHZ的时

sys_rst_n:系统复位信号

Pix_data[15:0]:图像信息,和rgb[15:0]相同

rgb[15:0]:图像信息,使用的是RGB565图像模式,所以位宽为16位

hsync:行同步信号

vsync:场同步限号

Pix_x:有效图像横坐标

Pix_y:有效图像纵坐标

VGA_ctrl模块信号波形图:

cnt_h[9:0]:行计数器,对行扫描周期计数,最大值799

cnt_h[9:0]:行计数器,对行扫描周期计数,最大值799

cnt_v[9:0]:场计数器,对场扫描周期计数,行计数器完成了一个完整的行扫描周期的计数,场计数器加一,最大值524

hsync:行同步信号,在行计数器计数到0~95时(行同步阶段)时拉高,其他时间为低电平

vsync:场同步信号,在场计数器计数到0~1时(行场同步阶段)时拉高,其他时间为低电平

rgb_valid:图像有效信号,行计数器计数到有效图像范围144~783并且场计数器计数到有效图像范围35~514,此信号为高电平

Pix_x:有效图像横坐标,有效图像为高电平时,在数值上等于行计数器数值减去行同步、行后延、行边框三个阶段数值之和

Pix_y:有效图像纵坐标,有效图像为高电平时,在数值上等于场计数器数值减去场同步、场后延、场边框三个阶段数值之和

rgb[15:0]:有效图像信息,初值全零表示显示黑色,当图像有效信号rgb_valid为高电平时,rgb[15:0]=Pix_data[15:0]

图④像信息生成模块:根据有效图像坐标信息产生要显示的图像数据

vga_clk:分频后的时钟

sys_rst_n:复位信号 Pix_x:横坐标 Pix_y:纵坐标

Pix_data[15:0]:生成的图像信息

3、模块代码

clk_gen:调用pll锁相环

vga_ctrl:

`timescale 1ns/1nsmodule vga_ctrl ( //VGA控制模块input wire vga_clk ,input wire sys_rst_n ,input wire [15:0] pix_data ,//图像数据output wire [9:0] pix_x ,output wire [9:0] pix_y ,output wire hsync ,//行扫描信号output wire vsync ,//场扫描信号output wire [15:0] rgb

);parameter H_SYNC = 10'd96 , //行同步H_BACK = 10'd40 , //行时序后沿H_LEFT = 10'd8 , //行时序左边框H_VALID = 10'd640 , //行有效数据H_RIGHT = 10'd8 , //行时序右边框H_FRONT = 10'd8 , //行时序前沿H_TOTAL = 10'd800 ; //行扫描周期

parameter V_SYNC = 10'd2 , //场同步V_BACK = 10'd25 , //场时序后沿V_TOP = 10'd8 , //场时序上边框V_VALID = 10'd480 , //场有效数据V_BOTTOM = 10'd8 , //场时序下边框V_FRONT = 10'd2 , //场时序前沿V_TOTAL = 10'd525 ; //场扫描周期reg [9:0] cnt_h ;

reg [9:0] cnt_v ;

wire pix_data_req ;

wire rgb_valid ; //图像有效信号,行扫描信号位于有效图像范围并且场扫描信号位于有效图像范围时图像有效信号为高电平//cnt_h:行同步信号计数器

always @(posedge vga_clk or negedge sys_rst_n ) beginif(sys_rst_n == 1'b0)cnt_h <= 10'd0;else if(cnt_h == H_TOTAL - 1'b1 )cnt_h <= 10'd0;elsecnt_h <= cnt_h + 10'd1;

end//hsync:行同步信号

assign hsync = (cnt_h <= H_SYNC - 1'd1) ? 1'b1 : 1'b0 ;//cnt_v:场同步信号计数器

always @(posedge vga_clk or negedge sys_rst_n ) beginif(sys_rst_n == 1'b0)cnt_v <= 10'd0;else if((cnt_v == V_TOTAL - 1'd1) && (cnt_h == H_TOTAL-1'd1))cnt_v <= 10'd0;else if(cnt_h == H_TOTAL -10'd1 )cnt_v <= cnt_v + 1'd1;elsecnt_v <= cnt_v;

end

//vsync:场同步信号

assign vsync = (cnt_v <= V_SYNC - 1'd1) ? 1'b1 : 1'b0 ;//图像有效信号

assign rgb_valid = (((cnt_h >= H_SYNC + H_BACK + H_LEFT)&& (cnt_h < H_SYNC + H_BACK + H_LEFT + H_VALID))&&((cnt_v >= V_SYNC + V_BACK + V_TOP)&& (cnt_v < V_SYNC + V_BACK + V_TOP + V_VALID)))? 1'b1 : 1'b0;assign pix_data_req = (((cnt_h >= H_SYNC + H_BACK + H_LEFT - 1'b1)&& (cnt_h < H_SYNC + H_BACK + H_LEFT + H_VALID - 1'b1))&&((cnt_v >= V_SYNC + V_BACK + V_TOP)&& (cnt_v < V_SYNC + V_BACK + V_TOP + V_VALID)))? 1'b1 : 1'b0;//pix_x,pix_y:VGA有效显示区域像素点坐标

assign pix_x = (pix_data_req == 1'b1)? (cnt_h - (H_SYNC + H_BACK + H_LEFT-1'b1)) : 10'h3ff;

assign pix_y = (pix_data_req == 1'b1)? (cnt_v - (V_SYNC + V_BACK + V_TOP)) : 10'h3ff;//rgb:输出像素点色彩信息

assign rgb = (rgb_valid == 1'b1) ? pix_data : 16'b0 ;

endmodule vga_pic:

`timescale 1ns/1ns

module vga_pic

(input wire vga_clk , //输入工作时钟,频率25MHzinput wire sys_rst_n , //输入复位信号,低电平有效input wire [9:0] pix_x , //输入VGA有效显示区域像素点X轴坐标input wire [9:0] pix_y , //输入VGA有效显示区域像素点Y轴坐标output reg [15:0] pix_data //输出像素点色彩信息

);parameter H_VALID = 10'd640 , //行有效数据V_VALID = 10'd480 ; //场有效数据parameter RED = 16'hF800, //红色ORANGE = 16'hFC00, //橙色YELLOW = 16'hFFE0, //黄色GREEN = 16'h07E0, //绿色CYAN = 16'h07FF, //青色BLUE = 16'h001F, //蓝色PURPPLE = 16'hF81F, //紫色BLACK = 16'h0000, //黑色WHITE = 16'hFFFF, //白色GRAY = 16'hD69A; //灰色always@(posedge vga_clk or negedge sys_rst_n)if(sys_rst_n == 1'b0)pix_data <= 16'd0;else if((pix_x >= 0) && (pix_x < (H_VALID/10)*1))pix_data <= RED;else if((pix_x >= (H_VALID/10)*1) && (pix_x < (H_VALID/10)*2))pix_data <= ORANGE;else if((pix_x >= (H_VALID/10)*2) && (pix_x < (H_VALID/10)*3))pix_data <= YELLOW;else if((pix_x >= (H_VALID/10)*3) && (pix_x < (H_VALID/10)*4))pix_data <= GREEN;else if((pix_x >= (H_VALID/10)*4) && (pix_x < (H_VALID/10)*5))pix_data <= CYAN;else if((pix_x >= (H_VALID/10)*5) && (pix_x < (H_VALID/10)*6))pix_data <= BLUE;else if((pix_x >= (H_VALID/10)*6) && (pix_x < (H_VALID/10)*7))pix_data <= PURPPLE;else if((pix_x >= (H_VALID/10)*7) && (pix_x < (H_VALID/10)*8))pix_data <= BLACK;else if((pix_x >= (H_VALID/10)*8) && (pix_x < (H_VALID/10)*9))pix_data <= WHITE;else if((pix_x >= (H_VALID/10)*9) && (pix_x < H_VALID))pix_data <= GRAY;elsepix_data <= BLACK;

endmodulevga_colorbar:

`timescale 1ns/1nsmodule vga_colorbar

(input wire sys_clk , input wire sys_rst_n , output wire hsync , output wire vsync , output wire [15:0] rgb

);wire vga_clk ;

wire locked ;

wire rst_n ;

wire [9:0] pix_x ;

wire [9:0] pix_y ;

wire [15:0] pix_data; assign rst_n = (sys_rst_n & locked);clk_gen clk_gen_inst

(.areset (~sys_rst_n ), .inclk0 (sys_clk ), .c0 (vga_clk ), .locked (locked )

);vga_ctrl vga_ctrl_inst

(.vga_clk (vga_clk ), .sys_rst_n (rst_n ), .pix_data (pix_data ), .pix_x (pix_x ), .pix_y (pix_y ), .hsync (hsync ), .vsync (vsync ), .rgb (rgb )

);vga_pic vga_pic_inst

(.vga_clk (vga_clk ), .sys_rst_n (rst_n ), .pix_x (pix_x ), .pix_y (pix_y ), .pix_data (pix_data ) );endmodule

4、实验结果

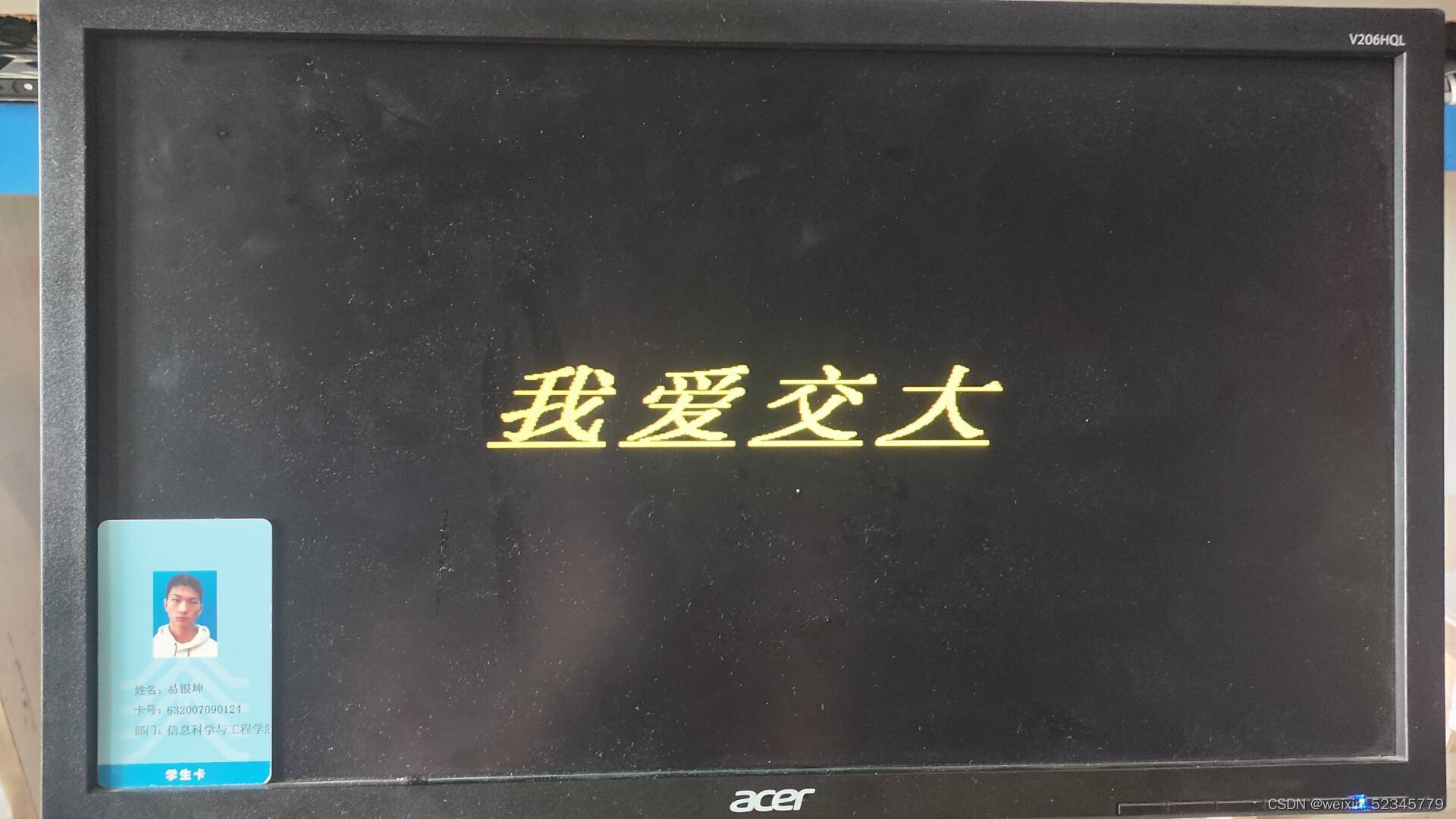

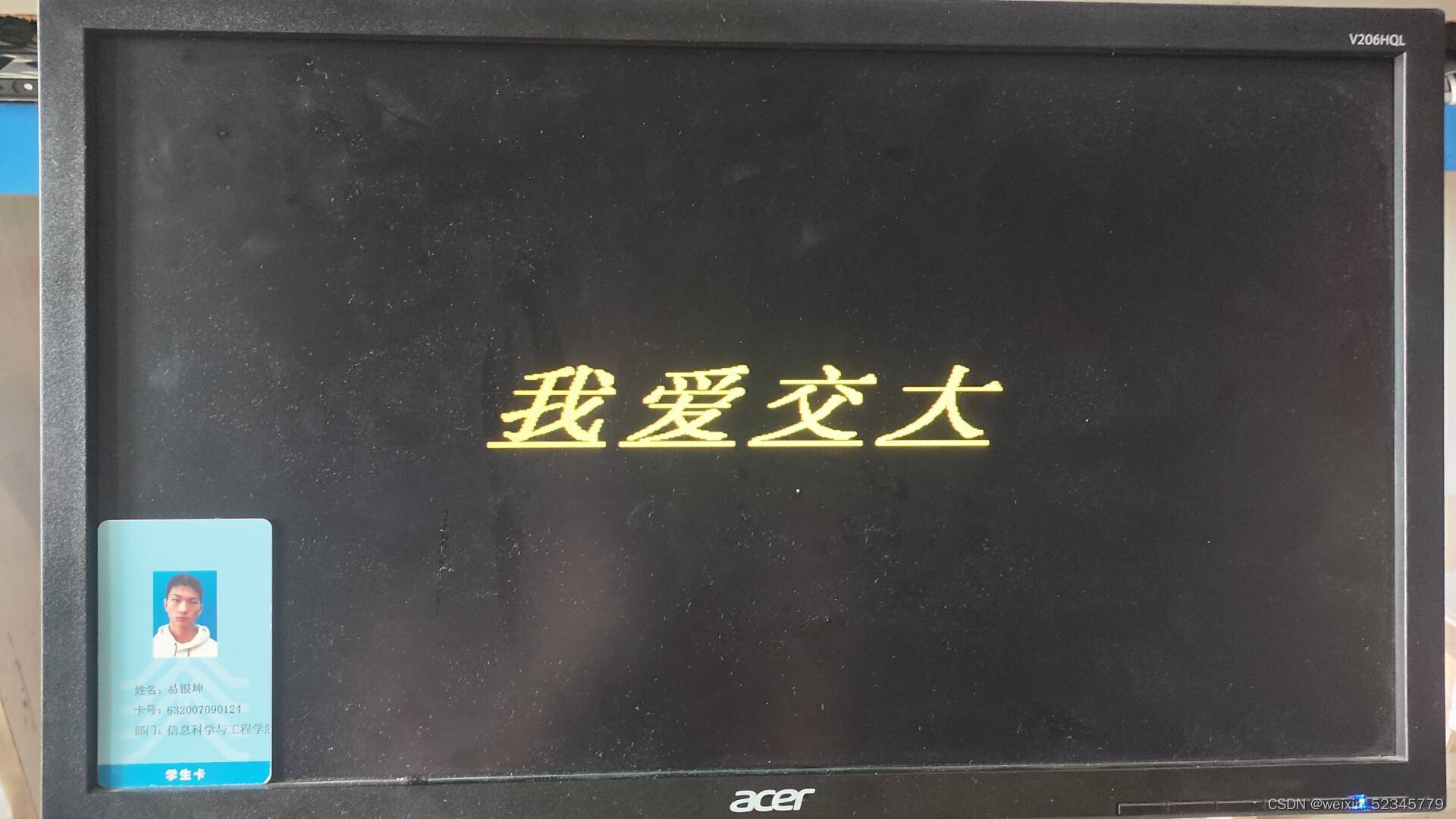

实战演练二:显示自定义字符:我爱交大

1、实验目标:

在vga显示屏上,显示点阵大小64x64,字宽x字高=56x56,显示模式640x480@60,背景为黑色的野火科技四个字符,如下:

2、各模块框图及其波箱图

顶层模块:

时钟分频模块:

vga控制模块:

图像信息生成模块:

图像信息生成模块波形图:

Vga_clk:经过时钟分频模块分频后的时钟 sys_rst_n:系统复位信号 Pix_x:由vga_ctrl产生的有效图像横坐标 Pix_y:由vga_ctrl产生的有效图像纵坐标 char_x:字符区域横坐标 char_y:字符区域纵坐标 Pix_data[15:0]:图像信息

3、模块代码:

顶层模块vga_char:

`timescale 1ns/1nsmodule vga_char

(input wire sys_clk , input wire sys_rst_n , output wire hsync , output wire vsync , output wire [15:0] rgb

);wire vga_clk ;

wire locked ;

wire rst_n ;

wire [9:0] pix_x ;

wire [9:0] pix_y ;

wire [15:0] pix_data; assign rst_n = (sys_rst_n & locked);clk_gen clk_gen_inst

(.areset (~sys_rst_n ), .inclk0 (sys_clk ), .c0 (vga_clk ), .locked (locked )

);vga_ctrl vga_ctrl_inst

(.vga_clk (vga_clk ), .sys_rst_n (rst_n ), .pix_data (pix_data ), .pix_x (pix_x ), .pix_y (pix_y ), .hsync (hsync ), .vsync (vsync ), .rgb (rgb )

);vga_pic vga_pic_inst

(.vga_clk (vga_clk ), .sys_rst_n (rst_n ), .pix_x (pix_x ), .pix_y (pix_y ), .pix_data (pix_data ) );endmodule

时钟分频模块:clk_gen,调用pll锁相环

vga控制模块:

`timescale 1ns/1nsmodule vga_ctrl

(input wire vga_clk , input wire sys_rst_n , input wire [15:0] pix_data , output wire [9:0] pix_x , output wire [9:0] pix_y , output wire hsync , output wire vsync , output wire [15:0] rgb

);parameter H_SYNC = 10'd96 , //行同步H_BACK = 10'd40 , //行时序后沿H_LEFT = 10'd8 , //行时序左边框H_VALID = 10'd640 , //行有效数据H_RIGHT = 10'd8 , //行时序右边框H_FRONT = 10'd8 , //行时序前沿H_TOTAL = 10'd800 ; //行扫描周期

parameter V_SYNC = 10'd2 , //场同步V_BACK = 10'd25 , //场时序后沿V_TOP = 10'd8 , //场时序上边框V_VALID = 10'd480 , //场有效数据V_BOTTOM = 10'd8 , //场时序下边框V_FRONT = 10'd2 , //场时序前沿V_TOTAL = 10'd525 ; //场扫描周期//wire define

wire rgb_valid ; //VGA有效显示区域

wire pix_data_req ; //像素点色彩信息请求信号//reg define

reg [9:0] cnt_h ; //行同步信号计数器

reg [9:0] cnt_v ; //场同步信号计数器//cnt_h:行同步信号计数器

always@(posedge vga_clk or negedge sys_rst_n)if(sys_rst_n == 1'b0)cnt_h <= 10'd0 ;else if(cnt_h == H_TOTAL - 1'b1)cnt_h <= 10'd0 ;elsecnt_h <= cnt_h + 1'd1 ;//hsync:行同步信号

assign hsync = (cnt_h <= H_SYNC - 1'd1) ? 1'b1 : 1'b0 ;//cnt_v:场同步信号计数器

always@(posedge vga_clk or negedge sys_rst_n)if(sys_rst_n == 1'b0)cnt_v <= 10'd0 ;else if((cnt_v == V_TOTAL - 1'd1) && (cnt_h == H_TOTAL-1'd1))cnt_v <= 10'd0 ;else if(cnt_h == H_TOTAL - 1'd1)cnt_v <= cnt_v + 1'd1 ;elsecnt_v <= cnt_v ;//vsync:场同步信号

assign vsync = (cnt_v <= V_SYNC - 1'd1) ? 1'b1 : 1'b0 ;//rgb_valid:VGA有效显示区域

assign rgb_valid = (((cnt_h >= H_SYNC + H_BACK + H_LEFT)&& (cnt_h < H_SYNC + H_BACK + H_LEFT + H_VALID))&&((cnt_v >= V_SYNC + V_BACK + V_TOP)&& (cnt_v < V_SYNC + V_BACK + V_TOP + V_VALID)))? 1'b1 : 1'b0;//pix_data_req:像素点色彩信息请求信号,超前rgb_valid信号一个时钟周期

assign pix_data_req = (((cnt_h >= H_SYNC + H_BACK + H_LEFT - 1'b1)&& (cnt_h < H_SYNC + H_BACK + H_LEFT + H_VALID - 1'b1))&&((cnt_v >= V_SYNC + V_BACK + V_TOP)&& (cnt_v < V_SYNC + V_BACK + V_TOP + V_VALID)))? 1'b1 : 1'b0;//pix_x,pix_y:VGA有效显示区域像素点坐标

assign pix_x = (pix_data_req == 1'b1)? (cnt_h - (H_SYNC + H_BACK + H_LEFT - 1'b1)) : 10'h3ff;

assign pix_y = (pix_data_req == 1'b1)? (cnt_v - (V_SYNC + V_BACK + V_TOP)) : 10'h3ff;//rgb:输出像素点色彩信息

assign rgb = (rgb_valid == 1'b1) ? pix_data : 16'b0 ;endmodule

图像信息生成模块:

module vga_pic (input wire vga_clk,input wire sys_rst_n,input wire [9:0] pix_x,input wire [9:0] pix_y,output reg [15:0] pix_data

);

parameter CHAR_B_H = 10'd192 ,//字符开始X轴坐标CHAR_B_V = 10'd208 ;//字符开始Y轴坐标parameter CHAR_W = 10'd256,//字符宽度CHAR_H = 10'd64 ;//字符高度parameter BLACK = 16'h0000,GOLDEN = 16'hFEC0;reg [CHAR_W-1:0] char [CHAR_H -1:0]; //存储器变量,位宽256,深度64,表示char有64个存储单元,每个单元能存储的位宽是256wire [9:0] char_x;

wire [9:0] char_y;assign char_x = (((pix_x >= CHAR_B_H) && (pix_x < CHAR_B_H + CHAR_W)) && ((pix_y >= CHAR_B_V) && (pix_y < CHAR_B_V + CHAR_H)))? (pix_x - CHAR_B_H) : 10'h3ff;assign char_y = (((pix_x >= CHAR_B_H) && (pix_x < CHAR_B_H + CHAR_W)) && ((pix_y >= CHAR_B_V) && (pix_y < CHAR_B_V + CHAR_H)))? (pix_y - CHAR_B_V) : 10'h3ff;always@(posedge vga_clk)

beginchar[0]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[1]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[2]<=256'h0000000000070000000000000000001E0000000003C000000000000000E00000;

char[3]<=256'h00000000038F800000000000000000FE0000000003E000000000000000F80000;

char[4]<=256'h000000000FCFE0000000000000001FFF0000000003F000000000000000FE0000;

char[5]<=256'h000000003FCFEF00000000000007FFFF0000000001F800000000000001FE0000;

char[6]<=256'h00000001FFDFCF800000000007FFFFFF0000000001FC00000000000001F80000;

char[7]<=256'h0000001FFFDF87E0000001FFFFFFFFC00000000001FC00000000000001F00000;

char[8]<=256'h000003FFFE1F07F0000001FFFFC003E00000000000FC000E0000000003F00000;

char[9]<=256'h00003FFFC01F03F80000001C03C007F00000000000F8001E0000000003F00000;

char[10]<=256'h00003F0F803F03F80000001E03E00FF00000000000F8007F0000000003E00000;

char[11]<=256'h0000000F803E03F80000001F01F01FC00000000000F000FF0000000007E00000;

char[12]<=256'h0000001F803E01F80000001F81F83F800000FFFFFFFFFFFF0000000007E00000;

char[13]<=256'h0000001F007E01F80000001F81F83E000000FFFFFFFFFFFF0000000007C0001C;

char[14]<=256'h0000001F007C01F00000000F81F87C000000000000000000000000000FC0003C;

char[15]<=256'h0000003F007C00E00000000F81F0F80000000007800E0000000000000FC000FE;

char[16]<=256'h0000003E00FC007000001C0F81F1F0000000000FC00F8000000000000F8001FE;

char[17]<=256'h0000003E00F801F800001C0F01E3C0780000003FC007E0000003FFFFFFFFFFFF;

char[18]<=256'h0000007E00F803FC00003C0E000381FC0000007FC003F8000003FFFFFFFFFFFF;

char[19]<=256'h0007FFFFFFFFFFFC00007FFFFFFFFFFC000000FF0001FC00000000001F000000;

char[20]<=256'h0007FFFFFFFFFFFC0000FFFFFFFFFFFC000001FC0000FF00000000003F000000;

char[21]<=256'h000000FC01F000000000F801C00003F8000007F800007F80000000003F000000;

char[22]<=256'h000000F801F000000003F003F00007E000000FF8003C7F80000000007F000000;

char[23]<=256'h000000F803F01E000007F003F0000F8000003FB8003F3F80000000007F000000;

char[24]<=256'h000001F803E03E00000FE007F0001F0000007F38007F9F8000000000FF000000;

char[25]<=256'h000001F003E07F00000FE007E0003E000001FC3800FF9F8000000000FF000000;

char[26]<=256'h000001F003E0FF00000F8007C00078000003F03800FE0F8000000001FF000000;

char[27]<=256'h000003F07BE1FE000000000FC001FC00000FC03C01FC0F0000000001FF000000;

char[28]<=256'h000003E3FFC3F8000001FFFFFFFFFE00003F003C03F8000000000003FF000000;

char[29]<=256'h000003FFE7C7F0000001FFFFFFFFFE00003C003C03F0000000000007EF000000;

char[30]<=256'h000007FF07CFE0000000003F000000000000003C07E0000000000007EF800000;

char[31]<=256'h00001FF807DFC0000000003E000700000000003C0FC000000000000FCF800000;

char[32]<=256'h0001FFE007FF80000000007E001F80000000003E1F8000000000001F87800000;

char[33]<=256'h001FFFC00FFF0000000000FFFFFFC0000000003E3F8000000000001F87800000;

char[34]<=256'h01FFFF800FFE0000000000FFFFFFC0000000001E7F0000000000003F07C00000;

char[35]<=256'h01FFFF800FF80000000001FE007F80000000001FFE0000000000007E07C00000;

char[36]<=256'h01FF1F000FF00000000003FE00FE00000000001FFC000000000000FC07C00000;

char[37]<=256'h00FC1F000FE00000000007FF01FC00000000001FF8000000000001F803E00000;

char[38]<=256'h00F03F001FC0070000000FDF03F800000000001FE0000000000003F803E00000;

char[39]<=256'h00003E007FC00F0000001F8F8FF000000000000FC0000000000007F003F00000;

char[40]<=256'h00003E00FFE00E0000003F0F9FC000000000003FC000000000000FE001F80000;

char[41]<=256'h00007E03FFE01E0000007E07FF8000000000007FE000000000001FC001FC0000;

char[42]<=256'h00007C0FF7F01E000001F807FF000000000001FFF000000000007F0001FE0000;

char[43]<=256'h00007C3FC3F83C000003F003FC000000000007FBFC0000000000FE0000FF0000;

char[44]<=256'h0000FC7F03F83C000007E007FC00000000001FE1FF0000000001FC0000FF8000;

char[45]<=256'h0000F9FC01FE7C00001F801FFF00000000007F80FFC000000007F000007FE000;

char[46]<=256'h00E1FFF001FF7800003F007FFFF000000001FE007FFC0000001FE000003FFC00;

char[47]<=256'h00FFFF8000FFF80000FC01FF7FFFE0000007F8003FFFFC00003F8000001FFC00;

char[48]<=256'h00FFFC00007FF80001F80FFC1FFFF800003FE0001FFFFC0000FE0000001FFC00;

char[49]<=256'h003FF000003FF80007E07FE007FFF80001FF000007FFF80007F80000000FE000;

char[50]<=256'h001FE000001FF8000F87FF0000FFE0000FF8000000FFE0001FC0000000078000;

char[51]<=256'h000F80000003F8000E3FF000001FC0003FC00000001FC0007F00000000000000;

char[52]<=256'h000E000000007800003E0000000000003C000000000000007800000000000000;

char[53]<=256'hFFFFFFFFFFFFFF80FFFFFFFFFFFFFF80FFFFFFFFFFFFFF80FFFFFFFFFFFFFF80;

char[54]<=256'hFFFFFFFFFFFFFF80FFFFFFFFFFFFFF80FFFFFFFFFFFFFF80FFFFFFFFFFFFFF80;

char[55]<=256'hFFFFFFFFFFFFFF80FFFFFFFFFFFFFF80FFFFFFFFFFFFFF80FFFFFFFFFFFFFF80;

char[56]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[57]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[58]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[59]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[60]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[61]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[62]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[63]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

endalways@(posedge vga_clk or negedge sys_rst_n)beginif(sys_rst_n == 1'b0)pix_data <= BLACK;else if((((pix_x >= CHAR_B_H-1'b1) && (pix_x <= CHAR_B_H + CHAR_W-1'b1)) && ((pix_y >= CHAR_B_V) && (pix_y <= CHAR_B_V + CHAR_H)))&& (char[char_y][10'd255- char_x] == 1'b1))pix_data <= GOLDEN;else pix_data <= BLACK;

endendmodule4、实验结果

相关文章:

基于FPGA的VGA协议实现

目录 一、VGA简介 二、VGA引脚的定义 三、VGA显示原理: 四、VESA标准下的VGA时序: 五、VGA显示模式以及相关参数: 六、数字信号与模拟信号的转换 实战演练一:VGA显示彩条 1、实验目标 2、各模块框图及其波形图 3、模块代…...

Java线程池的抛弃策略

Java线程池的抛弃策略 Java线程池是Java并发编程中非常重要的一个组件。它通过重用已创建的线程来减少线程创建和销毁的开销,从而提高应用程序的性能和响应速度。然而,当线程池中的任务数量超过其处理能力时,就需要一种机制来处理新提交的任…...

【python】Sklearn—Cluster

参考学习来自 10种聚类算法的完整python操作示例 文章目录 聚类数据集亲和力传播——AffinityPropagation聚合聚类——AgglomerationClusteringBIRCH——Birch(✔)DBSCAN——DBSCANK均值——KMeansMini-Batch K-均值——MiniBatchKMeans均值漂移聚类——…...

测试开发面经分享,面试七天速成 DAY 1

1. get、post、put、delete的区别 a. get请求: i. 用于从服务器获取资源。请求参数附加在URL的查询字符串中。 ii. 对服务器的请求是幂等的,即多次相同的GET请求应该返回相同的结果。 iii. 可以被缓存,可以被收藏为书签。 iv. 对于敏感数据不…...

C++ Primer Plus第五版笔记(p201-250)

第六章 函数(下) 在含有return语句的循环后面应该也有一条return语句 不要返回局部对象的引用或指针,当函数结束时临时对象占用的空间也就随之释放掉了,所以两条return语句都指向了不再可用的内存空间。 如果函数返回指针、引用…...

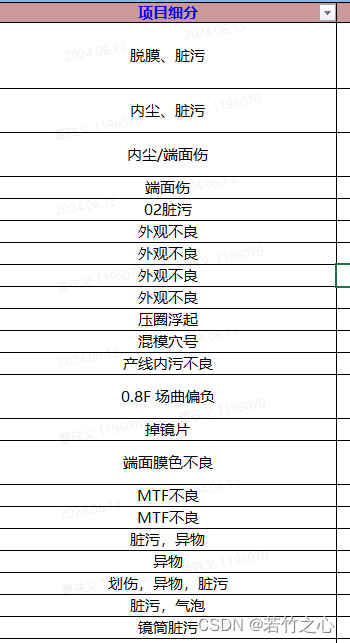

vba学习系列(5)--指定区域指定字符串计数

系列文章目录 文章目录 系列文章目录前言一、需求背景二、vba自定义函数1.引入库 总结 前言 一、需求背景 想知道所有客诉项目里面什么项目最多,出现过多少次。 二、vba自定义函数 1.引入库 引用: CountCharInRange(区域,“字符串”) Function CountCh…...

将Firefox插件导入Edge/Chrome中

目录 将Firefox插件导入Edge/Chrome中前言导出火狐插件.xpi格式插件导入edge/chorme中错误示范1错误示范2修改过程manifest.jsondict文件夹修改backgroundScript.jsinjectedScript.jsdebug过程最终backgroundScript.js和injectedScript.js代码 完工阶段修改后的源码 将Firefox插…...

云计算【第一阶段(14)】Linux的目录和结构

一、Liunx目录结构 1.1、linux目录结构 linux目录结构是树形目录结构 根目录(树根) 所有分区,目录,文件等的位置起点整个树形目录结构中,使用独立的一个"/",表示 1.2、常见的子目录 必须知道 目录路径目…...

Zynq学习笔记--AXI4-Stream到视频输出IP是如何工作的?

目录 1. 简介 2. 原理详解 2.1 示例工程 2.2 AXI4-Stream to Video Out 3. Master/Slave Timing Mode 3.1 Slave Timing Mode 3.2 Master Timing Mode 4. 总结 1. 简介 本文主要介绍了 AXI4-Stream 到视频输出 的内容。其中,示例工程展示了一个具体的设计&…...

2016-2023 年美国农业部作物序列边界

简介 2016-2023 年美国农业部作物序列边界 作物序列边界(CSB)是与美国农业部经济研究局合作开发的,它提供了美国毗连地区的田间边界、作物种植面积和作物轮作的估计数据。该数据集利用卫星图像和其他公共数据,并且是开放源码的,使用户能够对美国种植的商品进行面积和统计…...

数字人源码部署怎么做?如何高效搭建好用的数字人系统?

作为人工智能时代的风口项目,AI数字人自出现之日起便引发了大量的关注。不少创业者都有了搭建数字人系统的想法,但却苦于没有强大的专业背景和雄厚资金支撑,只能在局外徘徊,而这恰恰为数字人源码公司推出的数字人源码部署服务的火…...

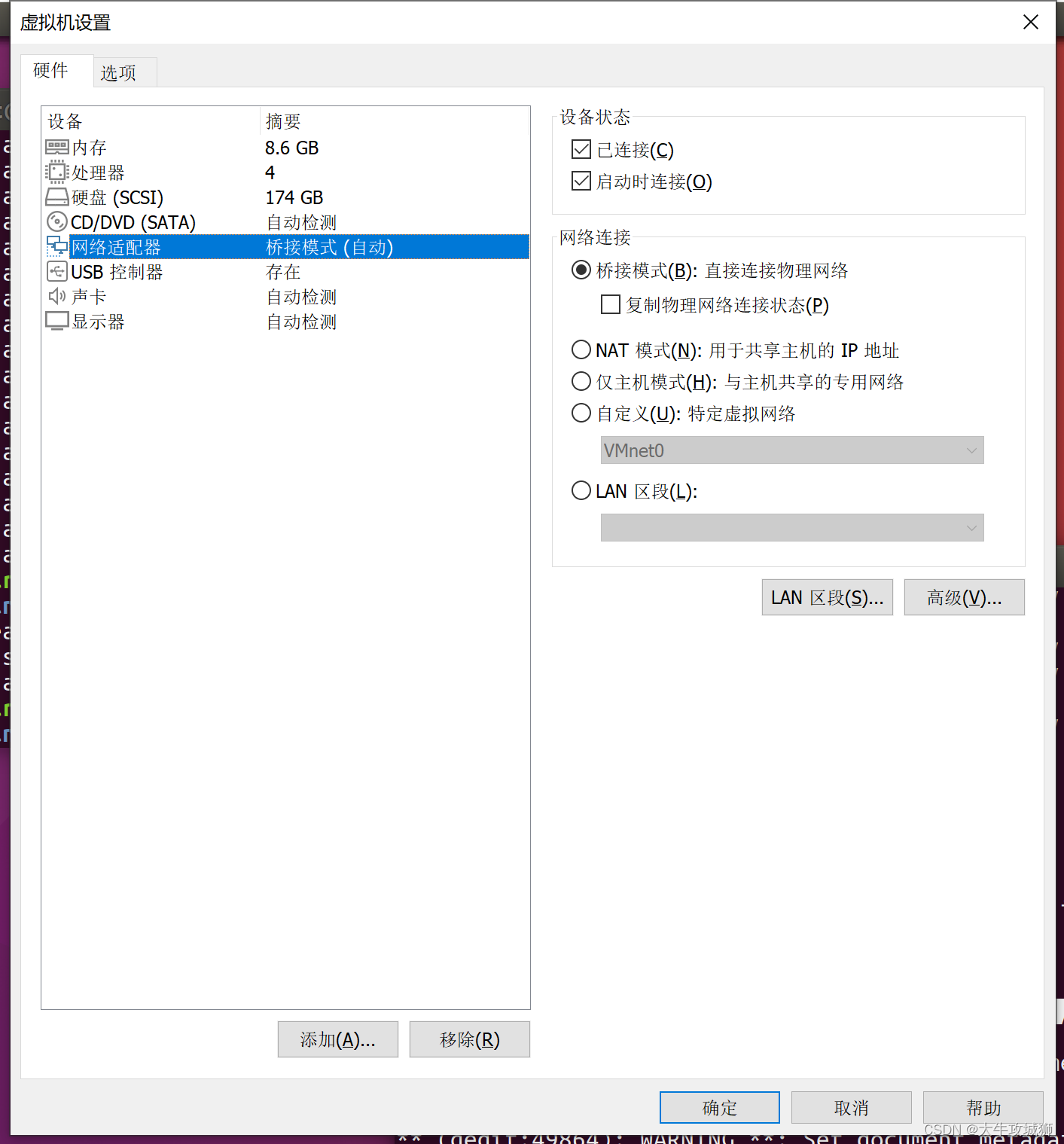

解决虚拟机Ubuntu IP总是掉的问题

问题 嵌入式开发过程中,需要使用NFS/TFTP等等,虚拟机Ubuntu就需要和板卡进行网络连接,但是我发现虚拟机Ubuntu的IP地址经常动不动就掉线,本文记录解决该问题的一些思路。 其实这个问题很简单,我早该想到,…...

[13] CUDA_Opencv联合编译过程

CUDA_Opencv联合编译过程 详细编译过程可见我之前的文章:Win10下OpencvCUDA联合编译详细教程(版本455、460、470,亲测可用!!!)本文给出Windows\linux下的opencvcuda的编译总结,摘自 <基于GP…...

uni-app canvas创建画布

canvasTmp: function(arr2, store_name, successFn, errFun) {let that this;const ctx uni.createCanvasContext(myCanvas);ctx.clearRect(0, 0, 0, 0);/*** 只能获取合法域名下的图片信息,本地调试无法获取* */uni.getImageInfo({ src: arr2[0],success: function(res) {…...

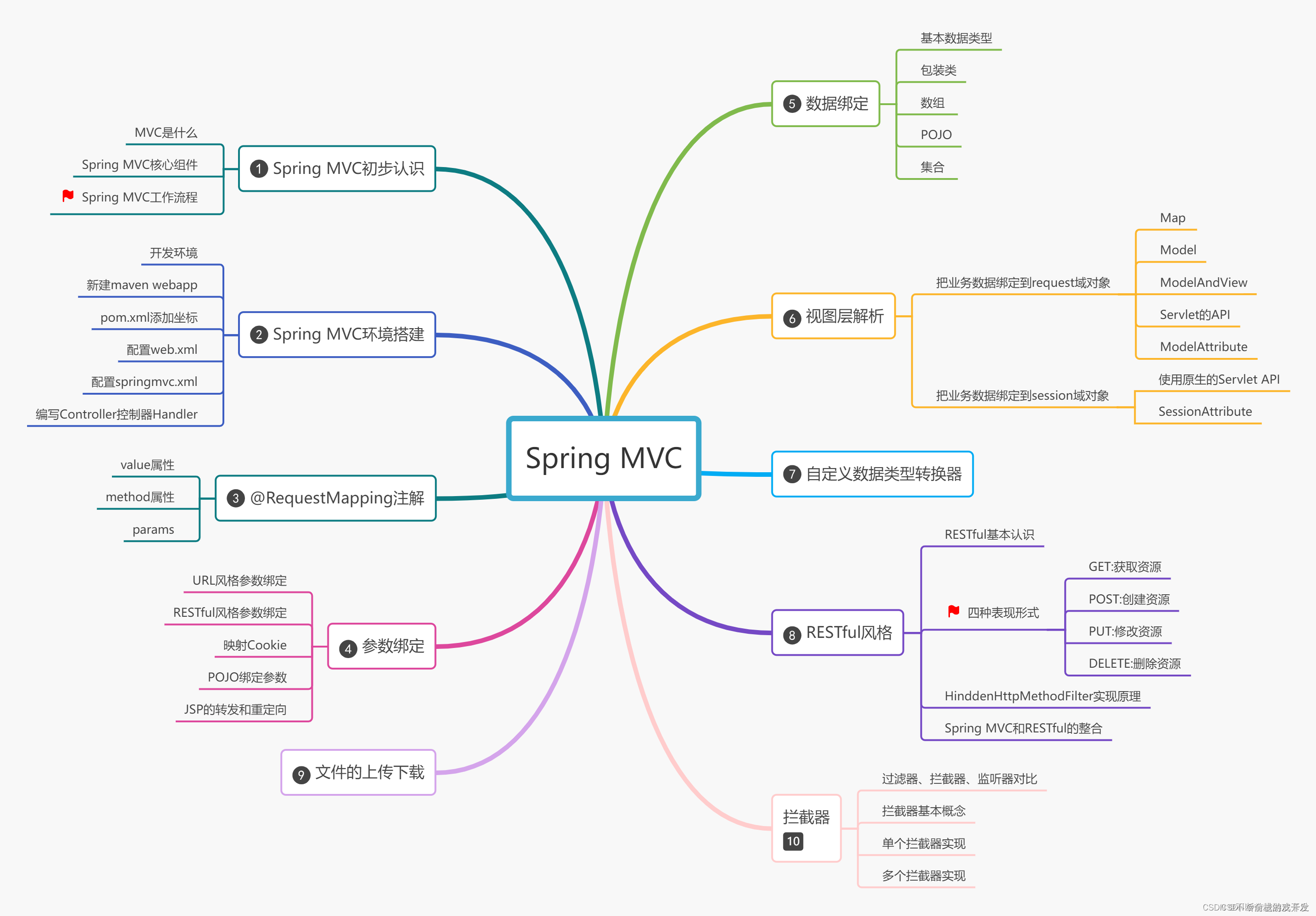

Spring MVC详解(上)

一、Spring MVC初步认识 1.1介绍 Spring MVC是Spring Framework提供的Web组件,全称是Spring Web MVC,是目前主流的实现MVC设计模式的框架,提供前端路由映射、视图解析等功能 Java Web开发者必须要掌握的技术框架 1.2MVC是什么 MVC是一种软件架构思想…...

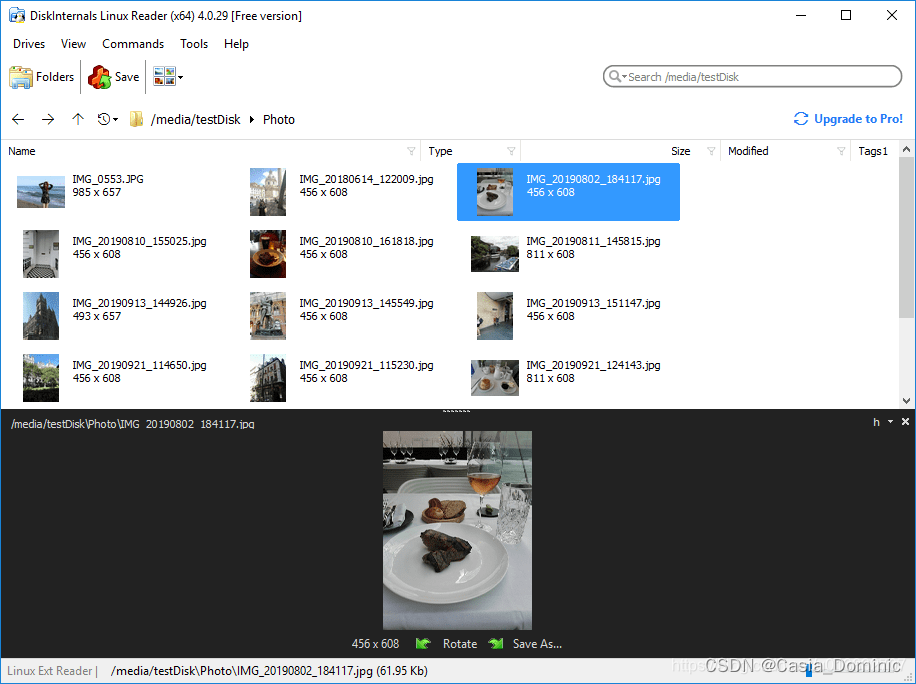

【Linux硬盘读取】Windows下读取Linux系统的文件解决方案:Linux Reader4.5 By DiskInternals

前言 相信做机器视觉相关的很多人都会安装 Windows 和 Linux 双系统。在 Linux 下,我们可以很方便的访问Windows的磁盘,反过来却不行。但是这又是必须的。通过亲身体验,向大家推荐这么一个工具,可以让 Windows 方便的访问 Ext 2/3…...

操作系统—页表(实验)

文章目录 页表1.实验目标2.实验过程记录(1).增加打印页表函数(2).独立内核页表(3).简化软件模拟地址翻译 3.实验问题及相应解答问题1问题2问题3问题4 实验小结 页表 1.实验目标 了解xv6内核当中页表的实现原理,修改页表,使内核更方便地进行用户虚拟地址…...

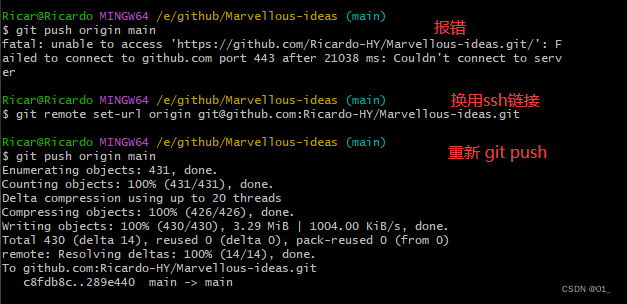

github 本地仓库上传及报错处理

一.本地文件上传 这里为上传部分,关于gitbash安装配置,读者可自行搜索,由于已经安装完成,未进行截图保存,这里便不做赘述。 1.登录git账号并创建一个仓库 点击仓库打开后会看到这个仓库的网址链接(这个链…...

)

【ZZULIOJ】1104: 求因子和(函数专题)

题目描述 输入正整数n(2<n<1000),计算并输出n的所有正因子(包括1,不包括自身)之和。要求程序定义一个FacSum ()函数和一个main()函数,FacSum ()函数计算并返回n的所有正因子之和,其余功能在main()函…...

轨迹优化 | 图解欧氏距离场与梯度场算法(附ROS C++/Python实现)

目录 0 专栏介绍1 什么是距离场?2 欧氏距离场计算原理3 双线性插值与欧式梯度场4 仿真实现4.1 ROS C实现4.2 Python实现 0 专栏介绍 🔥课程设计、毕业设计、创新竞赛、学术研究必备!本专栏涉及更高阶的运动规划算法实战:曲线生成…...

为AI智能体构建自动化RSS信息管道:agent-rss工具详解与实践

1. 项目概述:为AI智能体打造的RSS信息管道 如果你正在构建或使用AI智能体(比如Claude Code、OpenClaw这类工具),并且希望它们能像人类一样,定时、定向地获取互联网上的最新信息,那么你很可能需要一个专门为…...

Versal AI Engine加速椭圆曲线密码学计算实践

1. 项目概述:Versal AI Engine加速椭圆曲线密码学计算在当今的数字安全领域,椭圆曲线密码学(ECC)因其高安全性和计算效率成为主流方案。其中,多标量乘法(MSM)作为ECC的核心运算,在零…...

Rust异步运行时rustclaw:高性能任务调度与并发编程实践

1. 项目概述与核心价值最近在折腾一个需要处理大量网络请求和并发任务的后台服务,性能瓶颈卡得我有点难受。传统的异步框架用起来总觉得不够“爽利”,要么是内存占用高,要么是并发模型复杂,调试起来像在走迷宫。就在我四处翻找有没…...

Keyviz完全指南:5分钟掌握实时键鼠可视化技巧

Keyviz完全指南:5分钟掌握实时键鼠可视化技巧 【免费下载链接】keyviz Keyviz is a free and open-source tool to visualize your keystrokes ⌨️ and 🖱️ mouse actions in real-time. 项目地址: https://gitcode.com/gh_mirrors/ke/keyviz 你…...

抖音图片怎么去水印?2026实测免费去水印方法全盘点,这几款工具真好用

抖音图片怎么去水印?2026实测免费去水印方法全盘点,这几款工具真好用 刷抖音的时候,你有没有遇到过这种情况:看到一张超好看的图片,点保存,结果发现角落里多了一行「用户名」或者一个抖音 Logo,…...

京东自动评价工具:3分钟解决购物评价难题的智能助手

京东自动评价工具:3分钟解决购物评价难题的智能助手 【免费下载链接】jd_AutoComment 自动评价,仅供交流学习之用 项目地址: https://gitcode.com/gh_mirrors/jd/jd_AutoComment 还在为购物后的评价烦恼吗?每次收到京东的"待评价"提醒&…...

基于官方API的WhatsApp AI助手集成:规避封号风险与实战部署指南

1. 项目概述:为你的AI助手开通一个安全的WhatsApp专线 如果你正在使用OpenClaw构建自己的AI助手,并且希望它能通过WhatsApp与用户自然交流,那么你很可能已经研究过各种方案了。市面上常见的方案,比如基于 whatsapp-web.js 或 …...

AI技能包实战:用cc-skills打造专业级AI编程助手

1. 项目概述:为你的AI助手装上“专业工具箱”如果你和我一样,每天都在和Claude、Cursor、Copilot这类AI编程助手打交道,那你肯定遇到过这样的场景:想让AI帮你写一篇符合公司技术博客规范的PR稿,或者生成一段精准的Prom…...

ROS2导航SLAM建图实战:从Gazebo仿真到真实地图构建

1. 环境准备与基础配置 第一次接触ROS2导航和SLAM建图的朋友可能会觉得配置环境很复杂,其实只要跟着步骤一步步来,半小时就能搞定。我用的是一台装了Ubuntu 20.04的笔记本,ROS2版本选择Foxy,这个组合最稳定。记得先更新系统&#…...

风机技术演进与主动冷却系统优化实践

1. 风机技术演进与主动空气冷却系统优化作为一名在热管理领域工作多年的工程师,我见证了风机技术从简单的散热部件发展为精密的热管理系统的全过程。现代电子设备功率密度不断提升,从智能手机到数据中心服务器,散热设计已成为产品成败的关键因…...