【RISC-V设计-12】- RISC-V处理器设计K0A之验证环境

【RISC-V设计-12】- RISC-V处理器设计K0A之验证环境

文章目录

- 【RISC-V设计-12】- RISC-V处理器设计K0A之验证环境

- 1.简介

- 2.验证顶层

- 3.顶层代码

- 4.模型结构

- 4.1 地址映射

- 4.2 特殊功能寄存器

- 5.模型代码

- 6.运行脚本

- 7.总结

1.简介

在前几篇文章中,分别介绍了各个模块的设计,本篇文章将会针对k0a_core_top层搭建一个简单的验证环境。

2.验证顶层

3.顶层代码

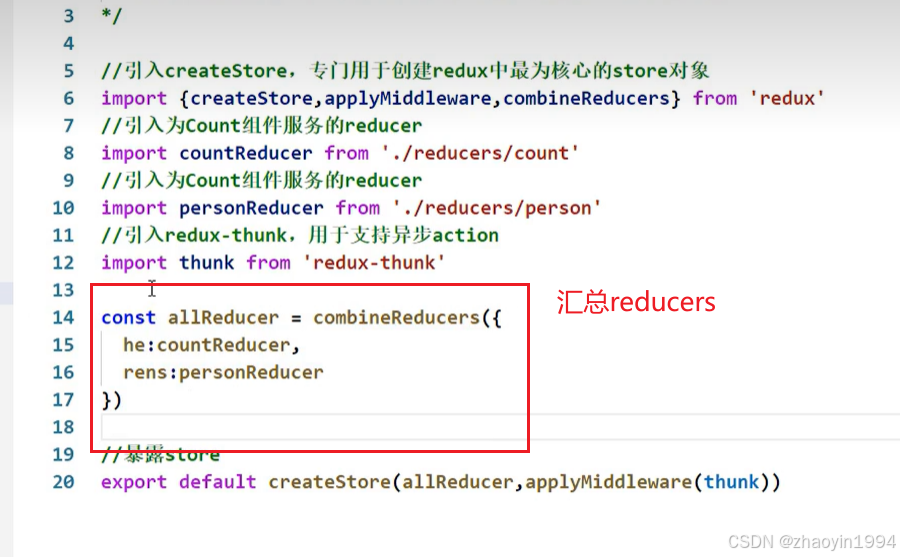

// -------------------------------------------------------------------------------------------------

// Copyright 2024 Kearn Chen, kearn.chen@aliyun.com

//

// Licensed under the Apache License, Version 2.0 (the "License");

// you may not use this file except in compliance with the License.

// You may obtain a copy of the License at

//

// http://www.apache.org/licenses/LICENSE-2.0

//

// Unless required by applicable law or agreed to in writing, software

// distributed under the License is distributed on an "AS IS" BASIS,

// WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

// See the License for the specific language governing permissions and

// limitations under the License.

// -------------------------------------------------------------------------------------------------

// Description :

// 1. testbench for simulation

// -------------------------------------------------------------------------------------------------`timescale 1ns/10psmodule test_top();reg core_clk ;

reg core_rstn ;wire bus_avalid ;

wire bus_aready ;

wire bus_write ;

wire [17:0] bus_addr ;

wire [3:0] bus_strb ;

wire [31:0] bus_wdata ;

wire bus_rvalid ;

wire bus_rready ;

wire [31:0] bus_rdata ;reg [15:0] irq_lines ;k0a_core_top dut (.core_clk (core_clk ),.core_rstn (core_rstn ),.bus_avalid (bus_avalid ),.bus_aready (bus_aready ),.bus_write (bus_write ),.bus_addr (bus_addr ),.bus_strb (bus_strb ),.bus_wdata (bus_wdata ),.bus_rvalid (bus_rvalid ),.bus_rready (bus_rready ),.bus_rdata (bus_rdata ),.irq_lines (irq_lines )

);slave_model u_slave (.clk (core_clk ),.rstn (core_rstn ),.avalid (bus_avalid ),.aready (bus_aready ),.write (bus_write ),.addr (bus_addr ),.strb (bus_strb ),.wdata (bus_wdata ),.rvalid (bus_rvalid ),.rready (bus_rready ),.rdata (bus_rdata )

);initial begincore_clk = 1'b0;forever #10 core_clk = ~core_clk;

endinitial begincore_rstn = 1'b0;irq_lines = 16'd0;initcase();#1000;core_rstn = 1'b1;testcase();$finish();

end`ifdef DUMP_LXT2initial begin$dumpfile("test_top.lxt2");$dumpvars(0, test_top);

end`endif`include "testcase.v"task load_instr(string path);integer i, fd, ret;reg [7:0] data;fd = $fopen($sformatf("../test/%s", path), "rb");if(fd == 0) begin$display("Open file : ../test/%s failed!", path);endfor(i=0; i<131072; i++) beginu_slave.imem[i] = 32'd0;endi = 0;while($feof(fd) == 0) beginret = $fread(data, fd);u_slave.imem[i/4][(i%4)*8+:8] = data;i++;end$fclose(fd);endtaskendmodule

在测试顶层代码中,连接了DUT的时钟、复位以及中断信号,总线的丛机模型和内核相连接。同时,提供了一个加载初始化软件代码的任务,验证用例通过load_instr任务,可加载二进制Bin文件到丛机模型中,在复位结束后,内核开始运行软件代码。

4.模型结构

4.1 地址映射

4.2 特殊功能寄存器

| 地址 | 寄存器 | 位宽 | 属性 | 描述 |

|---|---|---|---|---|

| 0xC0000 | DATA | 8 | WO | 队列的地址,软件可通过向此地址写入ASCII字符,输出到终端显示,以换行符\n结尾 |

| 0xC0004 | FINISH | 32 | WO | 写入数据0x12345678后,仿真运行结束 |

| 0xC0008 | CLOCK | 32 | RO | 时钟计数器,在复位结束后开始每个时钟周期自增1 |

| 0xC000C | SPEED | 8 | RW | 模型的总线速度,0:模型会随机拉住总线的ready,1:总线ready一直为1 |

5.模型代码

// -------------------------------------------------------------------------------------------------

// Copyright 2024 Kearn Chen, kearn.chen@aliyun.com

//

// Licensed under the Apache License, Version 2.0 (the "License");

// you may not use this file except in compliance with the License.

// You may obtain a copy of the License at

//

// http://www.apache.org/licenses/LICENSE-2.0

//

// Unless required by applicable law or agreed to in writing, software

// distributed under the License is distributed on an "AS IS" BASIS,

// WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

// See the License for the specific language governing permissions and

// limitations under the License.

// -------------------------------------------------------------------------------------------------

// Description :

// 1. slave model for simulation

// -------------------------------------------------------------------------------------------------module slave_model (input wire clk ,input wire rstn ,input wire avalid ,output wire aready ,input wire write ,input wire [17:0] addr ,input wire [3:0] strb ,input wire [31:0] wdata ,output wire rvalid ,input wire rready ,output wire [31:0] rdata

);reg flag;

reg [1:0] cycle;

reg [31:0] dout;reg [31:0] imem[0:131071];

reg [31:0] dmem[0:65535];reg [7:0] queue[$];reg [31:0] clock;

reg speed;string str;integer idx;assign aready = cycle == 3'd0 ? 1'b1 : 1'b0;

assign rvalid = cycle == 3'd0 ? flag : 1'b0;

assign rdata = cycle == 3'd0 ? dout : 32'dx;always @(posedge clk)

beginif(avalid & aready & write) beginif(~addr[17]) beginif(strb[0]) imem[addr[16:0]][0 +:8] <= wdata[0 +:8];if(strb[1]) imem[addr[16:0]][8 +:8] <= wdata[8 +:8];if(strb[2]) imem[addr[16:0]][16+:8] <= wdata[16+:8];if(strb[3]) imem[addr[16:0]][24+:8] <= wdata[24+:8];end else if(~addr[16]) beginif(strb[0]) dmem[addr[15:0]][0 +:8] <= wdata[0 +:8];if(strb[1]) dmem[addr[15:0]][8 +:8] <= wdata[8 +:8];if(strb[2]) dmem[addr[15:0]][16+:8] <= wdata[16+:8];if(strb[3]) dmem[addr[15:0]][24+:8] <= wdata[24+:8];endend

endalways @(posedge clk or negedge rstn)

beginif(!rstn)flag <= 1'b0;else if(avalid & aready & ~write)flag <= 1'b1;else if(rready & rvalid)flag <= 1'b0;

endalways @(posedge clk or negedge rstn)

beginif(!rstn)cycle <= 2'd0;else if(|cycle)cycle <= cycle - 2'd1;else if(avalid) beginidx = $urandom_range(0, 99);if(idx <= 80 || speed == 1'b1)cycle <= 2'd0;else if(idx <= 95)cycle <= 2'd1;else if(idx <= 97)cycle <= 2'd2;elsecycle <= 2'd3;end

endalways @(posedge clk or negedge rstn)

beginif(!rstn)dout <= 32'dx;else if(avalid & aready & ~write)if(~addr[17])dout <= imem[addr[16:0]];else if(~addr[16])dout <= dmem[addr[15:0]];else if(addr[15:0] == 16'h0002)dout <= clock;else if(addr[15:0] == 16'h0003)dout <= {31'd0, speed};else if(rready & rvalid)dout <= 32'dx;

endalways @(posedge clk)

beginif(avalid & aready & write & strb[0] & addr == 18'h30000) beginif(wdata[7:0] == 8'h0a) beginstr = "";while(queue.size() > 0) beginstr = $sformatf("%s%c", str, queue.pop_front());end$display("[MCU_INFO] : %s", str);end else beginqueue.push_back(wdata[7:0]);endend

endalways @(posedge clk)

beginif(avalid & aready & write & (&strb) & addr == 18'h30001) beginif(wdata == 32'h12345678) begin$finish();endend

endalways @(posedge clk or negedge rstn)

beginif(!rstn)clock <= 32'd0;elseclock <= clock + 1'b1;

endalways @(posedge clk or negedge rstn)

beginif(!rstn)speed <= 1'b0;else if(avalid & aready & write & strb[0] & addr == 18'h30003)speed <= wdata[0];

endendmodule

6.运行脚本

脚本支持两套仿真工具,一套为开源的iverilog+gtkwave的组合,另一套为vcs+verdi。

# -------------------------------------------------------------------------------------------------

# Copyright 2024 Kearn Chen, kearn.chen@aliyun.com

#

# Licensed under the Apache License, Version 2.0 (the "License");

# you may not use this file except in compliance with the License.

# You may obtain a copy of the License at

#

# http://www.apache.org/licenses/LICENSE-2.0

#

# Unless required by applicable law or agreed to in writing, software

# distributed under the License is distributed on an "AS IS" BASIS,

# WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

# See the License for the specific language governing permissions and

# limitations under the License.

# -------------------------------------------------------------------------------------------------

# Description :

# 1. Run simulation

# -------------------------------------------------------------------------------------------------TEST := hello_world_testvcs:cp ../case/$(TEST).v testcase.vmake -C ../test/$(TEST)vcs -full64 -sverilog +vcs+fsdbon -f ../list/filelist.vc./simv +ntb_random_seed_automatic -l simv.logiverilog:cp ../case/$(TEST).v testcase.vmake -C ../test/$(TEST)iverilog -o simv -f ../list/filelist.vc -g2012 -DDUMP_LXT2vvp simv -lxt2 -fstverdi:verdi -sverilog -f ../list/filelist.vc >kwave:gtkwave &clean:rm -rf simv *.log csrc simv.daidir verdiLog ucli.key novas* *.v

7.总结

本文介绍了一个简单的验证环境,包括测试顶层及模型、脚本等代码,在后续的文章中会基于此验证环境给出具体的验证用例。

相关文章:

【RISC-V设计-12】- RISC-V处理器设计K0A之验证环境

【RISC-V设计-12】- RISC-V处理器设计K0A之验证环境 文章目录 【RISC-V设计-12】- RISC-V处理器设计K0A之验证环境1.简介2.验证顶层3.顶层代码4.模型结构4.1 地址映射4.2 特殊功能寄存器 5.模型代码6.运行脚本7.总结 1.简介 在前几篇文章中,分别介绍了各个模块的设…...

react-redux的使用

关于react-redux 首先:react-redux和redux并不是一个东西,redux是一个独立的东西,react-redux是react官方根据市场偏好redux推出的react插件库。 了解react-redux的原理图: 安装:npm i react-redux redux的ui组件和…...

大模型在chat bi 场景下的优化思路

文章目录 背景提示词模版表结构注释示例数据给出示例答案语法验证外挂知识库 背景 大模型的出现使chat bi 成为一种可能,自然语句的交互,极大的提高了数据分析的效率,也极大的降低了用户使用的门槛。下面主要列出几点提高自然语句转成SQL的技…...

Qt登录窗口

#include "widget.h" #include "ui_widget.h"Widget::Widget(QWidget *parent): QWidget(parent), ui(new Ui::Widget),btn(new QPushButton("取消", this)),login_btn(new QPushButton("登录", this)) { ui->setupUi(this);thi…...

Zookeeper的在Ubuntu20.04上的集群部署

安装资源 官方安装包下载地址:https://zookeeper.apache.org/releases.html 懒得找版本的可以移步下载zookeeper3.84稳定版本: https://download.csdn.net/download/qq_43439214/89646735 安装方法 创建安装路径&&解压安装包 # 创建路径 m…...

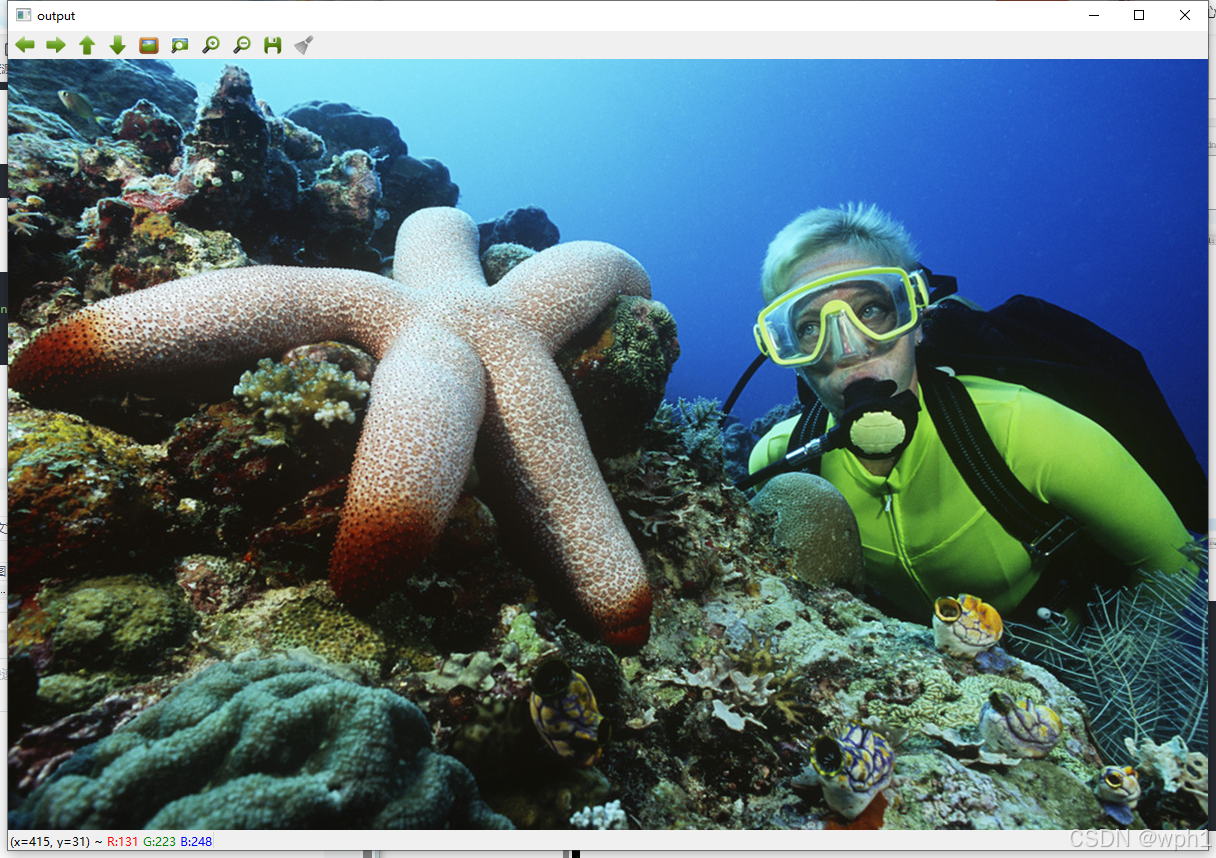

Qt+OpenCV配置和测试

一、前言 OpenCV作为比较大众化的跨平台计算机视觉开源库,可以运行在多种操作系统上,通过与Qt的结合,能够轻松的是实现一些图像处理和识别的任务,本文在Windows操作系统的基础上具体讲解Qt和OpenCV的配置和环境搭建方法ÿ…...

Ruby GUI宝典:探索顶级图形界面库

标题:Ruby GUI宝典:探索顶级图形界面库 Ruby,这门以优雅和简洁著称的语言,不仅在服务器端编程中大放异彩,其在图形用户界面(GUI)开发上同样拥有不可忽视的地位。本文将带领大家深入了解Ruby的G…...

探索Jinja2的神秘力量:Python模板引擎的魔法之旅

文章目录 探索Jinja2的神秘力量:Python模板引擎的魔法之旅1. 背景:为何选择Jinja2?2. 什么是Jinja2?3. 安装Jinja2:一键启程4. 基础用法:Jinja2的五大法宝5. 实战演练:Jinja2在场景中的应用6. 常…...

Vue3小兔仙电商项目实战

Vue3小兔仙电商项目实战 项目技术栈 create-vuePiniaElementPlusVue3-SetupVue-RouterVueUse 项目规模 项目亮点: 基于业务逻辑的组件拆分思想 长页面吸顶交互实现SKU电商组件封装图片懒加载指令封装通用逻辑函数封装面板插槽组件等业务通用组件封装路由缓存问题…...

)

MATLAB基础应用精讲-【数模应用】肯德尔协调系数(附MATLAB、R语言和python代码实现)

目录 前言 几个高频面试题目 肯德尔协调系数低原因? 知识储备 相关性分析对比 1 相关分析 2 Cochrans Q 检验 3 Kappa一致性检验 4 Kendall协调系数 5 组内相关系数 算法原理 数学模型 SPSSPRO:Kendall一致性检验 1、作用 2、输入输出描述 3、案例示例 4、案…...

计算函数(c语言)

1.描述 //小乐乐学会了自定义函数,BoBo老师给他出了个问题,根据以下公式计算m的值。 // //其中 max3函数为计算三个数的最大值,如: max3(1, 2, 3) 返回结果为3。 //输入描述: //一行,输入三个整数ÿ…...

Linux 7 x86平台上安装达梦8数据库

1、环境描述 2、安装前准备 2.1 操作系统信息调研 Linux平台需要通过命令查看操作系统版本、位数、磁盘空间、内存等信息。 CPU信息 [rootray1 ~]# cat /proc/cpuinfo | grep -E "physical id|core id|cpu cores|siblings|cpu MHz|model name|cache size"|tail -n…...

【老张的程序人生】我命由我不由天:我的计算机教师中级岗之旅

在计算机行业的洪流中,作为一名20年计算机专业毕业的博主,我深知这几年就业的坎坷与辉煌。今天,我想与大家分享我的故事,一段关于梦想、挑战与坚持的计算机教师中级岗之旅。希望我的经历能为大家提供一个发展方向,在计…...

1.Linux_常识

UNIX、Linux、GNU 1、UNIX UNIX是一个分时操作系统,特点是多用户、多任务 实时操作系统:来了请求就去解决请求 分时操作系统:来了请求先存着,通过调度轮到执行时执行 2、Linux Linux是一个操作系统内核 发行版本࿱…...

下载文件--后端返回文件数据,前端怎么下载呢

问题:有个功能是将tabel数据导出,并且后端写了个接口,这个接口返回你要下载的excel文件数据了。前端请求接口就行,然后下载下来,但前端该怎么操作(发起请求呢) /*** 导出文件* param {string} …...

CSS方向选择的艺术:深入探索:horizontal和:vertical伪类

CSS(层叠样式表)是构建网页视觉表现的核心工具。随着CSS规范的不断更新,我们拥有了更多的选择器来精确控制网页元素的样式。其中,:horizontal和:vertical伪类是CSS Level 4中引入的两个实验性选择器,它们允许开发者根据…...

探索PHP的心脏:流行CMS系统全解析

标题:探索PHP的心脏:流行CMS系统全解析 在数字化时代,内容管理系统(CMS)扮演着构建和维护网站的核心角色。PHP作为一种广泛使用的服务器端脚本语言,其强大的功能和灵活性使其成为开发CMS的首选。本文将详细…...

图片展示控件QGraphicsView、QGraphicsScene、QGraphicsItem的使用Demo

简介 /* * 图片展示控件 * Graphics View Framework的使用Demo * QGraphicsView、QGraphicsScene、QGraphicsItem的使用Demo * 支持图片的旋转与缩放,自动缩放至接触边框 */ 效果展示 坐标系示意图 Graphics View Framework的使用需要特别注意QGraphicsView、…...

C++仿C#实现事件处理

测试 #include "beacon/beacon.hpp" #include <cstdio> #include <thread>class mouseEvent : public beacon::args { public:mouseEvent(int x, int y) : x(x), y(y) {}int x, y; };class object : public beacon::sender { public:};class mouseHandl…...

SpringBoot-04--整合登录注册动态验证码

文章目录 效果展示1.导入maven坐标2.编写代码生成一个验证码图片3.前端如何拿到验证码4. 后端生成验证码5前端代码 效果展示 效果,每次进入页面展现出来不同的验证码。 技术 使用别人已经写好的验证码生成器,生成图片,转为Base64编码&#x…...

模块三-数据清洗与预处理——14. 重复值处理

14. 重复值处理 1. 概述 重复值是数据中的常见问题,可能来自数据录入错误、系统重复导出、数据合并等原因。重复数据会导致统计偏差、模型过拟合,需要在数据预处理阶段处理。 import pandas as pd import numpy as np# 创建包含重复值的示例数据 df pd.…...

---ESP32S3矩阵Matrix开发板之搭建开发环境)

【花雕学编程】Arduino动手做(252)---ESP32S3矩阵Matrix开发板之搭建开发环境

37款传感器与模块的提法,在网络上广泛流传,其实Arduino能够兼容的传感器模块肯定是不止37种的。鉴于本人手头积累了一些传感器和执行器模块,依照实践出真知(一定要动手做)的理念,以学习和交流为目的,这里准备逐一动手试试多做实验,不管成功与否,都会记录下来——小小的…...

openclaw-nerve:构建自包含应用包,彻底解决跨平台部署难题

1. 项目概述与核心价值最近在折腾一些自动化脚本和工具链,发现很多开源项目在依赖管理、环境配置和跨平台部署上,依然存在不小的摩擦。一个典型的场景是:你从GitHub上clone了一个看起来很酷的项目,满心欢喜地准备跑起来看看效果&a…...

2025届毕业生推荐的五大降AI率平台横评

Ai论文网站排名(开题报告、文献综述、降aigc率、降重综合对比) TOP1. 千笔AI TOP2. aipasspaper TOP3. 清北论文 TOP4. 豆包 TOP5. kimi TOP6. deepseek 当前,在生成式AI普及应用这个阶段,内容辨识度偏高这种情况࿰…...

1.8.2 掌握Scala类与对象 - 单例对象与伴生对象

本次实战通过三个案例深入解析了 Scala 中 object 的核心机制,展示了其如何替代 Java 的 static 关键字。首先,通过 MathUtils 定义了存放常量与工具方法的独立单例对象;其次,利用 Person 类与其同名对象演示了“伴生对象”特性&a…...

Python 爬虫进阶技巧:请求头 UA 随机伪装绕过基础检测

前言 当下绝大多数网站均部署了基础反爬检测机制,服务器会优先校验客户端请求身份标识,未携带合法浏览器标识、使用默认程序请求载体的爬虫请求,极易被直接拦截、封禁 IP、返回空数据或跳转拦截页面。爬虫默认发起请求时会自带程序原生 UA 标识,服务器可通过该标识直接识别…...

终极IDM试用重置指南:三步实现无限续期的免费解决方案

终极IDM试用重置指南:三步实现无限续期的免费解决方案 【免费下载链接】idm-trial-reset Use IDM forever without cracking 项目地址: https://gitcode.com/gh_mirrors/id/idm-trial-reset IDM Trial Reset是一款专为Internet Download Manager用户设计的实…...

)

别再为Canvas跨域头疼了!手把手教你用UniApp H5搞定网络图片转Base64并生成海报(附完整代码)

UniApp H5开发实战:Canvas跨域图片处理与海报生成全攻略 在移动端H5开发中,Canvas绘制网络图片并生成分享海报是个常见需求,但跨域问题往往让开发者头疼不已。本文将带你深入理解Canvas的CORS限制本质,对比两种主流解决方案的技术…...

)

从学生到工程师:我如何用大学单片机课设代码搞定第一个嵌入式项目(STM8实战)

从学生到工程师:STM8实战中如何将课设代码升级为工业级解决方案 记得大三那年,我第一次在实验室里点亮STM8开发板的LED时,那种成就感至今难忘。但当我真正进入企业参与嵌入式项目开发时,才发现学校里的"标准答案"在真实…...

JD-GUI深度解析:Java字节码逆向工程的瑞士军刀

JD-GUI深度解析:Java字节码逆向工程的瑞士军刀 【免费下载链接】jd-gui A standalone Java Decompiler GUI 项目地址: https://gitcode.com/gh_mirrors/jd/jd-gui 在Java开发的世界里,我们常常需要面对只有字节码没有源码的困境——第三方库的调试…...