【FPGA】MIPS 12条整数指令【1】

目录

修改后的仿真结果

修改后的完整代码

实现bgtz、bltz、jalr

仿真结果(有问题)

bltz------并未跳转,jCe?

原因是该条跳转语句判断的寄存器r7,在该时刻并未被赋值

代码(InstMem修改前)

`include "define.v"

module InstMem(input wire ce,input wire [31:0] addr,output reg [31:0] data

);reg [31:0] instmem [1023 : 0]; always@(*) if(ce == `RomDisable)data = `Zero;elsedata = instmem[addr[11 : 2]]; initialbegininstmem [0] = 32'h34011100; //ori r1,r0,1100h r1--32'h0000 1100instmem [1] = 32'h34020020; //ori r2,r0,0020h r2--32'h0000 0020instmem [2] = 32'h3403ff00; //ori r3,r0,ff00h r3--32'h0000 ff00instmem [3] = 32'h3404ffff; //ori r4,r0,ffffh r4--32'h0000 ffff

/* instmem [4] = 32'h3005ffff; //andi r5,r0,ffff r5--32'h0000 0000instmem [5] = 32'h3806ffff; //xori r6,r0,ffff r6--32'h0000 ffffinstmem [6] = 32'h2007ffff; //addi r7,r0,ffff r7--32'hffff ffffinstmem [7] = 32'h3c081234; //lui r8,1234 r8--32'h1234 0000instmem [8] = 32'h35095679; //ori r9,r8,5678 r9--32'h1234 5679instmem [9] = 32'h212aa011; //addi r10,r9,a011 r10--32'h1233 f68ainstmem [10] = 32'h306b1111; //andi r11,r3,1111 r10--32'h0000 1100instmem [11] = 32'h254C1111; //subi r12,r10,1111 r12--32'h1234 e579

*/

/*instmem [4] = 32'h00222820; //add r5,r1,r2 r5--32'h0000 1120instmem [5] = 32'h00223025; //or r6,r1,r2 r6--32'h0000 1120instmem [6] = 32'h00223822; //sub r7,r1,r2 r7--32'h0000 10e0instmem [7] = 32'h00224024; //and r8,r1,r2 r8--32'h0000 0000instmem [8] = 32'h00224826; //xor r9,r1,r2 r9--32'h0000 1120instmem [9] =32'h3c0affff; //lui r10,ffff r10--32'hffff 0000instmem [10] = 32'h000a5840; //sll r11,ra,r10 r11--32'hfffe 0000instmem [11] = 32'h000a6042; //srl,r12,ra,r10 r12--32'h7fff 8000instmem [12] = 32'h000a6843; //sra r13,ra,r10 r13--32'hffff 8000*/ instmem [4] = 32'b000000_00001_00010_00101_00000_100000;//add,R5,R1,R2 00001120instmem [5] = 32'h3405ffff; //ori r5,r0,ffffh r4--32'h0000 ffff//instmem [5] = 32'b000000_00001_00010_00110_00000_100101;//or,R6,R1,R2 00001120instmem [6] = 32'b000000_00011_00100_00111_00000_101010;//slt r7,r3,r4instmem [7] = 32'b000111_00101_00000_0000000000000001;//bgtz r5,1instmem [8] = 32'b000000_00001_00010_00111_00000_101010;//slt r7,r1,r2instmem [9] = 32'h2007ffff; //addi r7,r0,ffff r7--32'hffff ffff//instmem [10] = 32'b000001_00111_00000_1111111111111101;//bltz r7,-3 instmem [10] = 32'b000001_00111_00000_1111111111111010;//bltz r7,-6instmem [11] = 32'h34010000; //ori r1,r0,00hinstmem [12] = 32'b000000_00001_00000_01000_00000_001001;//jalr r8,r1//(r1)=0000 1100// +0000 0018//addr=0000 1118 // =1000100011000 // =100 0100 0110 // =446H // =46H // =70//mem[70]=(r6)/*instmem[6]=32'b101011_00001_00110_0000_0000_0001_1000; //sw r6,0x18(r1)instmem[7]=32'b100011_00001_00111_0000_0000_0001_1000; //lw r7,0x18(r1)*///(r7)=mem[70]end

endmodule修改后的仿真结果

bgtz、bltz

PC

ori r1,r0,1100h 00h

ori r2,r0,0020h 04h

ori r3,r0,ff00h 08h

ori r4,r0,ffffh 0ch

add r5,r1,r2 10h

ori r5,r0,ffffh 14h

or r6,r2,r3 18h

bgtz r5,1 1ch

or r6,r1,r2 20h

addi r7,r0,ffffh 24h

or r6,r3,r4 28h

bltz r7,-6 2ch

PC 1ch->24h 2ch->18h

jalr

PC

ori r1,r0,1100h 00h

ori r2,r0,0020h 04h

ori r3,r0,ff00h 08h

ori r4,r0,ffffh 0ch

ori r1,r0,1ch 10h

jalr r31,r1 14h

ori r5,r0,ffffh 18h

add r5,r1,r2 1ch

jr r31 20h

14h-->1ch

20h-->18h

修改后的完整代码

`define RstEnable 1'b1

`define RstDisable 1'b0

`define RomEnable 1'b1

`define RomDisable 1'b0

`define Zero 0

`define Valid 1'b1

`define Invalid 1'b0

//I

`define Inst_ori 6'b001101

`define Inst_addi 6'b001000

`define Inst_andi 6'b001100

`define Inst_xori 6'b001110

`define Inst_lui 6'b001111

`define Inst_subi 6'b001001//lw sw

`define Inst_lw 6'b100011

`define Inst_sw 6'b101011//beq bne

`define Inst_beq 6'b000100

`define Inst_bne 6'b000101//R

`define Inst_r 6'b000000

`define Inst_add 6'b100000

`define Inst_sub 6'b100010

`define Inst_and 6'b100100

`define Inst_or 6'b100101

`define Inst_xor 6'b100110

`define Inst_sll 6'b000000

`define Inst_srl 6'b000010

`define Inst_sra 6'b000011`define Inst_jr 6'b001000

//J

`define Inst_j 6'b000010

`define Inst_jal 6'b000011//12条整数指令

`define Inst_slt 6'b101010

`define Inst_bgtz 6'b000111

`define Inst_bltz 6'b000001

`define Inst_jalr 6'b001001

`define Inst_mult 6'b011000

`define Inst_multu 6'b011001

`define Inst_div 6'b011010

`define Inst_divu 6'b011011

`define Inst_mfhi 6'b010000

`define Inst_mflo 6'b010010

`define Inst_mthi 6'b010001

`define Inst_mtlo 6'b010011//中断

`define Inst_ll 6'b110000

`define Inst_sc 6'b111000

`define Inst_mfc0 6'b000000

`define Inst_mtc0 6'b000000

`define Inst_eret 6'b011000

`define syscall 6'b001100`define Nop 6'b000000

`define Or 6'b000001

`define Add 6'b000010

`define And 6'b000011

`define Xor 6'b000100

`define Lui 6'b000101

`define Sub 6'b000110

`define Sll 6'b000111

`define Srl 6'b001000

`define Sra 6'b001001

`define J 6'b001010

`define Jal 6'b001011

`define Beq 6'b001100

`define Bne 6'b001101

`define Jr 6'b001110

`define Lw 6'b010000

`define Sw 6'b010001

`define Bgtz 6'b010010

`define Bltz 6'b010011//MEM

`define RamWrite 1'b1

`define RamUnWrite 1'b0

`define RamEnable 1'b1

`define RamDisable 1'b0`include "define.v"

module EX(input wire rst,//input wire [5:0] op,input wire [5:0] op_i, input wire [31:0] regaData,input wire [31:0] regbData,input wire regcWrite_i,input wire [4:0]regcAddr_i,output reg [31:0] regcData,output wire regcWrite,output wire [4:0] regcAddr,output wire [5:0] op,output wire [31:0] memAddr,output wire [31:0] memData

); assign op = op_i;assign memAddr = regaData;assign memData = regbData;always@(*)if(rst == `RstEnable)regcData = `Zero;elsebegin//case(op)case(op_i)`Or:regcData = regaData | regbData;`Add:regcData = regaData + regbData;`And:regcData = regaData & regbData;`Xor:regcData = regaData ^ regbData;`Lui:regcData = regaData;/*`Lui:regcData = regaData | regbData;*/`Sub:regcData = regaData - regbData;`Sll:regcData = regbData << regaData;`Srl:regcData = regbData >> regaData;`Sra:regcData = ($signed(regbData)) >>> regaData;`J:regcData = `Zero;`Jr:regcData = `Zero;`Jal:regcData = regbData;`Beq:regcData = `Zero;`Bne:regcData = `Zero;`Bltz:regcData = `Zero;`Bgtz:regcData = `Zero;default:regcData = `Zero;endcaseendassign regcWrite = regcWrite_i;assign regcAddr = regcAddr_i;

endmodule

`include "define.v";

module ID (input wire rst, input wire [31:0] pc, //Jinput wire [31:0] inst,input wire [31:0] regaData_i,input wire [31:0] regbData_i,output reg [5:0] op, output reg [31:0] regaData,output reg [31:0] regbData,output reg regaRead,output reg regbRead,output reg regcWrite,output reg [4:0] regaAddr,output reg [4:0] regbAddr, output reg [4:0] regcAddr,output reg [31:0] jAddr, //Joutput reg jCe//J);wire [5:0] inst_op = inst[31:26]; reg [31:0] imm;//Rwire[5:0] func = inst[5:0]; //Jwire [31:0] npc = pc + 4;always@(*)if(rst == `RstEnable)beginop = `Nop; regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;imm = `Zero;jCe = `Invalid;//JjAddr = `Zero;//Jendelse beginjCe = `Invalid;//JjAddr = `Zero;//Jcase(inst_op)`Inst_ori:beginop = `Or; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {16'h0, inst[15:0]};end`Inst_andi:beginop = `And; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {16'h0, inst[15:0]};end`Inst_xori:beginop = `Xor; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {16'h0, inst[15:0]};end`Inst_addi:beginop = `Add; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {{16{inst[15]}}, inst[15:0]};end`Inst_subi:beginop = `Sub; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {{16{inst[15]}}, inst[15:0]};end`Inst_lui:beginop = `Lui; regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = inst[20:16];imm = {inst[15:0],16'h0};end`Inst_r:case(func)`Inst_add:beginop = `Add; regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_or:beginop = `Or;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_sub:beginop = `Sub;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_and:beginop = `And;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_xor:beginop = `Xor;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_sll:beginop = `Sll;regaRead = `Invalid;regbRead = `Valid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = inst[20:16];regcAddr = inst[15:11];imm = {27'b0,inst[10:6]};end`Inst_srl:beginop = `Srl;regaRead = `Invalid;regbRead = `Valid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = inst[20:16];regcAddr = inst[15:11];imm = {27'b0,inst[10:6]};end`Inst_sra:beginop = `Sra;regaRead = `Invalid;regbRead = `Valid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = inst[20:16];regcAddr = inst[15:11];imm = {27'b0,inst[10:6]};end`Inst_jr:beginop = `Jr;regaRead = `Valid;//rsregbRead = `Invalid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = 5'b11111;jAddr = regaData;jCe = `Valid;imm = `Zero;end`Inst_jalr:beginop = `Jal;regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[15:11]; //jAddr = regaData;jCe = `Valid;imm = npc;enddefault:beginregaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;imm = `Zero;endendcase//J`Inst_j:beginop = `J;regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;jAddr = {npc[31:28], inst[25:0], 2'b00};jCe = `Valid;imm = `Zero;end `Inst_jal:beginop = `Jal;regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = 5'b11111;jAddr = {npc[31:28], inst[25:0], 2'b00};jCe = `Valid;imm = npc;end//J `Inst_beq:beginop = `Beq;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;jAddr = npc+{{14{inst[15]}},inst[15:0],2'b00};jCe=(regaData==regbData)?`Valid:`Invalid; /* if(regaData==regbData)jCe = `Valid;elsejCe = `Invalid;*/imm = `Zero;end `Inst_bne:beginop = `Bne;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;jAddr = npc+{{14{inst[15]}},inst[15:0],2'b00};jCe=(regaData!=regbData)?`Valid:`Invalid; /* if(regaData!=regbData)jCe = `Valid;elsejCe = `Invalid;*/imm = `Zero;end `Inst_bgtz:beginop = `Bgtz;regaRead = `Valid;regbRead = `Valid;//regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;jAddr = npc+{{14{inst[15]}},inst[15:0],2'b00};jCe = (regaData[31]==0)?`Valid:`Invalid;imm = 32'b0; //end`Inst_bltz:beginop = `Bgtz;regaRead = `Valid;regbRead = `Valid;//regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;jAddr = npc+{{14{inst[15]}},inst[15:0],2'b00};jCe = (regaData[31]==1)?`Valid:`Invalid; //imm = 32'b0; //end`Inst_lw:beginop = `Lw;regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {{16{inst[15]}},inst[15:0]};end`Inst_sw:beginop = `Sw;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;imm = {{16{inst[15]}},inst[15:0]};end default:beginop = `Nop; regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;imm = `Zero;endendcase end/*always@(*)if(rst == `RstEnable)regaData = `Zero;else if(regaRead == `Valid)regaData = regaData_i;else regaData = imm;always@(*)if(rst == `RstEnable)regbData = `Zero; else if(regbRead == `Valid)regbData = regbData_i;elseregbData = imm; */

always@(*) if(rst == `RstEnable) regaData = `Zero; else if(op == `Lw || op == `Sw) regaData = regaData_i + imm; else if(regaRead == `Valid) regaData = regaData_i; else regaData = imm; always@(*) if(rst == `RstEnable) regbData = `Zero; else if(regbRead == `Valid) regbData = regbData_i; else regbData = imm;endmodule`include "define.v"

module IF(input wire clk,input wire rst,input wire [31:0] jAddr,//Jinput wire jCe,//Joutput reg ce,

output reg [31:0] pc

);always@(*)if(rst == `RstEnable)ce = `RomDisable;elsece = `RomEnable;

/* always@(posedge clk)if(ce == `RomDisable)pc = `Zero;elsepc = pc + 4;

*/always@(posedge clk)if(ce == `RomDisable)pc = `Zero;else if(jCe == `Valid)//Jpc = jAddr;elsepc = pc + 4;

endmodule`include "define.v"

module RegFile(input wire clk,input wire rst,input wire we,input wire [4:0] waddr,input wire [31:0] wdata,input wire regaRead,input wire regbRead,input wire [4:0] regaAddr,input wire [4:0] regbAddr,output reg [31:0] regaData,output reg [31:0] regbData

);reg [31:0] reg32 [31 : 0]; always@(*)if(rst == `RstEnable)regaData = `Zero;else if(regaAddr == `Zero)regaData = `Zero;elseregaData = reg32[regaAddr];always@(*)if(rst == `RstEnable) regbData = `Zero;else if(regbAddr == `Zero)regbData = `Zero;elseregbData = reg32[regbAddr];always@(posedge clk)if(rst != `RstEnable)if((we == `Valid) && (waddr != `Zero))reg32[waddr] = wdata;else ;

endmodule`include "define.v";

module DataMem(input wire clk,input wire ce,input wire we,input wire [31:0] addr,input wire [31:0] wtData,output reg [31:0] rdData

);reg [31:0] datamem [1023 : 0];always@(*) if(ce == `RamDisable)rdData = `Zero;elserdData = datamem[addr[11 : 2]]; always@(posedge clk)if(ce == `RamEnable && we == `RamWrite)datamem[addr[11 : 2]] = wtData;else ;endmodule

`include "define.v";

module MEM(input wire rst, input wire [5:0] op,input wire [31:0] regcData,input wire [4:0] regcAddr,input wire regcWr,input wire [31:0] memAddr_i,input wire [31:0] memData, input wire [31:0] rdData,output wire [4:0] regAddr,output wire regWr,output wire [31:0] regData, output wire [31:0] memAddr,output reg [31:0] wtData,output reg memWr, output reg memCe

);assign regAddr = regcAddr; assign regWr = regcWr; assign regData = (op == `Lw) ? rdData : regcData; assign memAddr = memAddr_i;always @(*) if(rst == `RstEnable) begin wtData = `Zero; memWr = `RamUnWrite; memCe = `RamDisable; end elsecase(op) `Lw: begin wtData = `Zero; memWr = `RamUnWrite; memCe = `RamEnable; end `Sw: begin wtData = memData; memWr = `RamWrite; memCe = `RamEnable; enddefault: begin wtData = `Zero; memWr = `RamUnWrite; memCe = `RamDisable; end endcase

endmodule`include "define.v"

module InstMem(input wire ce,input wire [31:0] addr,output reg [31:0] data

);reg [31:0] instmem [1023 : 0]; always@(*) if(ce == `RomDisable)data = `Zero;elsedata = instmem[addr[11 : 2]]; initialbegininstmem [0] = 32'h34011100; //ori r1,r0,1100h r1--32'h0000 1100instmem [1] = 32'h34020020; //ori r2,r0,0020h r2--32'h0000 0020instmem [2] = 32'h3403ff00; //ori r3,r0,ff00h r3--32'h0000 ff00instmem [3] = 32'h3404ffff; //ori r4,r0,ffffh r4--32'h0000 ffff

/* instmem [4] = 32'h3005ffff; //andi r5,r0,ffff r5--32'h0000 0000instmem [5] = 32'h3806ffff; //xori r6,r0,ffff r6--32'h0000 ffffinstmem [6] = 32'h2007ffff; //addi r7,r0,ffff r7--32'hffff ffffinstmem [7] = 32'h3c081234; //lui r8,1234 r8--32'h1234 0000instmem [8] = 32'h35095679; //ori r9,r8,5678 r9--32'h1234 5679instmem [9] = 32'h212aa011; //addi r10,r9,a011 r10--32'h1233 f68ainstmem [10] = 32'h306b1111; //andi r11,r3,1111 r10--32'h0000 1100instmem [11] = 32'h254C1111; //subi r12,r10,1111 r12--32'h1234 e579

*/

/*instmem [4] = 32'h00222820; //add r5,r1,r2 r5--32'h0000 1120instmem [5] = 32'h00223025; //or r6,r1,r2 r6--32'h0000 1120instmem [6] = 32'h00223822; //sub r7,r1,r2 r7--32'h0000 10e0instmem [7] = 32'h00224024; //and r8,r1,r2 r8--32'h0000 0000instmem [8] = 32'h00224826; //xor r9,r1,r2 r9--32'h0000 1120instmem [9] =32'h3c0affff; //lui r10,ffff r10--32'hffff 0000instmem [10] = 32'h000a5840; //sll r11,ra,r10 r11--32'hfffe 0000instmem [11] = 32'h000a6042; //srl,r12,ra,r10 r12--32'h7fff 8000instmem [12] = 32'h000a6843; //sra r13,ra,r10 r13--32'hffff 8000*/ //instmem [4] = 32'h34010000; //ori r1,r0,00h//instmem [5] = 32'b000000_00001_00000_01000_00000_001001;//jalr r8,r1instmem [4] = 32'b000000_00001_00010_00101_00000_100000;//add,R5,R1,R2 instmem [5] = 32'h3405ffff; //ori r5,r0,ffffh instmem [6] = 32'b000000_00010_00011_00110_00000_100101;//or,R6,R2,R3 instmem [7] = 32'b000111_00101_00000_0000000000000001;//bgtz r5,1instmem [8] = 32'b000000_00001_00010_00110_00000_100101;//or,R6,R1,R2 00001120instmem [9] = 32'h2007ffff; //addi r7,r0,ffff r7--32'hffff ffffinstmem [10] = 32'b000000_00011_00100_00110_00000_100101;//or,R6,R3,R4 //instmem [10] = 32'b000001_00111_00000_1111111111111101;//bltz r7,-3 instmem [11] = 32'b000001_00111_00000_1111111111111010;//bltz r7,-6/*instmem [6] = 32'b000000_00011_00100_00111_00000_101010;//slt r7,r3,r4instmem [8] = 32'b000000_00001_00010_00111_00000_101010;//slt r7,r1,r2*///(r1)=0000 1100// +0000 0018//addr=0000 1118 // =1000100011000 // =100 0100 0110 // =446H // =46H // =70//mem[70]=(r6)/*instmem[6]=32'b101011_00001_00110_0000_0000_0001_1000; //sw r6,0x18(r1)instmem[7]=32'b100011_00001_00111_0000_0000_0001_1000; //lw r7,0x18(r1)*///(r7)=mem[70]end

endmodule`include "define.v";

module MIPS(input wire clk,input wire rst,input wire [31:0] instruction,input wire [31:0] rdData,//lsoutput wire romCe,output wire [31:0] instAddr,output wire [31:0] wtData,//lsoutput wire [31:0] memAddr,//lsoutput wire memCe,//lsoutput wire memWr//ls

);wire [31:0] regaData_regFile, regbData_regFile;wire [31:0] regaData_id, regbData_id; wire [31:0] regcData_ex;//wire [5:0] op; wire [5:0] op_id; //ls wire regaRead, regbRead;wire [4:0] regaAddr, regbAddr;wire regcWrite_id, regcWrite_ex;wire [4:0] regcAddr_id, regcAddr_ex;//Jwire [31:0] jAddr;wire jCe;//lswire [5:0] op_ex;wire[31:0] memAddr_ex,memData_ex;wire [5:0] regAddr_mem;wire [31:0] regData_mem;wire regWr_mem;IF if0(.clk(clk),.rst(rst),.jAddr(jAddr),//J.jCe(jCe),//J.ce(romCe), .pc(instAddr));ID id0(.rst(rst), .pc(instAddr),//J.inst(instruction),.regaData_i(regaData_regFile),.regbData_i(regbData_regFile),//.op(op),.op(op_id),//ls.regaData(regaData_id),.regbData(regbData_id),.regaRead(regaRead),.regbRead(regbRead),.regaAddr(regaAddr),.regbAddr(regbAddr),.regcWrite(regcWrite_id),.regcAddr(regcAddr_id),.jAddr(jAddr),//J.jCe(jCe)//J);EX ex0(.rst(rst),//.op(op), .op_i(op_id), .regaData(regaData_id),.regbData(regbData_id),.regcWrite_i(regcWrite_id),.regcAddr_i(regcAddr_id),.regcData(regcData_ex),.regcWrite(regcWrite_ex),.regcAddr(regcAddr_ex),.op(op_ex),//ls.memAddr(memAddr_ex),//ls.memData(memData_ex)//ls); MEM mem0(.rst(rst), .op(op_ex),.regcData(regcData_ex),.regcAddr(regcAddr_ex),.regcWr(regcWrite_ex),.memAddr_i(memAddr_ex),.memData(memData_ex), .rdData(rdData),.regAddr(regAddr_mem),.regWr(regWr_mem),.regData(regData_mem), .memAddr(memAddr),.wtData(wtData),.memWr(memWr), .memCe(memCe));RegFile regfile0(.clk(clk),.rst(rst),//.we(regcWrite_ex),.we(regWr_mem),//.waddr(regcAddr_ex),.waddr(regAddr_mem),//.wdata(regcData_ex),.wdata(regData_mem),.regaRead(regaRead),.regbRead(regbRead),.regaAddr(regaAddr),.regbAddr(regbAddr),.regaData(regaData_regFile),.regbData(regbData_regFile));endmodule

module SoC(input wire clk,input wire rst

);wire [31:0] instAddr;wire [31:0] instruction;wire romCe;//lswire memCe, memWr; wire [31:0] memAddr;wire [31:0] rdData;wire [31:0] wtData;MIPS mips0(.clk(clk),.rst(rst),.instruction(instruction),.instAddr(instAddr),.romCe(romCe),.rdData(rdData), .wtData(wtData), .memAddr(memAddr), .memCe(memCe), .memWr(memWr) ); InstMem instrom0(.ce(romCe),.addr(instAddr),.data(instruction));//DataMemDataMem datamem0( .ce(memCe), .clk(clk), .we(memWr), .addr(memAddr), .wtData(wtData), .rdData(rdData) );

endmodule

`include "define.v"

module soc_tb;reg clk;reg rst;initialbeginclk = 0;rst = `RstEnable;#100rst = `RstDisable;#10000 $stop; endalways #10 clk = ~ clk;SoC soc0(.clk(clk), .rst(rst));

endmodule

相关文章:

【FPGA】MIPS 12条整数指令【1】

目录 修改后的仿真结果 修改后的完整代码 实现bgtz、bltz、jalr 仿真结果(有问题) bltz------并未跳转,jCe? 原因是该条跳转语句判断的寄存器r7,在该时刻并未被赋值 代码(InstMem修改前) i…...

Halcon 3D基础知识及常用函数

一、基本概念 1、点云(Point Cloud) 点云是一组3D数据点,每个点由笛卡尔坐标系或其他坐标系中的一个三维坐标表示,它被认为是一组非结构化的三维点,象征着三维物体的几何形状。点云是一种简单、完整的数据结构&#…...

贵金属铟,钌,铱,钯铂铑回收工艺详解

Tulsimer CH-95S 是一款为了从工业废水中去除回收汞和贵金属而专门开发的螯合树脂。 Tulsimer CH-95S 是一款拥有聚乙烯异硫脲官能基的大孔树脂,这种树脂对汞有极高的选择性。它也选 择其他的贵金属,如黄金,铂金和其他铂金族金属。…...

AutoSAR CP RTE 规范核心内容简介以及BswScheduler工作原理解析

一、Autosar CP RTE规范核心内容简介 本规范详细介绍了AUTOSAR运行时环境(RTE)和基本软件调度器(BswScheduler)的软件规范。 研究背景 背景介绍: 这篇文章的研究背景是AUTOSAR(Automotive Open System Architecture…...

Python Pyside6 加Sqlite3 写一个 通用 进销存 系统 初型

图: 说明: 进销存管理系统说明文档 功能模块 1. 首页 显示关键业务数据商品总数供应商总数本月采购金额本月销售金额显示预警信息库存不足预警待付款采购单待收款销售单2. 商品管理 商品信息维护商品编码(唯一标识)商品名称规格型号单位分类进货价销售价库存数量预警…...

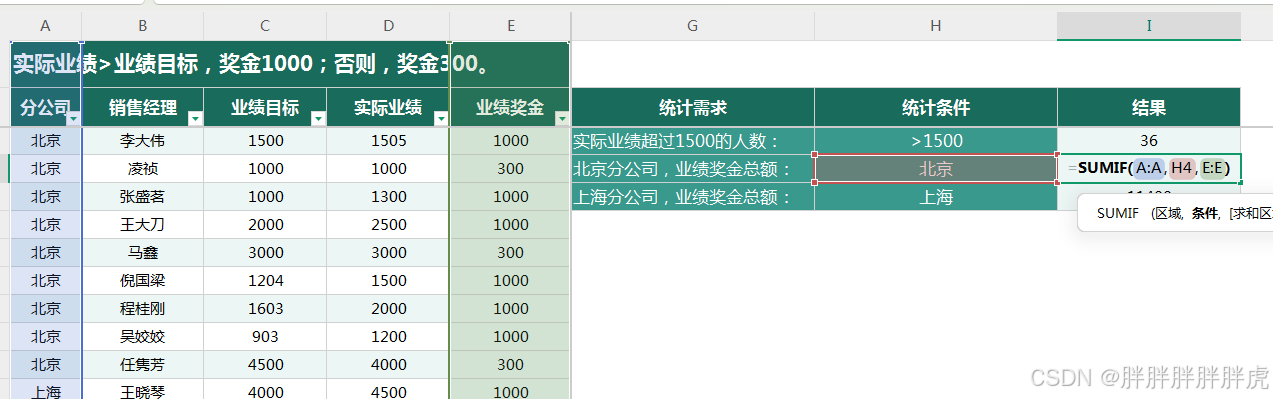

office 学习

Excel 视图 切片 通过视图进行数据分析 条形格式 函数 countif sumif sumifs 多条件 countifs 多条件...

【三维分割】Gaga:通过3D感知的 Memory Bank 分组任意高斯

文章目录 摘要一、引言二、主要方法2.1 3D-aware Memory Bank2.2 三维分割的渲染与下游应用 三、实验消融实验应用: Scene Manipulation 地址:https://www.gaga.gallery 标题:Gaga: Group Any Gaussians via 3D-aware Memory Bank 来源:加利福…...

期权懂|明日股指期货交割日该如何操作?

锦鲤三三每日分享期权知识,帮助期权新手及时有效地掌握即市趋势与新资讯! 明日股指期货交割日该如何操作? 一、需要确认股指期货交割日: 查查看明日是否为交割日,别忘了关注交易所公告,以免错过。 二、需要…...

大牙的2024年创作总结

文章目录 一、自动驾驶通讯协议的学习心得二、PyTorch框架应用的心得体会三、大规模语言模型(LLM)的研究心得四、神经网络架构与实战经验五、我的年度文章六、未来展望与个人成长 引言 2024年是我个人在深度学习和自动驾驶领域不断探索、实践并取得显著…...

AI软件栈:中间表示

概念 编译器通常可以分为前端、优化器和后端三个部分中间表示属于变异过程中表达源程序的方法,作为单独的表示语言。将不同的前端语言(例如C、python、Java等)描述转换为中间表示。优化器对中间表示进行转换和优化,输出新的中间表示。后端将优化后的中间表示转换为特定硬件…...

【PowerQuery专栏】PowerQuery的M语言函数Access数据库访问

Access是相对比较小型的文件型数据库,PowerQuery 进行Access数据库解析非常简单,直接使用Access.Database的函数可以实现数据库访问,函数包含如下参数,函数结果为Table表类型。 Access.Database(参数1 as binary,参数2 as record) as Table 参数1为数据库,数据类型为二进…...

C# OpenCvSharp 部署文档矫正,包括文档扭曲/模糊/阴影等情况

目录 说明 效果 模型 项目 代码 下载 参考 C# OpenCvSharp 部署文档矫正,包括文档扭曲/模糊/阴影等情况 说明 地址:https://github.com/RapidAI/RapidUnDistort 修正文档扭曲/模糊/阴影等情况,使用onnx模型简单轻量部署,…...

go读取excel游戏配置

1.背景 游戏服务器,配置数据一般采用csv/excel来作为载体,这种方式,策划同学配置方便,服务器解析也方便。在jforgame框架里,我们使用以下的excel配置格式。 然后可以非常方便的进行数据检索,例如ÿ…...

特殊类设计

[本节目标] 掌握常见特殊类的设计方式 1.请设计一个类,不能被拷贝 拷贝只会放生在两个场景中:拷贝构造函数以及赋值运算符重载,因此想要让一个类禁止拷贝,只需让该类不能调用拷贝构造函数以及赋值运算符重载即可。 C98 将拷贝构…...

图像去雾数据集的下载和预处理操作

前言 目前,因为要做对比实验,收集了一下去雾数据集,并且建立了一个数据集的预处理工程。 这是以前我写的一个小仓库,我决定还是把它用起来,下面将展示下载的路径和数据处理的方法。 下面的代码均可以在此找到。Auo…...

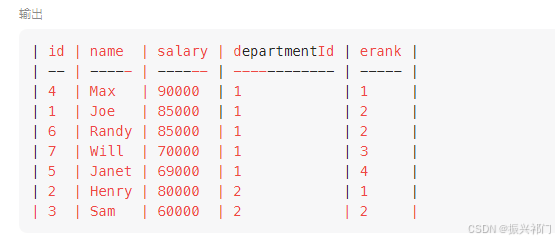

【LeetCode】--- MySQL刷题集合

1.组合两个表(外连接) select p.firstName,p.lastName,a.city,a.state from Person p left join Address a on p.personId a.personId; 以左边表为基准,去连接右边的表。取两表的交集和左表的全集 2.第二高的薪水 (子查询、if…...

基于Python的多元医疗知识图谱构建与应用研究(上)

一、引言 1.1 研究背景与意义 在当今数智化时代,医疗数据呈爆发式增长,如何高效管理和利用这些数据,成为提升医疗服务质量的关键。传统医疗数据管理方式存在数据孤岛、信息整合困难等问题,难以满足现代医疗对精准诊断和个性化治疗的需求。知识图谱作为一种知识表示和管理…...

小哆啦解题记:如何计算除自身以外数组的乘积

小哆啦开始力扣每日一题的第十二天 https://leetcode.cn/problems/product-of-array-except-self/description/ 《小哆啦解题记:如何计算除自身以外数组的乘积》 在一个清晨的阳光下,小哆啦坐在书桌前,思索着一道困扰已久的题目:…...

渐进式图片的实现原理

渐进式图片(Progressive JPEG)的实现原理与传统的基线 JPEG(Baseline JPEG)不同。它通过改变图片的编码和加载方式,使得图片在加载时能够逐步显示从模糊到清晰的图像。 1. 传统基线 JPEG 的加载方式 在传统的基线 JP…...

)

SQL刷题快速入门(三)

其他章节: SQL刷题快速入门(一) SQL刷题快速入门(二) 承接前两个章节,本系列第三章节主要讲SQL中where和having的作用和区别、 GROUP BY和ORDER BY作用和区别、表与表之间的连接操作(重点&…...

经典软件复活:DDrawCompat兼容性解决方案详解

经典软件复活:DDrawCompat兼容性解决方案详解 【免费下载链接】DDrawCompat DirectDraw and Direct3D 1-7 compatibility, performance and visual enhancements for Windows Vista, 7, 8, 10 and 11 项目地址: https://gitcode.com/gh_mirrors/dd/DDrawCompat …...

)

避坑指南:处理通达信5分钟数据.lc5文件时你可能遇到的5个问题(Python解决方案)

避坑指南:处理通达信5分钟数据.lc5文件时你可能遇到的5个问题(Python解决方案) 在金融数据分析领域,通达信的.lc5文件是存储5分钟级别行情数据的重要格式。许多量化交易者和数据分析师在处理这类文件时,往往会遇到一些…...

如何快速配置AI文献助手:5步完成智能学术管理

如何快速配置AI文献助手:5步完成智能学术管理 【免费下载链接】zotero-gpt GPT Meet Zotero. 项目地址: https://gitcode.com/gh_mirrors/zo/zotero-gpt 在当今数字化学术研究环境中,Zotero-GPT插件通过深度集成OpenAI的GPT模型,为学术…...

)

不止于测距:用蓝桥杯开发板DIY一个简易超声波倒车雷达(含蜂鸣器报警)

从测距到实战:蓝桥杯开发板打造智能超声波雷达系统 第一次倒车时听到蜂鸣器急促的"滴滴"声,我意识到这个简单的超声波模块能做的远不止显示数字。作为参加过蓝桥杯的电子爱好者,我们手头的开发板其实蕴藏着解决实际问题的潜力——…...

新入职场的软件测试员,请立刻戒掉这3个学生思维

在软件测试领域,新入职的员工往往带着校园习得的学生思维,这些思维模式在学术环境中或许有效,但在职场中却成为阻碍专业成长的隐形障碍。尤其对于软件测试从业者,工作核心是保障产品质量、识别潜在风险,而非简单执行任…...

AnyLogic-Pypeline:打破仿真与AI壁垒的智能集成方案

AnyLogic-Pypeline:打破仿真与AI壁垒的智能集成方案 【免费下载链接】AnyLogic-Pypeline A custom AnyLogic library for running Python inside an AnyLogic model (Java) 项目地址: https://gitcode.com/gh_mirrors/an/AnyLogic-Pypeline 还在为AnyLogic与…...

C++27 <filesystem> 2.0来了:3个被90%开发者忽略的原子操作接口,如何避免数据竞态丢失?

第一章:C27 2.0 核心演进与原子语义设计哲学C27 将对 进行里程碑式重构,引入“原子语义”(Atomic Semantics)作为核心设计范式——所有路径操作默认具备不可分割性与状态一致性保障,彻底规避竞态条件引发的中间态污染…...

Phi-4-mini-reasoning在ollama中如何提升数学推理能力?微调数据与提示策略分享

Phi-4-mini-reasoning在ollama中如何提升数学推理能力?微调数据与提示策略分享 数学推理一直是AI领域的挑战性任务,而Phi-4-mini-reasoning作为专门针对推理任务优化的轻量级模型,在ollama平台上展现出了令人惊喜的数学问题解决能力。本文将深…...

OpenClaw家庭相册:Kimi-VL-A3B-Thinking智能归档与回忆生成

OpenClaw家庭相册:Kimi-VL-A3B-Thining智能归档与回忆生成 1. 为什么需要智能相册管理 去年夏天整理家庭照片时,我发现自己陷入了数字时代的典型困境——手机里有8000多张照片,电脑硬盘上还有历年备份的3万多张。想找一张孩子第一次走路的照…...

)

用ESP32-S3做个桌面小玩意:语音助手、GIF时钟和网络摄像头三合一(附开源代码与避坑指南)

ESP32-S3三合一桌面终端:从零构建智能语音助手、动态时钟与摄像监控系统 引言:当极客精神遇见桌面美学 在创客圈里流传着一句话:"如果你桌面上没有至少三个正在吃灰的开发板,说明你不够极客。"而今天我们要做的…...