Design Complie实验,使用2007年Synopsy的Lab Guide

Design Complie实验,使用2007年Synopsy的Lab Guide

文章目录

- Design Complie实验,使用2007年Synopsy的Lab Guide

- 1 DC实验

- 1.1 Setup and Synthesis Flow

- Task 1 Update the setup file

- Task 2 Invoke Design Vision

- Task 3 Read the Design into DC Memory

- Task 4 Explore Symbol and Schematic Views

- Task 5 Explore the Mouse Functions

- Task 6 Constrain TOP with a Script file

- Task 7 Compile or Map to Vendor-Specific Gates

- Task 8 Generate Reports and Analyze Timing

- Task 9 Save the Optimized Design

- Task 10 Remove Designs and Exit Design Vision

- 1.2 Timing and Area Constraints

- Task 1 Determine the Target Library’s Time Unit

- Task 2 Create a Timing and Area Constraints File

- Task 3 Apply Constraints and Validate

- 1.3 Environmental Attributes

- Constraint

- Apply & Check

- 1.4 More Constraint Considerations

- Constraint

- Apply & Check

- Compile

1 DC实验

1.1 Setup and Synthesis Flow

Task 1 Update the setup file

为了观察.synopsys_dc.setup文件,需要查看隐藏文件。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-cusoOroY-1680765318841)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230401112904884.png)]](https://img-blog.csdnimg.cn/0eeda69ef33e489294e161615ec3ed20.png)

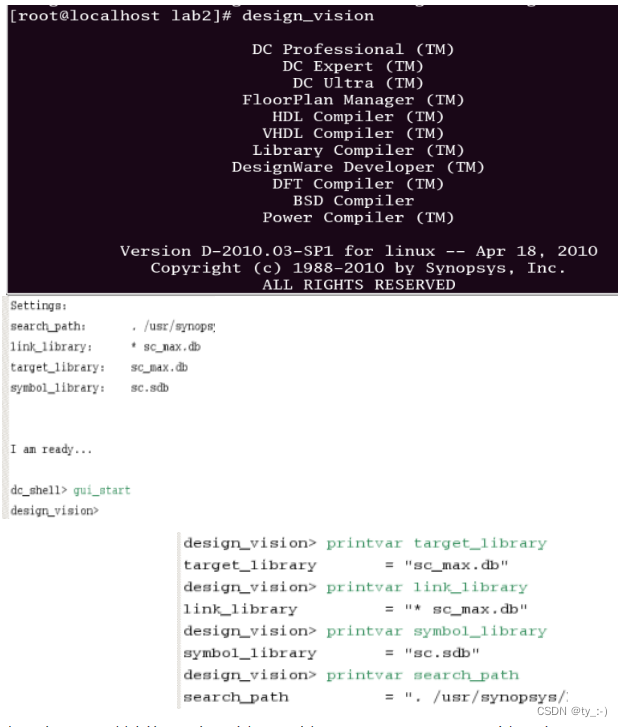

Task 2 Invoke Design Vision

通过design_vision开启DC。可以看到的是,link library为 * sc_max.db ,target_library为sc_max.db ,symbol library为sc.sdb ,也可以通过在DCprompt中输入printvar去查看不同的library

点开File->Setup其中的search path如下,确保syn,syn_ver,sim_ver路径正确

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-uXR1TkRy-1680765187277)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230330203619890.png)]](https://img-blog.csdnimg.cn/951107514b09426ea019f3b6a7126089.png)

Task 3 Read the Design into DC Memory

DC可以开VHDL,Verilog,System Verilog RTL文件。这里读取/rtl/TOP.vhd文件。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-kN7oue62-1680765187278)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230330204400685.png)]](https://img-blog.csdnimg.cn/dbceb3346e774fea85a57f90f75a2e5e.png)

之后File->Link Design->OK进行连接,同时对这个unmapped设计进行ddc保存,保存到unmapped文件夹

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Pif56hEY-1680765187278)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230330204835701.png)][外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-qmYG1oN3-1680765187279)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230330204852265.png)]](https://img-blog.csdnimg.cn/79269e322b844c9c839728bf74cfd0df.png)

Task 4 Explore Symbol and Schematic Views

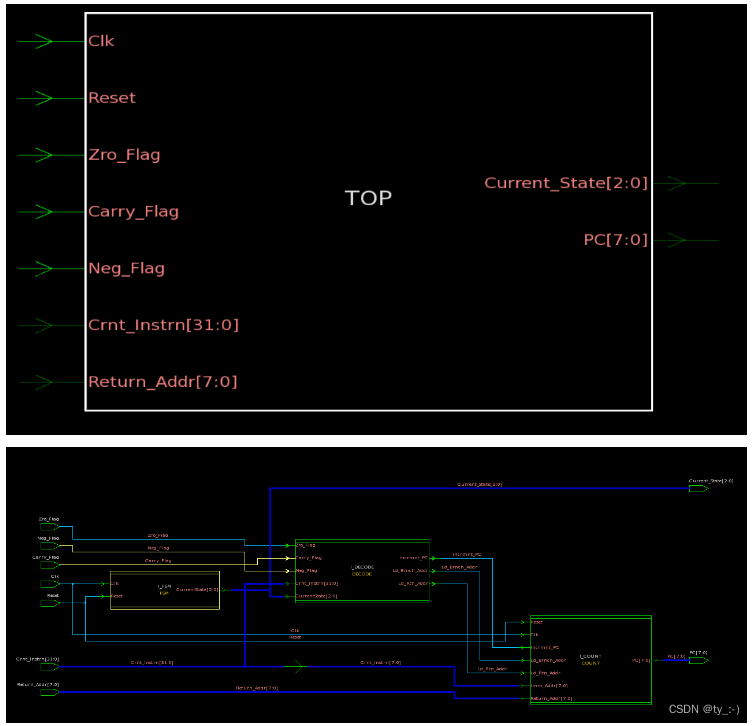

点击create symbol view,生成top的symbol,

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-1tHVDn7g-1680765187279)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230330205725407.png)]](https://img-blog.csdnimg.cn/79d3eebf5fd241ca8614653844bd0e84.png)

同时可以点进去(或者点击图标create design schematic)查看不同子模块的rtl,这里有FSM,DECODE,COUNT三部分组成。但是因为还没有完成design,所以暂时看不到gate级的电路

Task 5 Explore the Mouse Functions

鼠标schematic中右键,fit窗口大小

Task 6 Constrain TOP with a Script file

生成TOP.con约束文件,在命令行里输入source TOP.con

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Ik48jhL0-1680765187280)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230330212841352.png)]](https://img-blog.csdnimg.cn/1a748ba01df74d89a086e634fe3f6486.png)

Task 7 Compile or Map to Vendor-Specific Gates

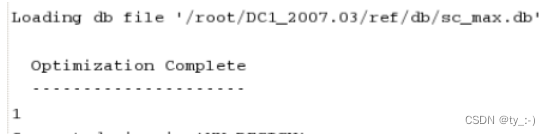

为了编译design,需要在DC中输入compile,log输出如下

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-oiPgTMEB-1680765187280)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230330213310698.png)]](https://img-blog.csdnimg.cn/930cde1198404949b153ffaab16a971b.png)

其中area表示面积,Worst neg slack表示相对于其约束,设计中的关键路径或最坏路径有多少是违反的(实际的delay减去预期的delay)。total neg slack表示violating path slacks的总数。

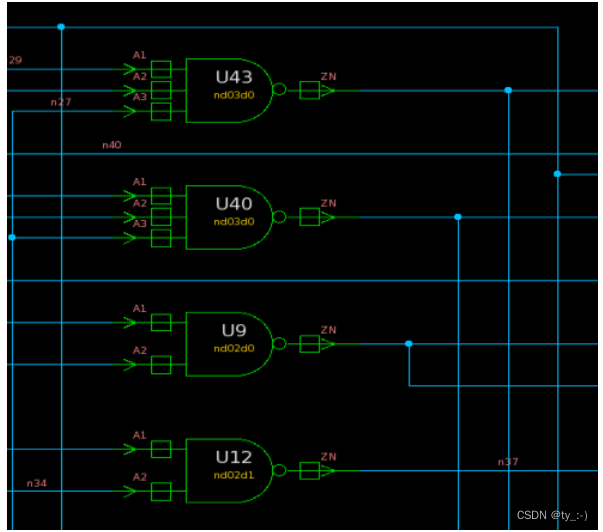

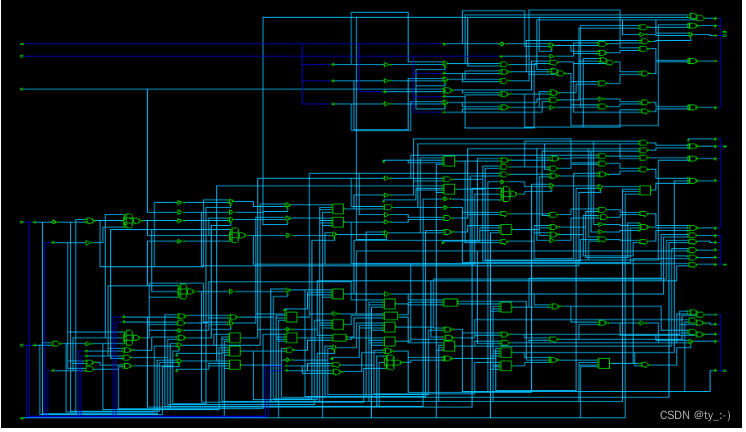

compile结束后可以看到门级电路

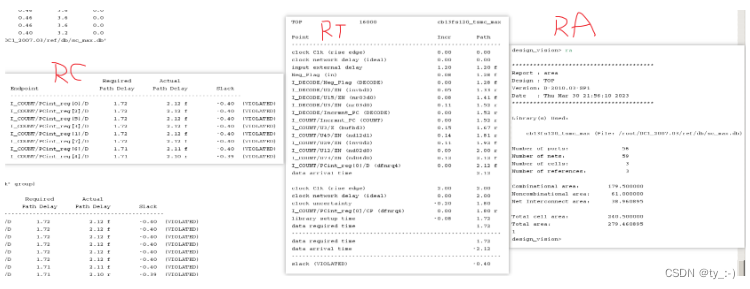

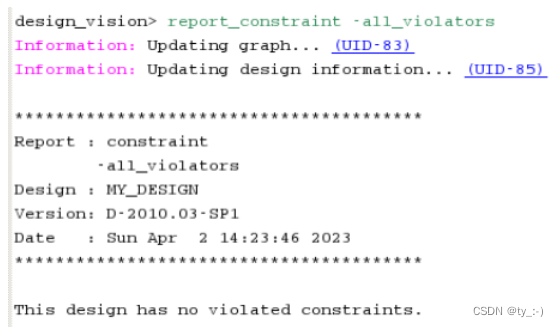

Task 8 Generate Reports and Analyze Timing

在top的symbol下,输入rc(report constraint),这条语句被提前在.setup里面定义过了,他实现了下面的语句。

report_constraint -all_violators

同时也有rt(report timing),默认看的是关键路径上的。还有ra(area)

关键路径是指设计中从输入到输出经过的延时最长的逻辑路径。优化关键路径是一种提高设计工作速度的有效方法。一般地,从输入到输出的延时取决于信号所经过的延时最大路径,而与其他延时小的路径无关。在优化设计过程中关键路径法可以反复使用,直到不可能减少关键路径延时为止。EDA工具中综合器及设计分析器通常都提供关键路径的信息以便设计者改进设计,提高速度。

每一个path都有专属的slack,slack值可以是正,0或者负。某一个path拥有最坏的slack的话则称之为 critical path

critical path拥有最大的负slack值。若是所有的path都没有时序违规,则slack都是正数,此时最小的那个slack则是critical path。

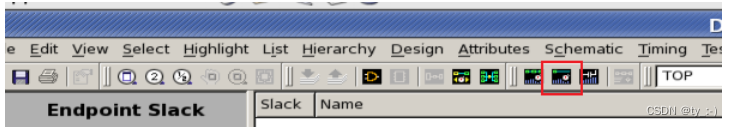

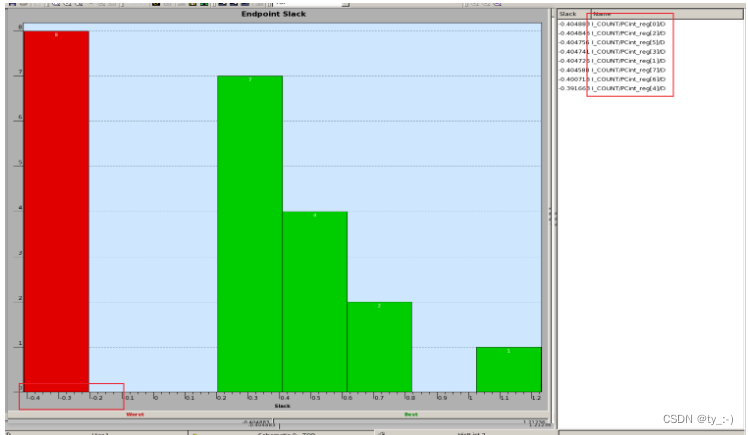

可以查看endpoint slack historgram,点击create endpoint slack historgram

可以看到,critical path在I_COUNT处。图中红色为violating paths,绿色则为满足的约束

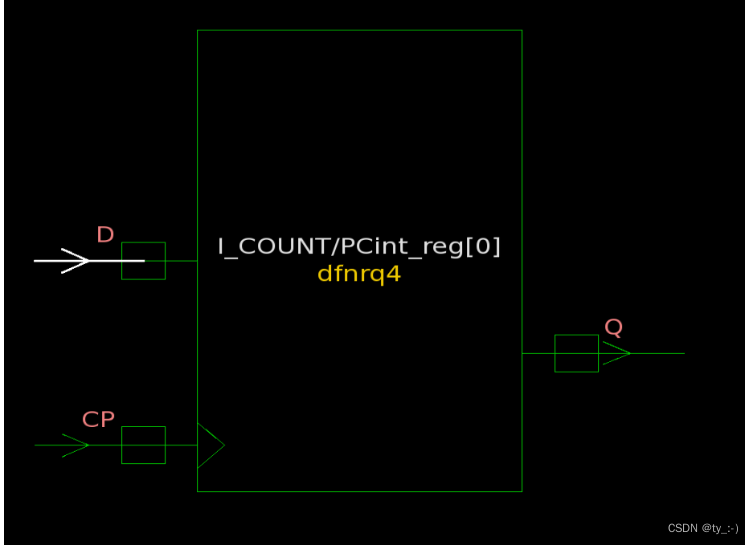

同时点slack里的名字,以及button,create pathschematic of selected logic,可以看到这个point

之后点中间的add paths to path schematic 可以看到在原理图里的path

Task 9 Save the Optimized Design

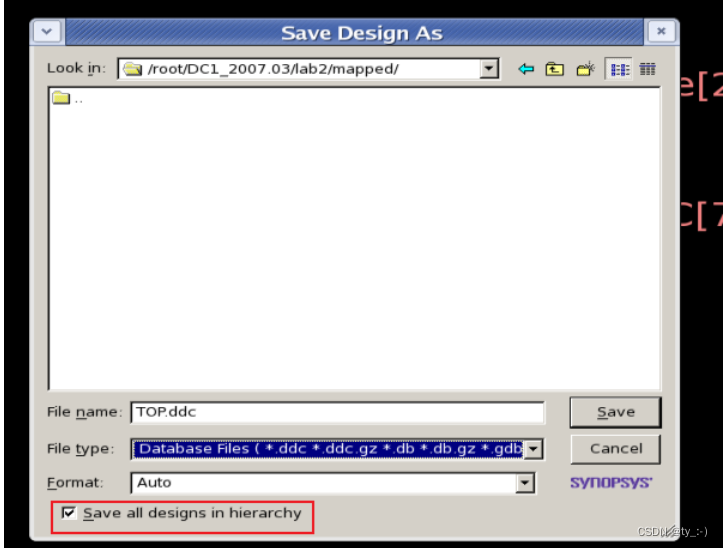

保存的是symbol,同时save as的时候要save all designs

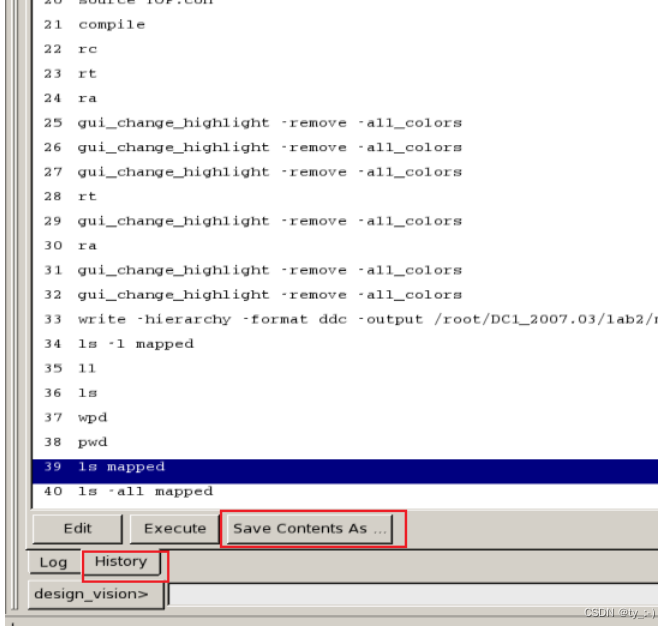

同时也可以在history里保存command history

Task 10 Remove Designs and Exit Design Vision

fr:关闭所有designs窗口,也可以File->Remove All Designs

remove_design -designs

h:查看所有的commands

通过exit关闭DC.

通过下面可以重新加载log文件,需要提前把command.log复制册成lab2.log

design_vision -f lab2.log

1.2 Timing and Area Constraints

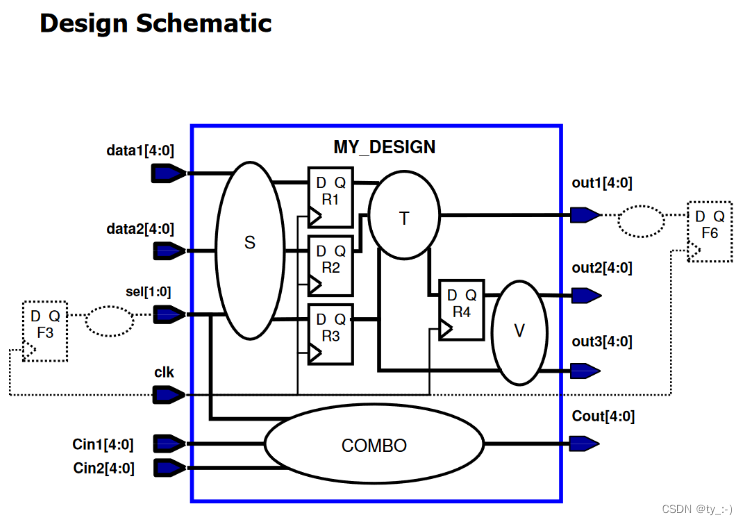

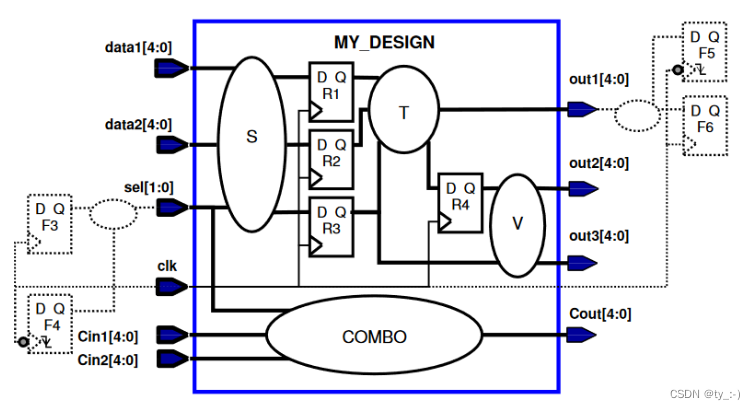

完成下面design的时序约束和面积约束。

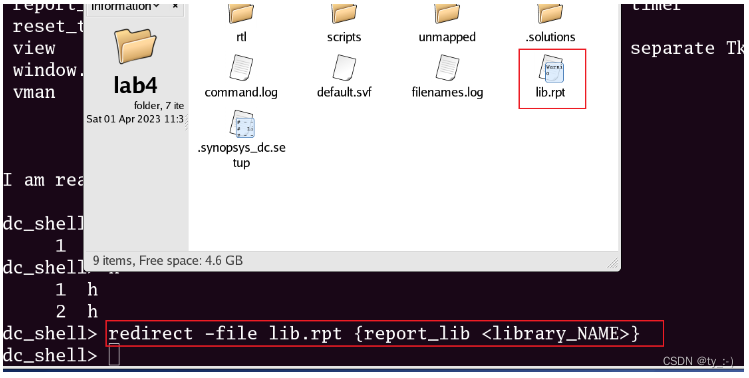

Task 1 Determine the Target Library’s Time Unit

通过下面指令启动dc,并且read taget文件

dc_shell-tread_db <target_library_FILE>

list_libs

生成report文件

Task 2 Create a Timing and Area Constraints File

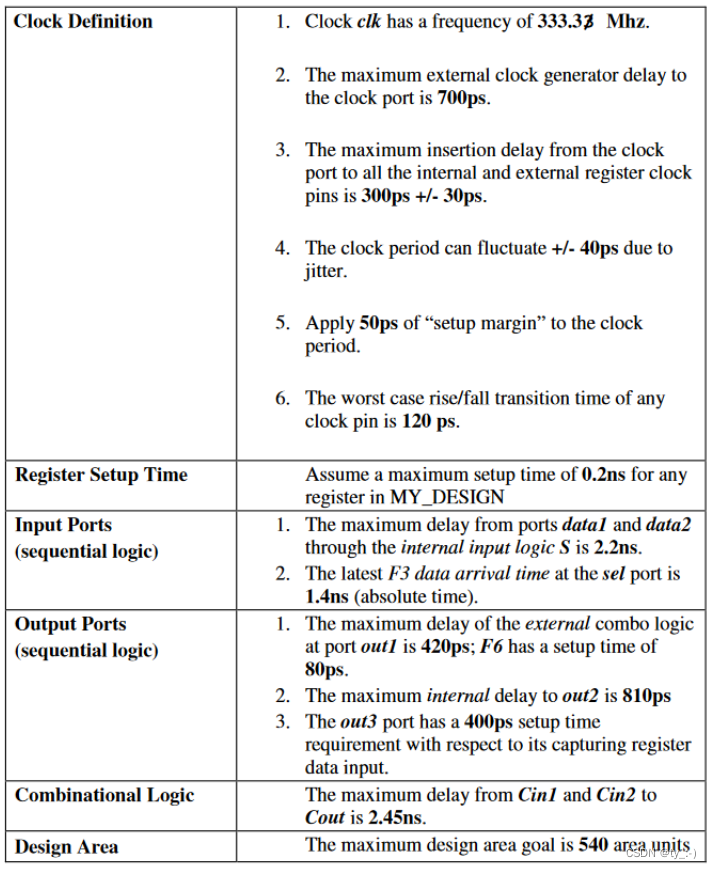

写时序约束和面积约束

time unit:1ns

要求如下

约束lab4.con如下

###################################

# Constraints file for lab4

###################################reset_design; #good first step#f=333.3MHz

create_clock -period 3 [get_ports clk] #clkgen->clock port 700ps

set_clock_latency -source -max 0.7 [get_ports clk]#clk port->all internal and external register clock pins is 300ps +/- 30ps,which means max0.33n and min0.27n.If not use -source,delay is applied to clk network latency

set_clock_latency -max 0.33 [get_ports clk]

set_clock_latency -min 0.27 [get_ports clk]#jitter +/-0.04n and margin 0.05n.Becauese it doesnot say setup or hold ,use default(include setup and hold)

set_clock_uncertainty 0.09 [get_ports clk]#worst rise/fall transition time of any clk pins 0.12n,use default(include fall and rise)

set_clock_transition 0.12 [get_ports clk]#assume a maximum setup time of 0.2n for any register in MY_DESIGN

#data1 and data2 2.2n delay through logic S. SO we have 3-(2.2+0.2)=0.6ns,where 3ns is Tclk ,2.2n is ports->S, 0.2n is Tsetup

set_input_delay -max 0.6 -clock clk [get_ports "data1 data2"]#F3->sel ports 1.4ns. So we have 3-1.4=1.6ns(to ports,not ff,dont have setup time)

set_input_delay -max 1.6 -clock clk [get_ports sel]##set output

#clk->out1=3-0.42-0.08=2.5,where 3n is Tclk,0.42n is combo logic at port out1,0.08n is F6 Tsetup

set_output_delay -clock clk -max 2.5 [get_ports out1]

#clk->out2=3-0.81=2.19,where 0.81n is internal delay

set_output_delay -clock clk -max 2.19 [get_ports out2]

#out3 has 0.4n Tsetup,3-0.4=2.6

set_output_delay -clock clk -max 2.6 [get_ports out3]##Combinational Logic,need virtual clk.But we only have cin1&cin2 -> cout delay is 2.45n<3n.So no need opt

#creat_clock -name Vclk -period 2#area

set_max_area 540

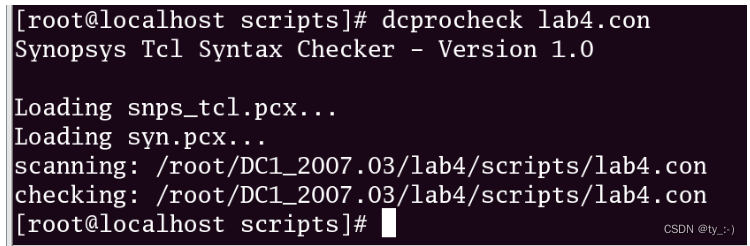

Check一下,无报错

Task 3 Apply Constraints and Validate

应用约束文件以及check

#apply

source scripts/lab4.con#check no missing or conflicting

check_timing#check design

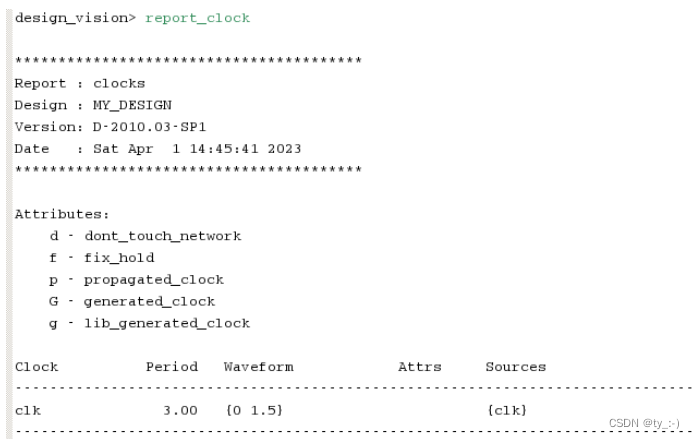

report_clock

reprot_clock -skew

report_port -verbose#write con

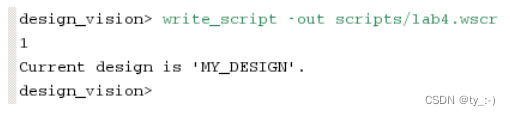

write_script -out scripts/lab4.wscr

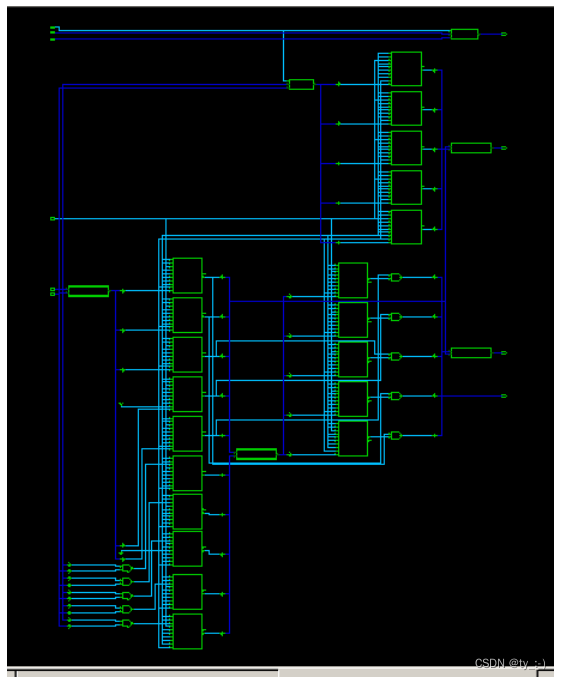

lab4的schematic如下

通过source lab4.con来约束

查看clock等信息

clk时钟周期3ns,report_clock

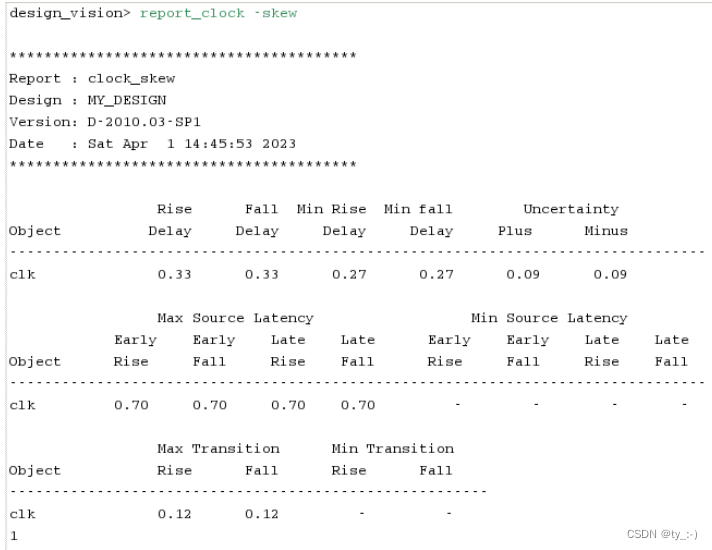

对于clk的一系列约束report_clock -skew

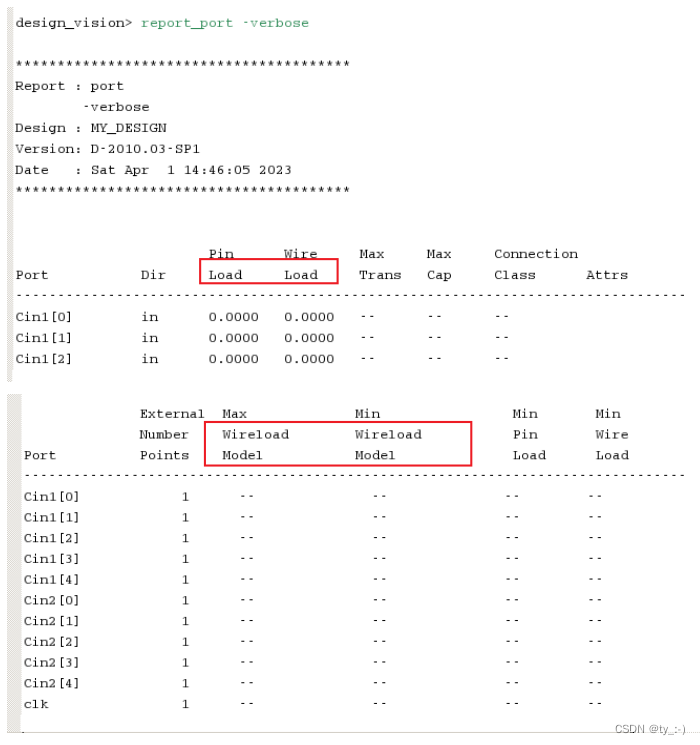

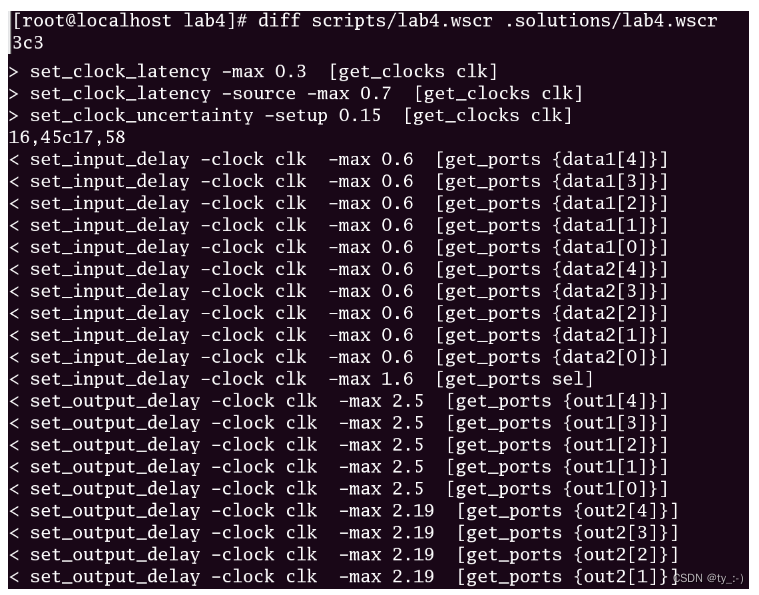

对于ports的报告,load都为0,线模型未定义。report_port -verbose(查看完整设置)

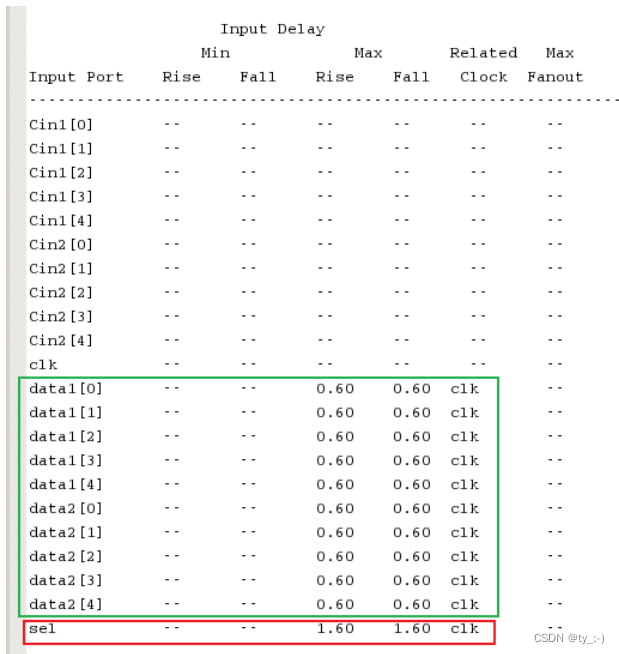

input delay,均和设置一致

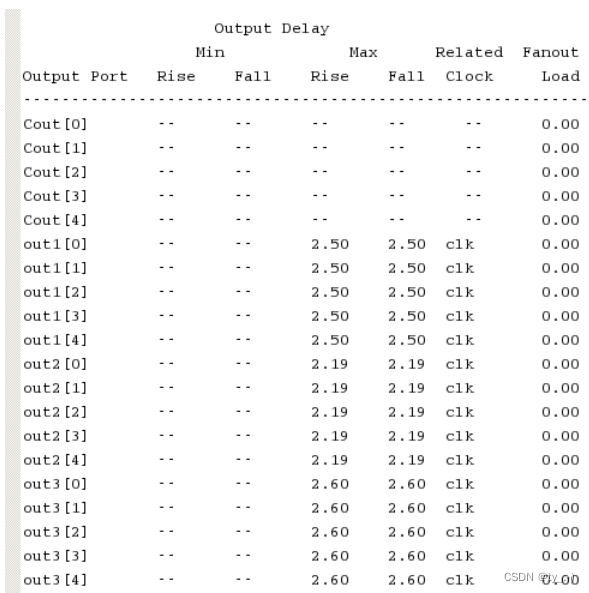

output delay,均和设置一致

写出约束文件,以进行进一步检查 是否正确。

diff a b

之后,对原约束文件进行修改,当完全符合之后的代码如下

###################################

# Constraints file for lab4

###################################reset_design; #good first step#f=333.3MHz

#

create_clock -period 3 [get_ports clk] #clkgen->clock port 700ps

#

set_clock_latency -source -max 0.7 [get_clocks clk]#clk port->all internal and external register clock pins is 300ps +/- 30ps,where +-30 is 60ps uncertainty.If not use -source,delay is applied to clk network latency

#

set_clock_latency -max 0.3 [get_clocks clk]#jitter +0.04n(max) and margin 0.05n and +-30=60ps skew.Becauese it doesnot say setup or hold ,use default(include setup and hold)

#skew+jitter(max)+margin

#

set_clock_uncertainty -setup 0.15 [get_clocks clk]#worst rise/fall transition time of any clk pins 0.12n,use default(include fall and rise)

#

set_clock_transition 0.12 [get_ports clk]#assume a maximum setup time of 0.2n for any register in MY_DESIGN

#data1 and data2 2.2n delay through logic S. SO we have 3-(2.2+0.2+0.15)=0.45ns,where 3ns is Tclk ,2.2n is ports->S, 0.2n is Tsetup,0.15n is clock uncertainty

#

set_input_delay -max 0.45 -clock clk [get_ports "data1 data2"]#F3->sel ports 1.4ns.

#The total clock insertion delay or latency to the external registers is 700p+300p=1n.So we have 1.4-1=0.4ns

#

set_input_delay -max 0.4 -clock clk [get_ports sel]##set output

#out1=0.42+0.08=0.5,where 0.42n is combo logic at port out1,0.08n is F6 Tsetup

#

set_output_delay -clock clk -max 0.5 [get_ports out1]

#out2=3-0.15-0.81=2.04,where 0.81n is internal delay,0.15n is clk uncertainty

#

set_output_delay -clock clk -max 2.04 [get_ports out2]

#out3 has 0.4n Tsetup

#

set_output_delay -clock clk -max 0.4 [get_ports out3]##The maximum delay through the combinational logic is 2.45ns. This can be constrained by pretending that there are launching registers on the input ports Cin1 and Cin2 and capturing registers on the output port Cout, and applying corresponding input and output delays. The sum of the external input and output delay values must be equal to the clock period minus the clock uncertainty minus the maximum combo delay = 3ns - 0.15ns - 2.45ns = 0.4ns. This means that the input and output delay values can be 0.4 and 0.0, or 0.2 and 0.2, or 0.1 and 0.3, etc., respectively.

#

set_input_delay -max 0.3 -clock clk [get_ports Cin*]

set_output_delay -max 0.1 -clock clk [get_ports Cout]

#area

set_max_area 540

通过组合逻辑的最大延迟为2.45ns。这可以通过假设在输入端口Cin1和Cin2上有启动寄存器,在输出端口Cout上有捕获寄存器,并应用相应的输入和输出延迟来限制。外部输入输出延时值之和必须等于时钟周期减去时钟不确定性减去最大组合延时= 3ns - 0.15ns - 2.45ns = 0.4ns。这意味着输入和输出延迟值可以分别为0.4和0.0,或0.2和0.2,或0.1和0.3,等等。

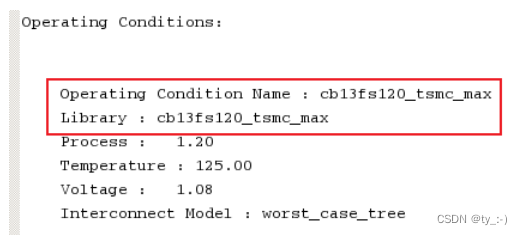

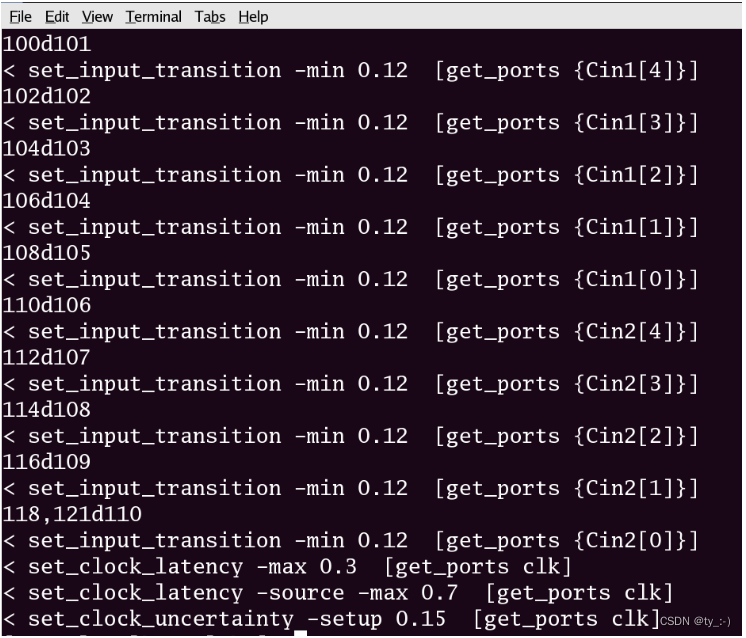

再次重复检查操作。红框中上边为标准答案(<),下方为本地答案(>),此时已经修改完成

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-qFuD2BuT-1680765187286)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230401154010407.png)]](https://img-blog.csdnimg.cn/b57350dd6ff4453ebe19444c41adefbd.png)

这里注意get_clocks和get_ports的区别

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-LBnuPtPL-1680765187286)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230401153350671.png)]](https://img-blog.csdnimg.cn/3273113601124fd2b98097b95a51ce32.png)

- get_clocks:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-erT4UWam-1680765187286)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230401154436219.png)]](https://img-blog.csdnimg.cn/ddf4c45518f5493ab5ae021d1ed189c1.png)

- get_ports:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-db8lst14-1680765187286)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230401154526908.png)]](https://img-blog.csdnimg.cn/a302f856bacd4d6ca535e3b9a16dd404.png)

最后保存symbol ,save as ddc文件

1.3 Environmental Attributes

Constraint

环境属性的约束如下

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-wrZXKyrn-1680765187286)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230401161636505.png)]](https://img-blog.csdnimg.cn/b12162d5483847349126dc084ec6d239.png)

首先根据lab4.con继续往下写约束条件

设置线模型的时候,先把auto_wire_load_selection 设置成false,这时,如果没有声明model_name,那么wire load model就不会被用到

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-pvMY7wpX-1680765187287)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230401165943990.png)]](https://img-blog.csdnimg.cn/4e14f43bffe04e58a6e8d648564ff01d.png)

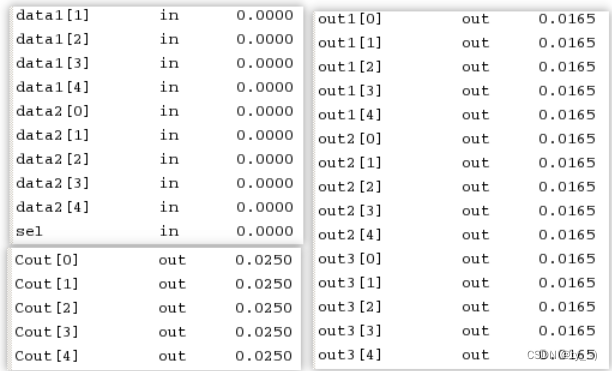

Operating Conditons:

如何去看所有线负载模型的name

整体con文件

#ENVIRONMENTAL ATTRIBUTES

#input ex clk & cin*

#

set_driving_cell -lib_cell bufbd1 -library cb13fs120_tsmc_max \[remove_from_collection [all_inputs] [get_ports "clk Cin*"]]#120ps max input transition

#

set_input_transition 0.12 [get_ports Cin*]#output

#ex cout

#

set_load [expr 2 * [load_of cb13fs120_tsmc_max/bufbd7/I]] [get_ports out*]# Cout drives 25fF,

#

set_load 0.025 [get_ports Cout*]# wireload model

# From the wireload model selection table, a design size between 200 and

# 8000 area units uses the model called "8000"; The default wireload

# mode in this library in "enclosed"

#

set auto_wire_load_selection false

set_wire_load_model -name 8000# operating condition use to scale cell and net delays.

#

set_operating_condition -max cb13fs120_tsmc_max

Apply & Check

之后apply并且check

#apply:

source scripts/lab6.con#check:

report_port -v

report_design

report_port -v

transition&input driving cell:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-jc7XgkDG-1680765187287)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230401174710049.png)]](https://img-blog.csdnimg.cn/8fd520a83e094cf7acf7c4db664d4ed9.png)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-fmntdAEB-1680765187287)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230401174504392.png)]](https://img-blog.csdnimg.cn/500f8d1a2a8f43a386a20952d4b4c549.png)

load:

report_design

使用的wire loading model为

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-V8ZVcozN-1680765187287)(./%E6%95%B0%E5%AD%97%E8%8A%AF%E7%89%87%E7%89%A9%E7%90%86%E8%AE%BE%E8%AE%A1%E4%B8%8EEDA%E5%B7%A5%E5%85%B7-%E9%92%9F%E5%A4%A9%E6%BA%90-2201210722.assets/image-20230401174843060.png)]](https://img-blog.csdnimg.cn/6f6f7499581c47a69782ea3d6b697212.png)

operating conditions为

进行对比显示的都是(<)即和答案一致。(这里仍然使用的是get_ports clk)

最后保存symbol ,save as ddc文件

1.4 More Constraint Considerations

Constraint

Design schematic如下

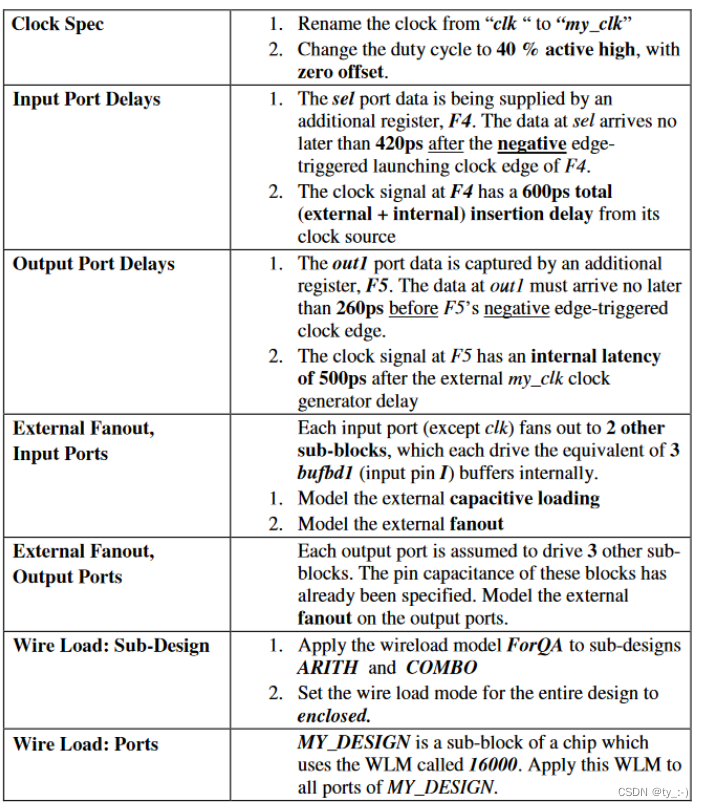

constraint要求如下:

clock spec:

rename clk->my_clk,同时修改文中-clock my_clk,这里只有-clock需要修改,但是对于get_ports而言或者get_clocks而言他仍然是clk

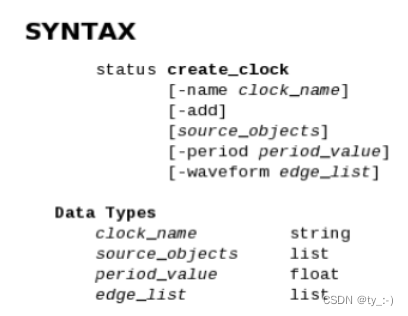

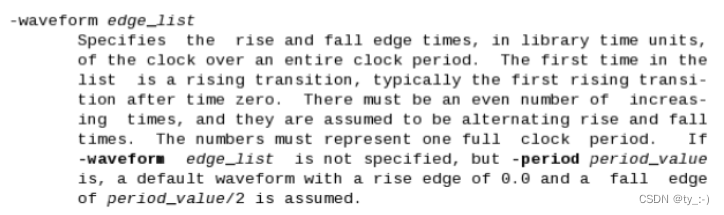

要修改他的占空比,首先看create_clock的语法以及参数,如下。需要着重关注的是-waveform edge_list参数

waveform的话,已经规定Tclk为3ns那么3*0.4=1.2ns,所以waveform{0 1.2},从0n开始上升,1.2n下降

Input ports delay:

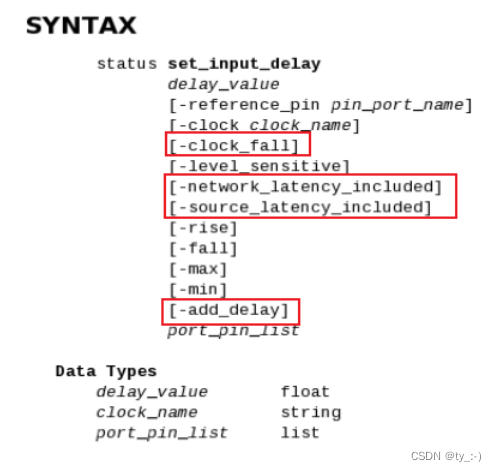

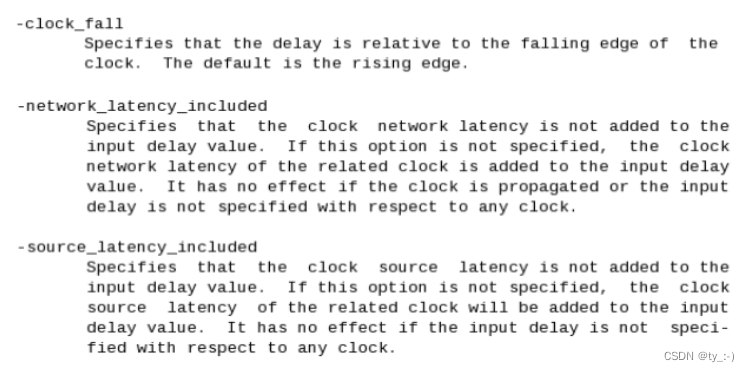

关注set_input_delay,因为在次之前已经有对input_delay的constraint故额外的需要add_delay。同时sel信号在之前我们知道存在clk的latency。以及注意是相对于下降沿的delay

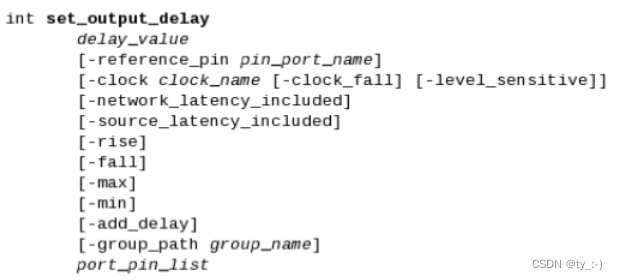

Output port delay:

输出的clk latency就只有network的了,因为从内部往外传的,同时也是相对clk的negtive.

external fanout:

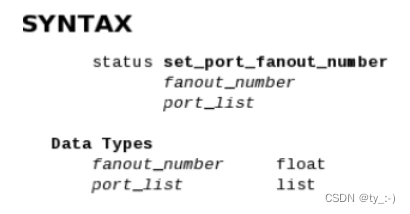

set_port_fanout_number 用来设置port的fanout数目

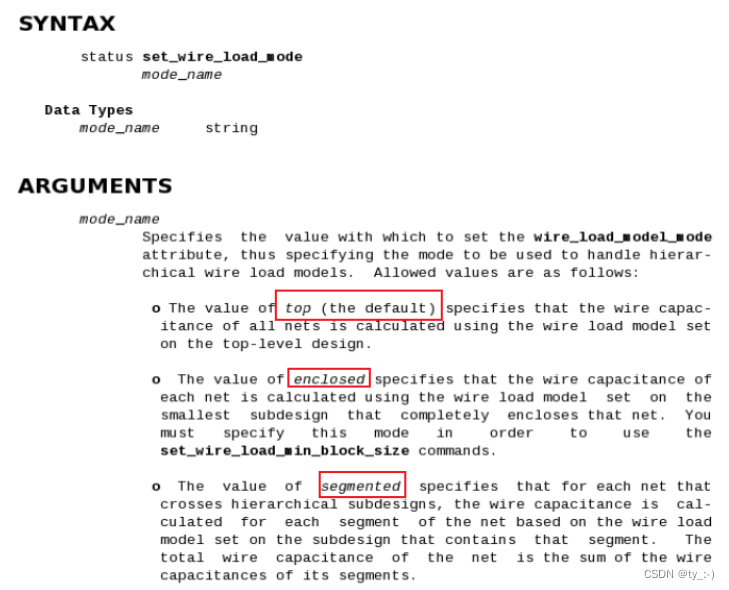

set wire model重新对输出的design进行定义,而enclosed用的是set_wire_load_mode,有三种不同的mode

整体代码如下

# more constraint

# input port delay

# sel,with latency 700ps (source) + 300ps (network)

#

set_input_delay -max 1.02 -clock my_clk -add_delay -clock_fall -network_latency_included -

source_latency_included [get_ports sel]#output port delay

#only network latency ,clock fall,0.26-0.5=-0.24n

#

set_output_delay -max -0.24 -clock my_clk -clock_fall -add_delay -network_latency_included [get_ports out1] #External fanout input

#each in port (ex clk)fans out to 2 other sub-blocks

#

set all_in_ex_clk [remove_from_collection [all_inputs] [get_ports clk]]#model external capacitive loading,2*3=6

#

set_load [expr 6 * [load_of cb13fs120_tsmc_max/bufbd1/I]] $all_in_ex_clk#model external fanout

#

set_port_fanout_number 2 $all_in_ex_clk#External fanout output

#driving 3 sub-blocks

#

set_port_fanout_number 3 [all_outputs]#wire load :sub-design

#wireload model->ForQA to sub-designs ARITH&COMBO

#use enclosed

#

set_wire_load_model -name ForQA [get_designs "ARITH COMBO"]

set_wire_load_mode enclosed#wire load :ports

#wlm(wire load model):"16000"

#

set_wire_load_model -name 16000 [all_inputs]

set_wire_load_model -name 16000 [all_outputs]

Apply & Check

source scripts/lab9.con进行apply

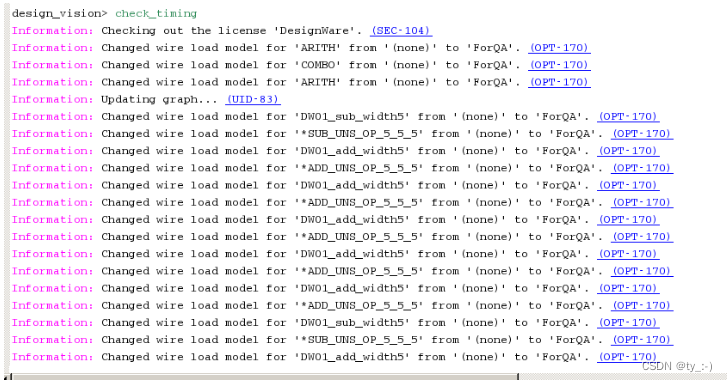

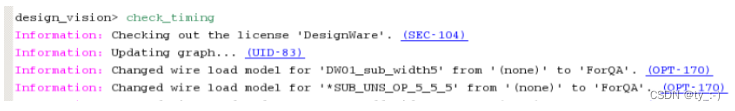

check_timing,可以看到一些变动的信息

report_clock,3ns周期,0n上升,1.2n下降,名称为my_clk

report_port -v查看port情况

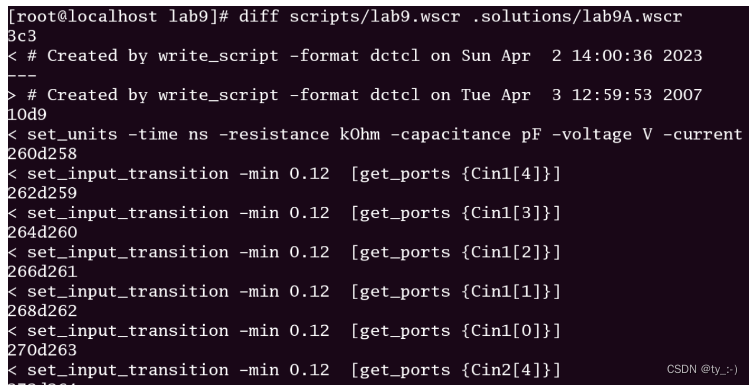

compare:

design_vision>write_script -out scripts/lab9.wscr

unix>diff scripts/lab9.wscr .solutions/lab9A.wscr

Compile

design_vision>compile_ultra -scan -retime -timing

注:这一步会比较久,完成会提示优化完成

再看他的schematic如下,相较于lab2时刻的电路,变动很大

同时检查是否还存在violation

save as到ddc文件

相关文章:

Design Complie实验,使用2007年Synopsy的Lab Guide

Design Complie实验,使用2007年Synopsy的Lab Guide 文章目录Design Complie实验,使用2007年Synopsy的Lab Guide1 DC实验1.1 Setup and Synthesis FlowTask 1 Update the setup fileTask 2 Invoke Design VisionTask 3 Read the Design into DC MemoryTas…...

问题 B: C语言10.2

题目描述: 输入a、b、c三个整数,按先大后小的顺序输出a、b和c。注意请使用指针变量的方式进行比较和输出。 输入 三个用空格隔开的整数a、b和c。 输出 按先大后小的顺序输出a、b和c,用空格隔开。 请注意行尾输出换行。 样例输入 9 0 1…...

多线程控制并发数目工具类Semaphore

文章目录前言Semaphore原理Semaphore源码解析内部继承AQS保证同步acquire获取许可release释放许可实战演示总结前言 在多线程编码过程中,我们会用到多线程来提升运行效率。比如我们的Executors创建线程池,程序尽可能的压榨CPU资源来提升我们程序吞吐量。…...

Redis篇之五大数据类型

1、五大数据类型 4.1、String(字符串) String是Redis最基本的类型,你可以理解成与Memcached一模一样的类型,一个key对应一个value String类型是二进制安全的。意味着Redis的string可以包含任何数据。比如jpg图片或者序列化的对象…...

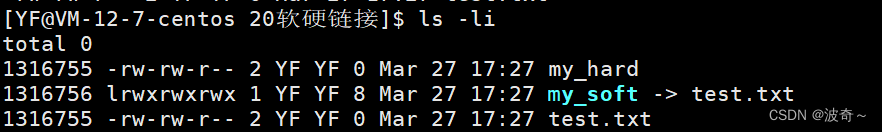

Linux->文件系统磁盘文件管理

目录 1 磁盘结构 2 逻辑抽象管理磁盘 2.1 逻辑抽象 2.2 管理磁盘 2.3 补充知识 3 软硬连接 1 磁盘结构 本篇的学习需要建立在大家在脑海中有一副磁盘的结构才能进行下去,所以我会以图解的方式为大家简单讲解一下,注:博主对这一部分并不是…...

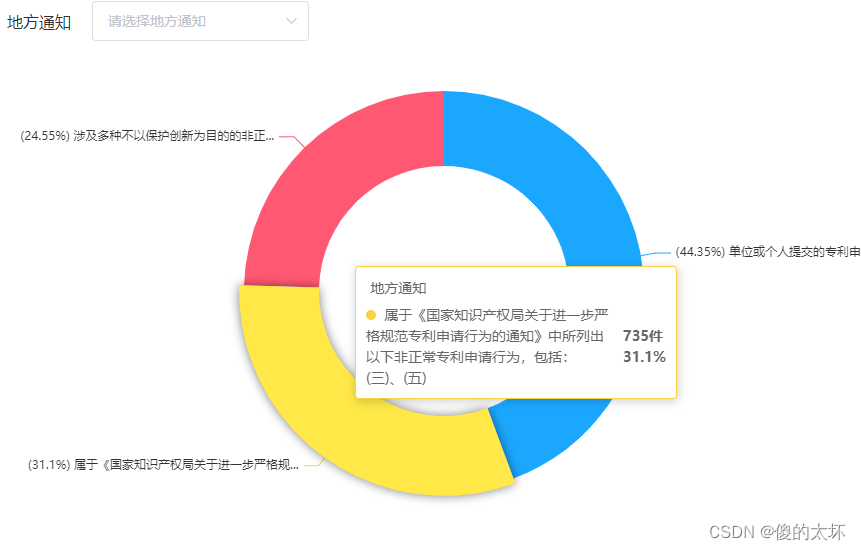

echarts tooltip文字太长换行

tooltip文字太长换行,设置了宽度也没有换行,加上一句: extraCssText: ‘max-width:300px; white-space:pre-wrap’, 没加之前是这样: 加上之后 extraCssText: ‘max-width:300px; white-space:pre-wrap’, tooltip: {trigger: &…...

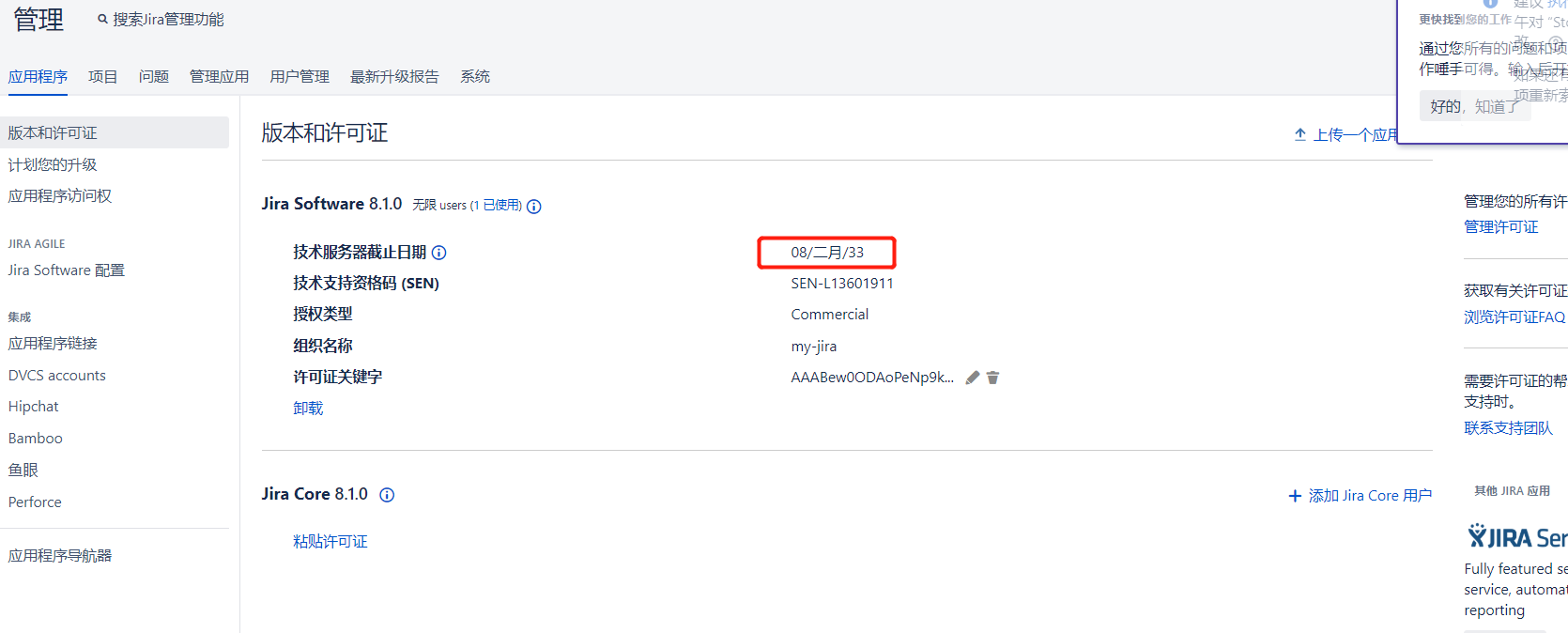

Docker 部署Jira8.1.0

Jira与Confluence一样,都需要用到独立的数据库,对于数据库的安装我们不做介绍,主要介绍如何用Docker部署Jira以及对Jira进行破解的操作。 1、数据库准备 关于数据库官方文档说明:https://confluence.atlassian.com/adminjiraserv…...

)

枚举、模拟法(蓝桥杯卡片、数的分解为例)

枚举和模拟算法是计算机领域常用的两种基本算法。枚举算法是一种通过列举所有可能的情况来解决问题的方法。模拟算法则是通过模拟真实场景来解决问题。 枚举、模拟法 枚举算法是指将问题分解为一系列离散的情况,通过枚举所有可能的情况,逐一检查每种情…...

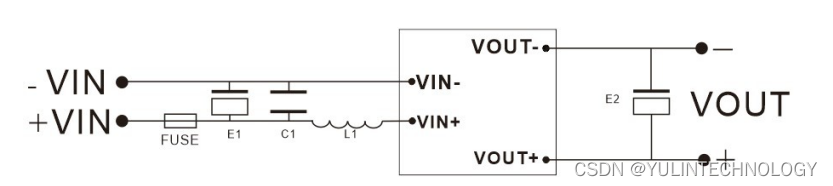

DC-DC升压变换器直流隔离高压输出稳压电源模块5v12v24v48v转50v110v150v220v250v300v350v500v

HRB 系列隔离宽电压输入高电压稳压输出 特点 效率高达 80%以上1*1英寸标准封装单电压输出稳压输出工作温度: -40℃~85℃阻燃封装,满足UL94-V0 要求温度特性好可直接焊在PCB 上应用 HRB 0.2~10W 系列模块电源是一种DC-DC升压变换器。该模块电源的输入电压分为&#…...

jQuery创建、添加、删除元素

一、创建元素 语法: $("<li></li>"); 动态的创建了一个 <li> 二、添加元素 1. 内部添加 1、element.append(内容) 把内容放入匹配元素内部最后面,类似原生 appendChild。 2、element.prepend(内容) 把内容放入匹…...

产品快讯丨神策数据 A/B 测试试验指标管理重磅升级

神策数据:为了更好地帮助企业管理试验指标,神策数据 A/B 测试完善了指标类型、配置方式、计算原理等,帮助分析师、运营同学等明确计算逻辑,并最大程度减少歧义以及与技术同学沟通的成本,以实现企业内部信息的有效统一。…...

游戏开发之Unity2021URP项目场景的构建

地面的修改和编辑:地面插件的使用 打开包管理器,在左边的包那里选择“Unity注册表”,在右边进行搜索“Polybrush”,之后选择右下角的安装 安装完之后要选择样本中的URP进行导入,因为我们的项目是URP渲染管线的&#x…...

数学分析:多元微积分1

卓里奇的数学分析的好处在于直接从多元函数来入手多元微积分,引出矩阵,十分自然。 紧集的概念,感觉直接用闭集去理解就行,(对于图形学来说)。 多元函数的极限,其实和单元函数并没有什么区别。 这…...

STC32G 三轮车负压电磁

文章目录前言整车效果控制思路循迹环岛处理障碍处理关键代码部分差比和以及当前速度计算角速度环速度环环岛处理障碍处理前言 年后就没怎么碰车了,到3月中旬换三轮了,可算有一点成效了,做个记录。 整车效果 三轮负压电磁慢速元素识别控制思…...

【编程小记】位运算 x -x 表示含义

位运算 x & -x 表示含义一、原码反码补码二、位运算 x & -x 表示含义三、最终结论一、原码反码补码 在计算机中,整数的数据的存储是按照补码的方式进行存储的 按照数据与0的大小,数据又被分为正数与负数 正数的原码反码补码相同。负数的原码&…...

信创PC利旧管理新模式,麒麟信安助力国家某部委实现高效云办公

2022年,国家某部委所有桌面终端均已完成信创PC替换,并将日常办公所需的办公Office套件、OA无纸化办公系统、即时通讯系统等全部迁移至信创PC,但在进行生产业务系统迁移时,该单位信创PC仍存在业务系统与不同芯片PC难适配、应用难兼…...

)

【玩转RT-Thread】RT-Thread内核宏定义详解(rtdef.h)

文章目录1.RT-Thread版本信息2.RT-Thrad基础数据类型定义3.RT-Thread基本数据类型的范围4.RT-Thread系统滴答时钟最大计数值5.RT-Thread IPC数据类型范围6.RT-Thread避免未使用变量警告7.编译器相关定义8.编译器相关定义9.RT-Thread错误码定义1.RT-Thread版本信息 /* RT-Threa…...

PDF转化器免费版有哪些?这几款办公达人们都在用

在现代办公中,文件的排版和格式是非常重要的,无论是发布通知或提交策划书、投档简历或是发表论文、宣传海报或是产品说明书等,我们经常使用PDF文件格式发送给他人。然而,很多人需要对PDF进行编辑修改,通常会先将其转换…...

2022MathorCup赛题B

以下所有文字均基于作者的实际经验,并不具有完全的合理性,请谨慎参考 目录 一、问题分析 (一)问题一 (二)问题二 二、预处理 (一)训练集预处理 (二)测…...

适合销售使用的CRM系统特点

销售人员抱怨CRM系统太复杂,这是一个很重要的问题。毕竟,如果系统太难使用,会导致CRM实用率和效率下降,最终影响公司的运作。在这篇文章中,我们来探讨当销售抱怨crm客户系统太复杂了,企业该如何解决。 缺少…...

实景复刻:动态目标实时映射与轨迹溯源平台

实景复刻:动态目标实时映射与轨迹溯源平台技术定位:实景动态复刻体系构建者 时空轨迹全链路溯源范式开创者执行摘要在数字孪生、视频孪生从静态可视化向动态可计算演进的关键阶段,物理世界与数字世界时空不同步、虚实不精准、动态不连续、轨…...

Qt程序图标设置全攻略:从.ico文件到任务栏显示,一个坑都不踩

Qt程序图标设置全攻略:从资源文件到系统缓存的完整解决方案 第一次用Qt打包发布程序时,我盯着任务栏上那个丑陋的默认图标发呆了十分钟——明明在代码里设置了图标,为什么还是显示不出来?相信很多Qt开发者都遇到过类似问题。图标…...

5大优势解析:如何高效使用免费离线OCR工具

5大优势解析:如何高效使用免费离线OCR工具 【免费下载链接】Umi-OCR OCR software, free and offline. 开源、免费的离线OCR软件。支持截屏/批量导入图片,PDF文档识别,排除水印/页眉页脚,扫描/生成二维码。内置多国语言库。 项目…...

等压雨幕原理在铝合金窗的应用

等压雨幕原理在铝合金窗的应用 摘要: 针对常见的样窗水密气密不达标,首先概述等压雨幕的作用原理,然后介绍其在铝合金门窗应用中的代表性细节。可以看出,控制框扇搭接处的间隙很重要,以及密封胶条合理设计选用的重要性。而且日系推拉采用等压设计的方式很值得借鉴。 关键…...

空洞骑士模组管理器Scarab:2024年最全面的安装与管理指南

空洞骑士模组管理器Scarab:2024年最全面的安装与管理指南 【免费下载链接】Scarab An installer for Hollow Knight mods written with Avalonia. 项目地址: https://gitcode.com/gh_mirrors/sc/Scarab 还在为空洞骑士模组安装的复杂流程而烦恼吗?…...

LVGL在无显存TFT屏上的驱动适配:双缓冲与DMA优化实践

1. 项目概述:当TFT屏幕遇上LVGL最近在做一个嵌入式GUI项目,核心任务是把LVGL这个轻量级图形库,适配到一块分辨率不算高但接口比较“个性”的TFT屏幕上。这活儿听起来像是把标准插头插到非标插座上,得自己动手改改线序。LVGL这几年…...

MySQL 视图使用场景与限制

视图是把查询封装成「虚拟表」的方式,用对了简化查询,用错了性能爆炸。这篇说说视图的用法和注意事项。 什么是视图? -- 视图:保存好的 SQL 查询,像表一样使用 CREATE VIEW view_name AS SELECT column1, column2 FROM…...

去中心化AI市场BloomBee:技术架构、挑战与开发者实践指南

1. 项目概述:当AI遇见去中心化,BloomBee想解决什么?最近在AI和Web3的交叉领域,一个名为BloomBee的项目引起了我的注意。它的名字很有意思,“Bloom”是开花、繁荣的意思,“Bee”是蜜蜂,合起来像是…...

【2026最新】鸿蒙NEXT ArkUI实战:培训班管理系统UI界面开发全攻略

鸿蒙UI开发总是踩坑?ArkUI组件用法记不住?本文用15分钟带你彻底搞懂ArkUI核心组件、布局系统、自定义组件和交互动画,附完整培训班管理系统实战代码和踩坑记录,让你的鸿蒙App界面从此丝滑流畅!一、培训班管理界面设计1…...

)

保姆级教程:INCA 7.2.3 从新建工程到观测标定的完整流程(附A2L文件处理技巧)

INCA 7.2.3 全流程实战指南:从工程搭建到参数标定的深度解析 在汽车电子开发领域,标定工具链的掌握程度直接影响开发效率。作为行业标准的INCA软件,其7.2.3版本在工程管理、实时观测和参数标定方面提供了更完善的解决方案。本文将采用"操…...