SerDes介绍以及原语使用介绍(2)OSERDESE2原语仿真

文章目录

- 前言

- 一、SDR模式

- 1.1、设计代码

- 1.2、testbench代码

- 1.3、仿真分析

- 二、DDR模式下

- 2.1、设计代码

- 2.2、testbench代码

- 2.3、仿真分析

- 三、OSERDES2级联

- 3.1、设计代码

- 3.2、testbench代码

- 3.3、代码分析

前言

上文通过xilinx ug471手册对OSERDESE有了简单的了解,接下来通过仿真进一步深化印象。

一、SDR模式

1.1、设计代码

以下代码表示在SDR模式下对输入的4位宽并行数据进行并串转换。

module serdes_top(input i_clk ,input i_div_clk ,input i_rst ,input [3 :0] i_par_data ,output o_ser_data

);wire OFB;OSERDESE2 #(.DATA_RATE_OQ ("SDR" ), // DDR, SDR.DATA_RATE_TQ ("DDR" ), // DDR, BUF, SDR.DATA_WIDTH (4 ), // Parallel data width (2-8,10,14).INIT_OQ (1'b0 ), // Initial value of OQ output (1'b0,1'b1).INIT_TQ (1'b0 ), // Initial value of TQ output (1'b0,1'b1).SERDES_MODE ("MASTER" ), // MASTER, SLAVE.SRVAL_OQ (1'b0 ), // OQ output value when SR is used (1'b0,1'b1).SRVAL_TQ (1'b0 ), // TQ output value when SR is used (1'b0,1'b1).TBYTE_CTL ("FALSE" ), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC ("FALSE" ), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH (1 ) // 3-state converter width (1,4))OSERDESE2_inst (.OFB (OFB ), // 1-bit output: Feedback path for data.OQ (o_ser_data ), // 1-bit output: Data path output// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each).SHIFTOUT1 ( ),.SHIFTOUT2 ( ),.TBYTEOUT ( ), // 1-bit output: Byte group tristate.TFB ( ), // 1-bit output: 3-state control.TQ ( ), // 1-bit output: 3-state control.CLK (i_clk ), // 1-bit input: High speed clock.CLKDIV (i_div_clk ), // 1-bit input: Divided clock// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each).D1 (i_par_data[0] ),.D2 (i_par_data[1] ),.D3 (i_par_data[2] ),.D4 (i_par_data[3] ),.D5 (),.D6 (),.D7 (),.D8 (),// .D5 (i_par_data[4] ),// .D6 (i_par_data[5] ),// .D7 (i_par_data[6] ),// .D8 (i_par_data[7] ),.OCE (1'b1 ), // 1-bit input: Output data clock enable.RST (i_rst ), // 1-bit input: Reset// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each).SHIFTIN1 (),.SHIFTIN2 (),// T1 - T4: 1-bit (each) input: Parallel 3-state inputs.T1 (1'b0 ),.T2 (1'b0 ),.T3 (1'b0 ),.T4 (1'b0 ),.TBYTEIN (1'b0 ), // 1-bit input: Byte group tristate.TCE (1'b0 ) // 1-bit input: 3-state clock enable);

1.2、testbench代码

以下为TB文件:

module serdes_sim();localparam P_CLK_PERIOD = 40;reg clk, div_clk , rst;

reg [3 :0] r_din;wire w_ser_dout;always begindiv_clk = 0;#(P_CLK_PERIOD); div_clk = 1;#(P_CLK_PERIOD);

endalways beginclk = 1;#(P_CLK_PERIOD/4); clk = 0;#(P_CLK_PERIOD/4);

endinitial beginrst = 1;#100;@(posedge clk);rst = 0;repeat(200) @(posedge clk);$stop;

endinitial beginr_din = 'd0;data_gen();

endserdes_top serdes_top_u0(.i_clk (clk ),.i_div_clk (div_clk ),.i_rst (rst ),.i_par_data (r_din ),.o_ser_data (w_ser_dout )

);task data_gen();

beginr_din <= 'd0;wait(!rst);repeat(10) @(posedge div_clk);r_din <= ({$random} % 16);forever begin@(posedge div_clk);r_din <= ({$random} % 16);end

end

endtaskendmodule

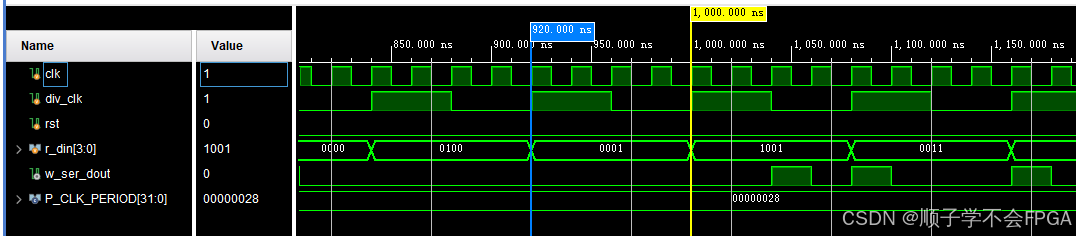

1.3、仿真分析

第一个并行数据为4’b0100,在蓝色刻度线处被采样,黄色刻度线开始输出,但是按照表中输出时延应该是3个CLK后开始输出,这是因为CLK和CLKDIV相位对齐,输出时延可以变化一个CLK,仿真结果显示是4个CLK,相比于表中描述多了一个CLK.

二、DDR模式下

2.1、设计代码

只需要修改位宽,输入D5-D8、以及并串转换模式即可。

module serdes_top(input i_clk ,input i_div_clk ,input i_rst ,input [7 :0] i_par_data ,output o_ser_data

);wire OFB;OSERDESE2 #(.DATA_RATE_OQ ("DDR" ), // DDR, SDR.DATA_RATE_TQ ("DDR" ), // DDR, BUF, SDR.DATA_WIDTH (8 ), // Parallel data width (2-8,10,14).INIT_OQ (1'b0 ), // Initial value of OQ output (1'b0,1'b1).INIT_TQ (1'b0 ), // Initial value of TQ output (1'b0,1'b1).SERDES_MODE ("MASTER" ), // MASTER, SLAVE.SRVAL_OQ (1'b0 ), // OQ output value when SR is used (1'b0,1'b1).SRVAL_TQ (1'b0 ), // TQ output value when SR is used (1'b0,1'b1).TBYTE_CTL ("FALSE" ), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC ("FALSE" ), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH (1 ) // 3-state converter width (1,4))OSERDESE2_inst (.OFB (OFB ), // 1-bit output: Feedback path for data.OQ (o_ser_data ), // 1-bit output: Data path output// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each).SHIFTOUT1 ( ),.SHIFTOUT2 ( ),.TBYTEOUT ( ), // 1-bit output: Byte group tristate.TFB ( ), // 1-bit output: 3-state control.TQ ( ), // 1-bit output: 3-state control.CLK (i_clk ), // 1-bit input: High speed clock.CLKDIV (i_div_clk ), // 1-bit input: Divided clock// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each).D1 (i_par_data[0] ),.D2 (i_par_data[1] ),.D3 (i_par_data[2] ),.D4 (i_par_data[3] ),// .D5 (),// .D6 (),// .D7 (),// .D8 (),.D5 (i_par_data[4] ),.D6 (i_par_data[5] ),.D7 (i_par_data[6] ),.D8 (i_par_data[7] ),.OCE (1'b1 ), // 1-bit input: Output data clock enable.RST (i_rst ), // 1-bit input: Reset// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each).SHIFTIN1 (),.SHIFTIN2 (),// T1 - T4: 1-bit (each) input: Parallel 3-state inputs.T1 (1'b0 ),.T2 (1'b0 ),.T3 (1'b0 ),.T4 (1'b0 ),.TBYTEIN (1'b0 ), // 1-bit input: Byte group tristate.TCE (1'b0 ) // 1-bit input: 3-state clock enable);endmodule

2.2、testbench代码

修改位宽以及产生随机数的大小即可。

module serdes_sim();localparam P_CLK_PERIOD = 40;reg clk, div_clk , rst;

reg [7 :0] r_din;wire w_ser_dout;always begindiv_clk = 0;#(P_CLK_PERIOD); div_clk = 1;#(P_CLK_PERIOD);

endalways beginclk = 1;#(P_CLK_PERIOD/4); clk = 0;#(P_CLK_PERIOD/4);

endinitial beginrst = 1;#100;@(posedge clk);rst = 0;repeat(200) @(posedge clk);$stop;

endinitial beginr_din = 'd0;data_gen();

endserdes_top serdes_top_u0(.i_clk (clk ),.i_div_clk (div_clk ),.i_rst (rst ),.i_par_data (r_din ),.o_ser_data (w_ser_dout )

);task data_gen();

beginr_din <= 'd0;wait(!rst);repeat(10) @(posedge div_clk);r_din <= ({$random} % 256);forever begin@(posedge div_clk);r_din <= ({$random} % 256);end

end

endtaskendmodule

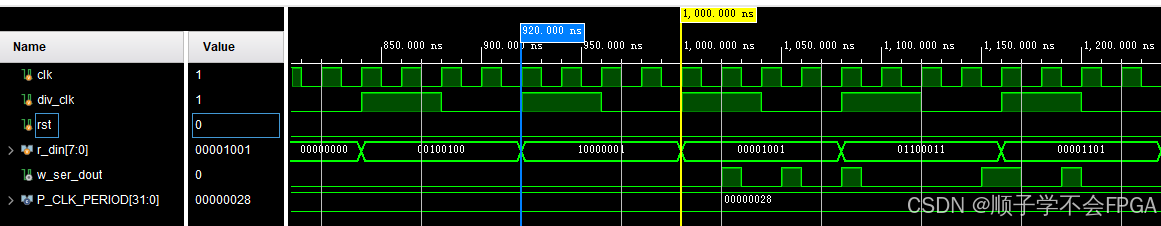

2.3、仿真分析

蓝色刻度线处采样到并行输入数据,黄色刻度线开始输出,延时为4个CLK,与表中描述是一致的。

三、OSERDES2级联

当我们需要对10位或14位并行数据进行并串转换时,需要对OSERDSES2进行级联。本实验以10位输入数据并串转换为例进行说明。

3.1、设计代码

俩个OSERDESE2级联,修改位宽,添加从OSERDESE2,连接SHIFT引脚,修改位宽即可。

module serdes_top(input i_clk ,input i_div_clk ,input i_rst ,input [9 :0] i_par_data ,output o_ser_data

);wire OFB ;

wire w_shiftout1 ;

wire w_shiftout2 ;OSERDESE2 #(.DATA_RATE_OQ ("DDR" ), // DDR, SDR.DATA_RATE_TQ ("DDR" ), // DDR, BUF, SDR.DATA_WIDTH (10 ), // Parallel data width (2-8,10,14).INIT_OQ (1'b0 ), // Initial value of OQ output (1'b0,1'b1).INIT_TQ (1'b0 ), // Initial value of TQ output (1'b0,1'b1).SERDES_MODE ("MASTER" ), // MASTER, SLAVE.SRVAL_OQ (1'b0 ), // OQ output value when SR is used (1'b0,1'b1).SRVAL_TQ (1'b0 ), // TQ output value when SR is used (1'b0,1'b1).TBYTE_CTL ("FALSE" ), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC ("FALSE" ), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH (1 ) // 3-state converter width (1,4))OSERDESE2_inst (.OFB (OFB ), // 1-bit output: Feedback path for data.OQ (o_ser_data ), // 1-bit output: Data path output// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each).SHIFTOUT1 ( ),.SHIFTOUT2 ( ),.TBYTEOUT ( ), // 1-bit output: Byte group tristate.TFB ( ), // 1-bit output: 3-state control.TQ ( ), // 1-bit output: 3-state control.CLK (i_clk ), // 1-bit input: High speed clock.CLKDIV (i_div_clk ), // 1-bit input: Divided clock// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each).D1 (i_par_data[0] ),.D2 (i_par_data[1] ),.D3 (i_par_data[2] ),.D4 (i_par_data[3] ),.D5 (i_par_data[4] ),.D6 (i_par_data[5] ),.D7 (i_par_data[6] ),.D8 (i_par_data[7] ),.OCE (1'b1 ), // 1-bit input: Output data clock enable.RST (i_rst ), // 1-bit input: Reset// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each).SHIFTIN1 (w_shiftout1 ),.SHIFTIN2 (w_shiftout2 ),// T1 - T4: 1-bit (each) input: Parallel 3-state inputs.T1 (1'b0 ),.T2 (1'b0 ),.T3 (1'b0 ),.T4 (1'b0 ),.TBYTEIN (1'b0 ), // 1-bit input: Byte group tristate.TCE (1'b0 ) // 1-bit input: 3-state clock enable);OSERDESE2 #(.DATA_RATE_OQ ("DDR" ), // DDR, SDR.DATA_RATE_TQ ("DDR" ), // DDR, BUF, SDR.DATA_WIDTH (10 ), // Parallel data width (2-8,10,14).INIT_OQ (1'b0 ), // Initial value of OQ output (1'b0,1'b1).INIT_TQ (1'b0 ), // Initial value of TQ output (1'b0,1'b1).SERDES_MODE ("SLAVE" ), // MASTER, SLAVE.SRVAL_OQ (1'b0 ), // OQ output value when SR is used (1'b0,1'b1).SRVAL_TQ (1'b0 ), // TQ output value when SR is used (1'b0,1'b1).TBYTE_CTL ("FALSE" ), // Enable tristate byte operation (FALSE, TRUE).TBYTE_SRC ("FALSE" ), // Tristate byte source (FALSE, TRUE).TRISTATE_WIDTH (1 ) // 3-state converter width (1,4))OSERDESE2_inst1 (.OFB ( ), // 1-bit output: Feedback path for data.OQ ( ), // 1-bit output: Data path output// SHIFTOUT1 / SHIFTOUT2: 1-bit (each) output: Data output expansion (1-bit each).SHIFTOUT1 (w_shiftout1 ),.SHIFTOUT2 (w_shiftout2 ),.TBYTEOUT ( ), // 1-bit output: Byte group tristate.TFB ( ), // 1-bit output: 3-state control.TQ ( ), // 1-bit output: 3-state control.CLK (i_clk ), // 1-bit input: High speed clock.CLKDIV (i_div_clk ), // 1-bit input: Divided clock// D1 - D8: 1-bit (each) input: Parallel data inputs (1-bit each).D1 (),.D2 (),.D3 (i_par_data[8] ),.D4 (i_par_data[9] ),// .D5 (),// .D6 (),// .D7 (),// .D8 (),.D5 (),.D6 (),.D7 (),.D8 (),.OCE (1'b1 ), // 1-bit input: Output data clock enable.RST (i_rst ), // 1-bit input: Reset// SHIFTIN1 / SHIFTIN2: 1-bit (each) input: Data input expansion (1-bit each).SHIFTIN1 (),.SHIFTIN2 (),// T1 - T4: 1-bit (each) input: Parallel 3-state inputs.T1 (1'b0 ),.T2 (1'b0 ),.T3 (1'b0 ),.T4 (1'b0 ),.TBYTEIN (1'b0 ), // 1-bit input: Byte group tristate.TCE (1'b0 ) // 1-bit input: 3-state clock enable);endmodule

3.2、testbench代码

首先需要修改时钟信号,因为输入输出位宽10:1,在DDR模式下,时钟比为5:1,其次修改位宽以及随机数产生即可。

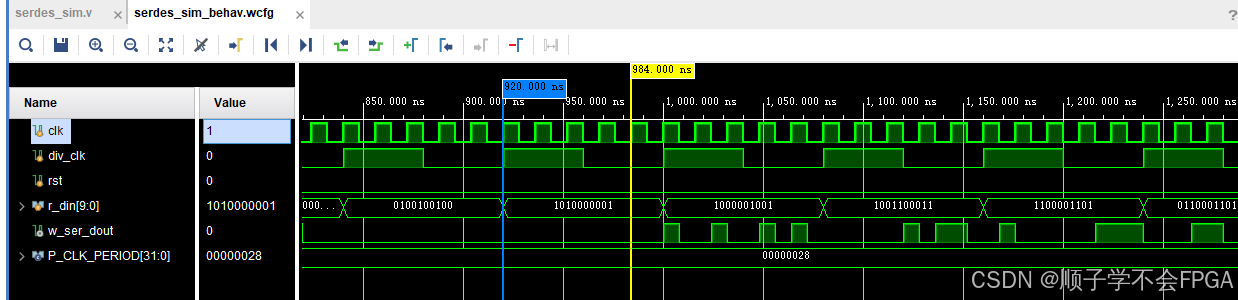

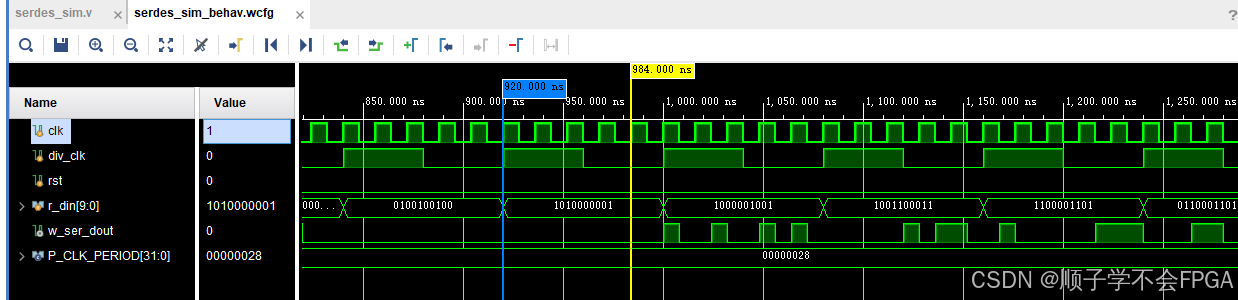

3.3、代码分析

蓝色刻度线处采样到并行输入数据,黄色刻度线开始输出,延时为4个CLK,表中描述延时应当为5个CLK,但此处CLK和DIVCLK是对齐的,所有导致了一个CLK的变化。

相关文章:

SerDes介绍以及原语使用介绍(2)OSERDESE2原语仿真

文章目录 前言一、SDR模式1.1、设计代码1.2、testbench代码1.3、仿真分析 二、DDR模式下2.1、设计代码2.2、testbench代码2.3、仿真分析 三、OSERDES2级联3.1、设计代码3.2、testbench代码3.3、代码分析 前言 上文通过xilinx ug471手册对OSERDESE有了简单的了解,接…...

【稳定检索/投稿优惠】2024年教育、人文发展与艺术国际会议(EHDA 2024)

2024 International Conference on Education, Humanities Development and Arts 2024年教育、人文发展与艺术国际会议 【会议信息】 会议简称:EHDA 2024 大会时间:点击查看 截稿时间:点击查看 大会地点:中国北京 会议官网&#…...

Docker拉取失败,利用 Git将 Docker镜像重新打 Tag 推送到阿里云等其他公有云镜像仓库里

目录 一、开通阿里云容器镜像服务 二、Git配置 三、去DockerHub找镜像 四、编写images.txt文件 五、演示 六、其他注意事项 最近一段时间 Docker 镜像一直是 Pull 不下来的状态,想直连 DockerHub 是几乎不可能的。更糟糕的是,很多原本可靠的国内…...

【区分vue2和vue3下的element UI Breadcrumb 面包屑组件,分别详细介绍属性,事件,方法如何使用,并举例】

在 Vue 2 中,Element UI 提供了 el-breadcrumb 面包屑组件,而在 Vue 3 中,Element UI 的官方版本并没有直接更新以支持 Vue 3,但有一个类似的库叫做 Element Plus,它是为 Vue 3 设计的。 Vue 2 Element UI 在 Vue 2…...

gdb调试命令大全

基本命令 #gdb test test是要调试的程序,由gcc test.c -g -o test生成。进入后提示符变为(gdb) 。 start : 指令会执行程序至main() 主函数的起始位置,即在main() 函数的第一行语句处停止执行(该行代码尚未执行) cont…...

ESP32之arduino环境安装及点灯

目录 前言 前两天安装了VScode,奈何资源找的困难,于是咨询淘宝客服,他说arduino用的多,资源多.然后就安装了a…...

查看VUE中安装包依赖的版本号

查看VUE中安装包依赖的版本号 全部依赖包版本查看某个依赖的例:查看stompjs 应用命令npm ls stompjs 全部依赖包版本 使用npm命令 使用 npm ls 命令可以列出项目中所有已安装的依赖包及其版本。 使用 npm list --depth1 命令可以列出项目中直接依赖的包及其版本&a…...

博途通讯笔记1:1200与1200之间S7通讯

目录 一、添加子网连接二、创建PUT GET三、各个参数的意义 一、添加子网连接 二、创建PUT GET 三、各个参数的意义...

)

Kafka搭建(集群版)

Kafka单机版 部署前提 VMware环境 : 两台centos系统 Jdk包:jdk-8u202-linux-x64.tar.gz Kafka包:kafka_2.12-3.5.0.tgz Zookeeper包:apache-zookeeper-3.7.2-bin.tar.gz 百度网盘自取: 链接: https://pan.baidu.com/s/11EWuhBoSmH3musd_3Rgodw?pwde32t 提取码: e32t Kafka搭建…...

【康复学习--LeetCode每日一题】3115. 质数的最大距离

题目: 给你一个整数数组 nums。 返回两个(不一定不同的)质数在 nums 中 下标 的 最大距离。 示例 1: 输入: nums [4,2,9,5,3] 输出: 3 解释: nums[1]、nums[3] 和 nums[4] 是质数。因此答案是…...

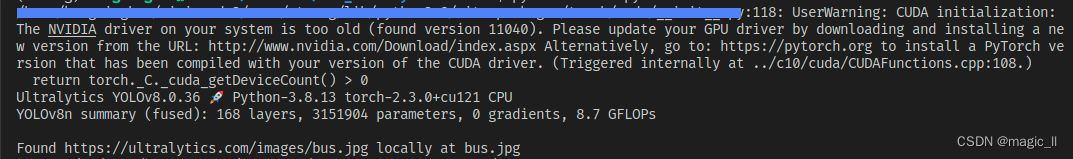

【yolov8系列】ubuntu上yolov8的开启训练的简单记录

前言 yolov8的广泛使用,拉取yolov8源码工程,然后配置环境后直接运行,初步验证自己数据的检测效果,在数据集准备OK的情况下 需要信手拈来,以保证开发过程的高效进行。 本篇博客更注意为了方便自己使用时参考。顺便也记录…...

Scala学习笔记15: 文件和正则表达式

目录 第十五章 文件和正则表达式1- 读取行2- 从URL或者其它源读取3- 写入文本文件4- 序列化5- 正则表达式6- 正则表达式验证输入数据格式end 第十五章 文件和正则表达式 1- 读取行 在Scala中读取文件中的行可以通过不同的方法实现 ; 一种常见的方法是使用 scala.io.Source 对…...

外卖员面试现状

说明: 以下身份角色用符号代替 # 面试官 $ 求职者 # 看了您的简历你有两年半的送外卖经验,可以简单说一下您平时是怎么送外卖的吗? $ 我首先在平台接单然后到店里取餐,取到餐后到顾客留下的地址,再通知顾客取餐 # 你们也用电动…...

异步加载与动态加载

异步加载和动态加载在概念上有相似之处,但并不完全等同。 异步加载(Asynchronous Loading)通常指的是不阻塞后续代码执行或页面渲染的数据或资源加载方式。在Web开发中,异步加载常用于从服务器获取数据,而不需要用户等…...

MUNIK解读ISO26262--什么是DFA

我们在学习功能安全过程中,经常会听到很多安全分析方法,有我们熟知的FMEA(Failure Modes Effects Analysis)和FTA(Fault Tree Analysis)还有功能安全产品设计中几乎绕不开的FMEDA(Failure Modes Effects and Diagnostic Analysis),相比于它们…...

启动spring boot项目停止 提示80端口已经被占用

可能的情况: 检查并结束占用进程: 首先,你需要确定哪个进程正在使用80端口。在Windows上,可以通过命令行输入netstat -ano | findstr LISTENING | findstr :80来查看80端口的PID,然后在任务管理器中结束该进程。在...

SOLIDWORKS分期许可(订阅形式),降低前期的投入成本!

SOLIDWORKS 分期许可使您能够降低前期软件成本,同时提供对 SOLIDWORKS 新版本和升级程序的即时访问,以及在每个期限结束时调整产品的灵活性,帮助您跟上市场需求和竞争压力的步伐。 目 录: ★ 1 什么是SOLIDWORKS分期许可 ★ 2 …...

)

详细分析Spring Boot 数据源配置的基本知识(附配置)

目录 前言1. 基本知识2. 模版3. 实战经验前言 对于Java的基本知识推荐阅读: java框架 零基础从入门到精通的学习路线 附开源项目面经等(超全)【Java项目】实战CRUD的功能整理(持续更新)1. 基本知识 包括数据源的概念、连接池的作用、多数据源的实现与管理、Druid 连接池…...

9轴IMU ICM-20948模块SPI接口调试)

海思SD3403/SS928V100开发(15)9轴IMU ICM-20948模块SPI接口调试

1.前言 芯片平台: 海思SD3403/SS928V100 操作系统平台: Ubuntu20.04.05【自己移植】 9轴IMU模块:ICM-20948 通讯接口: SPI 模块datasheet手册: https://download.csdn.net/download/jzwjzw19900922/89517096 2. 调试记录 2.1 pinmux配置 #spi0 bspmm 0x0102F01D8 …...

大力出奇迹:大语言模型的崛起与挑战

随着人工智能(AI)技术的迅猛发展,特别是在自然语言处理(NLP)领域,大语言模型(LLM)的出现与应用,彻底改变了我们与机器互动的方式。本文将探讨ChatGPT等大语言模型的定义、…...

Qwen3-0.6B快速调用:LangChain助力,轻松玩转大模型

Qwen3-0.6B快速调用:LangChain助力,轻松玩转大模型 1. 快速了解Qwen3-0.6B Qwen3-0.6B是阿里巴巴开源的通义千问系列最新一代语言模型,拥有6亿参数规模。相比前代模型,它在推理能力、指令遵循和多语言支持方面都有显著提升。这个…...

网盘直链获取工具:高效解析与实用指南

网盘直链获取工具:高效解析与实用指南 【免费下载链接】Online-disk-direct-link-download-assistant 可以获取网盘文件真实下载地址。基于【网盘直链下载助手】修改(改自6.1.4版本) ,自用,去推广,无需输入…...

Duix-Avatar全离线数字人创作平台深度指南:从部署到高级应用

Duix-Avatar全离线数字人创作平台深度指南:从部署到高级应用 【免费下载链接】Duix-Avatar 项目地址: https://gitcode.com/GitHub_Trending/he/Duix-Avatar 价值解析:Duix-Avatar的SWOT战略分析 优势(Strengths) 全栈本地化架构:所…...

教育软件控制突破:JiYuTrainer的内核级反控制解决方案

教育软件控制突破:JiYuTrainer的内核级反控制解决方案 【免费下载链接】JiYuTrainer 极域电子教室防控制软件, StudenMain.exe 破解 项目地址: https://gitcode.com/gh_mirrors/ji/JiYuTrainer 副标题:技术原理、实现路径与教育场景应用指南 一、…...

如何在PC上完美运行PS3游戏:RPCS3模拟器终极指南

如何在PC上完美运行PS3游戏:RPCS3模拟器终极指南 【免费下载链接】rpcs3 PS3 emulator/debugger 项目地址: https://gitcode.com/GitHub_Trending/rp/rpcs3 你是否曾经想过在电脑上重温那些经典的PS3游戏?或者想要体验那些只能在PlayStation 3上玩…...

3分钟上手!FrankMocap让普通摄像头变身专业动捕设备

3分钟上手!FrankMocap让普通摄像头变身专业动捕设备 【免费下载链接】frankmocap A Strong and Easy-to-use Single View 3D HandBody Pose Estimator 项目地址: https://gitcode.com/gh_mirrors/fr/frankmocap 在数字内容创作与交互设计领域,3D动…...

Qwen2-VL-2B-Instruct模型压缩实战:使用量化工具减小部署体积与加速推理

Qwen2-VL-2B-Instruct模型压缩实战:使用量化工具减小部署体积与加速推理 最近在折腾一个边缘设备上的视觉项目,用上了Qwen2-VL-2B-Instruct这个多模态模型。模型效果确实不错,但原始大小接近8GB,推理速度也慢,在资源有…...

LLaMA-Factory推理性能优化指南:如何用vLLM和量化技术提升3倍吞吐量

LLaMA-Factory推理性能优化实战:从参数调优到量化部署 当你的LLaMA-Factory模型推理请求从每秒10次飙升到1000次时,服务器突然开始报警——显存爆满、响应延迟激增、API错误率直线上升。这不是灾难片的开场,而是每个AI工程师终将面对的性能瓶…...

Millennium Steam Patcher架构解析:模块化主题引擎与Hook系统的深度实现

Millennium Steam Patcher架构解析:模块化主题引擎与Hook系统的深度实现 【免费下载链接】millennium-steam-patcher Apply themes/customize Steam after the 2023-04-27 Chromium UI update https://discord.gg/MXMWEQKgJF 项目地址: https://gitcode.com/gh_mi…...

Youtu-VL-4B-Instruct多模态模型部署教程:预防磁盘空间不足的5个实用技巧

Youtu-VL-4B-Instruct多模态模型部署教程:预防磁盘空间不足的5个实用技巧 1. 引言:多模态模型部署的磁盘挑战 部署大型多模态模型时,磁盘空间管理往往是第一个需要面对的挑战。Youtu-VL-4B-Instruct作为腾讯优图实验室开发的视觉语言模型&a…...