Xilinx AXI VIP使用教程

AXI接口虽然经常使用,很多同学可能并不清楚Vivado里面也集成了AXI的Verification IP,可以当做AXI的master、pass through和slave,本次内容我们看下AXI VIP当作master时如何使用。

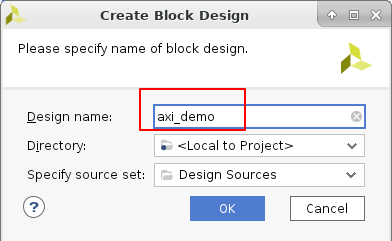

新建Vivado工程,并新建block design,命名为:axi_demo

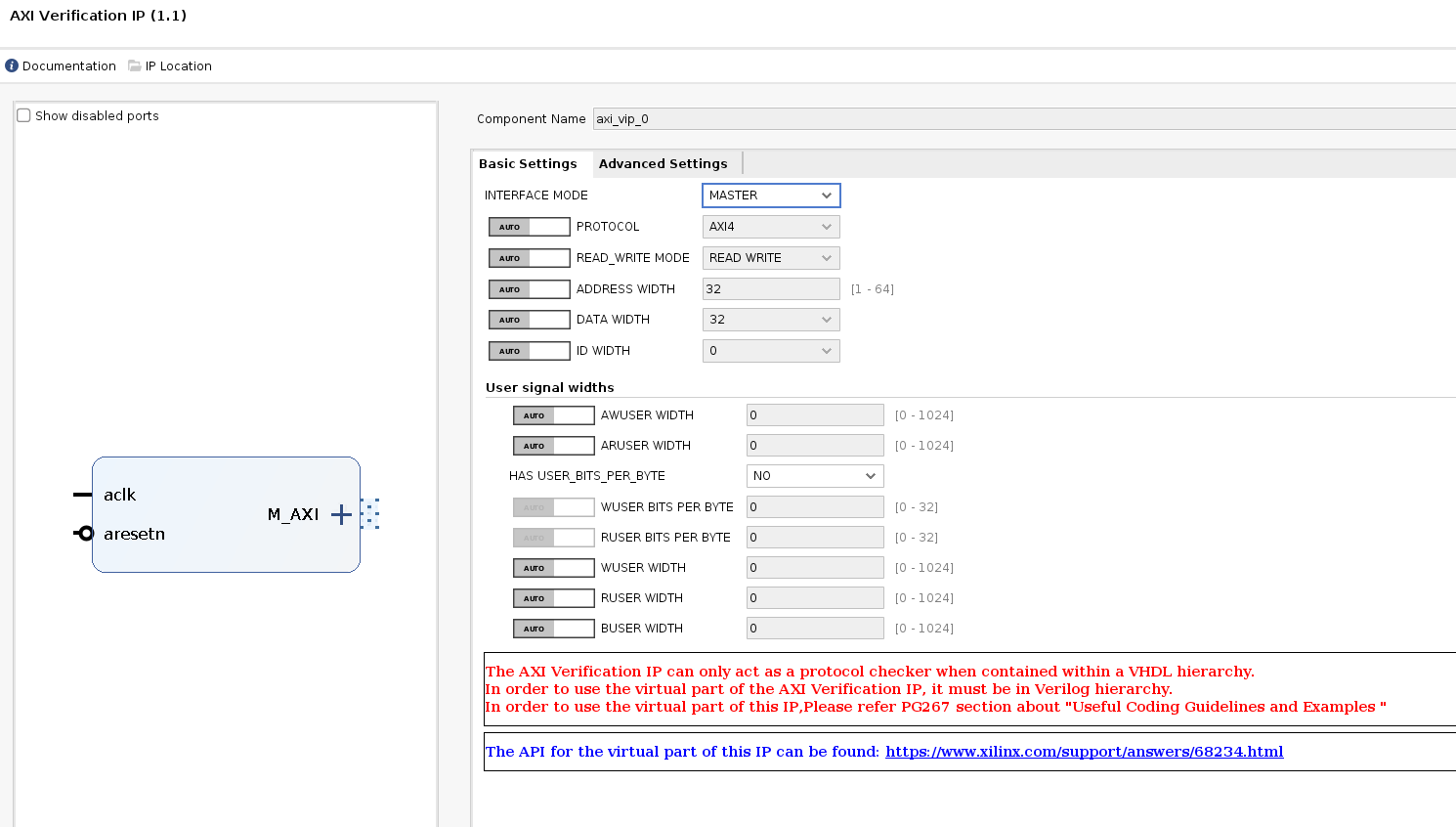

新建axi vip,参数设置如下,第一个参数设置为Master,其他都保持默认,当然如果可以根据自己的实际需求作改动,比如id位宽,数据位宽等等。

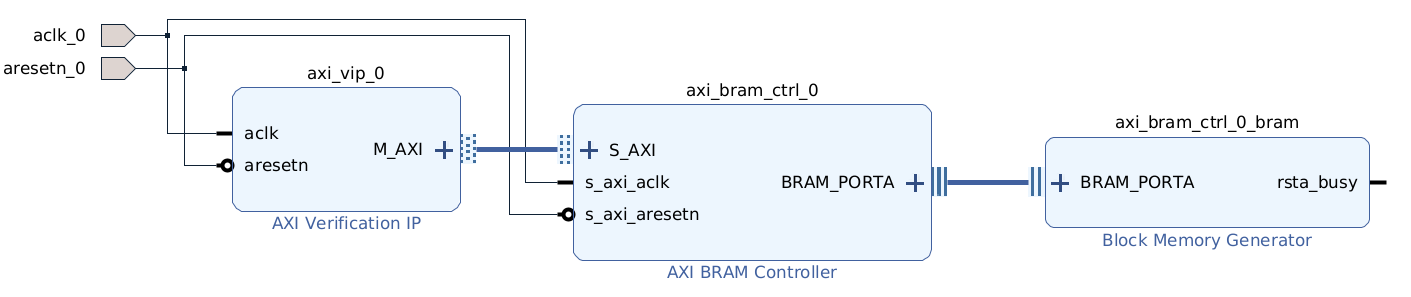

再添加AXI BRAM Controller和Block Memory Generator:

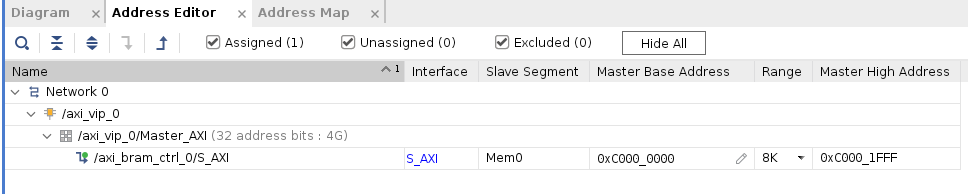

地址分配如下:0xc000_0000

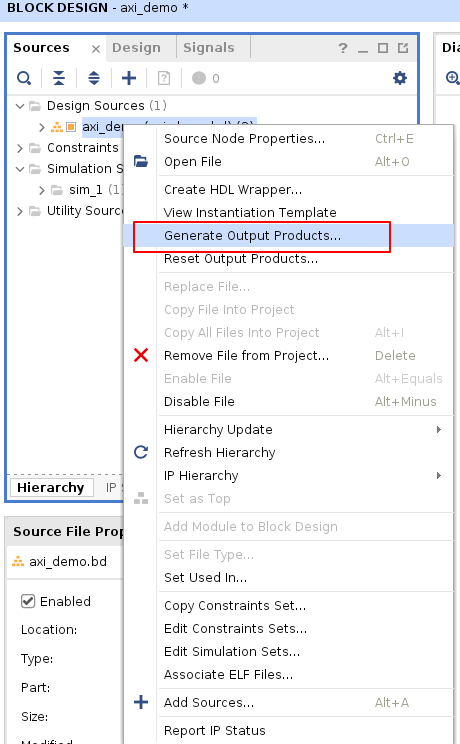

生成ip的各种文件:

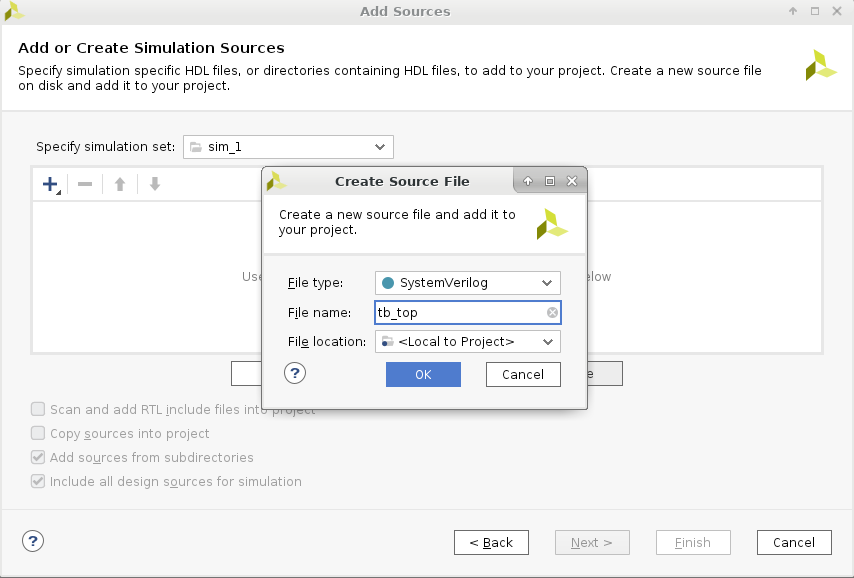

新建仿真的tb_top文件,需要注意,文件类型是system verilog。

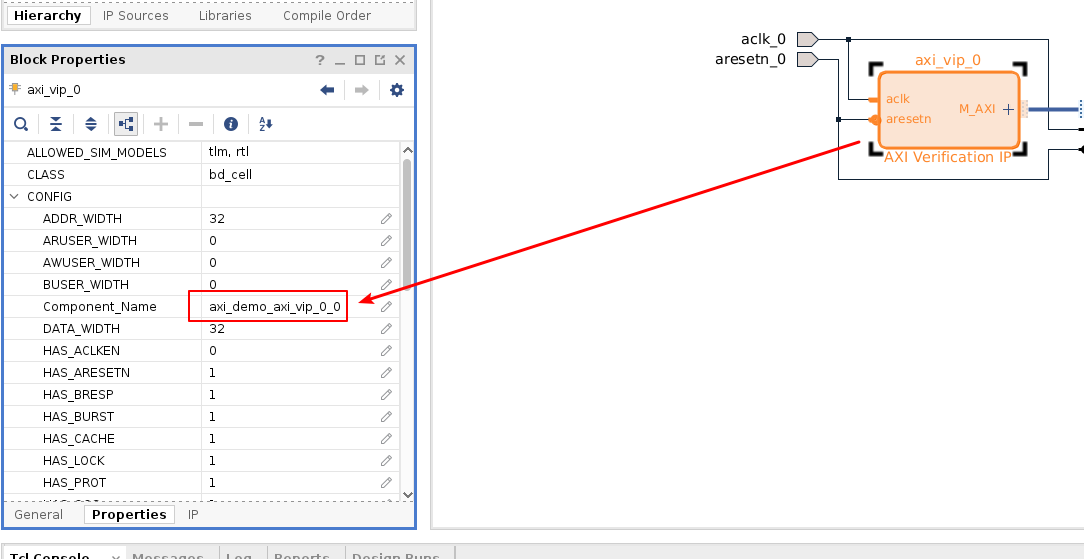

仿真代码放到文章末尾,代码中中导入的axi_demo_axi_vip_0_0_pkg,就是下面axi vip的component_name再加上后缀_pkg,后面的mst_agent也是component_name加上后缀 _mst_t

import axi_demo_axi_vip_0_0_pkg::*;

axi_demo_axi_vip_0_0_mst_t mst_agent;

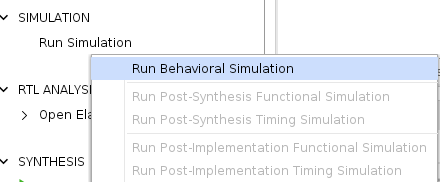

运行仿真:

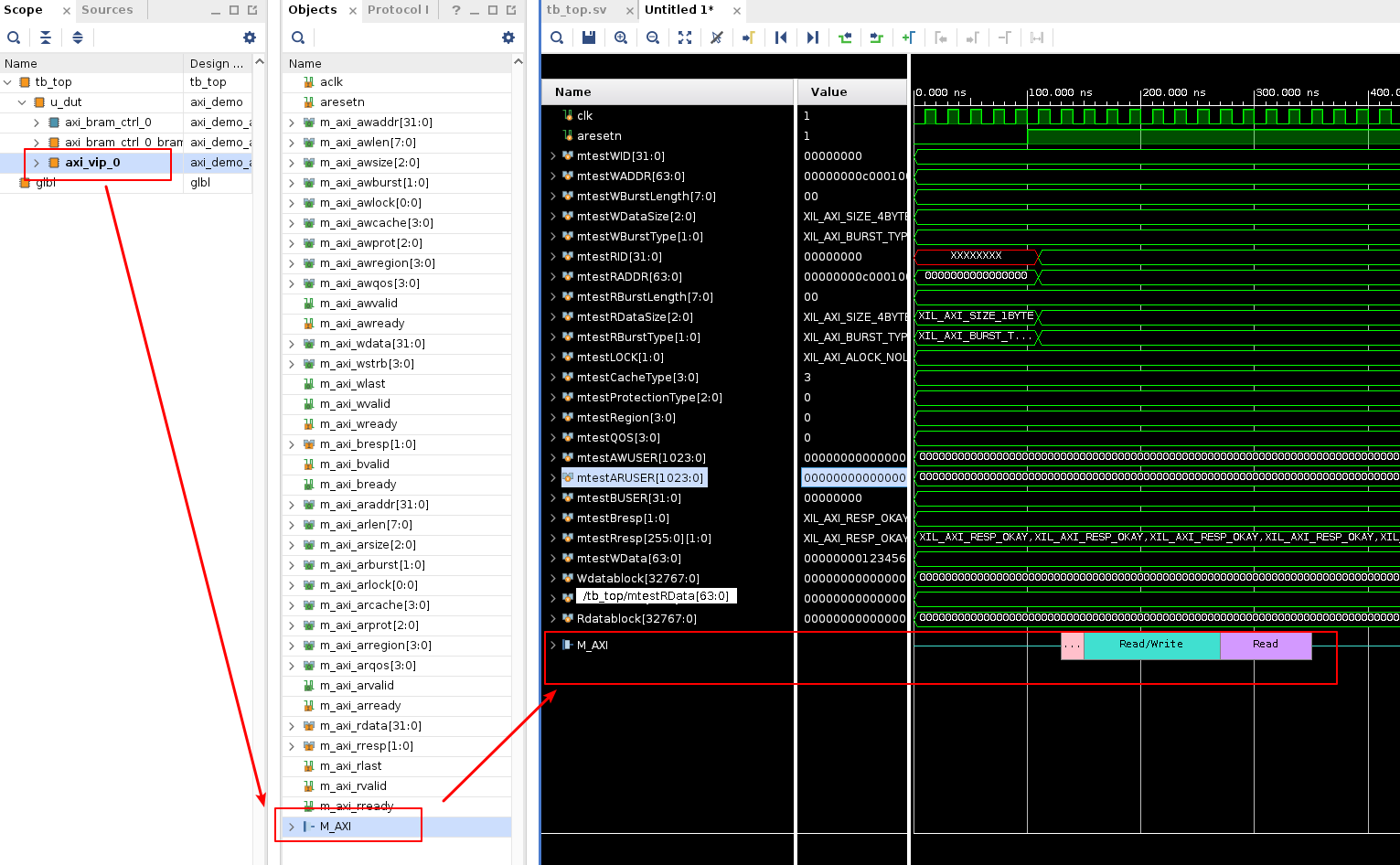

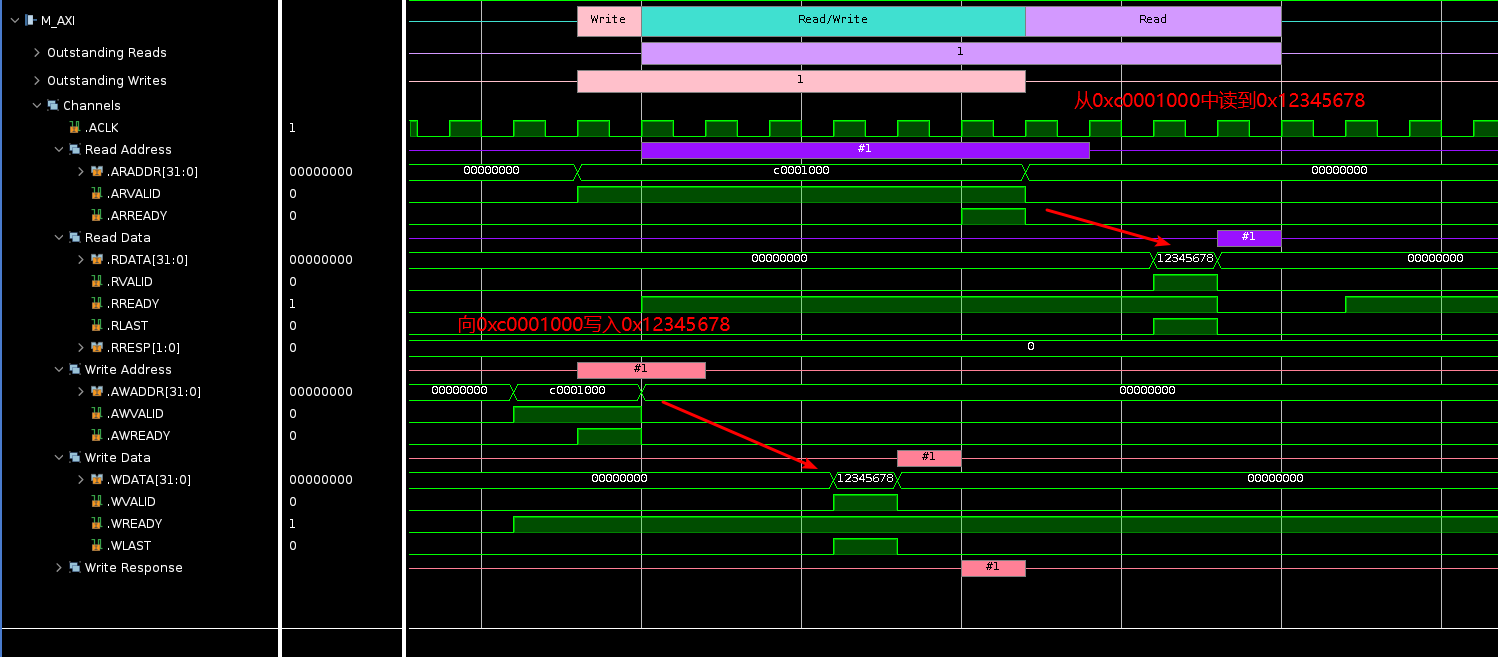

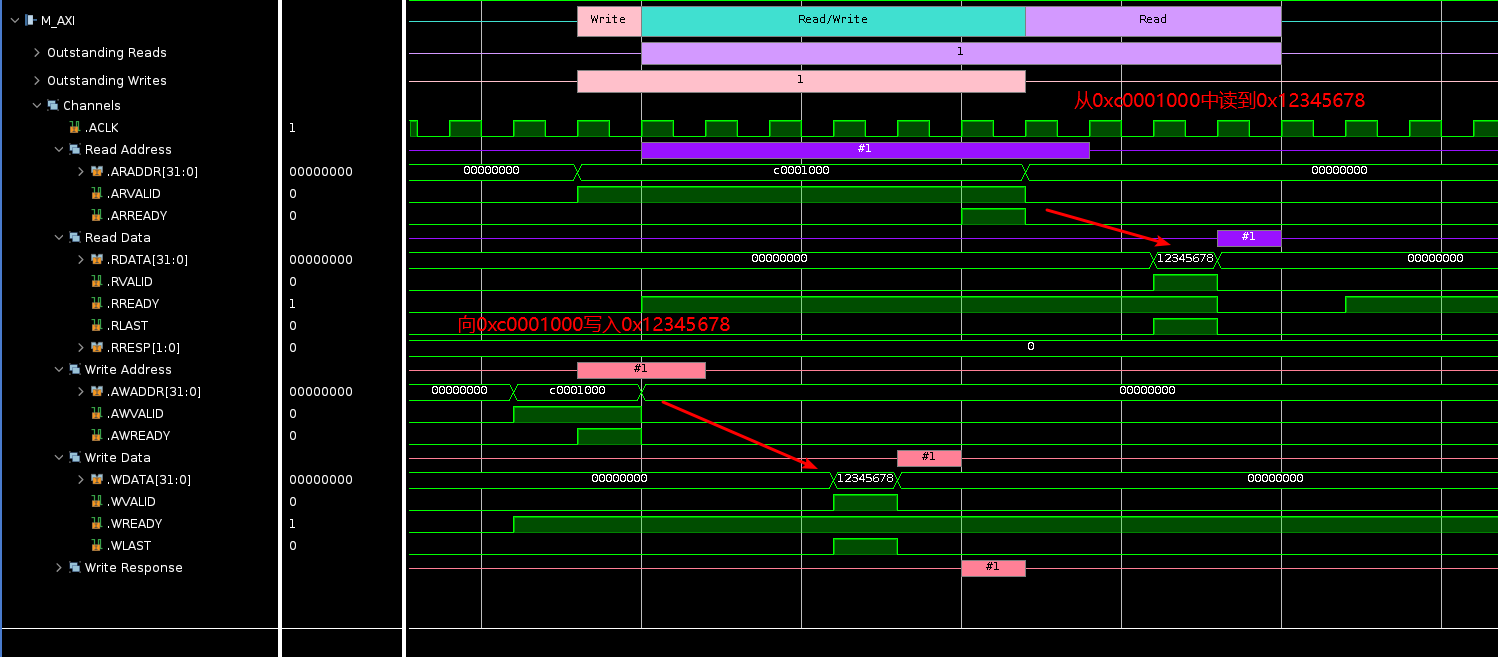

将axi vip的M-AXI添加到波形窗口中:

可以看到,我们一开始向地址0xc0001000写入0x12345678,又发起一次读操作,可以将该数据读出。

有同学可能习惯用vcs来仿真,下篇文章我们再用vcs+verdi来仿真vivado的axi vip。

关注公众号:傅里叶的猫

可以获取更多FPGA相关的博客和内容。

`timescale 1ns / 1psimport axi_vip_pkg::*;

import axi_demo_axi_vip_0_0_pkg::*;module tb_top();bit clk;

bit aresetn;//used in API and parital randomization for transaction generation and data read back from driver

axi_transaction wr_transaction; // Write transaction

axi_transaction rd_transaction; // Read transactionxil_axi_uint mtestWID; // Write ID

xil_axi_ulong mtestWADDR; // Write ADDR

xil_axi_len_t mtestWBurstLength; // Write Burst Length

xil_axi_size_t mtestWDataSize; // Write SIZE

xil_axi_burst_t mtestWBurstType; // Write Burst Type

xil_axi_uint mtestRID; // Read ID

xil_axi_ulong mtestRADDR; // Read ADDR

xil_axi_len_t mtestRBurstLength; // Read Burst Length

xil_axi_size_t mtestRDataSize; // Read SIZE

xil_axi_burst_t mtestRBurstType; // Read Burst Type

xil_axi_lock_t mtestLOCK; // LOCK value for WRITE/READ_BURST transaction

xil_axi_cache_t mtestCacheType = 3; // Cache Type value for WRITE/READ_BURST transaction

xil_axi_prot_t mtestProtectionType = 3'b000; // Protection Type value for WRITE/READ_BURST transaction

xil_axi_region_t mtestRegion = 4'b000; // Region value for WRITE/READ_BURST transaction

xil_axi_qos_t mtestQOS = 4'b000; // QOS value for WRITE/READ_BURST transaction

xil_axi_data_beat dbeat; // Data beat value for WRITE/READ_BURST transaction

xil_axi_user_beat usrbeat; // User beat value for WRITE/READ_BURST transaction

xil_axi_data_beat [255:0] mtestWUSER; // Wuser value for WRITE/READ_BURST transaction

xil_axi_data_beat mtestAWUSER = 'h0; // Awuser value for WRITE/READ_BURST transaction

xil_axi_data_beat mtestARUSER = 0; // Aruser value for WRITE/READ_BURST transaction

xil_axi_data_beat [255:0] mtestRUSER; // Ruser value for WRITE/READ_BURST transaction

xil_axi_uint mtestBUSER = 0; // Buser value for WRITE/READ_BURST transaction

xil_axi_resp_t mtestBresp; // Bresp value for WRITE/READ_BURST transaction

xil_axi_resp_t[255:0] mtestRresp; // Rresp value for WRITE/READ_BURST transactionbit [63:0] mtestWData; // Write Data

bit[8*4096-1:0] Wdatablock; // Write data block

xil_axi_data_beat Wdatabeat[]; // Write data beatsbit [63:0] mtestRData; // Read Data

bit[8*4096-1:0] Rdatablock; // Read data block

xil_axi_data_beat Rdatabeat[]; // Read data beatsinitial beginaresetn = 1'b0;clk = 1'b0;#100ns;aresetn = 1'b1;endalways #10 clk <= ~clk;axi_demo u_dut(.aclk_0 (clk ),.aresetn_0 (aresetn )

);axi_demo_axi_vip_0_0_mst_t mst_agent;initial beginmst_agent = new("master vip agent",u_dut.axi_vip_0.inst.IF);mst_agent.start_master(); // mst_agent start to runmtestWID = $urandom_range(0,(1<<(0)-1)); mtestWADDR = 'hc000_1000;//$urandom_range(0,(1<<(32)-1));mtestWBurstLength = 0;mtestWDataSize = xil_axi_size_t'(xil_clog2((32)/8));mtestWBurstType = XIL_AXI_BURST_TYPE_INCR;mtestWData = 'h12345678;//$urandom();$display("mtestWDataSize = %d", mtestWDataSize);//single write transaction filled in user inputs through API single_write_transaction_api("single write with api",.id(mtestWID),.addr(mtestWADDR),.len(mtestWBurstLength), .size(mtestWDataSize),.burst(mtestWBurstType),.wuser(mtestWUSER),.awuser(mtestAWUSER), .data(mtestWData));mtestRID = $urandom_range(0,(1<<(0)-1));mtestRADDR = mtestWADDR;mtestRBurstLength = 0;mtestRDataSize = xil_axi_size_t'(xil_clog2((32)/8)); mtestRBurstType = XIL_AXI_BURST_TYPE_INCR;$display("mtestRDataSize = %d", mtestRDataSize);//single read transaction filled in user inputs through API single_read_transaction_api("single read with api",.id(mtestRID),.addr(mtestRADDR),.len(mtestRBurstLength), .size(mtestRDataSize),.burst(mtestRBurstType));

endtask automatic single_write_transaction_api ( input string name ="single_write",input xil_axi_uint id =0, input xil_axi_ulong addr =0,input xil_axi_len_t len =0, input xil_axi_size_t size =xil_axi_size_t'(xil_clog2((32)/8)),input xil_axi_burst_t burst =XIL_AXI_BURST_TYPE_INCR,input xil_axi_lock_t lock = XIL_AXI_ALOCK_NOLOCK,input xil_axi_cache_t cache =3,input xil_axi_prot_t prot =0,input xil_axi_region_t region =0,input xil_axi_qos_t qos =0,input xil_axi_data_beat [255:0] wuser =0, input xil_axi_data_beat awuser =0,input bit [63:0] data =0);axi_transaction wr_trans;$display("single_write_transaction_api size = %d", size);wr_trans = mst_agent.wr_driver.create_transaction(name);wr_trans.set_write_cmd(addr,burst,id,len,size);wr_trans.set_prot(prot);wr_trans.set_lock(lock);wr_trans.set_cache(cache);wr_trans.set_region(region);wr_trans.set_qos(qos);wr_trans.set_data_block(data);mst_agent.wr_driver.send(wr_trans); endtask : single_write_transaction_api task automatic single_read_transaction_api ( input string name ="single_read",input xil_axi_uint id =0, input xil_axi_ulong addr =0,input xil_axi_len_t len =0, input xil_axi_size_t size =xil_axi_size_t'(xil_clog2((32)/8)),input xil_axi_burst_t burst =XIL_AXI_BURST_TYPE_INCR,input xil_axi_lock_t lock =XIL_AXI_ALOCK_NOLOCK ,input xil_axi_cache_t cache =3,input xil_axi_prot_t prot =0,input xil_axi_region_t region =0,input xil_axi_qos_t qos =0,input xil_axi_data_beat aruser =0);axi_transaction rd_trans;$display("single_read_transaction_api size = %d", size);rd_trans = mst_agent.rd_driver.create_transaction(name);rd_trans.set_read_cmd(addr,burst,id,len,size);rd_trans.set_prot(prot);rd_trans.set_lock(lock);rd_trans.set_cache(cache);rd_trans.set_region(region);rd_trans.set_qos(qos);mst_agent.rd_driver.send(rd_trans); endtask : single_read_transaction_apiendmodule相关文章:

Xilinx AXI VIP使用教程

AXI接口虽然经常使用,很多同学可能并不清楚Vivado里面也集成了AXI的Verification IP,可以当做AXI的master、pass through和slave,本次内容我们看下AXI VIP当作master时如何使用。 新建Vivado工程,并新建block design,命…...

mysql主主架构搭建,删库恢复

mysql主主架构搭建,删库恢复 搭建mysql主主架构环境信息安装msql服务mysql1mysql2设置mysql2同步mysql1设置mysql1同步mysql2授权测试用账户 安装配置keepalivedmysql1检查脚本mysql2检查脚本 备份策略mysqldump全量备份mysqldump增量备份数据库目录全量备份 删除my…...

pythonweek1

引言 做任何事情都要脚踏实地,虽然大一上已经学习了python的基础语法,大一下也学习了C加加中的类与对象,但是自我觉得基础还不太扎实,又害怕有什么遗漏,所以就花时间重新学习了python的基础,学习Python的基…...

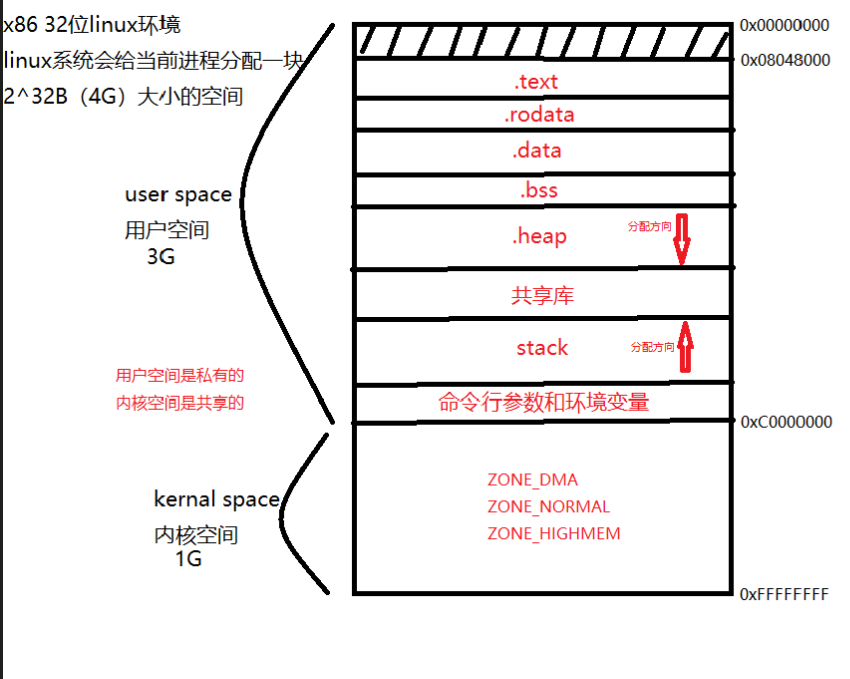

进程虚拟地址空间区域划分

目录 图示 详解 代码段 备注:x86 32位linux环境下,进程虚拟地址空间区域划分 图示 详解 用户空间 用于存储用户进程代码和数据,只能由用户进程访问 内核空间 用于存储操作系统内核代码和数据,只能由操作系统内核访问 text t…...

OpenAI Code Interpreter 的开源实现:GPT Code UI

本篇文章聊聊 OpenAI Code Interpreter 的一众开源实现方案中,获得较多支持者,但暂时还比较早期的项目:GPT Code UI。 写在前面 这篇文章本该更早的时候发布,但是 LLaMA2 发布后实在心痒难忍,于是就拖了一阵。结合 L…...

macOS Ventura 13.5 (22G74) 正式版发布,ISO、IPSW、PKG 下载

macOS Ventura 13.5 (22G74) 正式版发布,ISO、IPSW、PKG 下载 本站下载的 macOS Ventura 软件包,既可以拖拽到 Applications(应用程序)下直接安装,也可以制作启动 U 盘安装,或者在虚拟机中启动安装。另外也…...

Electron 主进程和渲染进程传值及窗口间传值

1 渲染进程调用主进程得方法 下面是渲染进程得代码: let { ipcRenderer} require( electron ); ipcRenderer.send( xxx ); //渲染进程中调用 下面是主进程得代码: var { ipcMain } require( electron ); ipcMain.on("xxx",function () { } )...

C#设计模式之---建造者模式

建造者模式(Builder Pattern) 建造者模式(Builder Pattern)是将一个复杂对象的构建与它的表示分离,使得同样的构建过程可以创建不同的表示。建造者模式使得建造代码与表示代码的分离,可以使客户端不必知道…...

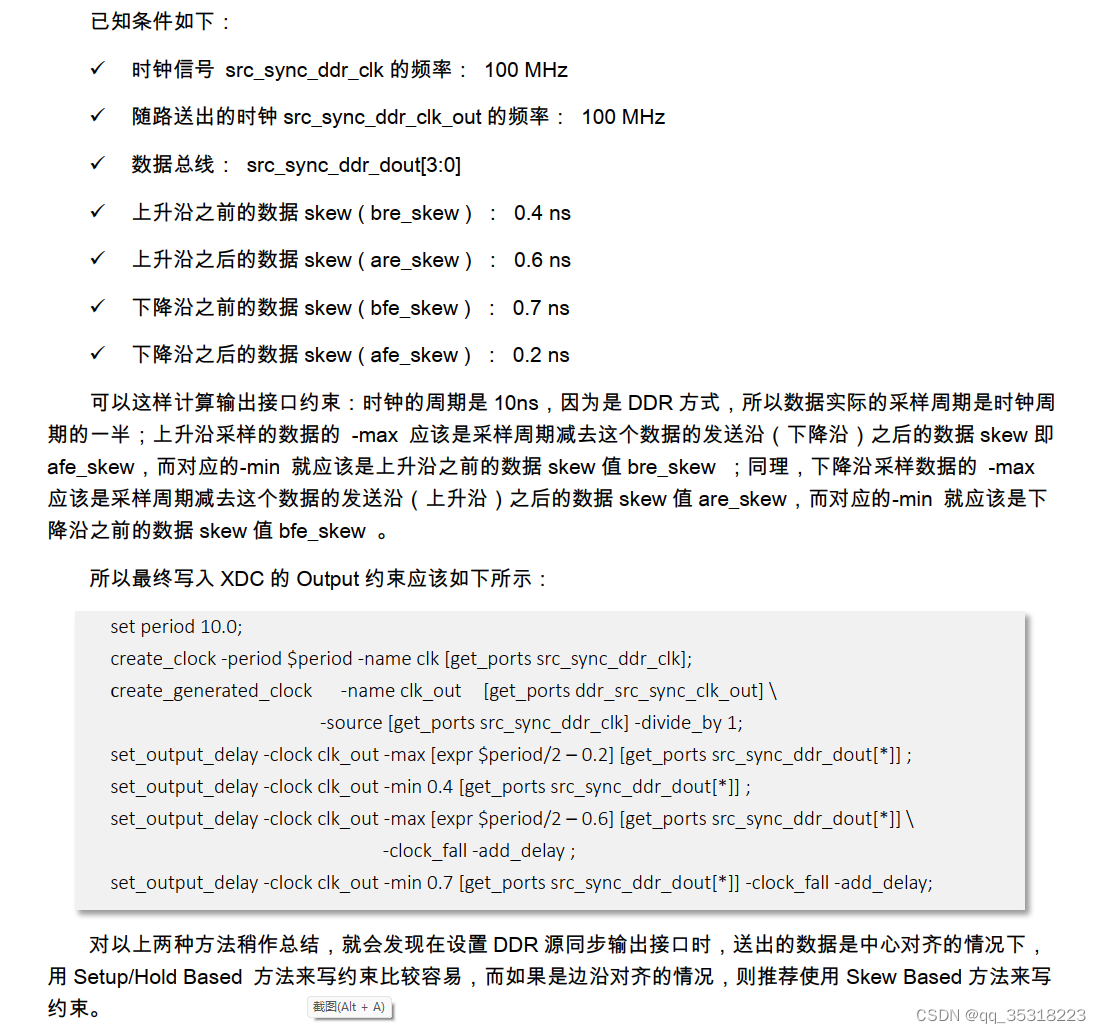

output delay 约束

output delay 约束 一、output delay约束概述二、output delay约束系统同步三、output delay约束源同步 一、output delay约束概述 特别注意:在源同步接口中,定义接口约束之前,需要用create_generated_clock 先定义送出的随路时钟。 二、out…...

html2Canvas+jsPDF 下载PDF 遇到跨域的对象存储的图片无法显示

一、问题原因 对象存储的域名和你网址的域名不一样,此时用Canvas相关插件 将DOM元素转化为PDF,就会出现跨域错误。 二、解决办法 两步 1. 图片元素上设置属性 crossorigin"anonymous" 支持原生img和eleme组件 2. 存储桶设置资源跨域访问…...

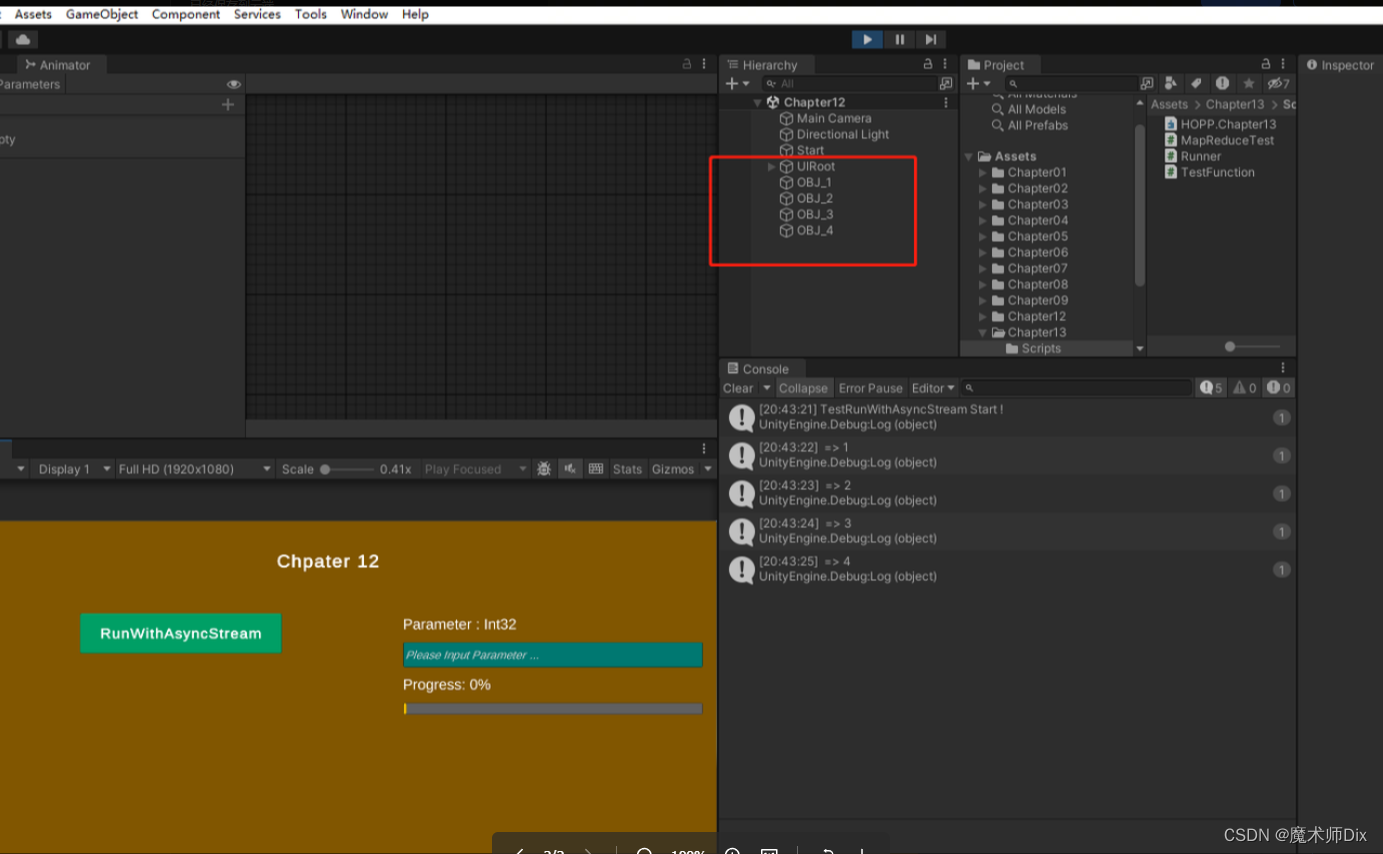

【C#】并行编程实战:异步流

本来这章该讲的是 ASP .NET Core 中的 IIS 和 Kestrel ,但是我看了下这个是给服务器用的。而我只是个 Unity 客户端程序,对于服务器的了解趋近于零。 鉴于我对服务器知识和需求的匮乏,这里就不讲原书(大部分)内容了。本…...

在家下载论文使用哪些论文下载工具比较好

在家下载论文如果不借助论文下载工具是非常艰难的事情,因为很多查找下载论文的数据库都是需要账号权限才可使用的。 例如,我们查找中文论文常用的知网、万方等数据库以及众多国外论文数据库。 在家下载知网、万方数据库论文可用下面的方法:…...

【LeetCode 算法】Handling Sum Queries After Update 更新数组后处理求和查询-Segment Tree

文章目录 Handling Sum Queries After Update 更新数组后处理求和查询问题描述:分析代码线段树 Tag Handling Sum Queries After Update 更新数组后处理求和查询 问题描述: 给你两个下标从 0 开始的数组 n u m s 1 和 n u m s 2 nums1 和 nums2 nums1…...

基于Linux操作系统中的MySQL数据库SQL语句(三十一)

MySQL数据库SQL语句 目录 一、SQL语句类型 1、DDL 2、DML 3、DCL 4、DQL 二、数据库操作 1、查看 2、创建 2.1、默认字符集 2.2、指定字符集 3、进入 4、删除 5、更改 6、练习 三、数据表操作 (一)数据类型 1、数值类型 1.1、TINYINT …...

)

【Matlab】基于BP神经网络的数据回归预测新数据(Excel可直接替换数据)

【Matlab】基于BP神经网络的数据回归预测新数据(Excel可直接替换数据) 1.模型原理2.数学公式3.文件结构4.Excel数据5.分块代码5.1 main.m5.2 NewData.m6.完整代码6.1 main.m6.2 NewData.m7.运行结果1.模型原理 基于BP神经网络的数据回归预测是一种常见的机器学习方法,用于处…...

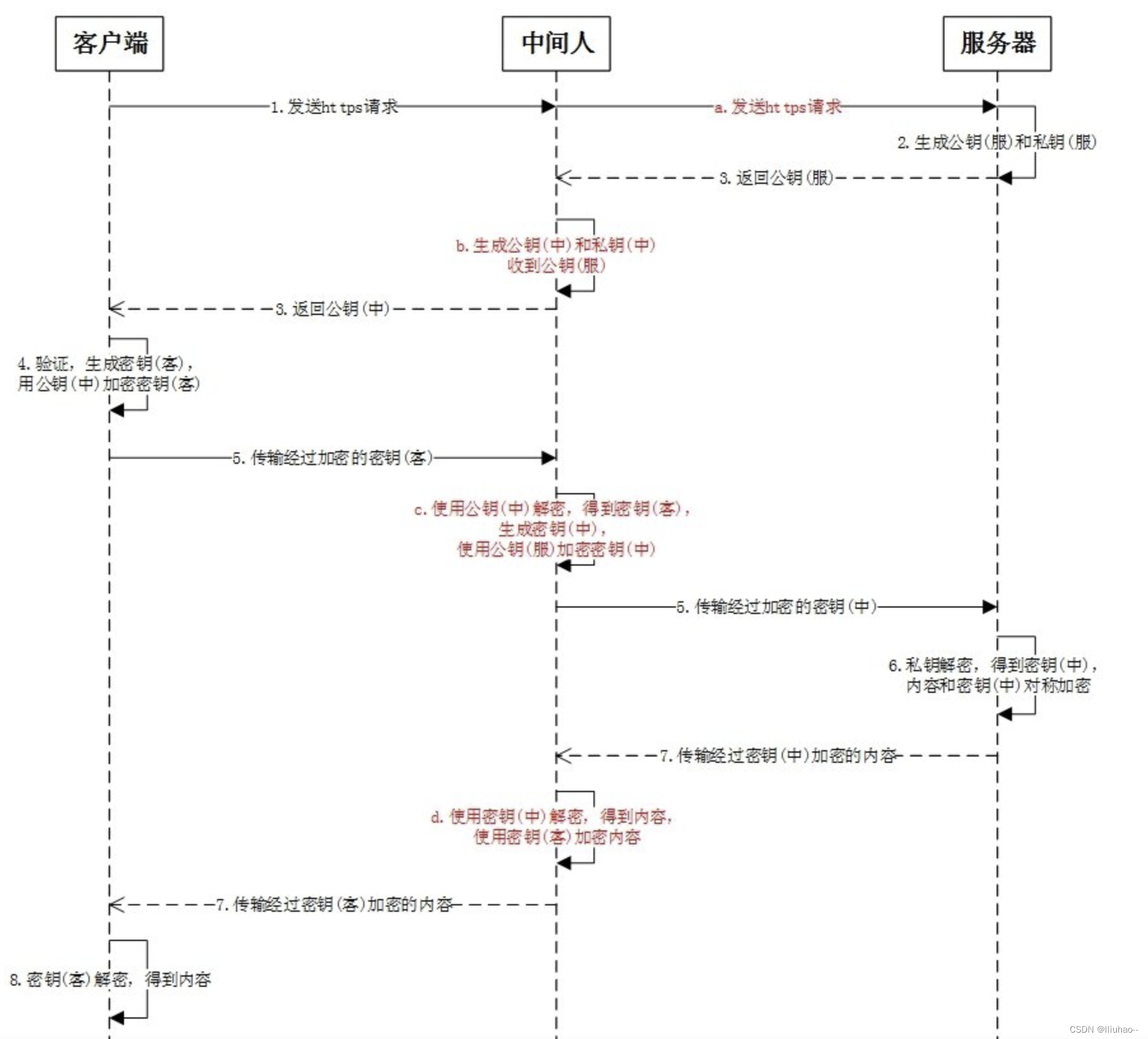

HTTPS连接过程中的中间人攻击

HTTPS连接过程中的中间人攻击 HTTPS连接过程中间人劫持攻击 HTTPS连接过程 https协议就是httpssl/tls协议,如下图所示为其连接过程: HTTPS连接的整个工程如下: https请求:客户端向服务端发送https请求;生成公钥和私…...

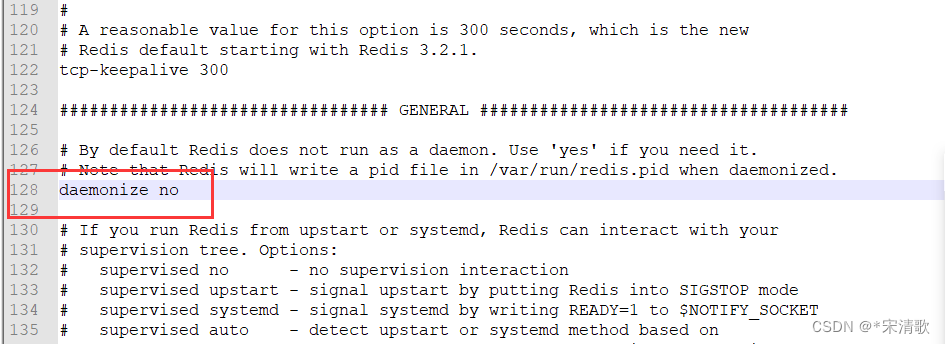

redis启动失败,oO0OoO0OoO0Oo Redis is starting oO0OoO0OoO0Oo

在redis文件夹下,启动redis正常。 但是加入到system后启动redis失败。 一直处于starting状态。 对比正常redis服务的配置之后,把redis.conf里的守护进程关掉就可以了(但是没用system管理之前,直接./redis.server启动是可以的&…...

milvus: 专为向量查询与检索设计的向量数据库

1. 什么是milvus? milvus docs milvus release Milvus的目标是:store, index, and manage massive embedding vectors generated by deep neural networks and other machine learning (ML) models. Milvus 向量数据库专为向量查询与检索设计…...

【C# 数据结构】Heap 堆

【C# 数据结构】Heap 堆 先看看C#中有那些常用的结构堆的介绍完全二叉树最大堆 Heap对类进行排序实现 IComparable<T> 接口 对CompareTo的一点解释 参考资料 先看看C#中有那些常用的结构 作为 数据结构系类文章 的开篇文章,我们先了解一下C# 有哪些常用的数据…...

智慧园区楼宇合集:数字孪生管控系统

智慧园区是指将物联网、大数据、人工智能等技术应用于传统建筑和基础设施,以实现对园区的全面监控、管理和服务的一种建筑形态。通过将园区内设备、设施和系统联网,实现数据的传输、共享和响应,提高园区的管理效率和运营效益,为居…...

UnrealPakViewer:虚幻引擎资源分析与Pak文件解析工具指南

UnrealPakViewer:虚幻引擎资源分析与Pak文件解析工具指南 【免费下载链接】UnrealPakViewer 查看 UE4 Pak 文件的图形化工具,支持 UE4 pak/ucas 文件 项目地址: https://gitcode.com/gh_mirrors/un/UnrealPakViewer 作为虚幻引擎开发者࿰…...

Rust离线部署技术方案:企业级零网络依赖实施指南

Rust离线部署技术方案:企业级零网络依赖实施指南 【免费下载链接】rustup The Rust toolchain installer 项目地址: https://gitcode.com/gh_mirrors/ru/rustup 场景痛点:网络隔离环境下的Rust部署挑战 在企业内网、高安全等级环境或网络不稳定场…...

从‘单打独斗’到‘团队协作’:实战解析如何将DeepSeek的文本能力与Gemini的多模态API组合使用

从‘单打独斗’到‘团队协作’:实战解析如何将DeepSeek的文本能力与Gemini的多模态API组合使用 在AI技术日新月异的今天,开发者们常常面临一个困境:是选择专注于单一领域的强大模型,还是尝试整合多个模型的优势?这个问…...

Calibre中文路径保护插件:如何让电子书保持原汁原味的中文命名

Calibre中文路径保护插件:如何让电子书保持原汁原味的中文命名 【免费下载链接】calibre-do-not-translate-my-path Switch my calibre library from ascii path to plain Unicode path. 将我的书库从拼音目录切换至非纯英文(中文)命名 项目…...

在 Windows 上实现 SSH 掉线重连与会话持久化

在 Windows 上实现 SSH 掉线重连与会话持久化:完整方案指南 SSH 是连接和管理远程 Linux 服务器的必备工具,但在 Windows 环境下,网络波动或电脑休眠常常导致 SSH 连接中断,正在运行的任务(如模型训练、编译等…...

BGE-Large-Zh效果可视化:向量维度投影图+相似度分布直方图双模展示

BGE-Large-Zh效果可视化:向量维度投影图相似度分布直方图双模展示 1. 项目概述 BGE-Large-Zh是一款专为中文语义理解设计的本地化向量化工具,基于BAAI的bge-large-zh-v1.5模型开发。这个工具能够将中文文本转换为1024维的语义向量,并通过计…...

12年不上班,我靠什么支撑到现在

我已经12年没去上过班了,14年从学校辞职出来后,就没再给人打过工。虽然我不上班,但身边人都觉得我很会赚钱,觉得我很幸运,也觉得我很有勇气。 其实,并不是我多勇敢,是因为早在2014年,…...

REFramework:游戏增强引擎与开源工具集的革新实践

REFramework:游戏增强引擎与开源工具集的革新实践 【免费下载链接】REFramework Mod loader, scripting platform, and VR support for all RE Engine games 项目地址: https://gitcode.com/GitHub_Trending/re/REFramework 价值定位:重新定义RE引…...

告别默认丑界面!手把手教你用.vimrc文件配置出高颜值、高效率的Gvim工作环境

告别默认丑界面!手把手教你用.vimrc文件配置出高颜值、高效率的Gvim工作环境 第一次打开Gvim时,那个灰蒙蒙的界面和密密麻麻的代码是不是让你瞬间失去了继续使用的欲望?别急着关掉它——通过简单的.vimrc配置,你完全可以把这款经典…...

Pixel Dream Workshop 创意激发:利用算法生成无限可能的艺术图案与纹理

Pixel Dream Workshop 创意激发:利用算法生成无限可能的艺术图案与纹理 1. 当算法遇见艺术:数字创作的新纪元 在传统艺术创作中,设计师们常常需要花费大量时间手工绘制图案和纹理。而如今,Pixel Dream Workshop的出现彻底改变了…...