02 认识Verilog HDL

02 认识Verilog HDL

对于Verilog的语言的学习,我认为没必要一开始就从头到尾认真的学习这个语言,把这个语言所有细节都搞清楚也不现实,我们能够看懂当前FPGA的代码的程度就可以了,随着学习FPGA深度的增加,再不断的去查阅不会的Verilog的语法。例如下面这个流水灯的程序,请带着能够看懂这段代码的目的去开始Verilog的入门学习吧!

module flow_led(input sys_clk , input sys_rst_n, output reg [3:0] led );//reg define

reg [23:0] counter;//*****************************************************

//** main code

//***************************************************** always @(posedge sys_clk or negedge sys_rst_n) beginif (!sys_rst_n)counter <= 24'd0;else if (counter < 24'd1000_0000)counter <= counter + 1'b1;elsecounter <= 24'd0;

endalways @(posedge sys_clk or negedge sys_rst_n) beginif (!sys_rst_n)led <= 4'b0001;else if(counter == 24'd1000_0000) led[3:0] <= {led[2:0],led[3]};elseled <= led;

endendmodule

一. Verilog 简介

Verilog 是一种硬件描述语言,FPGA 开发主要有两种语言,Verilog 和 VHDL。 而 Verilog 更加容易上手, Verilog 是在 C 语言的基础上发展出来的。其语法也和 C 语言更加的接近,入门更加的简单,也是目前最多使用的。

特点:

1. 语法自由,易学易用。2.代码简单。3.发展速度快。3.适合算法级,门级设计。

二. Verilog 基础语法

1.逻辑值

(1) 0:低电平

(2) 1:高电平

(3) z : 高阻态

(4) x:未知状态

2. 关键字

module endmodule input outpt inout

2.2 变量

Verilog 最常用的 2 种数据类型就是线网(wire)与寄存器(reg)。

wire : 直接的连接,会被映射成真实的物理连接,表示硬件单元之间的物理连线,由其连接的器件输出端连续驱动。

**reg:**某一时间点状态的保持,会被映射成物理寄存器,用来表示存储单元,它会保持数据原有的值,直到被改写

reg [3:0] counter ; //声明4bit位宽的寄存器counter

wire [32-1:0] gpio_data; //声明32bit位宽的线型变量gpio_data

2.3 参数

二者之间有区别和联系,使用到再详细结介绍。

parameter:

localparam:

2.4 常量

表示格式 :[换算成二进制后的总长度]'[数制进制符号][与数值进制符号对应的数值]

8'd171: 位宽为 8,十进制的 171.

直接写 100,就表示 32'd100,模式是 10 进制 32 位宽,这是 verliog 中默认的。

3.赋值方式

Verliog 中的赋值方式有两种 阻塞赋值 和 非阻塞赋值。

阻塞赋值

a=1;b=2;

顺序执行,当执行完 a=1,才去执行 b=2;

非阻塞赋值

a<=1;b<=2;

两条语句是同时执行的。

4.常用的语句

过程结构语句有 2 种,initial 与 always 语句。它们是行为级建模的 2 种基本语句。

一个模块中可以包含多个 initial 和 always 语句,但 2 种语句不能嵌套使用。

这些语句在模块间并行执行,与其在模块的前后顺序没有关系。

但是 initial 语句或 always 语句内部可以理解为是顺序执行的(非阻塞赋值除外)。

每个 initial 语句或 always 语句都会产生一个独立的控制流,执行时间都是从 0 时刻开始。

4.1 always

4.2 initial

只在仿真文件中使用,不可综合的。

4.2 if else

和 c 语言中的使用一致。

if():

else():

4.3 case

在 c 语言的基础上,在结束的时候需要添加一个 endcase。

case() <> : 语句1;<> : 语句2;default :

endcase

4.4 assign( 全加器)

4.5 @(事件控制)

语句执行的条件是信号的值发生特定的变化。

关键字 posedge 指信号发生边沿正向跳变,negedge 指信号发生负向边沿跳变,未指明跳变方向时,则 2 种情况的。

5. 常用的运算符

基础的运算符的使用和 c 语言中大概相同,使用到的时候如果不会,自己复习一下就好,这里说明不常见的运算符,但在 Verliog 中经常使用到的。

5.1 位拼接运算符 {}

d = { a, b, c} // 将 a,b,c按顺序拼接成了d,注意的是a,b,c,d的宽度一定要符合。

5.2 条件运算符 ? :

也就是 c 语言中的三目运算符。

表达式1?表达式2:表达式3

如果表达式 1 为真,就执行 2,否则执行 3.

6. 系统函数

verliog 中系统预定义一些函数,完成特殊的功能,以下就是经常使用到的一些系统函数。

·timescale 1ns/1ns //时间尺度预编译指令 时间单位/时间精度

$display("%d",1); //用于输出,类似c语言中的print

$write("\n",1); //用于输出,和display一样,但是display可以自动换行,wirte需要换行符

#1 //表示延时的时间

$stop; //暂停仿真

$finish; //结束仿真

$time; //返回64位的当前时间

以反引号 ` 开始的某些标识符是 Verilog 系统编译指令。

相关文章:

02 认识Verilog HDL

02 认识Verilog HDL 对于Verilog的语言的学习,我认为没必要一开始就从头到尾认真的学习这个语言,把这个语言所有细节都搞清楚也不现实,我们能够看懂当前FPGA的代码的程度就可以了,随着学习FPGA深度的增加,再不断的…...

解决VUE安装依赖时报错:npm ERR! code ERESOLVE

前言 在使用 npm 安装项目依赖时,有时会遇到错误信息 “npm ERR! code ERESOLVE”,该错误通常发生在依赖版本冲突或者依赖解析问题时。本文将详细介绍出现这个错误的原因,并提供解决方法,确保正确安装项目依赖并避免该错误的发生。…...

软件公司的项目管理软件选择指南

我们经常在项目推进中经常遇到各种各样的问题,最常见的是因团队工作效率低而无法在截止日期之前按时完成工作。但是如果能合理使用项目管理软件,可以有效监控项目进程,提高工作效率,从而保证按时完成任务。那么软件公司适合什么项…...

2、服务器安装docker

# 1.卸载旧的版本 yum remove -y docker \ docker-client\ docker-client-latest\ docker-common docker-latest\ docker-latest-logrotate\ docker-logrotate docker-s…...

UDP报文结构

文章目录 一、UDP报头1.1源端口号1.2目的端口号1.3UDP报文长度1.4UDP校验和(checksum) UDP报头和UDP载荷(payload)之间的拼接可以认为是一个“字符串拼接”,里面是二进制数据。 一、UDP报头 UDP报头分成4个部分,每个部分2个字节。分别是: 1…...

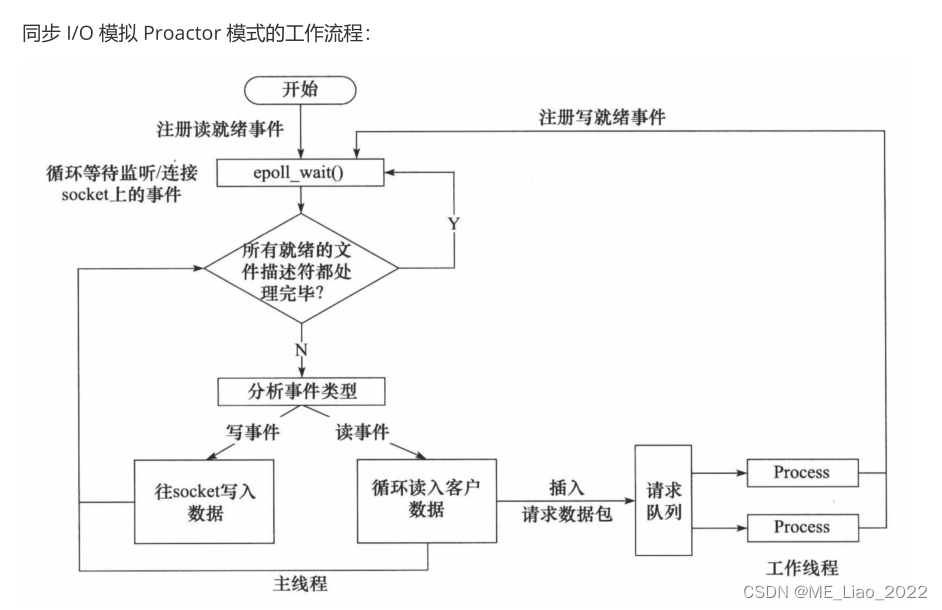

(高阶) Redis 7 第21讲 IO多路复用模型 完结篇

🌹 以下分享 Redis IO多路复用模型,如有问题请指教。🌹🌹 如你对技术也感兴趣,欢迎交流。🌹🌹🌹 如有对阁下帮助,请👍点赞💖收藏🐱🏍分享😀 IO多路复用模型是什么 I/O:网络IO 多路:多个客户端连接(连接即套接字描述符,即socket或channel),指…...

2023年入职/转行网络安全,该如何规划?

前言 前段时间,知名机构麦可思研究院发布了 《2022年中国本科生就业报告》,其中详细列出近五年的本科绿牌专业,其中,信息安全位列第一。 网络安全前景 对于网络安全的发展与就业前景,想必无需我多言,作为…...

解密RabbitMQ:你所不知道的端口及其重要性

解密RabbitMQ:你所不知道的端口及其重要性 前言第一部分:AMQP默认端口(5672)第二部分:RabbitMQ管理界面端口(15672)第三部分:Erlang Port Mapper Daemon(epmd)端口(4369&…...

)

Docker 环境搭建 (centeros)

CentOS环境下安装Docker 本文档将指导您在CentOS操作系统上安装Docker。Docker是一个开源的容器化平台,可以帮助您轻松地创建、部署和管理容器化应用程序。 步骤1:更新系统 在安装Docker之前,首先确保您的系统已经更新到最新版本。打开终端…...

服务器编程基本框架

服务器编程基本框架 虽然服务器程序种类繁多,但其基本框架都一样,不同之处在于逻辑处理。 I/O 处理单元是服务器管理客户连接的模块。它通常要完成以下工作:等待并接受新的客户连接,接收客户数据,将服务器响应数据返回…...

Leetcode——数组的遍历系列练习

485. 最大连续 1 的个数 class Solution { public:int findMaxConsecutiveOnes(vector<int>& nums) {// 记录最大连续1个数int max 0;// 记录数组中存在1个数int sum 0;// 遍历连续1个数int count 0;for (int i 0; i < nums.size() - 1; i) {if (nums[i] 1)s…...

免费的ChatGPT与StableDiffusion AI绘画 二合一 附在线地址

ChatGPT与StableDiffusion 在线地址在文末 介绍 嘿,大家好!今天我要给大家介绍一个非常酷炫的技术结合——ChatGPT与StableDiffusion的合作。听起来是不是很有趣?那么,让我们一起来看看这个组合到底能带给我们什么样的奇妙体验…...

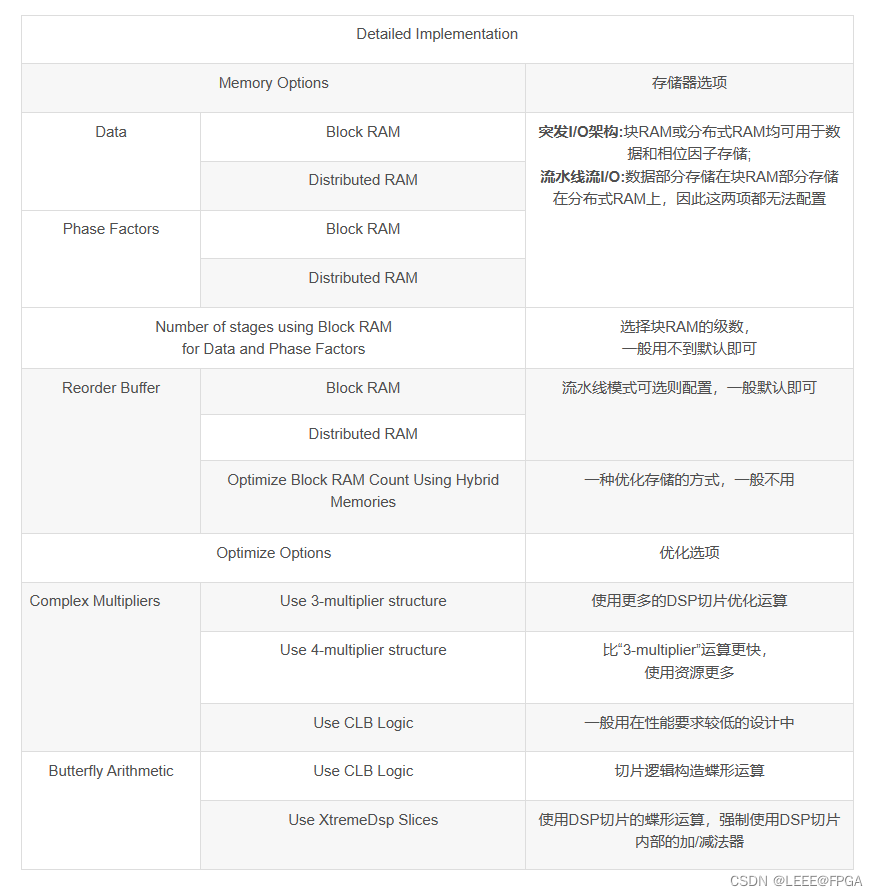

vivado FFT IP仿真(3)FFT IP选项说明

xilinx FFT IP手册PG109 1 Configuration 2 Implementation 3 Detailed Implementation IP Symbol...

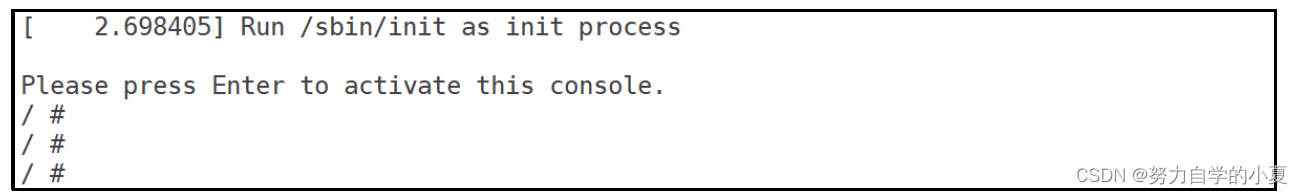

正点原子嵌入式linux驱动开发——Busybox根文件系统构建

前面已经移植了TF-A、Uboot和Linux kernel,就剩最后一个 rootfs(根文件系统)了,本章就来学习一下根文件系统的组成以及如何构建根文件系统。这是Linux系统移植的最后一步,根文件系统构建好以后就意味着拥有了一个完整的、可以运行的最小系统 …...

React闭包

声明 本文将深入探讨React与闭包之间的关系。 我们将首先介绍React和闭包的基本概念,然后详细解释React组件中如何使用闭包来处理状态和作用域的问题。 通过本文的阅读,你将对React中闭包的概念有更深入的理解,并能够在开发React应用时更好地…...

【VS Code】推荐一套我非常喜欢的主题和字体样式

话不多说,先上样式: 这里我的主题是 One Dark Pro,也是 VS Code 里面使用非常多的主题之一。直接安装插件即可使用。 我的字体是 JetBrains Mono,虽然使用的是 VS Code,但还是喜欢 webstorm 的字体。我们可以直接去官网…...

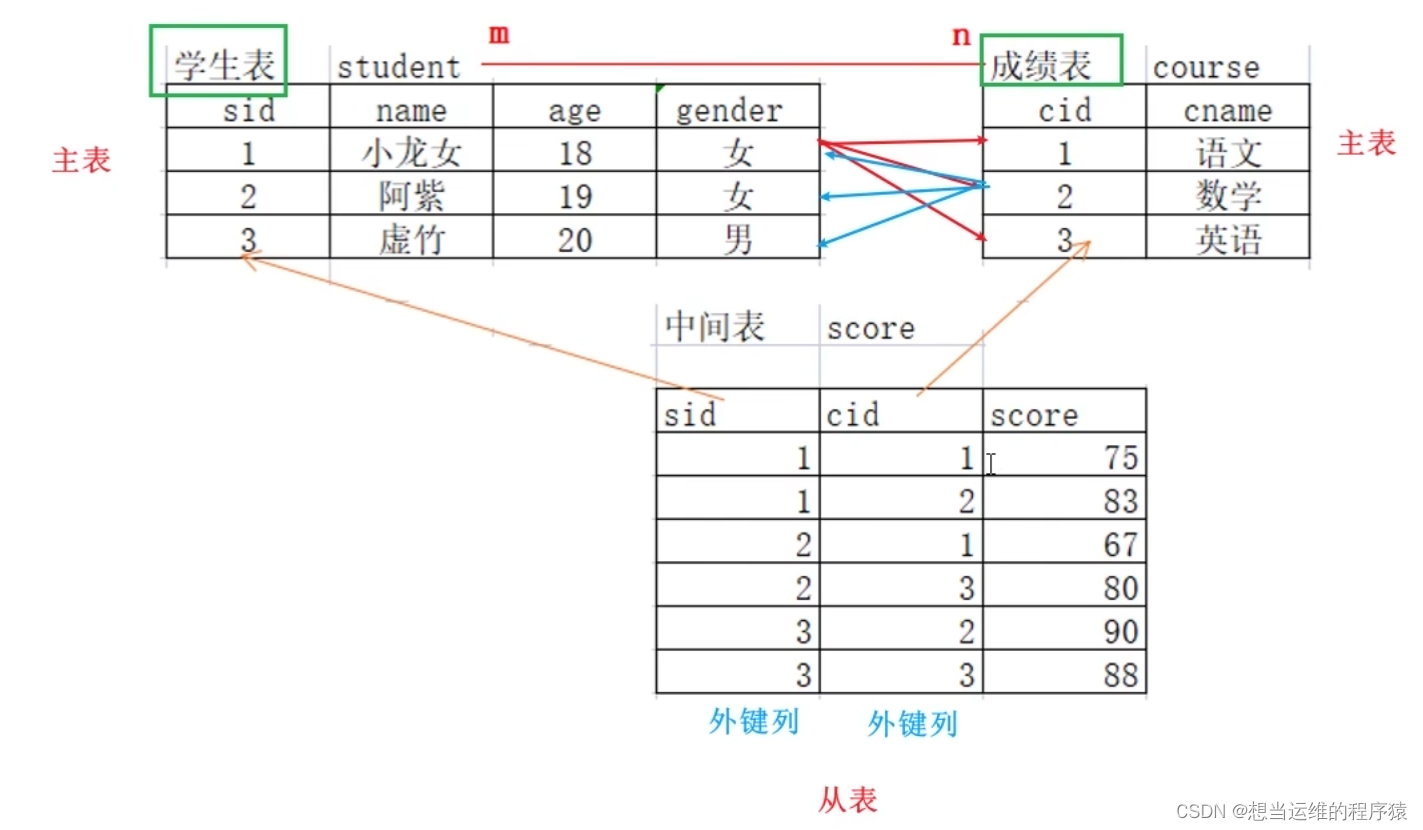

【SQL】MySQL中的约束

1. 主键约束(primary key): 相当于唯一约束非空约束分为单列主键,多列联合主键,一个表只有一个主键多列联合主键的每列都不能为空 2. 自增长约束(auto_increment): 用在单列主键后…...

css div左右布局

div左右布局 htm代码 <div class"content-box"><div class"left"></div><div class"right"></div></div>css样式 .content-box{height: 100%;width: 100%;display: flex; } .left{display: block;width:…...

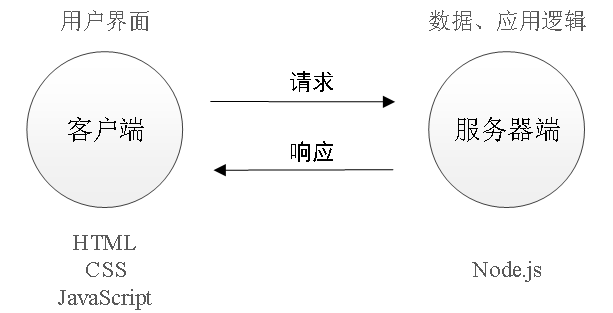

06_Node.js服务器开发

1 服务器开发的基本概念 1.1 为什么学习服务器开发 Node.js开发属于服务器开发,那么作为一名前端工程师为什么需要学习服务器开发呢? 为什么学习服务器开发? 能够和后端程序员更加紧密配合网站业务逻辑前置扩宽知识视野 1.2 服务器开发可…...

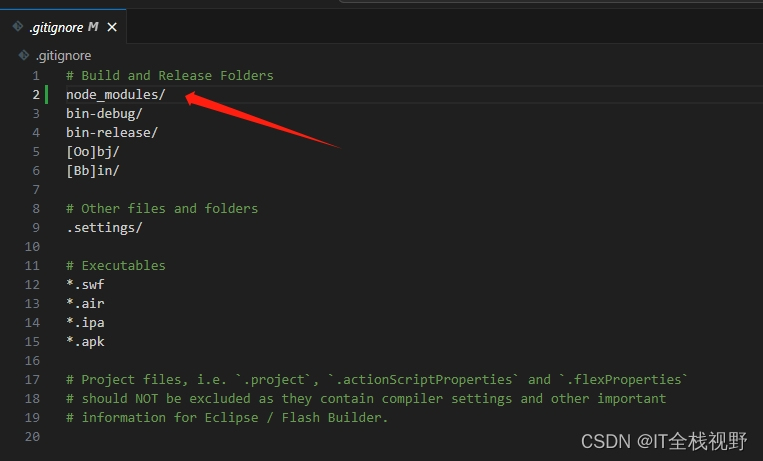

git中添加不上传的文件夹或文件的名字

在该目录.gitignore中 添加不上传的文件夹或文件的名字...

)

等保测评必看!用组策略批量关闭445/139端口(域环境适用版)

企业域环境下批量关闭高危端口的组策略实战指南 在等保测评和日常安全运维中,445、139、135等端口因其历史漏洞和潜在风险,常被列为必须管控的高危端口。对于拥有数百甚至上千台终端的中大型企业来说,逐台手动配置不仅效率低下,更…...

【独家首发】Polars 2.0 vs Pandas 2.2清洗基准测试:10亿行CSV清洗仅耗11.3秒?真相在此

第一章:Polars 2.0大规模数据清洗的范式跃迁Polars 2.0 不再是 Pandas 的轻量替代品,而是一次面向现代硬件与真实业务场景的数据处理范式重构。其核心跃迁体现在零拷贝内存布局、全链路惰性执行引擎(LazyFrame)与原生支持的并行流…...

Go语言的context.WithCancel取消信号传播与资源清理在分布式系统中的协调

Go语言的context.WithCancel取消信号传播与资源清理在分布式系统中的协调 在分布式系统中,任务的取消与资源清理是确保系统稳定性和高效性的关键挑战。Go语言通过context包提供了优雅的解决方案,尤其是context.WithCancel机制,能够实现跨组件…...

一本计算机专业,准大一,有什么忠告?

你现在大概处于一种很特别的状态。高考刚结束不久,录取通知书拿到了,专业是计算机。可能是你自己选的,也可能是家里建议的,也可能是分数刚好够就填了。不管哪种,你现在对”计算机专业到底学什么”的理解大概率是模糊的…...

STM32姿态报警器设计:MPU6050与卡尔曼滤波实战

基于STM32的姿态翻转报警器设计与实现1. 项目概述1.1 系统架构本姿态翻转报警系统采用模块化设计,核心架构由STM32F103RCT6微控制器作为主控单元,通过I2C接口连接MPU6050惯性测量单元(IMU)传感器,实时采集设备的三轴加速度和三轴角速度数据。…...

参数)

煤矿电液阀系统摄像仪护套连接器 DLJ01(1000)参数

在煤矿综采工作面液压支架电液控制系统中,摄像仪护套连接器 DLJ01(1000)作为矿用本安型摄像仪与电源、信号传输线缆之间的专用接口,承担着视频信号与供电的稳定传输任务。其型号中的“1000”代表线缆长度为1000mm(1米),…...

CentOS7下SSD性能调优实战:iostat与dd命令的黄金组合

CentOS7下SSD性能调优实战:iostat与dd命令的黄金组合 在当今数据驱动的时代,存储性能往往成为系统瓶颈的关键所在。对于使用CentOS7系统的运维工程师来说,如何充分释放SSD硬件的性能潜力,是一个既具挑战性又充满成就感的技术课题。…...

)

数据清洗避坑指南:缺失值和异常值处理的5个常见错误(附真实案例)

数据清洗避坑指南:缺失值和异常值处理的5个常见错误(附真实案例) 在电商平台的用户行为分析中,我们曾遇到一个诡异现象:某促销活动页面的转化率突然飙升到98%。进一步排查发现,是爬虫程序将未加载完成的页…...

云容笔谈开源镜像优势:免编译、免依赖、BF16原生支持,开箱即生成

云容笔谈开源镜像优势:免编译、免依赖、BF16原生支持,开箱即生成 最近在尝试各种AI图像生成工具时,我发现了一个很有意思的现象:很多工具要么安装配置复杂,要么生成效果不尽如人意,特别是想要生成具有东方…...

)

新手避坑指南:用Prometheus+PX4+ROS在Gazebo里复现无人机追踪小车(保姆级流程)

新手避坑指南:用PrometheusPX4ROS在Gazebo里复现无人机追踪小车(保姆级流程) 当第一次接触无人机仿真开发时,很多人会被复杂的工具链和晦涩的错误信息劝退。本文将手把手带你完成从零搭建仿真环境到实现视觉追踪的全过程ÿ…...