FPGA project : flash_secter_erase

flash的指定扇区擦除实验。

先发写指令,再进入写锁存周期等待500ns,进入写扇区擦除指令,然后写扇区地址,页地址,字节地址。即可完成扇区擦除。

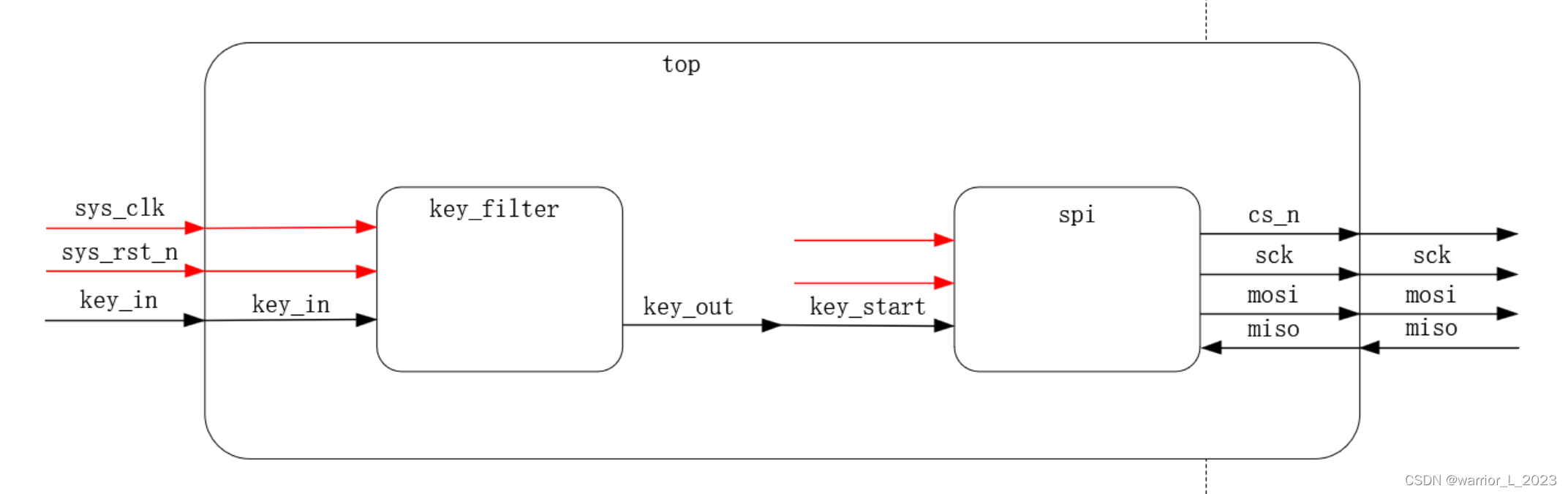

模块框图:

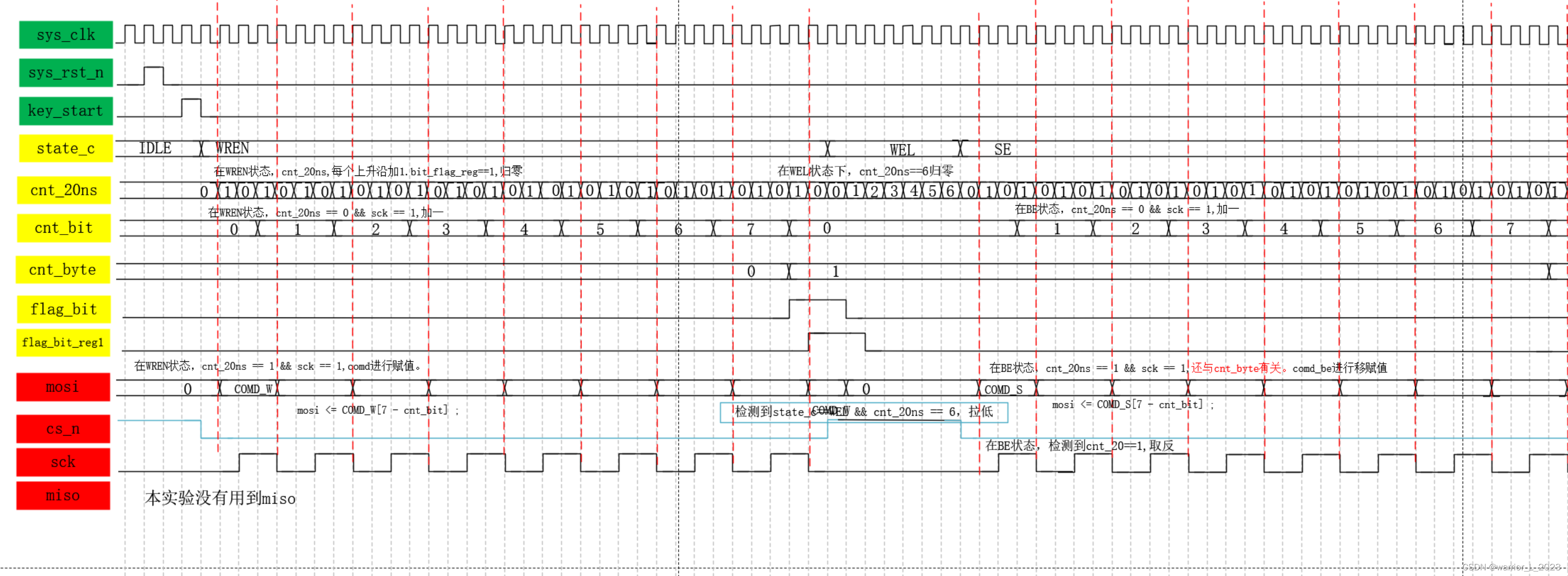

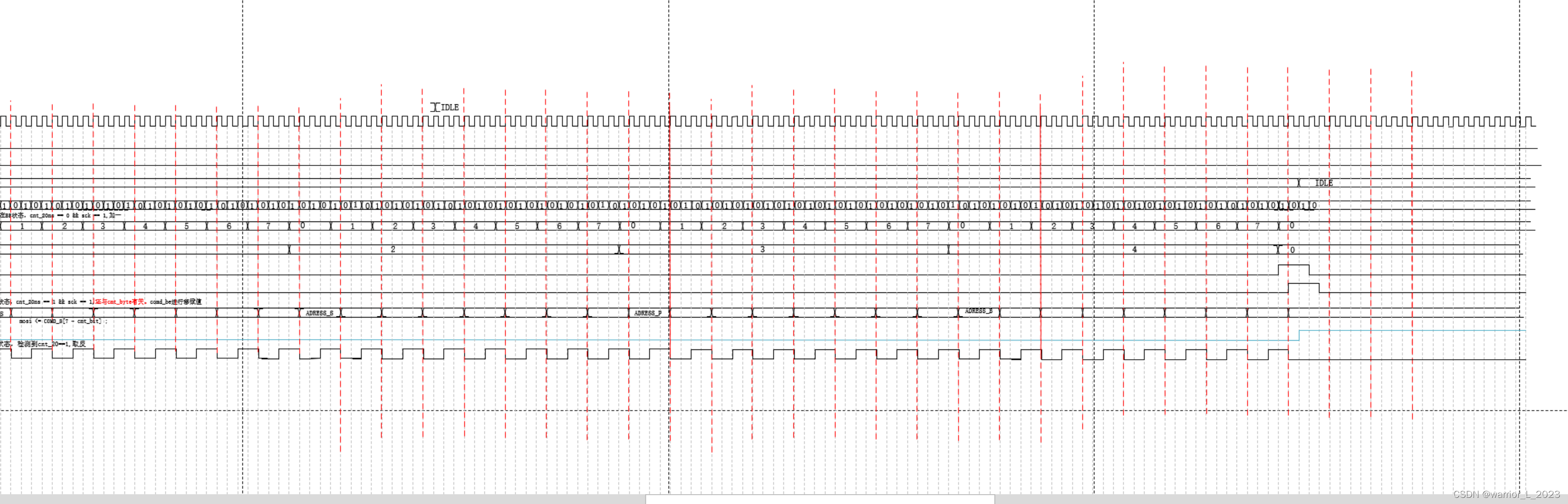

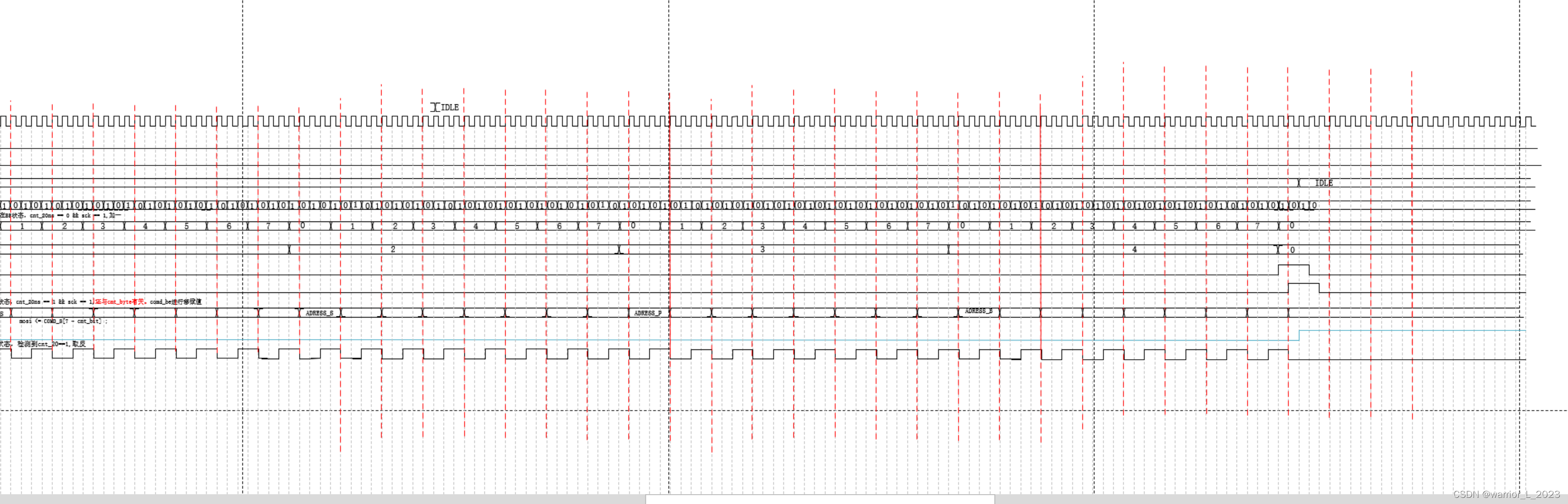

时序图:

代码:

module spi (input wire sys_clk ,input wire sys_rst_n , input wire key_start ,output wire miso ,output reg mosi ,output reg cs_n ,output reg sck

);// parameter parameter COMD_W = 8'h06 , // 写指令COMD_B = 8'hc7 , // 全擦除指令COMD_S = 8'hd8 ; // 扇区擦除指令parameter ADR_SE = 8'h00 , // 扇区地址 adress secterADR_PA = 8'h04 , // 页地址 adress pageADR_BY = 8'h25 ; // 字节地址 adress byteparameter IDLE = 4'b0001 ,WREN = 4'b0010 ,WEL = 4'b0100 ,SE = 4'b1000 ;// wire signal deginewire IDLEtoWREN; wire WRENtoWEL ; wire WRENtoSE ; wire SEtoIDLE ; // reg signal definereg [3:0] state_c ;reg [3:0] state_n ;reg [3:0] cnt_20ns ;reg [3:0] cnt_bit ;reg [3:0] cnt_byte ;reg flag_bit ;reg f_b_reg ; // flag_bit_reg的缩写

/****************************************************************************/// 三段式状态机// 现态与次态描述// state_calways @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) state_c <= IDLE ;elsestate_c <= state_n ;end// state_nalways @(*) begincase (state_c)IDLE :if(IDLEtoWREN)state_n <= WREN ;else state_n <= IDLE ;WREN :if(WRENtoWEL)state_n <= WEL ;else state_n <= WREN ;WEL :if(WRENtoSE)state_n <= SE ;else state_n <= WEL ;SE :if(SEtoIDLE)state_n <= IDLE ;else state_n <= SE ;default: state_n <= IDLE ;endcaseend// 状态转移描述assign IDLEtoWREN = ( state_c == IDLE) && ( key_start ) ;assign WRENtoWEL = ( state_c == WREN) && ( f_b_reg ) ;assign WRENtoSE = ( state_c == WEL ) && ( cnt_20ns == 6 ) ;assign SEtoIDLE = ( state_c == SE ) && ( f_b_reg ) ;// 相关信号描述// reg [3:0] cnt_20ns ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) cnt_20ns <= 4'd0 ;else case (state_c)IDLE : cnt_20ns <= 4'd0 ;WREN : if(cnt_20ns || f_b_reg)cnt_20ns <= 4'd0 ;else cnt_20ns <= cnt_20ns + 1'b1 ;WEL : if(cnt_20ns == 6) // 60x20ns==120nscnt_20ns <= 4'd0 ;elsecnt_20ns <= cnt_20ns + 1'b1 ;SE : if(cnt_20ns || f_b_reg)cnt_20ns <= 4'd0 ;else cnt_20ns <= cnt_20ns + 1'b1 ;default: cnt_20ns <= 4'd0 ;endcaseend// reg [3:0] cnt_bit ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n)cnt_bit <= 4'd0 ;else case (state_c)IDLE : cnt_bit <= 4'd0 ;WREN : if(!cnt_20ns && sck && cnt_bit == 7)cnt_bit <= 4'd0 ;else if(!cnt_20ns && sck)cnt_bit <= cnt_bit + 1'b1 ;WEL : cnt_bit <= 4'd0 ;SE : if(!cnt_20ns && sck && cnt_bit == 7)cnt_bit <= 4'd0 ;else if(!cnt_20ns && sck)cnt_bit <= cnt_bit + 1'b1 ;default: cnt_bit <= 4'd0 ;endcaseend// reg [3:0] cnt_bytealways @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) cnt_byte <= 4'd0 ;else if(cnt_bit == 7 && !cnt_20ns && sck && cnt_byte == 4)cnt_byte <= 4'd0 ;else if(cnt_bit == 7 && !cnt_20ns && sck)cnt_byte <= cnt_byte + 1'b1 ;else cnt_byte <= cnt_byte ;end// reg flag_bit ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) flag_bit <= 1'b0 ;elsecase (state_c)IDLE : flag_bit <= 1'b0 ;WREN : if(cnt_bit == 7 && sck && !cnt_20ns)flag_bit <= 1'b1 ;else flag_bit <= flag_bit ;WEL : flag_bit <= 1'b0 ;SE : if(cnt_bit == 7 && sck && !cnt_20ns && cnt_byte == 4)flag_bit <= 1'b1 ;else flag_bit <= flag_bit ;default: flag_bit <= 1'b0 ;endcaseend// reg f_b_reg ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) beginf_b_reg <= 1'b0 ;end else beginf_b_reg <= flag_bit ;endend// output signal// wire miso ,assign miso = 1'bz ;// mosialways @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n)mosi <= 1'b0 ;elsecase (state_c)IDLE : mosi <= 1'b0 ;WREN : if(!cnt_bit) // (cnt_bit == 0)mosi <= COMD_W[7] ;else if(cnt_20ns && sck)mosi <= COMD_W[7 - cnt_bit] ;else mosi <= mosi ;WEL : mosi <= 1'b0 ;SE : case (cnt_byte)1: beginif(!cnt_bit)mosi <= COMD_S[7] ;else if(cnt_20ns && sck)mosi <= COMD_S[7 - cnt_bit] ;else mosi <= mosi ; end2: beginif(!cnt_bit)mosi <= ADR_SE[7] ;else if(cnt_20ns && sck)mosi <= ADR_SE[7 - cnt_bit] ;else mosi <= mosi ; end3: beginif(!cnt_bit)mosi <= ADR_PA[7] ;else if(cnt_20ns && sck)mosi <= ADR_PA[7 - cnt_bit] ;else mosi <= mosi ; end4: beginif(!cnt_bit)mosi <= ADR_BY[7] ;else if(cnt_20ns && sck)mosi <= ADR_BY[7 - cnt_bit] ;else mosi <= mosi ; enddefault: mosi <= 1'b0 ;endcasedefault: mosi <= 1'b0 ;endcaseend// reg cs_n ,always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) begincs_n <= 1'b1 ;end else begincase (state_c)IDLE : if(key_start)cs_n <= 1'b0 ;else cs_n <= 1'b1 ;WREN : if(f_b_reg)cs_n <= 1'b1 ;else cs_n <= cs_n ;WEL : if(cnt_20ns == 6) cs_n <= 1'b0 ;else cs_n <= cs_n ;SE : if(f_b_reg)cs_n <= 1'b1 ;else cs_n <= cs_n ;default: cs_n <= 1'b1 ;endcaseendend// reg sck always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n)sck <= 1'b0 ;else case (state_c)IDLE : sck <= 1'b0 ;WREN : if(cnt_20ns)sck <= ~sck ;else sck <= sck ;WEL : sck <= 1'b0 ;SE : if(cnt_20ns)sck <= ~sck ;else sck <= sck ;default: sck <= 1'b0 ;endcaseendendmodule

module top(input wire sys_clk ,input wire sys_rst_n ,input wire key_in ,output wire cs_n ,output wire sck ,output wire mosi

);// 例化间连线wire key_flag ;key_filter key_filter_inst(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_in ( key_in ) ,.key_out ( key_flag )

);spi spi_inst(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_start ( key_flag ) ,.mosi ( mosi ) ,.miso ( ) ,.cs_n ( cs_n ) ,.sck ( sck )

);endmodulemodule key_filter

#(parameter MAX_CNT_20MS = 20'd100_0000

)(input wire sys_clk ,input wire sys_rst_n ,input wire key_in ,output wire key_out

);reg key_r_0 ;reg key_r_1 ;wire nege ;wire pose ;reg [19:00] cnt_20ms ;wire add_cnt_20ms ;wire end_cnt_20ms ;reg add_cnt_flag ;// key_r_0 key_r_1 always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) beginkey_r_0 <= 1'b1 ;end else beginkey_r_0 <= key_in ;endendalways @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) beginkey_r_1 <= 1'b1 ;end else beginkey_r_1 <= key_r_0 ;endend// nege poseassign nege = ~key_r_0 && key_r_1 ;assign pose = key_r_0 && ~key_r_1 ;// add_cnt_flagalways @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) beginadd_cnt_flag <= 1'b0 ;end else beginif(nege) beginadd_cnt_flag <= 1'b1 ;end else beginif( pose || end_cnt_20ms ) beginadd_cnt_flag <= 1'b0 ;end else beginadd_cnt_flag <= add_cnt_flag ;endend endend// cnt_20ms add_cnt_20ms end_cnt_20msalways @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) begincnt_20ms <= 20'd0 ;end else beginif(add_cnt_20ms) beginif(end_cnt_20ms) begincnt_20ms <= 20'd0 ;end else begincnt_20ms <= cnt_20ms + 20'd1 ;endend else begincnt_20ms <= 20'd0 ;endendendassign add_cnt_20ms = add_cnt_flag ;assign end_cnt_20ms = add_cnt_20ms && cnt_20ms == ( MAX_CNT_20MS - 1'b1 ) ;// key_out// always @(posedge sys_clk or negedge sys_rst_n) begin// // always @(*) begin // 这样的话 会综合成 数据选择器// if(~sys_rst_n) begin// key_out <= 1'b0 ;// end else begin// if(end_cnt_20ms) begin// key_out <= 1'b1 ;// end else begin// key_out <= 1'b0 ;// end// end// endassign key_out = end_cnt_20ms ;

endmodule

仿真图:忘记截屏了。

需要用到仿真模型。

上版验证通过。

相关文章:

FPGA project : flash_secter_erase

flash的指定扇区擦除实验。 先发写指令,再进入写锁存周期等待500ns,进入写扇区擦除指令,然后写扇区地址,页地址,字节地址。即可完成扇区擦除。 模块框图: 时序图: 代码: module…...

HarmonyOS/OpenHarmony原生应用-ArkTS万能卡片组件Radio

单选框,提供相应的用户交互选择项。该组件从API Version 8开始支持。无子组件。 一、接口 Radio(options: {value: string, group: string}) 从API version 9开始,该接口支持在ArkTS卡片中使用。 参数: 二、属性 除支持通用属性外,还支持以…...

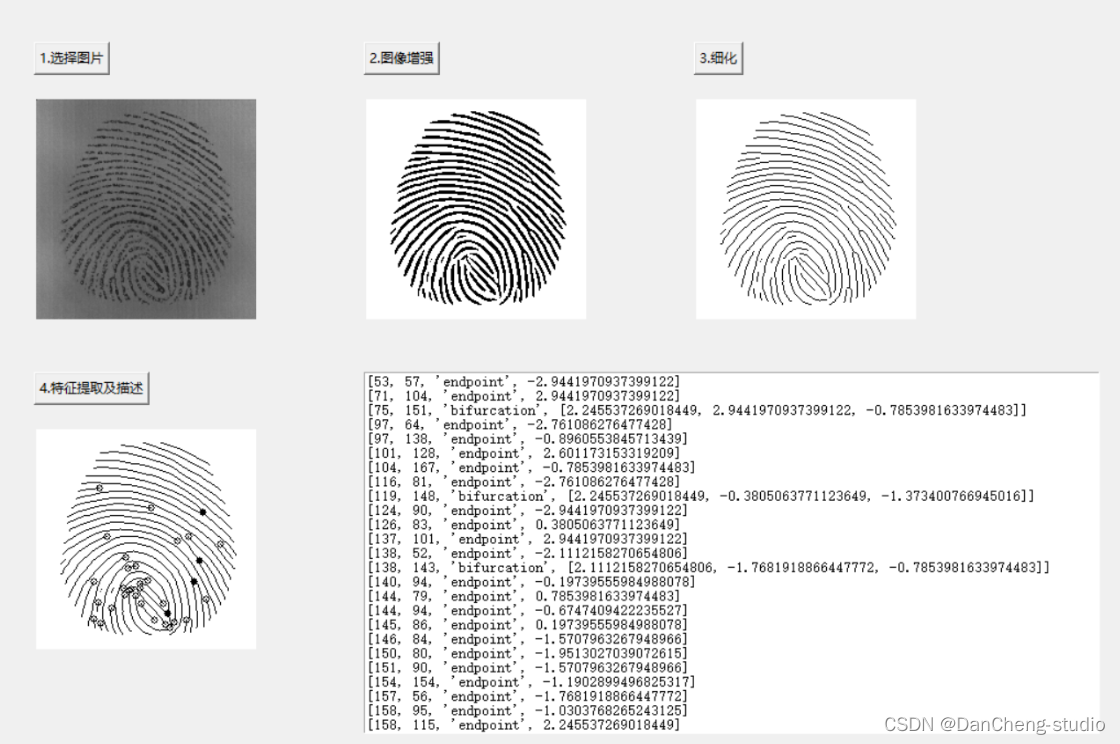

python opencv 深度学习 指纹识别算法实现 计算机竞赛

1 前言 🔥 优质竞赛项目系列,今天要分享的是 🚩 python opencv 深度学习 指纹识别算法实现 🥇学长这里给一个题目综合评分(每项满分5分) 难度系数:3分工作量:4分创新点:4分 该项目较为新颖…...

一图看懂CodeArts Inspector 三大特性,带你玩转漏洞管理服务

华为云漏洞管理服务CodeArts Inspector是面向软件研发和服务运维提供的一站式漏洞管理能力,通过持续评估系统和应用等资产,内置风险量化管理和在线风险分析处置能力,帮助组织快速感应和响应漏洞,并及时有效地完成漏洞修复工作&…...

)

【Mysql】Mysql的启动选项和系统变量(二)

概述 在Mysql的设置项中一般都有各自的默认值,比方说mysql 5.7服务器端允许同时连入的客户端的默认数量是 151 ,表的默认存储引擎是 InnoDB ,我们可以在程序启动的时候去修改这些默认值,对于这种在程序启动时指定的设置项也称之为…...

FPGA project : flash_read

实验目标: flash的普通读指令,在指定地址开始读。可以更改地址与读的数据个数。 先发送读指令扇区地址页地址字节地址。 然后读数据。再把读到的串行数据转化为8bit的数据,存入fifo。 然后读出FIFO中数据,通过uart_tx模块发送…...

nnunetv2训练报错 ValueError: mmap length is greater than file size

目录 报错解决办法 报错 笔者在使用 nnunetv2 进行 KiTS19肾脏肿瘤分割实验的训练步骤中 使用 2d 和3d_lowres 训练都没有问题 nnUNetv2_train 40 2d 0nnUNetv2_train 40 3d_lowres 0但是使用 3d_cascade_fullres 和 3d_fullres 训练 nnUNetv2_train 40 3d_cascade_fullres …...

-每天10个小知识)

React知识点系列(2)-每天10个小知识

目录 1. 如何优化 React 应用的性能?你用过哪些性能分析工具?2. 在 React 中,什么是 Context API?你在什么场景下会使用它?3. 你能解释一下什么是 React Fiber 吗?4. 在项目中,你是否使用过 Rea…...

AutoGPT:让 AI 帮你完成任务事情 | 开源日报 No.54

Significant-Gravitas/AutoGPT Stars: 150.4k License: MIT AutoGPT 是开源 AI 代理生态系统的核心工具包。它采用模块化和可扩展的框架,使您能够专注于以下方面: 构建 - 为惊人之作打下基础。测试 - 将您的代理调整到完美状态。查看 - 观察进展成果呈…...

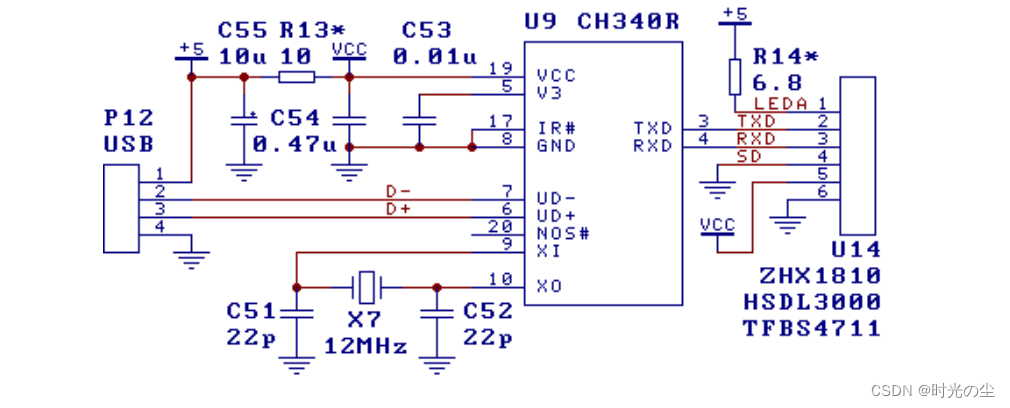

USB 转串口芯片 CH340

目录 1、概述 2、特点 3、封装 4、引脚 6、参数 6.1 绝对最大值(临界或者超过绝对最大值将可能导致芯片工作不正常甚至损坏) 6.2 电气参数(测试条件:TA25℃,VCC5V,不包括连接 USB 总线的引脚&…...

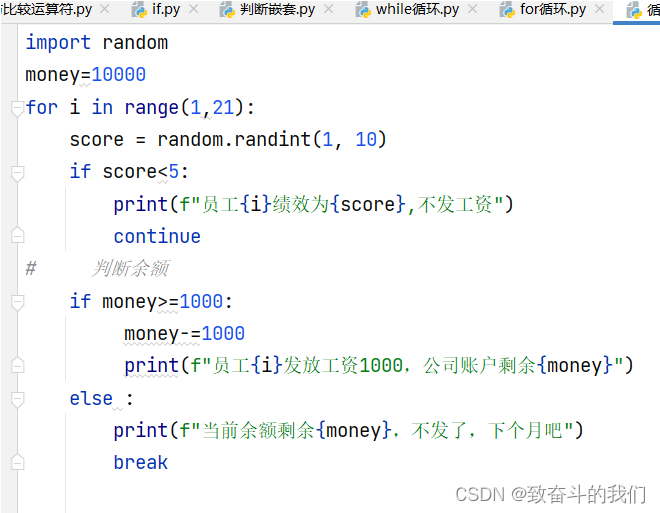

Day 05 python学习笔记

循环 应用:循环轮播图 最基础、最核心 循环:周而复始,谓之循环 (为了代码尽量不要重复) while循环 while的格式 索引定义 while 表达式(只要结果为布尔值即可): 循环体 通过条件的不断变化,从…...

Python如何17行代码画一个爱心

🌈write in front🌈 🧸大家好,我是Aileen🧸.希望你看完之后,能对你有所帮助,不足请指正!共同学习交流. 🆔本文由Aileen_0v0🧸 原创 CSDN首发🐒 如…...

生产环境中常用Linux命令

太简单的我就不讲解啦,浪费时间,直接将生产中常用的 文章目录 1.总纲2.整机 top3.CPU vmstat3. 内存 free4. 硬盘: df5. 磁盘IO iostat6. 网络IO ifstat7: 内存过高的情景排查 1.总纲 整机:topcpu:vmstat内存:free硬盘:df磁盘io: iostat网络io:ifstat 2.整机 top 首先们要查…...

【使用 TensorFlow 2】03/3 创建自定义损失函数

一、说明 TensorFlow 2发布已经接近5年时间,不仅继承了Keras快速上手和易于使用的特性,同时还扩展了原有Keras所不支持的分布式训练的特性。3大设计原则:简化概念,海纳百川,构建生态.这是本系列的第三部分,…...

Vue3中使用v-model高级用法参数绑定传值

Vue3中使用v-model高级用法参数绑定传值 单个输入框传值多个输入框传值,一个组件接受多个v-model值 单个输入框传值 App.vue <template><p>{{firstName}}</p><hello-world v-model"firstName"></hello-world> </template><…...

你的工作中,chatGPT可以帮你做什么?

如何在工作中使用 ChatGPT 的 10 种实用方法 现在您已经知道如何开始使用 ChatGPT 并了解其基本功能(提示 -> 响应),让我们探讨如何使用它来大幅提高工作效率。 1. 总结报告、会议记录等 ChatGPT可以快速分析大文本并识别关键点。例如&a…...

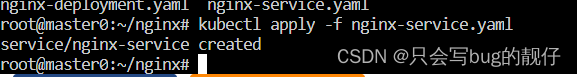

k8s简单部署nginx

文章目录 1. 前言2. 部署nginx2.1. **创建一个nginx的Deployment**2.2. **创建一个nginx的service** 3. 总结 1. 前言 前文提要: kubeadm简单搭建k8s集群第三方面板部署k8s 上篇文章我们简单部署了k8s的集群环境,相比一定迫不及待的想部署一个实际应用了…...

小黑子—MyBatis:第四章

MyBatis入门4.0 十 小黑子进行MyBatis参数处理10.1 单个简单类型参数10.1.1 单个参数Long类型10.1.2 单个参数Date类型 10.2 Map参数10.3 实体类参数(POJO参数)10.4 多参数10.5 Param注解(命名参数)10.6 Param注解源码分析 十一 小…...

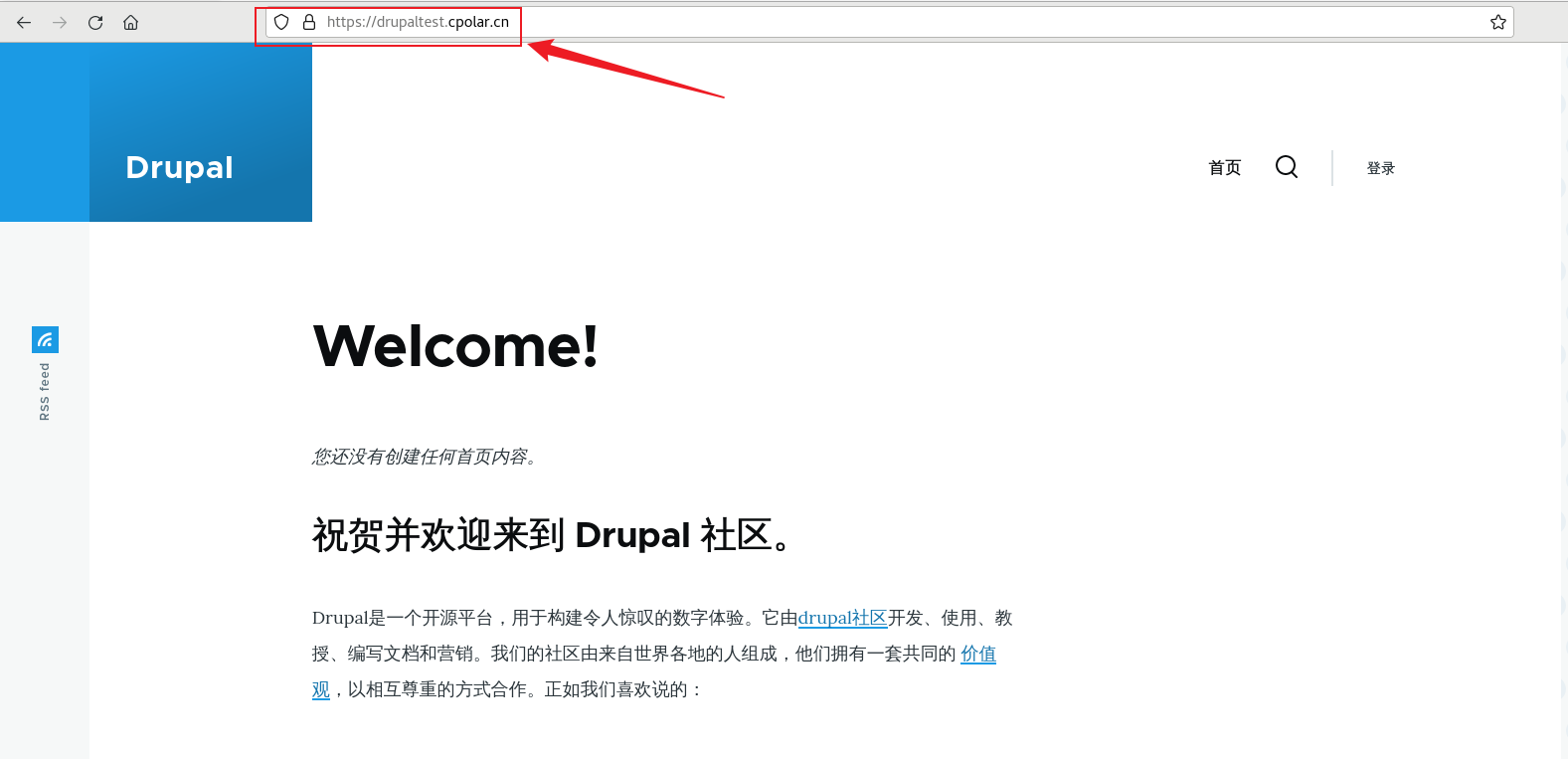

Docker快速上手:使用Docker部署Drupal并实现公网访问

文章目录 前言1. Docker安装Drupal2. 本地局域网访问3 . Linux 安装cpolar4. 配置Drupal公网访问地址5. 公网远程访问Drupal6. 固定Drupal 公网地址 前言 Dupal是一个强大的CMS,适用于各种不同的网站项目,从小型个人博客到大型企业级门户网站。它的学习…...

-每天10个小知识)

React知识点系列(1)-每天10个小知识

目录 1.什么是 React,以及它在前端开发中的优势是什么?2.你是如何组织和管理 React 组件的?3.你能解释一下 React 的生命周期方法吗?你通常在哪个生命周期方法中发起网络请求?4.什么是 React Hooks?你常用哪…...

FDTD Solutions 8.0 保姆级上手教程:从软件安装到第一个仿真结果

FDTD Solutions 8.0 零基础实战指南:从安装到首个完整仿真 当你第一次打开FDTD Solutions 8.0时,那些复杂的工具栏和陌生的术语可能会让你望而却步。作为一款专业的光学仿真软件,它确实有着陡峭的学习曲线——但别担心,这正是本文…...

)

告别GitHub!手把手教你用Gitblit在Windows 10上搭建私人局域网Git服务器(附SourceTree配置)

告别GitHub!手把手教你用Gitblit在Windows 10上搭建私人局域网Git服务器(附SourceTree配置) 在当今代码托管平台高度集中的环境下,越来越多的开发者开始关注数据主权和隐私保护。特别是对于金融、医疗等敏感行业的开发团队&#x…...

2025最新版PHP加密系统MENC加密系统 V2.4.0 含搭建教程

内容目录一、详细介绍二、效果展示1.部分代码2.效果图展示三、学习资料下载一、详细介绍 很牛逼的一款加密系统,PHP代码加密系统是一个值得信赖的工具,它可以帮助开发者保护自己的代码不受恶意攻击和盗用。无论是个人开发者还是企业用户,都可…...

:从Token溢出到模型幻觉全击破)

Perplexity编程问题解答实战手册(2024最新版):从Token溢出到模型幻觉全击破

更多请点击: https://intelliparadigm.com 第一章:Perplexity编程问题解答实战手册(2024最新版):从Token溢出到模型幻觉全击破 Perplexity 作为面向开发者优化的AI问答平台,其底层依赖大语言模型的上下文理…...

树莓派命令行保姆级避坑指南:从sudo权限到安全关机,别再乱敲命令了

树莓派命令行深度避坑手册:从权限管理到系统维护的黄金法则 当你第一次拿到树莓派时,那种兴奋感可能让你迫不及待地想尝试各种命令。但很快,你会发现这个小小的设备背后隐藏着许多"陷阱"——一个错误的sudo命令可能导致系统崩溃&am…...

Mac用户必看:免费开源的NTFS读写神器,3分钟解决跨平台文件传输难题

Mac用户必看:免费开源的NTFS读写神器,3分钟解决跨平台文件传输难题 【免费下载链接】Free-NTFS-for-Mac Nigate: An open-source NTFS utility for Mac. It supports all Mac models (Intel and Apple Silicon), providing full read-write access, moun…...

【亲测免费】 ADS1118驱动程序

ADS1118驱动程序 【下载地址】ADS1118驱动程序 本仓库提供了专用于ADS1118模数转换器(ADC)的驱动程序。ADS1118是一款高性能、高精度的16位模拟到数字转换器,广泛应用于需要精准测量的应用场景中,例如传感器数据采集系统、医疗设备…...

QT 5.14.2 编译调试踩坑实录:从‘file not found’到‘Illegal byte sequence’的保姆级排错指南

QT 5.14.2 编译调试实战:从文件缺失到编码陷阱的深度排错手册 接手一个遗留的QT串口通信项目时,本以为只是简单的代码移植,却在QT 5.14.2环境下遭遇了三个典型的"拦路虎":神秘的库文件失踪、程序突然崩溃的灵异事件&…...

从Polycam扫描到自定义街道:用3D高斯泼溅碎片‘搭积木’创建虚拟场景的完整流程

从Polycam扫描到自定义街道:用3D高斯泼溅碎片‘搭积木’创建虚拟场景的完整流程 走在城市的街道上,你是否曾想过把那些有趣的街景元素——复古的路灯、造型独特的长椅、枝繁叶茂的行道树——全都数字化,然后像玩乐高一样重新组合成自己理想中…...

FPGA验证核心:Vivado中功能与代码覆盖率的实战指南

1. 项目概述:为什么验证是FPGA开发的重中之重? 如果你刚接触FPGA开发,可能会觉得写代码(HDL)是最核心、最花时间的部分。但等你真正上手几个项目,尤其是那些需要流片或者部署到关键系统的项目后,…...